查询LC75366供应商

#### Ordering number : EN4929A

#### 捷多邦,专业PCB打样工厂,24小时加急出货

CMOS LSI

# LC75366, 75366M

# Two-Channel Electronic Volume Control

# **Overview**

The LC75366 (DIP20) and the LC75366M (MFP20) are electronic volume controls that can be controlled by serial input data and provide volume, balance and loudness functions.

## **Features**

• Silicon gate CMOS process for low switching noise

## **Functions**

• Volume: 0 dB to -68 dB (in 2 dB steps) and  $-\infty$ ; 36 positions.

A balance function can be implemented by controlling the left and right channel volume settings independently.

- Loudness: Taps are provided at the -20 dB positions in the 10 dB step resistor ladder used by the volume control function. A loudness function can be implemented by attaching external RC circuits at these tap points.

- An address selection pin (the S pin) allows two LC75366 chips to be used on the same bus.

- Serial data input: Supports CCB\* format communication with the system controller.

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

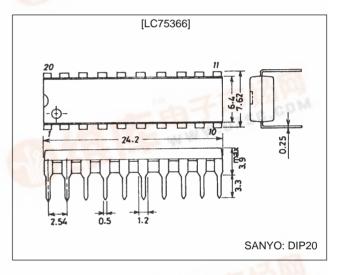

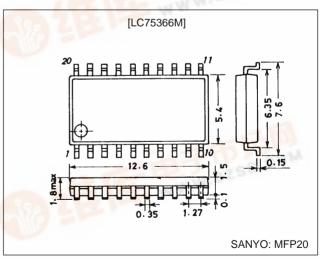

# Package Dimensions

unit: mm

#### 3021B-DIP20

unit: mm

#### 3036B-MFP20

# **Specifications**

Absolute Maximum Ratings at  $Ta = 25^{\circ}C$ ,  $V_{SS} = 0 V$

| Parameter                   | Symbol                              | Conditions                       | Ratings                          | Unit |

|-----------------------------|-------------------------------------|----------------------------------|----------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max V <sub>DD</sub> |                                  | 12                               | V    |

| Maximum input volto go      | V <sub>IN</sub> max1                | CL, DI, CE, S                    | $V_{SS}$ – 0.3 to $V_{DD}$ + 0.3 | V    |

| Maximum input voltage       | V <sub>IN</sub> max2                | L10dBIN, L2dBIN, R10dBIN, R2dBIN | $V_{SS}$ – 0.3 to $V_{DD}$ + 0.3 | V    |

| Allowable power dissipation | Pd max                              | Ta ≤ 85°C                        | 140                              | mW   |

| Operating temperature       | Topr                                |                                  | -40 to +85                       | °C   |

| Storage temperature         | Tstg                                |                                  | -50 to +125                      | °C   |

|                             |                                     |                                  |                                  |      |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

# Allowable Operating Ranges at $Ta=25^{\circ}C,\,V_{SS}$ = 0 V

| Parameter                | Symbol              | Conditions                       | Ratings                                    | Unit |

|--------------------------|---------------------|----------------------------------|--------------------------------------------|------|

| Supply voltage           | V <sub>DD</sub>     | V <sub>DD</sub>                  | 4.0 to 11.0                                | V    |

| Input high level voltage | V <sub>IH</sub> (1) | CL, DI, CE                       | 0.3 V <sub>DD</sub> + 1 to V <sub>DD</sub> | V    |

| input high level voltage | V <sub>IH</sub> (2) | S                                | 0.8 V <sub>DD</sub> to V <sub>DD</sub>     | V    |

| Input low level voltage  | V <sub>IL</sub> (1) | CL, DI, CE                       | $V_{SS}$ to 0.2 $V_{DD}$                   | V    |

|                          | V <sub>IL</sub> (2) | S                                | $V_{SS}$ to 0.2 $V_{DD}$                   | V    |

| Input voltage amplitude  | V <sub>IN</sub>     | L10dBIN, L2dBIN, R10dBIN, R2dBIN | V <sub>SS</sub> to V <sub>DD</sub>         | Vp-p |

| Input pulse width        | t <sub>øW</sub>     | CL                               | 1 or longer                                | μs   |

| Setup time               | t <sub>set up</sub> | CL, DI, CE                       | 1 or longer                                | μs   |

| Hold time                | t <sub>hold</sub>   | CL, DI, CE                       | 1 or longer                                | μs   |

| Operating frequency      | fop                 | CL                               | Up to 500                                  | kHz  |

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{SS}$ = 0 V

| Parameter                                            | Symbol               | Conditions                                                                                                         | min  | typ   | max  | Unit |

|------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

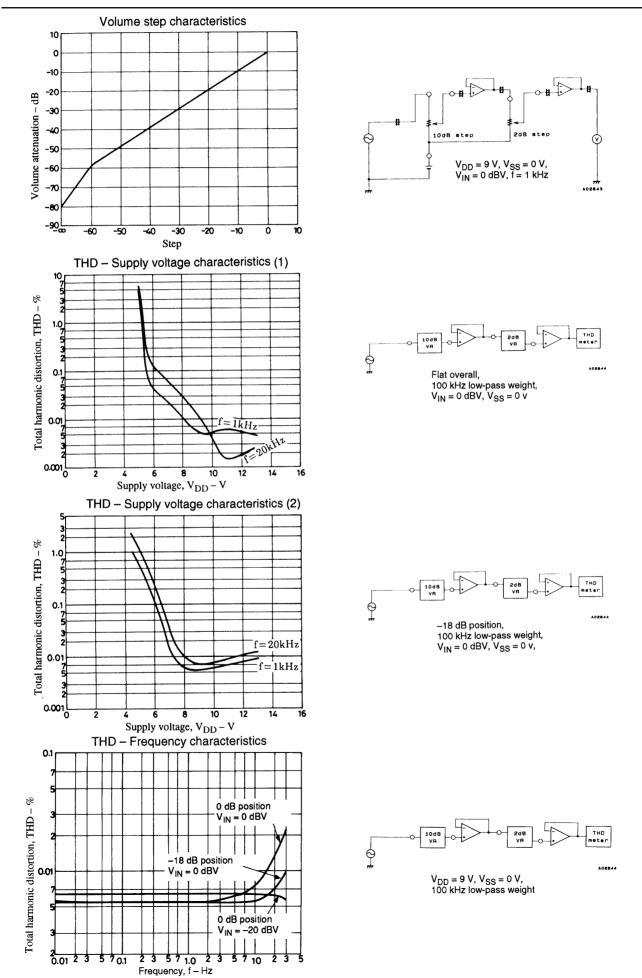

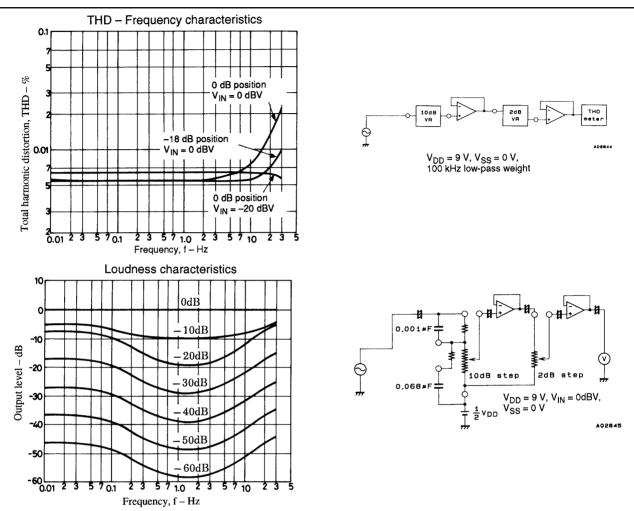

| Total harmonic distortion                            | THD (1)              | $V_{IN}$ = 1 Vrms, f = 1 kHz, all settings flat overall,<br>V <sub>DD</sub> = 9 V                                  |      | 0.006 |      | %    |

| rotal narmonic distortion                            | THD (2)              | $V_{IN}$ = 1 Vrms, f = 20 kHz, all settings flat overall,<br>V <sub>DD</sub> = 9 V                                 |      | 0.015 |      | %    |

| Crosstalk                                            | СТ                   | $V_{IN}$ = 1 Vrms, f = 20 kHz, all settings flat overall,<br>Rg = 1 kΩ                                             |      | 85    |      | dB   |

| Output at maximum attenuation                        | V <sub>O</sub> min   | $V_{IN}$ = 1 Vrms, f = 20 kHz, volume setting: -∞, with a 470 µF capacitor between L/R Vref and V <sub>SS</sub>    |      | -80   |      | dB   |

| Total resistance                                     | R <sub>VOL</sub> (1) | 10 dB steps                                                                                                        | 28.2 | 47    | 65.8 | kΩ   |

|                                                      | R <sub>VOL</sub> (2) | 2 dB steps                                                                                                         | 12   | 20    | 28   | kΩ   |

| Output off leakage current                           | loff                 | L10dBIN, R10dBIN, LCT1, L2dBIN, R2dBIN, RCT1,<br>L10dBOUT, R10dBOUT, LCT2, L2dBOUT, R2dBOUT,<br>RCT2, LVref, RVref | -10  |       | +10  | μΑ   |

| Input high level current                             | IIH                  | VI = V <sub>DD</sub> (CL, CE and DI pins)                                                                          |      |       | 10   | μA   |

| Input low level current                              | Ι <sub>ΙL</sub>      | VI = V <sub>SS</sub> (CL, CE and DI pins)                                                                          | -10  |       |      | μA   |

| Output noise voltage                                 | V <sub>N</sub>       | All settings flat overall (IHF-A), $V_{DD}$ = 9 V, Rg = 1 k $\Omega$                                               |      | 2     | 10   | μV   |

| Current drain                                        | I <sub>DD</sub>      | $V_{DD} - V_{SS} = 11 V$                                                                                           |      |       | 1    | mA   |

| Analog switch on resistance<br>(Design target value) | R <sub>ON</sub>      | CT1                                                                                                                | 180  | 300   | 420  | Ω    |

|                                                      |                      | For use between CT2 and Vref                                                                                       | 90   | 150   | 210  | Ω    |

|                                                      |                      | 0 dB, -∞                                                                                                           | 0.6  | 1.0   | 1.4  | kΩ   |

|                                                      |                      | Other than the above                                                                                               | 6.0  | 10.0  | 14.0 | kΩ   |

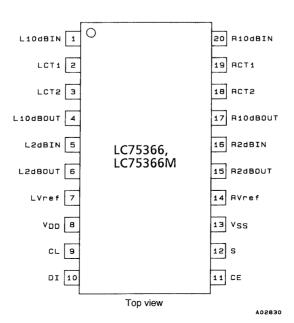

## **Pin Assignment**

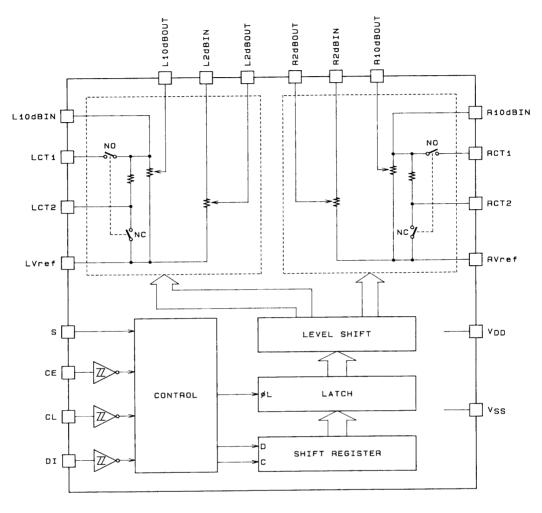

## **Equivalent Circuit Block Diagram**

A02831

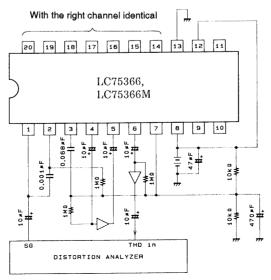

## **Test Circuits**

1. Total harmonic distortion

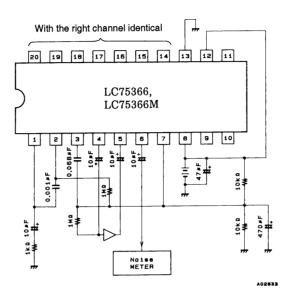

## 2. Output noise voltage

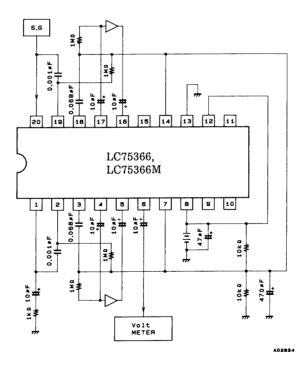

#### 3. Crosstalk

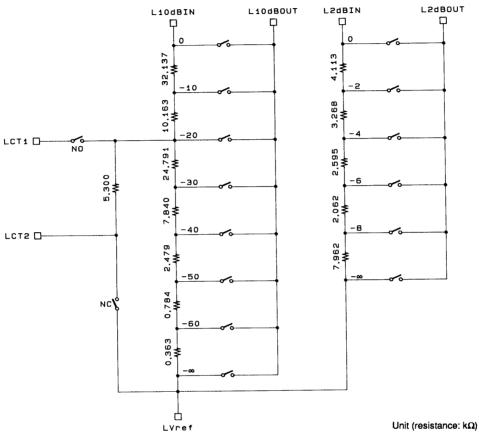

# **Volume Block Equivalent Circuit**

The right channel is identical.

A02835

## **Pin Functions**

| Pin No. | Symbol          | Function                                                                                                                                                                                                  | Note                 |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1       | L10dBIN         | Input pins for the 10 dB step attenuator. Must be driven from a low impedance.                                                                                                                            |                      |

| 20      | R10dBIN         |                                                                                                                                                                                                           | VSS # # A02836       |

| 2       | LCT1            |                                                                                                                                                                                                           |                      |

| 3       | LCT2            | Loudness connections. Connect a high band compensation capacitor between                                                                                                                                  |                      |

| 19      | RCT1            | <ul> <li>CT1 and 10dBIN and connect a low band compensation capacitor between CT2<br/>and Vref.</li> </ul>                                                                                                |                      |

| 18      | RCT2            |                                                                                                                                                                                                           |                      |

| 4       | L10dBOUT        | Output pins for the 10 dB step attenuator. These outputs must be received by a                                                                                                                            |                      |

| 17      | R10dBOUT        | load of about 1 MΩ.                                                                                                                                                                                       | ₩ ₩ VSS 402837       |

| 5       | L2dBIN          |                                                                                                                                                                                                           |                      |

| 16      | R2dBIN          | Input pins for the 2 dB step attenuator. Must be driven from a low impedance.                                                                                                                             | □                    |

| 6       | L2dBOUT         | Output pins for the 2 dB step attenuator. These outputs must be received by a                                                                                                                             |                      |

| 15      | R2dBOUT         | load of about 1 MΩ.                                                                                                                                                                                       | ₩ ₩ ₩ VSS            |

| 7       | LVref           | Volume circuit common pins. The impedance of the pattern connected to these pins should be kept as low as possible.<br>Since the capacitors between Vref and V <sub>SS</sub> form the residual resistance |                      |

| 14      | RVref           | components when the volume is cut, adequate care must be taken in determining the value of these capacitors.                                                                                              | Vref<br>ZZ<br>A02838 |

| 12      | S               | Pin that selects the address code in the data format. Data will be accepted for an address code of 88 when this pin is tied to $V_{DD}$ , and for an address code of 89 when tied to $V_{SS}$ .           | VDD                  |

| 9       | CL              |                                                                                                                                                                                                           | - <del></del> VDD    |

| 10      | DI              | Serial data and clock inputs for control                                                                                                                                                                  | × ×                  |

| 11      | CE              | Chip enable. The internally latched data is written and the analog switches operate when this pin goes from high to low. Data transfer is enabled when this pin is at the high level.                     | VSS A02840           |

| 8       | V <sub>DD</sub> |                                                                                                                                                                                                           |                      |

| 13      | V <sub>SS</sub> | <ul> <li>These pins must be connected to the power supply.</li> </ul>                                                                                                                                     |                      |

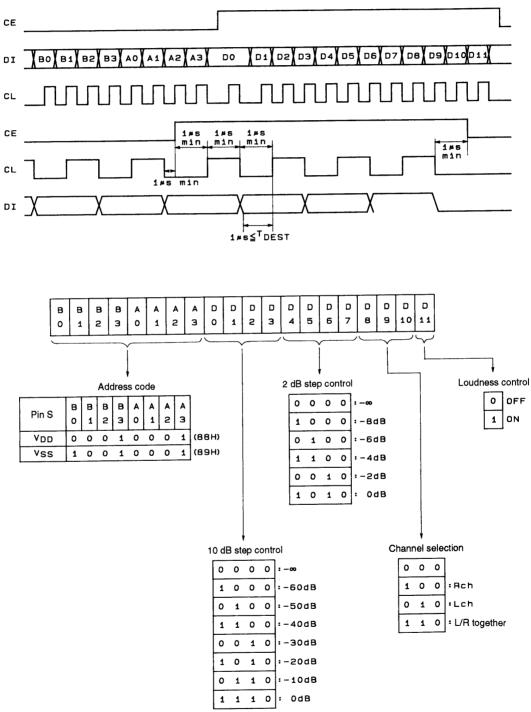

#### **Control System Timing and Data Format**

Apply the stipulated serial data to the CE, CL and DI pins to control the LC75366 and LC75366M. The data consists of 20 bits, of which 8 bits are the address and 12 bits are control data.

A02841

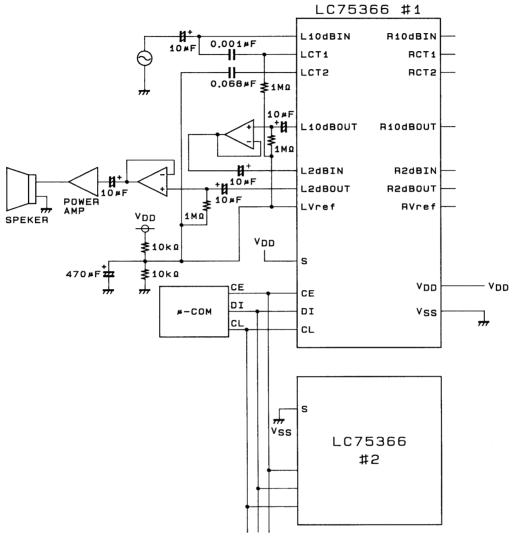

# Sample Application Circuit

A02842

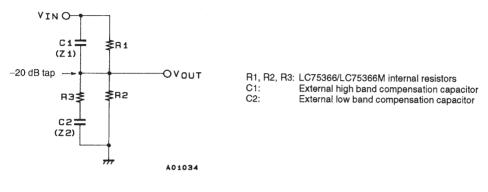

#### Loudness Function External Circuit Constant Calculation Example

First, refer to the LC75366 and LC75366M 10 dB step internal equivalent circuit shown on page 5. Figure 1 below shows this circuit simplified with the external components used for the loudness function connected for this calculation. The sample calculation below uses this diagram to acquire a 5 dB boost at f = 100 Hz.

(f = 100 Hz, 5 dB boost) Let R and C in Figure 1 be: R1 = R2 = 10 k $\Omega$ R3 = 1 k $\Omega$ C1 = Z1, C2 = Z2 Then:

$$V_{OUT} = \frac{\frac{R2 (R3 + Z2)}{R2 + R3 + Z2}}{(at = 1 \text{ kHz})} = -20 \text{ dB}$$

$$(at = 1 \text{ kHz}) \frac{\frac{R1 \cdot Z1}{R1 + Z1} + \frac{R2 (R3 + Z2)}{R2 + R3 + Z2}}{\frac{R2 (R3 + 10 \cdot Z2)}{R2 + R3 + 10 \cdot Z2}} = -15 \text{ dB}$$

$$(at = 100 \text{ Hz}) \frac{\frac{R1 \cdot 10 \cdot Z1}{R1 + 10 \cdot Z1} + \frac{R2 (R3 + 10 \cdot Z2)}{R2 + R3 + 10 \cdot Z2}}{R2 + R3 + 10 \cdot Z2} = -15 \text{ dB}$$

Solving the above equations gives:

$Z1 \neq 178.3 \text{ k}\Omega$  and  $Z2 = 176 \Omega$

Therefore, under such conditions where f = 1 kHz, specifications may be satisfied if C (capacitor) having these impedances is supplied externally.

The result is that C1 = 893 pF and  $C2 = 0.9 \mu$ F.

#### **Usage Notes**

- 1. The states of the internal analog switches will be indeterminate when power is first applied. Muting should be applied externally until control data has been transferred and stored.

- 2. The signal lines for the CL, DI and CE pins should either be covered by the pattern ground or be formed from shielded cable to prevent the high-frequency digital signals transmitted over these lines from entering the analog system.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 1997. Specifications and information herein are subject to change without notice.