CMOS LSI

SANYO

No. ※ 4278

LC89560

Error Correction and ADPCM Decoder for CD-I and CD-ROM XA Applications

Preliminary

### **OVERVIEW**

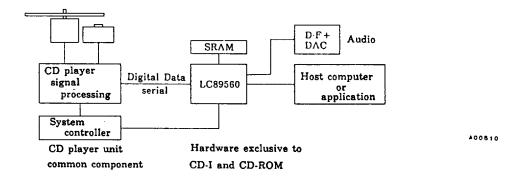

The LC89560 is an error-correction and ADPCM decoder for CD-I and CD-ROM applications. It combines the functionality of the earlier LC8951 and LC8955 devices into one chip. It also includes on-board erasure correction RAM, and support for connection to 64 to 512 Kbits of external RAM. (The ADPCM decoder function is not supported with 64 Kbits of external RAM option.)

### **FEATURES**

- Support for CD-ROM (Mode 1), CD-I and CD-ROM XA (Mode 2, Forms 1 and 2)

- Incorporates circuitry required for CD-I and CD-ROM onto a single chip

- Error-detection and correction implemented in hardware

- Real-time error correction that does not require communications over a host interface bus

- High transfer rate of up to 2.3 Mbytes/s (18.4 Mbits/s)

- Multiple block buffering allows operation even with slow hosts

- Erasure correction gives twice the error-correction capability

- · Command status FIFO on the host interface

- · Status FIFO on the host interface

- · ADPCM decoder circuits on-chip

- · Sub-code interface on-chip

.dzsc.com

- External SRAM can be accessed directly from a SUB-CPU

- On-chip 8 Kbit RAM for erasure correction

- CMOS process, single 5 V supply

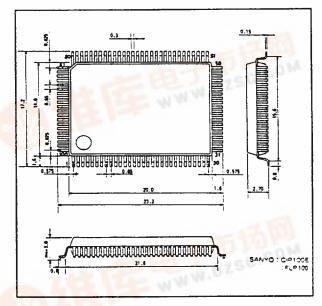

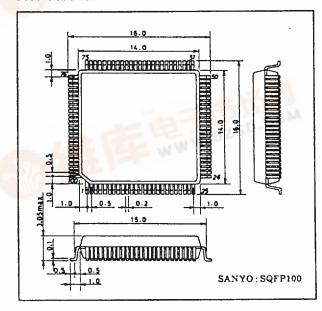

- 100-pin flat package (SQFP100, QIP100E)

### PACKAGE DIMENSIONS

Unit: mm

#### 3151-QFP100E

#### 3181-SQFP100

Specifications and information herein are subject to change without notice.

## CD-I/CD-ROM SYSTEM BLOCK DIAGRAM

## **BLOCK DIAGRAM**

400778

# PIN DESCRIPTION (QIP100E)

The letter 'Z' as the first character of a name indicates negative logic.

| Number | Name            | l/O | Description                                                           |  |  |  |  |  |

|--------|-----------------|-----|-----------------------------------------------------------------------|--|--|--|--|--|

| 1      | SA0             | 1   | Host register select                                                  |  |  |  |  |  |

| 2      | ZAPCS           | , 1 | Host register chip select                                             |  |  |  |  |  |

| 3      | BUSY            | 0   | Busy signal. This signal is active when the host writes ADPCM data.   |  |  |  |  |  |

| 4      | INTH            | 0   | Interrupt to host                                                     |  |  |  |  |  |

| 5      | HDE             | 0   | Erasure flag output. This pin has an internal pull-up resistor.       |  |  |  |  |  |

| 6      | HD7             | 1/0 |                                                                       |  |  |  |  |  |

| 7      | HD6             | 1/0 |                                                                       |  |  |  |  |  |

| 8      | HD5             | vo  |                                                                       |  |  |  |  |  |

| 9      | HD4             | vo  | Host interface data. These pins have internal pull-up resistors.      |  |  |  |  |  |

| 10     | HD3             | vo  | These interface data. These pins have internal purity resource.       |  |  |  |  |  |

| 11     | HD2             | 1/0 |                                                                       |  |  |  |  |  |

| 12     | HD1             | 10  |                                                                       |  |  |  |  |  |

| 13     | HD0             | 10  |                                                                       |  |  |  |  |  |

| 14     | Vss             | -   | Ground                                                                |  |  |  |  |  |

| 15     | ZEOP            | 0   | End-of-process signal. This signal is used during DMA data transfer.  |  |  |  |  |  |

| 16     | MSTEMON         | 0   | Audio block monitor pin                                               |  |  |  |  |  |

| 17     | MEMPHAS         | 0   | Addit Glock Holling pill                                              |  |  |  |  |  |

| 18     | OLRCK           | 0   |                                                                       |  |  |  |  |  |

| 19     | ODATA           | 0   | D/A converter outputs                                                 |  |  |  |  |  |

| 20     | OBCLK           | 0   |                                                                       |  |  |  |  |  |

| 21     | SOC1            | 0   | Output pin for LC7883K                                                |  |  |  |  |  |

| 22     | DACCK           | 0   | Clock output. 16.9344 MHz for levels A and B, 8.4672 MHz for level C. |  |  |  |  |  |

| 23     | V <sub>SS</sub> |     | Ground                                                                |  |  |  |  |  |

| 24     | RA0             | 0   |                                                                       |  |  |  |  |  |

| 25     | RA1             | 0   |                                                                       |  |  |  |  |  |

| 26     | RA2             | 0   |                                                                       |  |  |  |  |  |

| 27     | RA3             | 0   |                                                                       |  |  |  |  |  |

| 28     | RA4             | 0   |                                                                       |  |  |  |  |  |

| 29     | RA5             | 0   |                                                                       |  |  |  |  |  |

| 30     | RA6             | 0   | RAM address lines                                                     |  |  |  |  |  |

| 31     | RA7             | 0   |                                                                       |  |  |  |  |  |

| 32     | RA8             | 0   |                                                                       |  |  |  |  |  |

| 33     | RA9             | 0   |                                                                       |  |  |  |  |  |

| 34     | RA10            | 0   |                                                                       |  |  |  |  |  |

| 35     | RA11            | 0   |                                                                       |  |  |  |  |  |

| 36     | RA12            | 0   |                                                                       |  |  |  |  |  |

| Number | Name            | VO    | Description                                                               |  |  |  |

|--------|-----------------|-------|---------------------------------------------------------------------------|--|--|--|

| 37     | RA13            | 0     |                                                                           |  |  |  |

| 38     | RA14            | 0     | RAM address lines                                                         |  |  |  |

| 39     | RA15            | 0     |                                                                           |  |  |  |

| 40     | V <sub>SS</sub> | _     | Ground                                                                    |  |  |  |

| 41     | V <sub>DO</sub> | -     | 5 V supply                                                                |  |  |  |

| 42     | ZRWE            | 0     | RAM write pin                                                             |  |  |  |

| 43     | ZROE            | 0     | RAM read pin                                                              |  |  |  |

| 44     | ERA             | νο    | Erasure flag RAM data input/output                                        |  |  |  |

| 45     | 100             | VO    |                                                                           |  |  |  |

| 46     | IO1             | VO    |                                                                           |  |  |  |

| 47     | 102             | VO    |                                                                           |  |  |  |

| 48     | 103             | . 1/0 | Data buffer RAM input/output. These pins have internal pull-up resistors. |  |  |  |

| 49     | 104             | VO    | Sold Surial Hipotocipal Those pine hate internal pen op received.         |  |  |  |

| 50     | 105             | vo    |                                                                           |  |  |  |

| 51     | 106             | vo    |                                                                           |  |  |  |

| 52     | 107             | ю     |                                                                           |  |  |  |

| 53     | V <sub>SS</sub> | -     | Ground                                                                    |  |  |  |

| 54     | EXTAL           | ţ.    | Crystal oscillator                                                        |  |  |  |

| 55     | XTAL            | 0     | Organia vadinator                                                         |  |  |  |

| 56     | TEST            | 1     | Test pin. Connect to Vss.                                                 |  |  |  |

| 57     | V <sub>SS</sub> | -     | Ground                                                                    |  |  |  |

| 58     | мск             | 0     |                                                                           |  |  |  |

| 59     | LRCK            | 1     |                                                                           |  |  |  |

| 60     | SDATA           | 1     | Connections to CD-DSP                                                     |  |  |  |

| 61     | BCK             | 1     |                                                                           |  |  |  |

| 62     | C2PO            | l     |                                                                           |  |  |  |

| 63     | WFCK            | l     |                                                                           |  |  |  |

| 64     | EXCK            | 0     | Sub-code inputs and outputs                                               |  |  |  |

| 65     | SBSO            | ı     | See seed impais and darpois                                               |  |  |  |

| 66     | SCOR            | ı     |                                                                           |  |  |  |

| 67     | CEMPHAS         | 0     | Connect to CD-DSP emphasis pin.                                           |  |  |  |

| 68     | ZRESET          | ī     | Reset pin. Hold LOW for 1 µs.                                             |  |  |  |

| 69     | SCPUCNT         | ı     | SUB-PCU interface select                                                  |  |  |  |

| 70     | DO              | 1/0   |                                                                           |  |  |  |

| 71     | D1              | 1/0   |                                                                           |  |  |  |

| 72     | D2              | ľO    | SUB-CPU data signal pins. These pins have internal pull-up resistors.     |  |  |  |

| 73     | D3              | ľO    |                                                                           |  |  |  |

| 74     | D4              | 1/0   |                                                                           |  |  |  |

| Number | Name            | ľO   | Description                                                                                |  |  |  |

|--------|-----------------|------|--------------------------------------------------------------------------------------------|--|--|--|

| 75     | D5              | νo   |                                                                                            |  |  |  |

| 76     | D6              | , no | SUB-CPU data signal pins. These pins have internal pull-up resistors.                      |  |  |  |

| 77     | D7              | vo   |                                                                                            |  |  |  |

| 78     | V <sub>SS</sub> | -    | Ground                                                                                     |  |  |  |

| 79     | SUA0            | 1    |                                                                                            |  |  |  |

| 80     | SUA1            | ı    |                                                                                            |  |  |  |

| 81     | SUA2            | ı    | SUB-CPU register select address                                                            |  |  |  |

| 82     | · SUA3          | l    |                                                                                            |  |  |  |

| 83     | SUA4            | ı    |                                                                                            |  |  |  |

| 84     | NC              | _    | No connection                                                                              |  |  |  |

| 85     | ZINT            | 0    | SUB-CPU interrupt signal. This is an open-drain output, with an internal pull-up resistor. |  |  |  |

| 86     | RS (ALE)        | ı    | Internal register set pin                                                                  |  |  |  |

| 87     | ZRD             | 1    | SUB-CPU read signal                                                                        |  |  |  |

| 88     | ZWR             | ı    | SUB-CPU write signal                                                                       |  |  |  |

| 89     | V <sub>DO</sub> | -    | 5 V supply                                                                                 |  |  |  |

| 90     | Vss             | -    | Ground                                                                                     |  |  |  |

| 91     | zcs             | 0    | SUB-CPU chip select signal                                                                 |  |  |  |

| 92     | ZENABLE         | Į.   | Chip select from host                                                                      |  |  |  |

| 93     | SELDRO          | 1    | DRQ/WAIT select                                                                            |  |  |  |

| 94     | ZWAIT/DRQ       | 0    | DRO/ZWAIT output                                                                           |  |  |  |

| 95     | ZDTEN           | 0    | Data enable                                                                                |  |  |  |

| 96     | ZSTEN           | 0    | Status enable                                                                              |  |  |  |

| 97     | ZHWR            | 1    | Host data write signal                                                                     |  |  |  |

| 98     | ZHRD            | ı    | Host data read signal                                                                      |  |  |  |

| 99     | ZCMD            | 1    | Host data/command signal select                                                            |  |  |  |

| 100    | SA1             | ı    | Audio block register select                                                                |  |  |  |

# PIN DESCRIPTION (SQFP100)

The letter 'Z' as the first character of a name indicates negative logic.

| Number | Name | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | INTH | 0   | interrupt to host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 2      | HDE  | 0   | Erasure flag output. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 3      | HD7  | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 4      | HD6  | vo  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 5      | HD5  | vo  | Il a list of the last of the l |  |  |  |  |

| 6      | HD4  | VO  | Host interface data. These pins have internal pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 7      | HD3  | lο  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 8      | HD2  | vo  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Number | Name              | ľO. | Description                                                               |  |  |  |

|--------|-------------------|-----|---------------------------------------------------------------------------|--|--|--|

| 9      | HD1               | VO  | Heat interfere date. There give have internal culture recistors           |  |  |  |

| 10     | HD0               | VO  | Host interface data. These pins have internal pull-up resistors.          |  |  |  |

| 11     | V <sub>S</sub> \$ | -   | Ground                                                                    |  |  |  |

| 12     | ZEOP              | 0   | End-of-process signal. This signal is used during DMA data transfer.      |  |  |  |

| 13     | MSTEMON           | 0   | Audio block monitor pin                                                   |  |  |  |

| 14     | MEMPHAS           | 0   | Audio block monitor piri                                                  |  |  |  |

| 15     | OLRCK             | 0   |                                                                           |  |  |  |

| 16     | ODATA             | 0   | D/A converter outputs                                                     |  |  |  |

| 17     | OBCLK             | 0   |                                                                           |  |  |  |

| 18     | SOCI              | 0   | Output pin for LC7883K                                                    |  |  |  |

| 19     | DACCK             | 0   | Clock output. 16.9344 MHz for levels A and B, 8.4672 MHz for level C.     |  |  |  |

| 20     | V <sub>SS</sub>   | -   | Ground                                                                    |  |  |  |

| 21     | RA0               | 0   | _                                                                         |  |  |  |

| 22     | RA1               | 0   |                                                                           |  |  |  |

| 23     | RA2               | 0   |                                                                           |  |  |  |

| 24     | RA3               | 0   |                                                                           |  |  |  |

| 25     | RA4               | 0   |                                                                           |  |  |  |

| 26     | RA5               | 0   |                                                                           |  |  |  |

| 27     | RA6               | 0   |                                                                           |  |  |  |

| 28     | RA7               | 0   | RAM address lines                                                         |  |  |  |

| 29     | RA8               | 0   |                                                                           |  |  |  |

| 30     | RA9               | 0   | <u>.</u>                                                                  |  |  |  |

| 31     | RA10              | 0   |                                                                           |  |  |  |

| 32     | RA11              | 0   |                                                                           |  |  |  |

| 33     | RA12              | 0   |                                                                           |  |  |  |

| 34     | RA13              | 0   |                                                                           |  |  |  |

| 35     | RA14              | 0   | <u> </u>                                                                  |  |  |  |

| 36     | RA15              | 0   |                                                                           |  |  |  |

| 37     | ZRWE              | 0   | RAM write pin                                                             |  |  |  |

| 38     | ZROE              | 0   | RAM read pin                                                              |  |  |  |

| 39     | ERA               | vo  | Erasure flag RAM data input/output                                        |  |  |  |

| 40     | V <sub>SS</sub>   | _   | Ground                                                                    |  |  |  |

| 41     | V <sub>00</sub>   | -   | 5 V supply                                                                |  |  |  |

| 42     | 100               | VO  |                                                                           |  |  |  |

| 43     | 101               | VO  |                                                                           |  |  |  |

| 44     | 102               | ιo  | Data buffer RAM input/output. These pins have internal pull-up resistors. |  |  |  |

| 45     | 103               | Ю   | ·                                                                         |  |  |  |

| 46     | 104               | vo  |                                                                           |  |  |  |

| Number | Name            | ľO  | Description                                                                                |  |  |  |  |  |

|--------|-----------------|-----|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| 47     | 105             | 1/0 |                                                                                            |  |  |  |  |  |

| 48     | 106             | 1/0 | Data buffer RAM input/output. These pins have internal pull-up resistors.                  |  |  |  |  |  |

| 49     | 107             | 1/0 |                                                                                            |  |  |  |  |  |

| 50     | Vss             | -   | Ground                                                                                     |  |  |  |  |  |

| 51     | EXTAL           | I   | Cantal assillates                                                                          |  |  |  |  |  |

| 52     | XTAL            | 0   | Crystal oscillator                                                                         |  |  |  |  |  |

| 53     | TEST            | ı   | Test pin. Connect to V <sub>SS</sub> .                                                     |  |  |  |  |  |

| 54     | Vss             | -   | Ground                                                                                     |  |  |  |  |  |

| 55     | MCK             | 0   |                                                                                            |  |  |  |  |  |

| 56     | LRCK            | ı   |                                                                                            |  |  |  |  |  |

| 57     | SDATA           | ı   | Connections to CD-DSP                                                                      |  |  |  |  |  |

| 58     | вск             | ı   |                                                                                            |  |  |  |  |  |

| 59     | C2PO            |     |                                                                                            |  |  |  |  |  |

| 60     | WFCK            | ı   |                                                                                            |  |  |  |  |  |

| 61     | EXCK            | 0   | 2 hours and a second                                                                       |  |  |  |  |  |

| 62     | SBSO            | 1   | Sub-code inputs and outputs                                                                |  |  |  |  |  |

| 63     | SCOR            | 1   |                                                                                            |  |  |  |  |  |

| 64     | CEMPHAS         | 0   | Connect to CD-DSP emphasis pin                                                             |  |  |  |  |  |

| 65     | ZRESET          | 1   | Reset pin. Hold LOW for 1 µs.                                                              |  |  |  |  |  |

| 66     | SCPUCNT         | ı   | SUB-CPU interface select                                                                   |  |  |  |  |  |

| 67     | DO              | ľO  |                                                                                            |  |  |  |  |  |

| 68     | D1              | VO. |                                                                                            |  |  |  |  |  |

| 69     | D2              | VO  |                                                                                            |  |  |  |  |  |

| 70     | D3              | 10  |                                                                                            |  |  |  |  |  |

| 71     | D4              | VO  | SUB-CPU data signal pins. These pins have internal pull-up resistors.                      |  |  |  |  |  |

| 72     | D5              | vo  |                                                                                            |  |  |  |  |  |

| 73     | D6              | 10  |                                                                                            |  |  |  |  |  |

| 74     | D7              | vo  |                                                                                            |  |  |  |  |  |

| 75     | V <sub>SS</sub> | -   | Ground                                                                                     |  |  |  |  |  |

| 76     | SUA0            | ı   |                                                                                            |  |  |  |  |  |

| 77     | SUA1            |     |                                                                                            |  |  |  |  |  |

| 78     | SUA2            | 1   | SUB-CPU register select address                                                            |  |  |  |  |  |

| 79     | SUA3            | 1   |                                                                                            |  |  |  |  |  |

| 80     | SUA4            | 1   |                                                                                            |  |  |  |  |  |

| 81     | ZSWAIT          | 0   | WAIT signal to SUB-CPU                                                                     |  |  |  |  |  |

| 82     | ZINT            | 0   | SUB-CPU interrupt signal. This is an open-drain output, with an internal pull-up resistor. |  |  |  |  |  |

| 83     | RS (ALE)        | 1   | Internal register set pin                                                                  |  |  |  |  |  |

| 84     | ZRD             | 1   | SUB-CPU read signal                                                                        |  |  |  |  |  |

| Number | Name            | VO | Description                                                         |  |  |  |

|--------|-----------------|----|---------------------------------------------------------------------|--|--|--|

| 85     | ZWR             | ı  | SUB-CPU write signal                                                |  |  |  |

| 86     | zcs             | 0  | SUB-CPU chip select seignal                                         |  |  |  |

| 87     | ZENABLE         | ı  | Chip select from host                                               |  |  |  |

| 88     | SELDRO          | ı  | DRQ/WAIT select                                                     |  |  |  |

| 89     | V <sub>OD</sub> | -  | 5 V supply                                                          |  |  |  |

| 90     | Vss             | -  | Ground                                                              |  |  |  |

| 91     | ZWAIT/DRQ       | 0  | DRO/ZWAIT output                                                    |  |  |  |

| 92     | ZDTEN           | 0  | Data enable                                                         |  |  |  |

| 93     | ZSTEN           | 0  | Status enable                                                       |  |  |  |

| 94     | ZHWR            | ı  | Host data write signal                                              |  |  |  |

| 95     | ZHRD            | 1  | Host data read signal                                               |  |  |  |

| 96     | ZCMD            | 1  | Host data/command signal select                                     |  |  |  |

| 97     | SA1             | 1  | Audio block register select                                         |  |  |  |

| 98     | SAO             | 1  | Host register select                                                |  |  |  |

| 99     | ZAPCS           | ı  | Host register chip select                                           |  |  |  |

| 100    | BUSY            | 0  | Busy signal. This signal is active when the host writes ADPCM data. |  |  |  |

# **SPECIFICATIONS**

# **Absolute Maximum Ratings**

$V_{ss} = 0 V$

| Parameter             | Symbol                          | Conditions             | Rating                   | Unit |

|-----------------------|---------------------------------|------------------------|--------------------------|------|

| Supply voltage        | V <sub>DD</sub>                 | T <sub>a</sub> = 25 °C | -0.3 to 7.0              | ٧    |

| input/output voltage  | V <sub>I</sub> , V <sub>O</sub> | T <sub>a</sub> = 25 °C | $-0.3$ to $V_{DO} + 0.3$ | ٧    |

| Power dissipation     | PD                              | T <sub>a</sub> ≤ 70 °C | 350                      | mW   |

| Operating temperature | Topg                            |                        | -30 td 70                | •℃   |

| Storage temperature   | T <sub>stg</sub>                |                        | -55 to 125               | ~℃   |

| Soldering temperature |                                 | 10 s                   | 260                      | ಞ    |

# **Recommended Operating Conditions**

$T_a = -30$  to +70 °C,  $V_{SS} = 0$  V

| Parameter           | Symbol          | Rating |     |                 | Unit  |

|---------------------|-----------------|--------|-----|-----------------|-------|

| raidiletei          |                 | min    | typ | max             | Oille |

| Supply voltage      | V <sub>DD</sub> | 4.5    | 5.0 | 5.5             | ٧     |

| input voltage range | VIN             | 0      | -   | V <sub>DO</sub> | ٧     |

### DC Electrical Characteristics

$V_{SS}$  = 0 V,  $V_{DD}$  = 4.5 to 5.5 V,  $T_a$  = -30 to 70 °C

63E D

| Parameter                 | A                | 0                                                                       |     | Rating |     |      |

|---------------------------|------------------|-------------------------------------------------------------------------|-----|--------|-----|------|

|                           | Symbol           | Condition                                                               | min | typ    | max | Unit |

| HIGH-level input voltage  | V <sub>IH1</sub> | All input pins except                                                   | 2.2 | -      | -   | ٧    |

| LOW-level input voltage   | ViLi             | XTALCK and those in the note.                                           | -   | -      | 0.8 | ٧    |

| HIGH-level input voltage  | V <sub>IH2</sub> |                                                                         | 2.5 | -      | -   | ٧    |

| LOW-level input voltage   | V <sub>IL2</sub> | See note.                                                               | -   | -      | 0.6 | ٧    |

| HIGH-level output voltage | V <sub>OH1</sub> | l <sub>OH1</sub> = -3 mA, all output<br>pins excepting ZTAL and<br>ZINT | 2.4 | -      | -   | ٧    |

| LOW-level output voltage  | V <sub>OL1</sub> | l <sub>OL1</sub> = 3 mA, all output<br>pins excepting ZTAL and<br>ZINT  | -   | -      | 0.4 | v    |

| LOW-level output voltage  | V <sub>OL2</sub> | l <sub>OL2</sub> = 3 mA, ZINT<br>(open-drain with pull-up)              | -   | -      | 0.4 | v    |

| Input leakage current     | l <sub>L</sub>   | V <sub>1</sub> = V <sub>SS</sub> or V <sub>DD</sub> ,<br>all input pins | -25 | -      | 25  | μА   |

| Pull-up resistance        | Rup              | All bus pins, ZINT                                                      | 10  | 20     | 40  | kΩ   |

#### Note

RESET (Schmitt trigger) and all bus pins (ZHRD, ZHWR, ZENABLE, ZCMD, WFCK, SBSO and SCOR)

### **FUNCTIONAL DESCRIPTION**

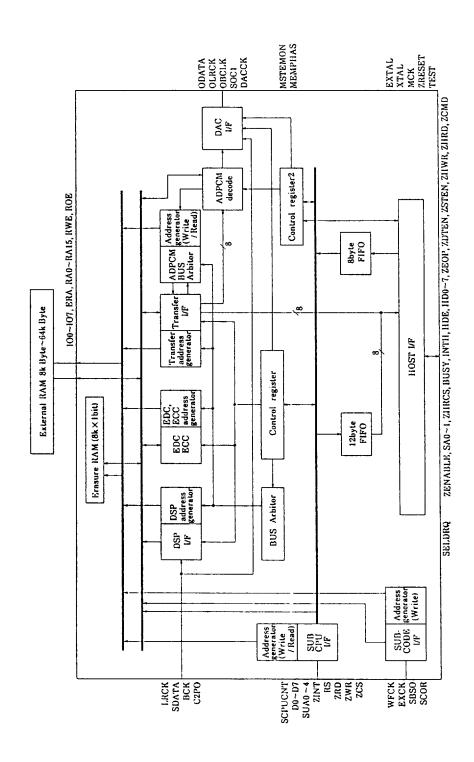

The LC89560 has five main functional blocks. Each is described in the following sections.

# CD Player Interface and Data Input Block

The LC89560 supports three different input data formats, selected by programming the CSEL and LMSEL internal registers.

The internal operation of the device is synchronized to the input data signal on a block-by-block (that is, sector-by-sector) basis. The sync detector circuit operates by detecting patterns in the input data. An additional sync insertion circuit can be used to preserve synchronization. These two synchronization methods can be programmed on or off.

The input data passes through the de-scrambling circuit, and is then written 8 bits at a time into buffer RAM. The C2 pointer (error flag) from the CD player is also written into RAM. If the error correction block uses 128 Kbits or more, the RAM is nine bits wide. However, the C2 pointer can also be omitted—in this case, the RAM need only be eight bits wide. Note that erasure correction cannot be performed if the C2 pointer is omitted.

Data from the CD is written to buffer RAM in its entirety, including the SYNC, header, sub-header and parity (2352 bytes per block).

The LC89560 master clock is output on MCK, thus allowing this clock to be used as the CD LSI clock.

### Error Detection and Correction

Error correction is performed on each block (2352 bytes) after it has been stored in buffer RAM.

The LC89560 is able to perform error correction in real time in hardware. This allows controller software to perform other functions during this time, such as buffering data from the CD or transferring data to the host computer. This ensures that the data transfer rate from the CD is not reduced while corrected data is being sent to the host computer.

The standard error detection and correction technique is supplemented by an erasure correction method using the C2 pointer. This results in very low error rates. The standard error correction can correct one incorrect symbol whereas the erasure correction can correct two incorrect symbols.

The correction algorithm is programmable, allowing the use of a variety of techniques, including repeated correction and QP/PQ correction.

After recovery of the error correction code (ECC), a 32-bit CRC error check is performed using the error detection code (EDC). The header and sub-header are stored into internal registers at this time.

The LC89560 then generates a decoding-completed interrupt to the host microcontroller. The controller reads the header, sub-header, block header address in buffer RAM, and the decoding status from the LC89560.

Also, since the 8 Kbit erasure RAM has been integrated into the chip, the usual external 8 Kbit RAM is not needed.

### Host Interface Block

The data transfer rate to the host computer has been increased to a peak rate of 2.3 Mbytes/s. Up to 60 Kbytes of external buffer RAM can now be supported, allowing up to 26 sectors of data to be buffered. This can be used to implement disk caching.

The host command interface has an 8-byte FIFO for received commands. By activating the ZHWR signal, the host can write up to eight commands at once. When the host writes to the FIFO, the LC89560 generates a command interrupt to the host microcontroller. The command written to the FIFO is not interpreted completely by the LC89560 at this time. To transfer data to the host, the host microcontroller sets the LC89560 registers with the number of bytes to be transferred and the buffer RAM address of the header of the block to be transferred. It then writes to the transfer trigger register. ZDTEN then goes LOW to indicate the start of data transfer to the host. The host repeatedly generates ZHRD pulses while ZDTEN is LOW to read the data. If the host attempts to read data faster than approximately 2.3 Mbytes/s, the LC89560 activates the ZWAIT/DRO signal. The host must hold ZHRD HIGH while ZWAIT/DRQ is LOW. During the transfer of this block. the microcontroller waits for the next transfer-completed interrupt.

DRQ (data request) data transfer can be performed using the SELDRQ pin. This form of data transfer operates rather like a DMA controller in that the host generates ZHRD pulses in response to the data request signal produced by the LC89560.

When the last data byte is read, ZEOP goes active while the read pulse is active. Following that, the ZDTEN signal goes inactive. The transfer-completed interrupt is then generated to inform the microcontroller that data transfer to the host has completed.

The microcontroller can transfer information such as the decoding results and CD-ROM drive status to the host computer by writing to registers in the LC89560. The status register comprises twelve bytes. The microcontroller and the host handshake using the ZSTEN signal. The LC89560 has no knowledge of the contents of these registers.

Since these command and status registers are not interpreted or executed by the LC89560, the meaning of the

data passed through these registers can be defined in any way desired. Thus, CD-ROM applications can be easily designed, and the LC89560 can easily be incorporated into existing systems.

### **Shared Circuits**

The LC89560 performs data decoding and buffering using pipeline processing. Furthermore, writing to buffer RAM, data decoding and transfer of data from buffer RAM to the host can be synchronized and performed simultaneously. As a result, the controlling microcontroller does not need to control access to the buffer RAM in any way.

### **ADPCM Decoder**

Error-corrected ADPCM data (although in actual fact, error correction is not performed) is transferred to the ADPCM decoder under the control of the microcontroller. Transfer is essentially the same as for transfer of data to the host.

More correctly, data is transferred between the SRAM error correction area and the ADPCM data area. The ADPCM decoder then reads the data from the ADPCM data area and initiates audio replay.

The level (A, B, or C) and stereo/mono mode can be determined from the sub-header data. Also, temporarily collected ADPCM data can be replayed to the host.

The LC89560 ADPCM decoder output can be directly connected to the LC7883K eight-times oversampling filter and D/A converter.

CD-DA data can also be specified for output on the audio output pins by programming the internal registers. Digital mute is also provided (for ADPCM replay only.)

### Sub-code Data Interface

Sub-code data can be written to the external RAM by connecting to the sub-code pin of the CD-DSP, thus allowing the microcontroller to read the sub-code values. The Q code contains the CRC check information.

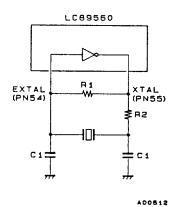

## RECOMMENDED OSCILLATOR CIRCUIT

LC89560  $R1 = 120k\Omega$   $R2 = 47\Omega$  C1 = 30pF  $16.9344 \ MHz \ crystal \ oscillator \ frequency$

Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.