September 2000 Revised February 2001

## SSTV16857

# 14-Bit Register with SSTL-2 Compatible I/O and Reset

#### **General Description**

The SSTV16857 is a 14-bit register designed for use with 184 and 232 pin DDR-I memory modules. The device has a differential input clock, SSTL-2 compatible data inputs and a LVCMOS compatible RESET input. The device has been designed for compliance with the JEDEC DDR module and register specifications.

The device is fabricated on an advanced submicron CMOS process and is designed to operate at power supplies of less than 3.6V's.

#### **Features**

- Compliant with DDR-I registered module specifications

- Operates at 2.5V ± 0.2V V<sub>DD</sub>

- SSTL-2 compatible input and output structure

- Differential SSTL-2 compatible clock inputs

- Low power mode when device is reset

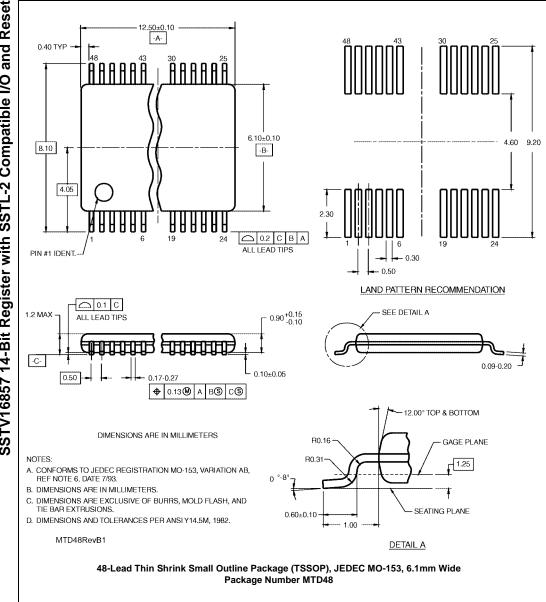

- Industry standard 48 pin TSSOP package

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |  |  |  |  |

|--------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|

| SSTV16857MTD | MTD48          | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |  |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

## Connection Diagram

#### **Pin Descriptions**

| Pin Name                        | Description                                 |

|---------------------------------|---------------------------------------------|

| Q <sub>1</sub> -Q <sub>14</sub> | SSTL-2 Compatible Output                    |

| D <sub>1</sub> -D <sub>14</sub> | SSTL-2 Compatible Inputs                    |

| RESET                           | Asynchronous LVCMOS Reset Input             |

| CK                              | Positive Master Clock Input                 |

| CK                              | Negative Master Clock Input                 |

| V <sub>REF</sub>                | Voltage Reference Pin for SSTL Level Inputs |

| $V_{DDQ}$                       | Power Supply Voltage for Output Signals     |

| $V_{DD}$                        | Power Supply Voltage for Inputs             |

#### **Truth Table**

| RESET | D <sub>n</sub>   | СК               | СК               | Q <sub>n</sub> |

|-------|------------------|------------------|------------------|----------------|

| L     | X or<br>Floating | X or<br>Floating | X or<br>Floating | 7-70           |

| Н     | L                | 1                | $\downarrow$     | 457            |

| Н     | Н                | 1                | <b>1</b>         | Н              |

| H     | X                | L                | Н                | Q <sub>n</sub> |

| - Н ( | X                | Н                | L                | Q <sub>n</sub> |

- L = Logic LOW

- H = Logic HIGH

- X = Don't Care, but not floating unless noted

- ↑ = LOW-to-HIGH Clock Transition

- ↓ = HIGH-to-LOW Clock Transition

## **Functional Description**

The SSTV16857 is a 14-bit register with SSTL-2 compatible inputs and outputs. Input data is captured by the register on the positive edge crossing of the differential clock pair.

When the LV-CMOS RESET signal is asserted LOW, all outputs and internal registers are asynchronously placed into the LOW logic state. In addition, the clock and data differential comparators are disabled for power savings. Output glitches are prevented by disabling the internal registers more quickly than the input comparators. When

RESET is removed, the system designer must insure the clock and data inputs to the device are stable during the rising transition of the RESET signal.

The SSTL-2 data inputs transition based on the value of  $V_{REF}$ .  $V_{REF}$  is a stable system reference used for setting the trip point of the input buffers of the SSTV16857 and other SSTL-2 compatible devices.

The  $\overline{\rm RESET}$  signal is a standard CMOS compatible input and is not referenced to the  $\rm V_{REF}$  signal.

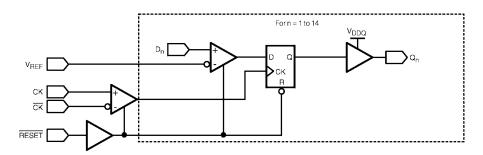

#### **Logic Diagram**

### **Absolute Maximum Ratings**(Note 1)

-0.5V to +3.6V Supply Voltage ( $V_{\rm DDQ}$ ) Supply Voltage (V<sub>DD</sub>) -0.5V to +3.6V-0.5V to +3.6V Reference Voltage (V<sub>REF</sub>) Input Voltage (V<sub>I</sub>) -0.5V to  $V_{DD} + 0.5V$

Output Voltage (VO)

$-0.5 \mbox{V}$  to  $\mbox{V}_{\mbox{DDQ}} + 0.5 \mbox{V}$ Outputs Active (Note 2)

DC Input Diode Current (I<sub>IK</sub>)

$V_I < 0V$  $V_I > V_{DD}$ +50 mA DC Output Diode Current (I<sub>OK</sub>) -50 mA  $V_{O} < 0V$

$V_O > V_{DD}$ +50 mA

DC Output Source/Sink Current

$(I_{OH}/I_{OL})$ ±50 mA

DC V<sub>DD</sub> or Ground Current

per Supply Pin (I<sub>DD</sub> or Ground) ±100 mA Storage Temperature Range (T<sub>stg</sub>)  $-65^{\circ}C$  to  $+150^{\circ}C$

## **Recommended Operating** Conditions (Note 3)

Power Supply (V<sub>DDQ</sub>) 2.3V to 2.7V

Power Supply (V<sub>DD</sub>)

Operating Range V<sub>DDQ</sub> to 2.7V

Reference Supply

1.15 to 1.35  $(V_{REF} = V_{DDQ}/2)$

$V_{REF} \pm 40 \; mV$ Termination Voltage (V<sub>TT</sub>) Input Voltage 0V to V<sub>DD</sub>

Output Voltage (VO)

-50 mA

0V to  $V_{\rm DDQ}$ Output in Active States

Output Current I<sub>OH</sub>/I<sub>OL</sub>

$V_{DD} = 2.3V$  to 2.7V±20 mA 0°C to +70°C

Free Air Operating Temperature (T<sub>A</sub>)

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 2: IO Absolute Maximum Rating must be observed.

Note 3: The  $\overline{\text{RESET}}$  input of the device must be held at  $\text{V}_{\text{DD}}$  or GND to ensure  $\underline{\text{proper}}$  device operation. The differential inputs must not be floating, unless  $\overline{\text{RESET}}$  is asserted LOW.

## DC Electrical Characteristics (2.3 $V \le V_{DD} \le 2.7V$ )

| Symbol             | Parameter                                   | Conditions                                    | V <sub>DD</sub> | Min                     | Max                     | Units  |  |

|--------------------|---------------------------------------------|-----------------------------------------------|-----------------|-------------------------|-------------------------|--------|--|

| Cymbol             | r arameter                                  | (V)                                           |                 |                         | IWIAX                   | Onito  |  |

| $V_{IKL}$          | Input LOW Clamp Voltage                     | I <sub>I</sub> = -18 mA                       | 2.3             |                         | -1.2                    | V      |  |

| V <sub>IKH</sub>   | Input HIGH Clamp Voltage                    | I <sub>I</sub> = +18 mA                       | 2.3             |                         | 3.5                     | V      |  |

| V <sub>IH-AC</sub> | AC HIGH Level Input Voltage                 | Data Inputs                                   |                 | V <sub>REF</sub> +310mV |                         | V      |  |

| V <sub>IL-AC</sub> | AC LOW Level Input Voltage                  | Data Inputs                                   |                 |                         | V <sub>REF</sub> -310mV | V      |  |

| V <sub>IH-DC</sub> | DC HIGH Level Input Voltage                 | Data Inputs                                   |                 | V <sub>REF</sub> +150mV |                         | V      |  |

| V <sub>IL-DC</sub> | DC LOW Level Input Voltage                  | Data Inputs                                   |                 |                         | V <sub>REF</sub> -150mV | V      |  |

| V <sub>IH</sub>    | HIGH Level Input Voltage                    | RESET                                         |                 | 1.7                     |                         | V      |  |

| V <sub>IL</sub>    | LOW Level Input Voltage                     | RESET                                         |                 |                         | 0.7                     | V      |  |

| V <sub>ICR</sub>   | Common Mode Input Voltage Range             | CLK, CLK                                      |                 | 0.97                    | 1.53                    | V      |  |

| V <sub>I(PP)</sub> | Peak to Peak Input Voltage                  | CLK, CLK                                      |                 | 360                     |                         | mV     |  |

| V <sub>OH</sub>    | HIGH Level Output Voltage                   | $I_{OH} = -100 \mu A$                         | 2.3 to 2.7      | V <sub>DD</sub> - 0.2   |                         | V      |  |

|                    |                                             | $I_{OH} = -16 \text{ mA}$                     | 2.3             | 1.95                    |                         | V      |  |

| V <sub>OL</sub>    | LOW Level Output Voltage                    | $I_{OL} = 100 \mu A$                          | 2.3 to 2.7      |                         | 0.2                     | V      |  |

|                    |                                             | I <sub>OL</sub> = 16 mA                       | 2.3             |                         | 0.35                    | V      |  |

| I <sub>I</sub>     | Input Leakage Current $V_I = V_{DD}$ or GND |                                               | 2.7             |                         | ±5.0                    | μΑ     |  |

| I <sub>DD</sub>    | Static Standby                              | $\overline{RESET} = GND,  I_{O} = 0$          |                 |                         | 10                      | μΑ     |  |

|                    | Static Operating                            | $\overline{RESET} = V_{DD}, I_{O} = 0$        | 2.7             |                         |                         |        |  |

|                    |                                             | $V_I = V_{IH(AC)}$ or $V_{IL(AC)}$            |                 |                         | 25                      | mA     |  |

| I <sub>DDD</sub>   | Dynamic Operating Current                   | $\overline{RESET} = V_DD, \; I_O = 0$         |                 |                         |                         |        |  |

|                    | Clock Only                                  | $V_I = V_{IH(AC)}$ or $V_{IL(AC)}$            |                 |                         | 90                      | μA/MHz |  |

|                    |                                             | CK, CK Duty Cycle 50%                         |                 |                         |                         |        |  |

|                    | Dynamic Operating Current                   | $\overline{\text{RESET}} = V_{DD}, I_{O} = 0$ | 2.7             |                         |                         |        |  |

|                    | per Data Input                              | $V_I = V_{IH(AC)}$ or $V_{IL(AC)}$            | 2.7             |                         |                         |        |  |

|                    |                                             | CK, CK Duty Cycle 50%                         |                 |                         | 15                      | μΑ/MHz |  |

|                    |                                             | Data Input = 1/2 Clock                        |                 |                         |                         |        |  |

|                    |                                             | Rate 50% Duty Cycle                           |                 |                         |                         |        |  |

# DC Electrical Characteristics (Continued)

| Symbol          | Parameter                         | Conditions                                          | V <sub>DD</sub><br>(V) | Min | Max | Units |

|-----------------|-----------------------------------|-----------------------------------------------------|------------------------|-----|-----|-------|

| R <sub>OH</sub> | Output HIGH On Resistance         | $I_{OH} = -20 \text{ mA}$                           | 2.3 to 2.7             | 7   | 20  | Ω     |

| R <sub>OL</sub> | Output LOW On Resistance          | I <sub>OL</sub> = 20 mA                             | 2.3 to 2.7             | 7   | 20  | Ω     |

| R <sub>O∆</sub> | R <sub>OH</sub> - R <sub>OL</sub> | $I_{O} = 20 \text{ mA}, T_{A} = 25^{\circ}\text{C}$ | 2.5                    |     | 4   | Ω     |

## **AC Electrical Characteristics** (Note 4)

|                                     |                                                                                                                                 | $T_A = 0$ °C to +70°C, 0                             | Units |     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------|-----|

| Symbol                              | Parameter                                                                                                                       | $\mathbf{V_{DD}} = \mathbf{2.5V} \pm \mathbf{0.2V};$ |       |     |

|                                     |                                                                                                                                 | Min                                                  | Max   |     |

| f <sub>MAX</sub>                    | Maximum Clock Frequency                                                                                                         | 200                                                  |       | MHz |

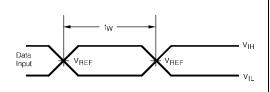

| t <sub>W</sub>                      | Pulse Duration, CK, CK HIGH or LOW (Figure 2)                                                                                   | 2.5                                                  |       | ns  |

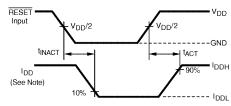

| t <sub>ACT</sub><br>(Note 5)        | Differential Inputs Activation Time, data inputs must be LOW after RESET HIGH (Figure 3)                                        | 22                                                   |       | ns  |

| t <sub>INACT</sub><br>(Note 5)      | Differential Inputs De-activation Time,<br>data and clock inputs must be held at valid levels<br>(not floating) after RESET LOW | 22                                                   |       | ns  |

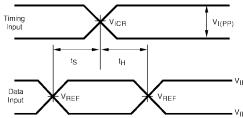

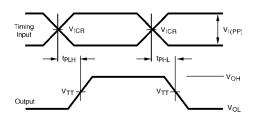

| t <sub>S</sub>                      | Setup Time, Fast Slew Rate (Note 6)(Note 7) (Figure 5) Setup Time, Slow Slew Rate (Note 7)(Note 8) (Figure 5)                   | 0.75<br>0.9                                          |       | ns  |

| t <sub>H</sub>                      | Hold Time, Fast Slew Rate (Note 6)(Note 8) (Figure 5) Hold Time, Slow Slew Rate (Note 7)(Note 8) (Figure 5)                     | 0.75                                                 |       | ns  |

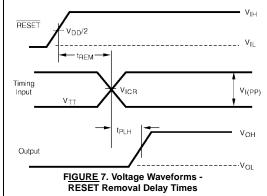

| t <sub>REM</sub>                    | Reset Removal Time (Figure 7)                                                                                                   | 10                                                   |       | ns  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay CLK, CLK to Q <sub>n</sub> (Figure 4)                                                                         | 1.1                                                  | 2.8   | ns  |

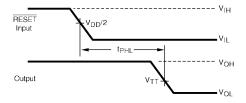

| t <sub>PHL</sub>                    | Propagation Delay RESET to Q <sub>n</sub> (Figure 6)                                                                            |                                                      | 5.0   | ns  |

| t <sub>SK(Pn-Pn)</sub>              | Output to Output Skew                                                                                                           |                                                      | 200   | ps  |

Note 4: Refer to Figure 1 through Figure 7.

Note 5: This parameter is not production tested.

Note 6: For data signal input slew rate  $\geq$  1 V/ns.

Note 7: For data signal input slew rate  $\geq 0.5$  V/ns and < 1 V/ns.

Note 8: For CK,  $\overline{CK}$  signals input slew rates are  $\geq$  1 V/ns.

## Capacitance (Note 9)

| Symbol          | Parameter                  | Min | Тур | Max | Units | Conditions                                                   |

|-----------------|----------------------------|-----|-----|-----|-------|--------------------------------------------------------------|

| C <sub>IN</sub> | Data Pin Input Capacitance | 2.0 |     | 3.0 | pF    | $V_{DD} = 2.5V, V_{I} = V_{REF} \pm 350 \text{ mV}$          |

|                 | CK, CK - Input Capacitance | 2.5 |     | 3.5 | pF    | $V_{DD} = 2.5V, V_{ICR} = 1.25V, V_{I(PP)} = 360 \text{ mV}$ |

|                 | RESET                      | 2.5 |     | 3.5 | pF    | $V_{DD} = 2.5V$ , $V_I = V_{DD}$ to GND                      |

Note 9: T<sub>A</sub> = +25°C, f = 1 MHz, Capacitance is characterized but not tested.

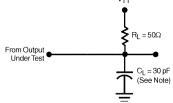

### AC Loading and Waveforms (See Notes A through F below)

Note: C<sub>L</sub> includes probe and jog capacitance

FIGURE 1. AC Test Circuit

Note:  $I_{DD}$  tested with clock and data inputs held at  $V_{DD}$  or GND, and  $I_{O}=0$  mA.

FIGURE 3. Voltage and Current Waveforms Inputs

Active and Inactive Times

FIGURE 5. Voltage Waveforms - Setup and Hold Times

FIGURE 2. Voltage Waveforms - Pulse Duration

FIGURE 4. Voltage Waveforms - Propagation Delay Times

FIGURE 6. Voltage Waveforms - RESET Propagation Delay Times

**Note A:** All input pulses are supplied by generators having the following characteristics:

PRR  $\leq$  10 MHz,  $Z_0=50\Omega,$  input slew rate = 1V/ns  $\pm$  20% (unless otherwise specified).

**Note B**: The outputs are measured one at a time with one transition per measurement.

Note C:  $V_{TT} = V_{REF} = V_{DD}/2$ .

Note D:  $V_{IH} = V_{REF}$  +310 mV (AC voltage levels) for differential inputs.  $V_{IH} = V_{DD}$  for LVCMOS input.

Note E:  $V_{IL} = V_{REF}$  –310 mV (AC voltage levels) for differential inputs.  $V_{IL}$  = GND for LVCMOS input.

**Note F:** Removal time (t<sub>REM</sub>) is tested with one data input held active HIGH. The propagation time from CK to the corresponding output must meet valid timing specifications for the measurement to be accurate.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com