# MAXIM

## 10Gbps 16:1 Serializer

MAX3952

### General Description

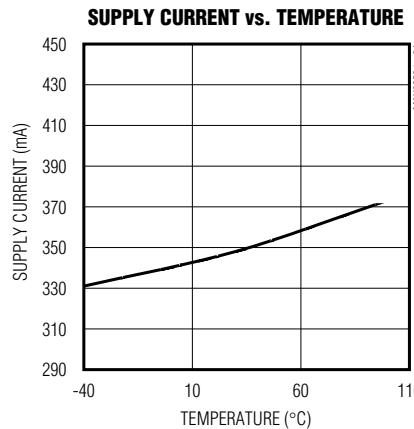

The MAX3952 16:1 serializer is optimized for 10.3Gbps and 9.95Gbps Ethernet applications. A serial clock output is provided for retiming the data at the latch input of the laser driver. Both the high-speed data and clock are CML outputs. The serializer operates from a single +3.3V supply, consuming only 1.15W typical power.

The clock multiplier reference clock frequency can be either 1/16 or 1/64 the serial output clock rate. A FIFO aligns the phase between the parallel clock input and the internally synthesized clock. In addition, a 1/16 counterdirectional clock output (LVDS) is provided for use as the clock signal of the XAUI codec IC or framer.

The operating temperature range is from -40°C to +85°C. The MAX3952 is available in a 10mm × 10mm 68-pin QFN package.

### Applications

10Gbps Ethernet LAN

10Gbps Ethernet WAN

### Features

- ◆ Operates at 9.953Gbps and 10.3125Gbps

- ◆ 16-Bit LVDS Interface

- ◆ Single +3.3V Supply

- ◆ 1.15W Power Dissipation

- ◆ LVDS Source Clock Output

- ◆ Built-In 2<sup>7</sup> - 1 PRBS Pattern Generator

- ◆ Deterministic Jitter: 9ps (max) at 0°C to +85°C

- ◆ Operating Temperature Range: -40°C to +85°C

- ◆ 68-Pin QFN Package (10mm × 10mm)

### Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX3952EGK | -40°C to +85°C | 68 QFN      |

*Pin Configuration appears at end of data sheet.*

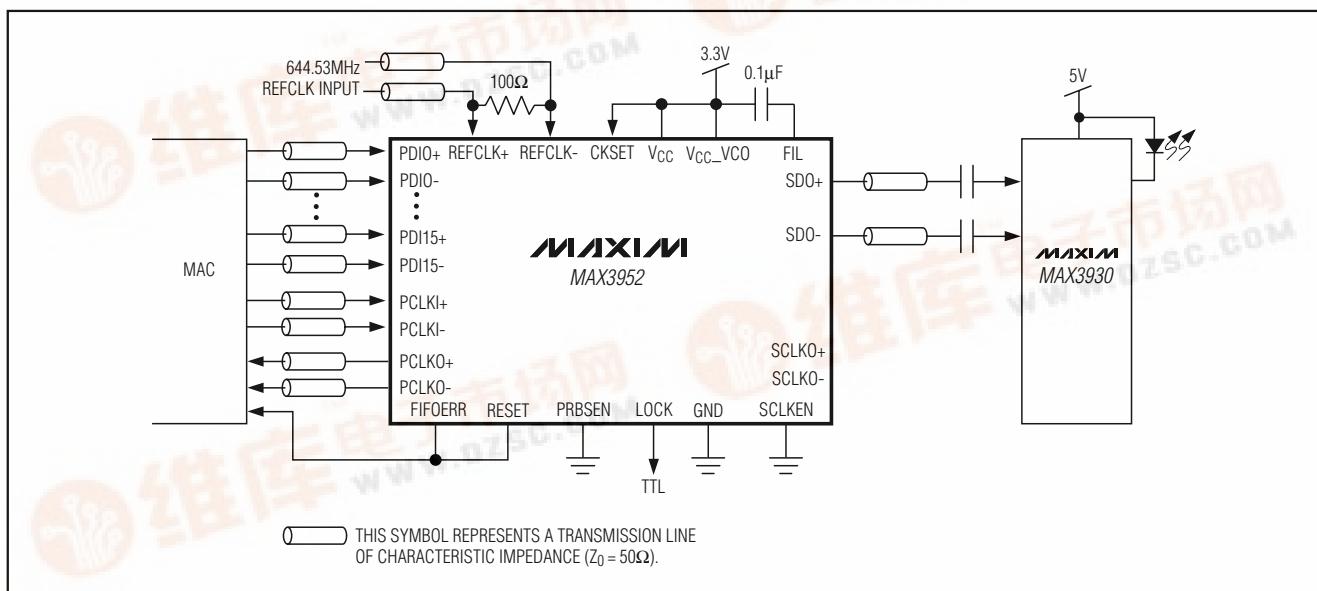

### Typical Application Circuit

# 10Gbps 16:1 Serializer

## ABSOLUTE MAXIMUM RATINGS

Power Supply ( $V_{CC}$ ).....-0.5 to +5V

CML Output Current ( $SDO_{\pm}$ ,  $SCLKO_{\pm}$ ).....22mA

LVDS Input Voltage Levels

( $PDI_{\pm}$ ,  $PCLKI_{\pm}$ ).....-0.5V to ( $V_{CC}$  + 0.5V)

LVDS Output Voltage ( $PCLKO_{\pm}$ ).....-0.5V to ( $V_{CC}$  + 0.5V)

Continuous Power Dissipation ( $T_A = +85^{\circ}C$ )

QFN (derate 30.3mW/ $^{\circ}C$  above  $70^{\circ}C$ ).....2424mW

Operating Temperature Range .....-40 $^{\circ}C$  to +85 $^{\circ}C$

Storage Temperature Range .....-65 $^{\circ}C$  to +160 $^{\circ}C$

Voltage Levels at FIL, RESET, CKSET.....-0.5V to ( $V_{CC}$  + 0.5V)

Lead Temperature (soldering, 10s) .....+300 $^{\circ}C$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

( $V_{CC} = +3V$  to +3.6V,  $T_A = -40^{\circ}C$  to +85 $^{\circ}C$ . Typical values are at  $V_{CC} = +3.3V$ , differential LVDS load = 100 $\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                                                                   | SYMBOL            | CONDITIONS             | MIN   | TYP   | MAX | UNITS    |

|---------------------------------------------------------------------------------------------|-------------------|------------------------|-------|-------|-----|----------|

| Supply Current                                                                              | $I_{CC}$          | (Note 1)               |       | 350   | 500 | mA       |

| <b>LVDS INPUT SPECIFICATIONS (<math>PDI_{\pm}[15...0]</math>, <math>PCLKI_{\pm}</math>)</b> |                   |                        |       |       |     |          |

| Input Voltage Range                                                                         | $V_I$             |                        | 0     | 2400  |     | mV       |

| Differential Input Voltage                                                                  | $IV_{IDL}$        |                        | 100   |       |     | mV       |

| Input Common-Mode Current                                                                   |                   | Input, $V_{OS} = 1.2V$ | 100   |       |     | $\mu A$  |

| Threshold Hysteresis                                                                        |                   |                        | 70    |       |     | mV       |

| Differential Input Impedance                                                                | $R_{IN}$          |                        | 85    | 100   | 115 | $\Omega$ |

| <b>LVDS OUTPUT SPECIFICATIONS (<math>PCLKO_{\pm}</math>)</b>                                |                   |                        |       |       |     |          |

| Output High Voltage                                                                         | $V_{OH}$          |                        |       | 1.475 |     | V        |

| Output Low Voltage                                                                          | $V_{OL}$          |                        | 0.925 |       |     | V        |

| Differential Output Voltage                                                                 | $IV_{ODL}$        |                        | 250   | 400   |     | mV       |

| Change in Magnitude<br>of Differential Outputs<br>for Complementary Inputs                  | $\Delta IV_{ODL}$ |                        |       | 25    |     | mV       |

| Offset Output Voltage                                                                       |                   |                        | 1.125 | 1.275 |     | V        |

| Change in Magnitude<br>of Output Offset Voltage<br>for Complementary States                 | $\Delta IV_{OSL}$ |                        |       | 25    |     | mV       |

| Differential Output Impedance                                                               |                   |                        | 80    | 140   |     | $\Omega$ |

| Output Current                                                                              |                   | Short together         |       | 12    |     | mA       |

|                                                                                             |                   | Short to ground        |       | 40    |     |          |

# 10Gbps 16:1 Serializer

MAX3952

## DC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +3V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ . Typical values are at  $V_{CC} = +3.3V$ , differential LVDS load =  $100\Omega$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

| PARAMETER                                                                       | SYMBOL   | CONDITIONS                   | MIN             | TYP  | MAX             | UNITS      |

|---------------------------------------------------------------------------------|----------|------------------------------|-----------------|------|-----------------|------------|

| <b>CML OUTPUT SPECIFICATIONS (<math>SDO^\pm</math>, <math>SCLKO^\pm</math>)</b> |          |                              |                 |      |                 |            |

| Differential Output                                                             |          | $R_L = 50\Omega$ to $V_{CC}$ | 640             | 800  | 1000            | $mV_{P-P}$ |

| Differential Output Impedance                                                   |          |                              | 85              | 100  | 115             | $\Omega$   |

| Output Common-Mode Voltage                                                      |          | $R_L = 50\Omega$ to $V_{CC}$ | $V_{CC} - 0.2$  |      | V               |            |

| <b>LVTTL SPECIFICATIONS (RESET, FIFO_ERROR, LOCK, PRBSEN)</b>                   |          |                              |                 |      |                 |            |

| LVTTL Input High Voltage                                                        | $V_{IH}$ |                              | 2.0             |      |                 | V          |

| LVTTL Input Low Voltage                                                         | $V_{IL}$ |                              |                 | 0.8  |                 | V          |

| LVTTL Input High Current                                                        | $I_{IH}$ |                              | -28             | 10   |                 | $\mu A$    |

| LVTTL Input Low Current                                                         | $I_{IL}$ |                              | -50             | 10   |                 | $\mu A$    |

| LVTTL Output High Voltage                                                       | $V_{OH}$ | $I_{OH} = 20\mu A$           | 2.4             |      | $V_{CC}$        | V          |

| LVTTL Output Low Voltage                                                        | $V_{OL}$ | $I_{OL} = 1mA$               |                 | 0.4  |                 | V          |

| <b>LVPECL INPUT SPECIFICATIONS (<math>REFCLK^\pm</math>)</b>                    |          |                              |                 |      |                 |            |

| LVPECL Input High Voltage                                                       | $V_{IH}$ |                              | $V_{CC} - 1.16$ |      | $V_{CC} - 0.88$ | V          |

| LVPECL Input Low Voltage                                                        | $V_{IL}$ |                              | $V_{CC} - 1.81$ |      | $V_{CC} - 1.48$ | V          |

| LVPECL Input Bias Voltage                                                       |          |                              | $V_{CC} - 1.3$  |      | V               |            |

| LVPECL Single-Ended Impedance                                                   |          |                              | 1.4             |      |                 | $k\Omega$  |

| LVPECL Differential Input Voltage Swing                                         |          |                              | 300             | 1900 |                 | $mV_{P-P}$ |

**Note 1:** CML outputs AC-coupled to  $100\Omega$  differential load, PRBSEN = GND, and SCLKEN = GND.

# 10Gbps 16:1 Serializer

## AC ELECTRICAL CHARACTERISTICS

( $V_{CC} = +3V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ . Typical values are at  $V_{CC} = +3.3V$ , differential LVDS and CML load =  $100\Omega$ ,  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                                                | SYMBOL                    | CONDITIONS                                                   | MIN                 | TYP  | MAX | UNITS |

|------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------|---------------------|------|-----|-------|

| <b>Tx DATA INPUT SPECIFICATIONS (PDI<math>\pm</math>[15...0], PCLKI<math>\pm</math>)</b> |                           |                                                              |                     |      |     |       |

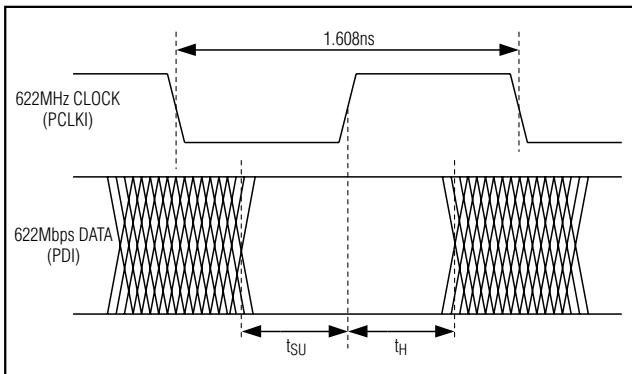

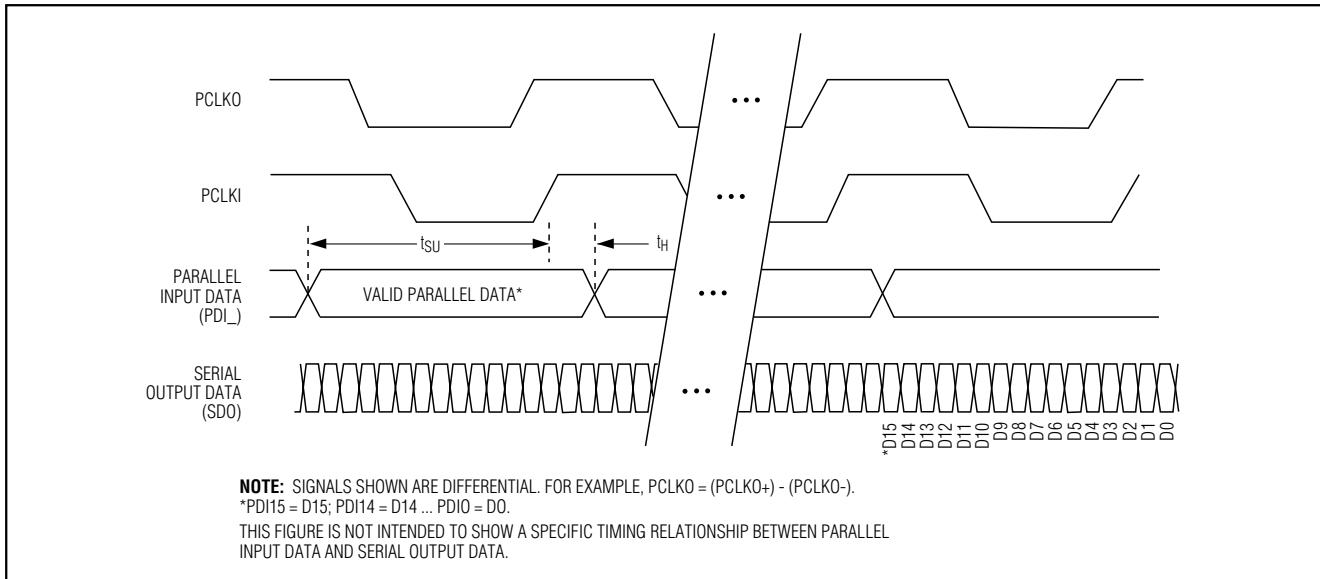

| Parallel Input Setup Time                                                                | $t_{SU}$                  | (Figure 1)                                                   |                     | 200  |     | ps    |

| Parallel Input Hold Time                                                                 | $t_H$                     | (Figure 1)                                                   |                     | 200  |     | ps    |

| <b>Tx SOURCE CLOCK OUTPUT SPECIFICATIONS (PCLKO<math>\pm</math>)</b>                     |                           |                                                              |                     |      |     |       |

| Parallel Clock Output Rise/Fall Time                                                     | $t_r, t_f$                | 20% to 80%                                                   | 100                 | 250  |     | ps    |

| Parallel Clock Output Duty Cycle                                                         |                           |                                                              | 45                  | 55   |     | %     |

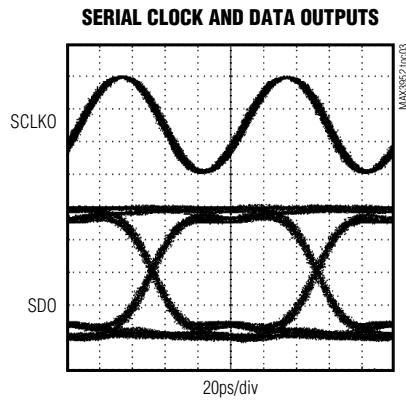

| <b>SERIAL DATA OUTPUT SPECIFICATIONS (SDO<math>\pm</math>, SCLKO<math>\pm</math>)</b>    |                           |                                                              |                     |      |     |       |

| Bit-Error Rate                                                                           |                           |                                                              | $1 \times 10^{-12}$ |      |     |       |

| Serial Data Output Rise/Fall Time                                                        | $t_r, t_f$                | 20% to 80%                                                   |                     | 28   |     | ps    |

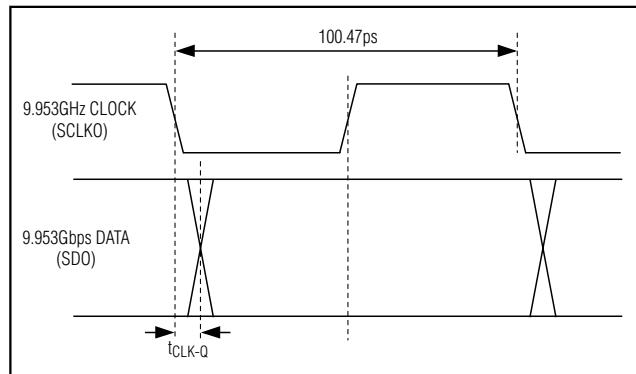

| Serial Output Clock-to-Data Delay                                                        | $t_{CK-Q}$                | (Note 3)                                                     | -15                 | +15  |     | ps    |

| Serial Data or Clock Output Random Jitter                                                | $t_{RJ}$                  |                                                              |                     | 0.9  |     | psRMS |

| Serial Data Output Deterministic Jitter                                                  | $t_{DJ}$                  | 0°C to $+85^\circ C$ (Note 4)                                |                     | 9    |     | psP-P |

|                                                                                          |                           | -40°C to $+85^\circ C$ (Note 4)                              |                     | 15   |     |       |

| Serial Clock or Data Output Return Loss                                                  | $RL = -20\log_{10}S_{22}$ | 100kHz to 10GHz                                              |                     | 17   |     | dB    |

|                                                                                          |                           | 10GHz to 13GHz                                               |                     | 10   |     |       |

|                                                                                          |                           | 13GHz to 15GHz                                               |                     | 7    |     |       |

| <b>Tx REFERENCE CLOCK INPUT SPECIFICATIONS (REFCLK<math>\pm</math>)</b>                  |                           |                                                              |                     |      |     |       |

| Reference Clock Frequency Tolerance                                                      |                           |                                                              | -100                | +100 |     | ppm   |

| Reference Clock Input Duty Cycle                                                         |                           |                                                              | 30                  | 70   |     | %     |

| <b>RESET INPUT (RESET)</b>                                                               |                           |                                                              |                     |      |     |       |

| Minimum Pulse Width of FIFO Reset                                                        |                           | UI is PCLKO period                                           |                     | 4    |     | UI    |

| Tolerated Drift Between PCLKI and PCLKO After Reset                                      |                           | UI is PCLKO period; drift is PCLKO crossing - PCLKI crossing | -1                  | +1   |     | UI    |

**Note 2:** See Table 1 for valid operating clock frequencies. AC characteristics are guaranteed by design and characterization.

**Note 3:** Relative to the falling edge of the SCLKO.

**Note 4:** Deterministic jitter includes pattern-dependent jitter and pulse-width distortion. Measured with a pattern equivalent to  $2^{23} - 1$  PRBS.

# 10Gbps 16:1 Serializer

MAX3952

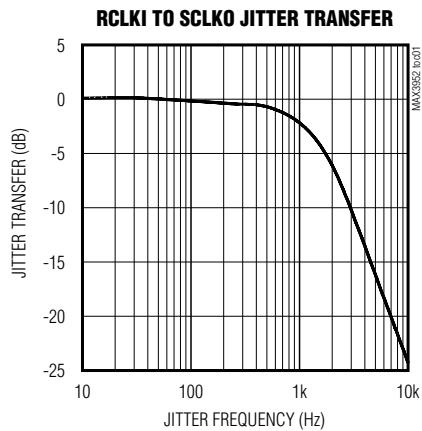

## Typical Operating Characteristics

( $T_A = +25^\circ\text{C}$ ,  $V_{CC} = +3.3\text{V}$ , unless otherwise noted.)

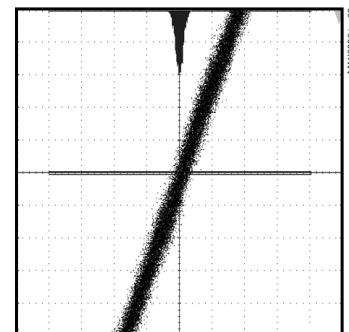

### SERIAL CLOCK OUTPUT RANDOM JITTER

# 10Gbps 16:1 Serializer

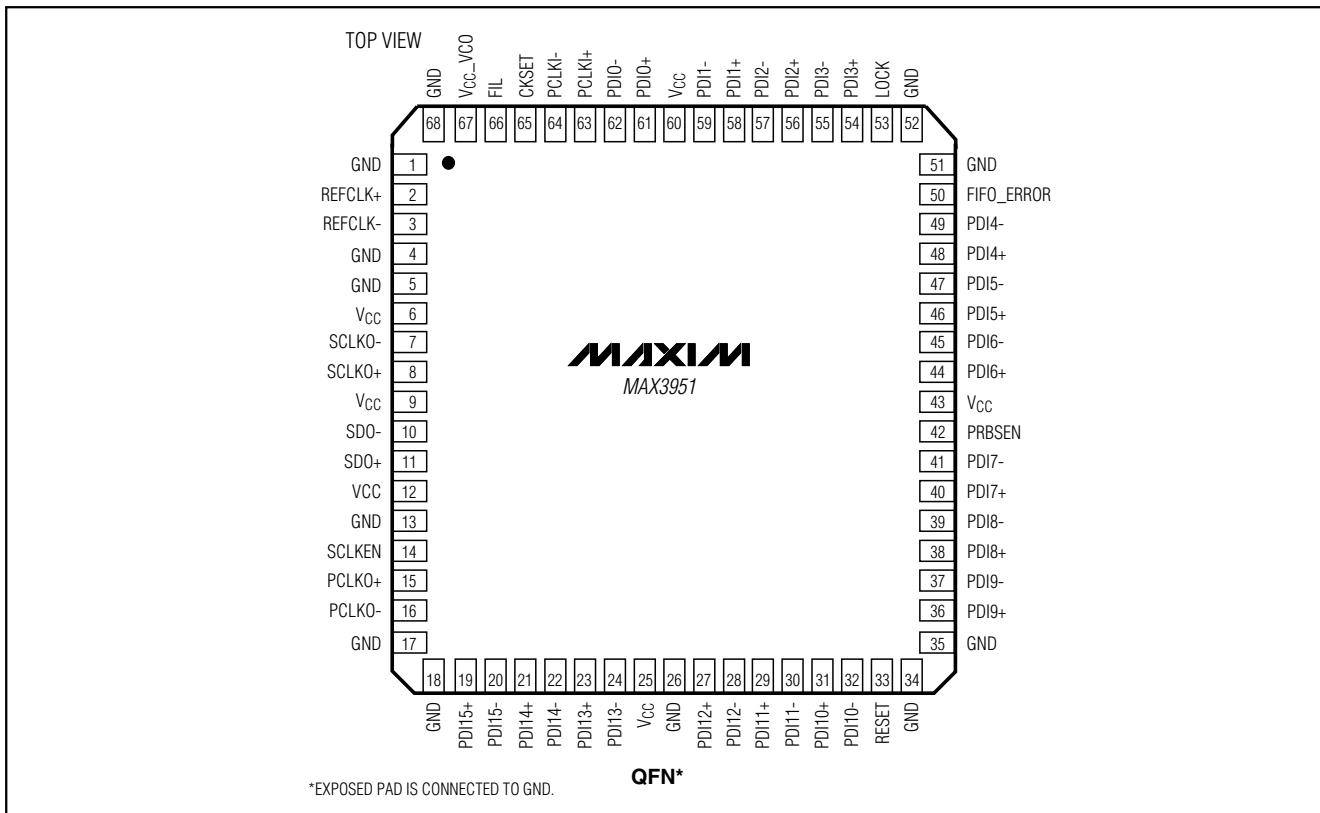

## Pin Description

| PIN                                                                        | NAME            | FUNCTION                                                                                                                     |

|----------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 5, 13,<br>17, 18, 26,<br>34, 35, 51,<br>52, 68                       | GND             | Ground                                                                                                                       |

| 2                                                                          | REFCLK+         | Positive Reference Clock Input, LVPECL                                                                                       |

| 3                                                                          | REFCLK-         | Negative Reference Clock Input, LVPECL                                                                                       |

| 6, 9, 12, 25,<br>43, 60                                                    | Vcc             | Positive Power Supply                                                                                                        |

| 7                                                                          | SCLKO-          | Negative Serial Clock Output, CML. 9.95328GHz or 10.3125GHz                                                                  |

| 8                                                                          | SCLKO+          | Positive Serial Clock Output, CML. 9.95328GHz or 10.3125GHz                                                                  |

| 10                                                                         | SDO-            | Negative Serial Data Output, CML. 9.95328Gbps or 10.3125Gbps                                                                 |

| 11                                                                         | SDO+            | Positive Serial Data Output, CML. 9.95328Gbps or 10.3125Gbps                                                                 |

| 14                                                                         | SCLKEN          | Control Input for Disabling SCLKO Output:<br>SCLKEN = GND $\Rightarrow$ SCLKO Off<br>SCLKEN = Vcc $\Rightarrow$ SCLKO Active |

| 15                                                                         | PCLKO+          | Positive Source Clock Output. LVDS, 622MHz or 644MHz. Clocks the MAC.                                                        |

| 16                                                                         | PCLKO-          | Negative Source Clock Output. LVDS, 622MHz or 644MHz. Clocks the MAC.                                                        |

| 19, 21, 23,<br>27, 29, 31,<br>36, 38, 40,<br>44, 46, 48,<br>54, 56, 58, 61 | PDI15+ to PDI0+ | Positive Parallel Data Inputs, LVDS. PDI15+ is MSB                                                                           |

| 20, 22, 24,<br>28, 30, 32,<br>37, 39, 41,<br>45, 47, 49,<br>55, 57, 59, 62 | PDI15- to PDI0- | Negative Parallel Data Inputs, LVDS. PDI15- is MSB                                                                           |

| 33                                                                         | RESET           | 16 x 4-Bit FIFO Reset Input, TTL, Active High                                                                                |

| 42                                                                         | PRBSEN          | PRBS Pattern Generator Enable Input, TTL, Active High                                                                        |

| 50                                                                         | FIFO_ERROR      | FIFO Error, TTL, Active High                                                                                                 |

| 53                                                                         | LOCK            | PLL Lock Indicator, TTL, Active High                                                                                         |

| 63                                                                         | PCLKI+          | Positive Parallel Clock Input, LVDS                                                                                          |

| 64                                                                         | PCLKI-          | Negative Parallel Clock Input, LVDS                                                                                          |

| 65                                                                         | CKSET           | Reference Clock Programming Pin. Programming instructions in Table 1.                                                        |

| 66                                                                         | FIL             | Filter Capacitor Input Pin                                                                                                   |

| 67                                                                         | Vcc_VCO         | Loop Filter and VCO Positive Power Supply                                                                                    |

# 10Gbps 16:1 Serializer

## Detailed Description

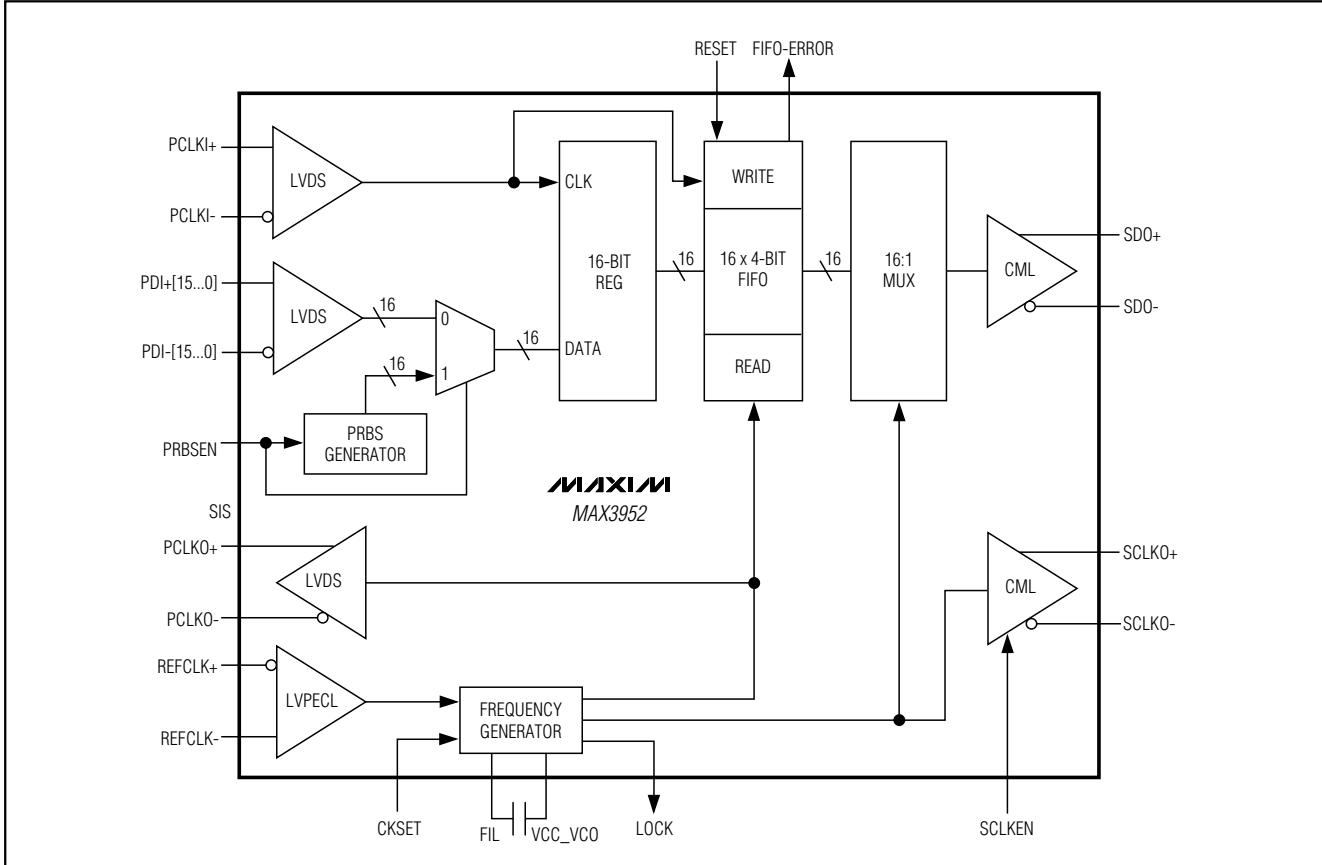

The MAX3952 converts 16-bit-wide, 622Mbps/644Mbps data to 9.95Gbps/10.3Gbps serial data (Figures 3 and 4). Data is loaded into the 16:1 mux through a 16 x 4 FIFO buffer for wide tolerance to clock skew. Clock and data inputs are LVDS levels, and high-speed serial outputs are current-mode logic (CML). An internal PLL frequency synthesizer generates a serial clock from a low-speed reference clock.

### Low-Voltage Differential-Signal Inputs and Outputs

The MAX3952 has LVDS inputs for interfacing with high-speed digital circuitry. This technology uses 250mV to 400mV differential low-voltage swings to achieve fast transition times, minimal power dissipation, and noise immunity. For proper operation, the parallel clock LVDS outputs ( $\text{PCLKO}\pm$ ) require  $100\Omega$  differential DC terminations between the positive and negative outputs. Do not terminate these outputs to ground. The parallel data and parallel clock LVDS inputs ( $\text{PDI}_+$ ,  $\text{PDI}_-$ ,  $\text{PCLKI}_+$ ,  $\text{PCLKI}_-$ ) are internally terminated with a  $100\Omega$  differential input resistance and therefore do not require external termination.

### LVPECL Inputs

The reference clock ( $\text{REFCLK}\pm$ ) has LVPECL inputs for interfacing to a crystal oscillator using AC- or DC-coupling. The  $\text{REFCLK}\pm$  inputs are self-biasing to  $\text{VCC} - 1.3\text{V}$  for AC-coupled inputs. Only a  $100\Omega$  differential termination resistance must be added when inputs are AC-coupled.

### Current-Mode Logic Outputs

The high-speed data and clock outputs ( $\text{SDO}\pm$ ,  $\text{SCLKO}\pm$ ) of the MAX3952 are designed using CML. The CML outputs include internal  $50\Omega$  back termination to  $\text{VCC}$ . These outputs are intended to drive a  $50\Omega$  transmission line terminated with a matched load impedance. For detailed instructions on how to interface with LVDS, PECL, and CML, refer to HFAN-01.0: *Introduction to LVDS, PECL, and CML*.

### FIFO Buffer

Data is latched into the MAX3952 by the parallel input clock ( $\text{PCLKI}\pm$ ). The parallel input clock is the FIFO write clock. The parallel output clock ( $\text{PCLKO}\pm$ ) is the FIFO read clock that loads the 16:1 mux. The FIFO allows the read and write clock to vary by up to  $\pm 1\text{UI}$  (unit interval). This specification makes the MAX3952 noncompliant with the IEEE802.3ae standard, as this standard requires a tolerance of  $\pm 14\text{UI}$ . Conditions that result in the read and write clock accessing the same FIFO address are indicated by  $\text{FIFO\_ERROR}$ . To clear

this condition, assert  $\text{RESET}$  high for at least 4UI.  $\text{FIFO\_ERROR}$  can be connected directly to the  $\text{RESET}$  input to clear timing errors. After reset, the full elastic range of the FIFO is available again.

### Frequency Synthesizer

The PLL synthesizes a 9.95GHz/10.31GHz clock from an external reference clock. The PLL reference clock ( $\text{REFCLK}\pm$ ) can be programmed as 622MHz/644MHz or 155MHz/161MHz using the  $\text{CKSET}$  pin. See Table 1 for  $\text{CKSET}$  settings. The parallel output clock ( $\text{PCLKO}\pm$ ) is derived from the synthesizer and is  $\text{SCLKO} \div 16$ . A TTL-compatible loss-of-lock indicator ( $\text{LOCK}$ ), asserts low when the VCO is unable to lock to the reference frequency. This pin can be used to directly drive an LED. If jitter on the  $\text{REFCLK}\pm$  input is present, an error with respect to the divided down  $\text{SCLKO}$  frequency of 500ppm will be indicated by a low state on  $\text{LOCK}$ .

**Table 1. Setting REFCLK Frequency**

| REFERENCE CLOCK FREQUENCY (MHz) | CKSET PIN SETTING                  | SERIAL CLOCK FREQUENCY (GHz) |

|---------------------------------|------------------------------------|------------------------------|

| 622.08                          | OPEN                               | 9.95                         |

| 644.53                          | $\text{VCC}$                       | 10.3                         |

| 155.52                          | $\text{GND}$                       | 9.95                         |

| 161.13                          | $30\text{k}\Omega$ to $\text{GND}$ | 10.3                         |

### Internal Pattern Generator

The MAX3952 includes a SONET-compliant internal pattern generator capable of a  $27 - 1$  PRBS pattern. Connecting the  $\text{PRBSEN}$  pin to  $\text{VCC}$  enables the pattern generator.

### Layout Techniques

For best performance, use good high-frequency layout techniques. Filter voltage supplies and keep ground connections short. Use multiple vias where possible. Use controlled impedance transmission lines to interface with the MAX3952 clock and data inputs and outputs. Give special consideration to filtering the  $\text{VCC}_\text{VCO}$  pin; all other power supplies can be connected through a common filter.

### Exposed Pad (EP) Package

The EP 68-pin QFN incorporates features that provide a very low thermal resistance path for heat removal from the IC to a PC board. The MAX3952's exposed paddle must be soldered directly to a ground plane with good thermal conductance. Refer to HFAN-08.1: *Thermal Considerations of QFN and Other Exposed-Paddle Packages*.

# 10Gbps 16:1 Serializer

## Chip Information

TRANSISTOR COUNT: 8400

PROCESS: SiGe bipolar

Figure 1. Setup and Hold Time

Figure 2. Definition of Clock to Q

Figure 3. Functional Diagram

# 10Gbps 16:1 Serializer

MAX3952

Figure 4. Parallel and Serial Data Timing

## Pin Configuration

# 10Gbps 16:1 Serializer

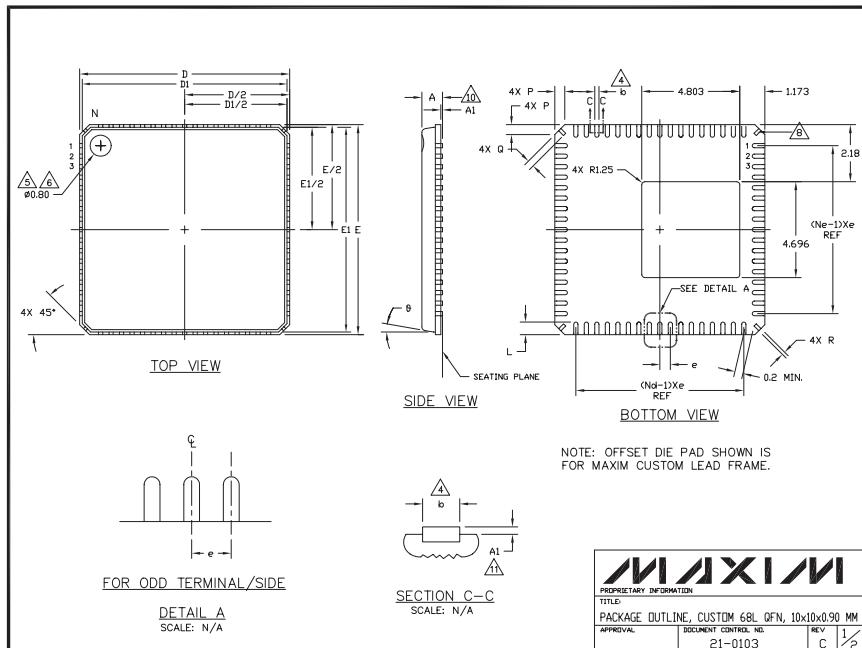

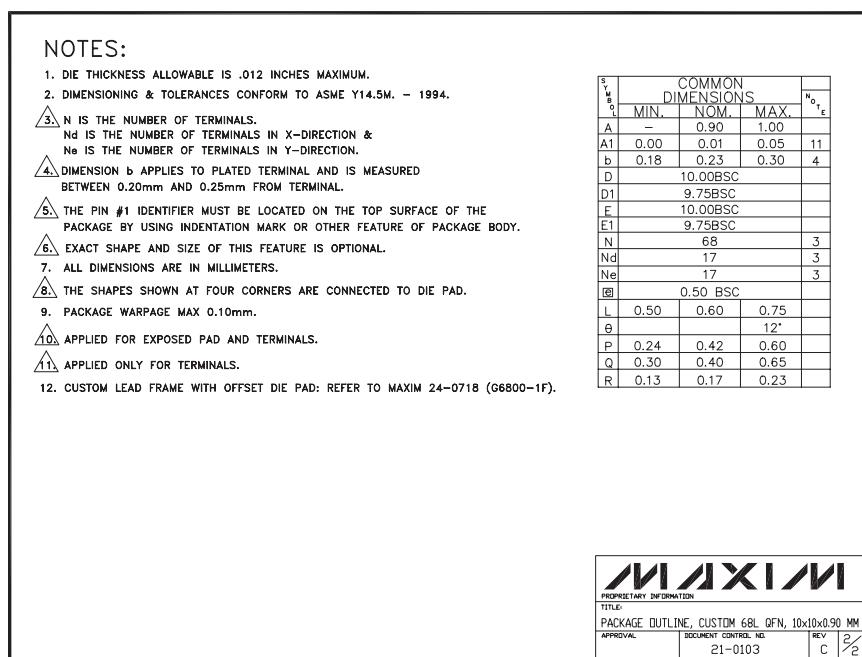

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to [www.maxim-ic.com/packages](http://www.maxim-ic.com/packages).)

### NOTES:

1. DIE THICKNESS ALLOWABLE IS .012 INCHES MAXIMUM.

2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. - 1994.

3.  $\triangle$  N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

4.  $\triangle$  DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED

BETWEEN 0.20mm AND 0.25mm FROM TERMINAL.

5.  $\triangle$  THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE

PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY.

6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

7. ALL DIMENSIONS ARE IN MILLIMETERS.

8.  $\triangle$  THE SHAPES SHOWN AT FOUR CORNERS ARE CONNECTED TO DIE PAD.

9. PACKAGE WARPAGE MAX 0.10mm.

10.  $\triangle$  APPLIED FOR EXPOSED PAD AND TERMINALS.

11.  $\triangle$  APPLIED ONLY FOR TERMINALS.

12. CUSTOM LEAD FRAME WITH OFFSET DIE PAD: REFER TO MAXIM 24-0718 (G6800-1F).

| SYMBOL | COMMON DIMENSIONS |      |      | N <sub>0</sub> T <sub>E</sub> |

|--------|-------------------|------|------|-------------------------------|

|        | MIN.              | NOM. | MAX. |                               |

| A      | —                 | 0.90 | 1.00 |                               |

| A1     | 0.00              | 0.01 | 0.05 | 11                            |

| b      | 0.18              | 0.23 | 0.30 | 4                             |

| D      | 10.00BSC          |      |      |                               |

| D1     | 9.75BSC           |      |      |                               |

| E      | 10.00BSC          |      |      |                               |

| E1     | 9.75BSC           |      |      |                               |

| N      | 68                |      |      | 3                             |

| Nd     | 17                |      |      | 3                             |

| Ne     | 17                |      |      | 3                             |

| Q      | 0.50 BSC          |      |      |                               |

| L      | 0.50              | 0.60 | 0.75 |                               |

| θ      | 12°               |      |      |                               |

| P      | 0.24              | 0.42 | 0.60 |                               |

| Q      | 0.30              | 0.40 | 0.65 |                               |

| R      | 0.13              | 0.17 | 0.23 |                               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

10 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**