MAX1996A

# **High-Efficiency, Wide Brightness** Range, CCFL Backlight Controller

## **General Description**

The MAX1996A integrated controller is optimized to drive cold-cathode fluorescent lamps (CCFLs) using synchronized full-bridge inverter architecture. Synchronized drive provides near sinusoidal waveforms over the entire input range to maximize the life of CCFLs. The controller also operates over a wide inputvoltage range with high efficiency and broad dimming

The MAX1996A includes safety features that limit the transformer secondary voltage and protect against single-point fault conditions including lamp-out and shortcircuit faults.

The MAX1996A regulates the CCFL brightness in three ways: linearly controlling the lamp current, digital pulsewidth modulating (DPWM) the lamp current, or using both methods simultaneously to achieve the widest dimming range (>30:1). CCFL brightness can be controlled with either an analog voltage or a 2-wire SMBus<sup>™</sup>-compatible interface. The MAX1996A directly drives the four external N-channel power MOSFETs of the full bridge inverter. An internal 5.3V linear regulator powers the MOSFET drivers, the synchronizable DPWM oscillator, and most of the internal circuitry.

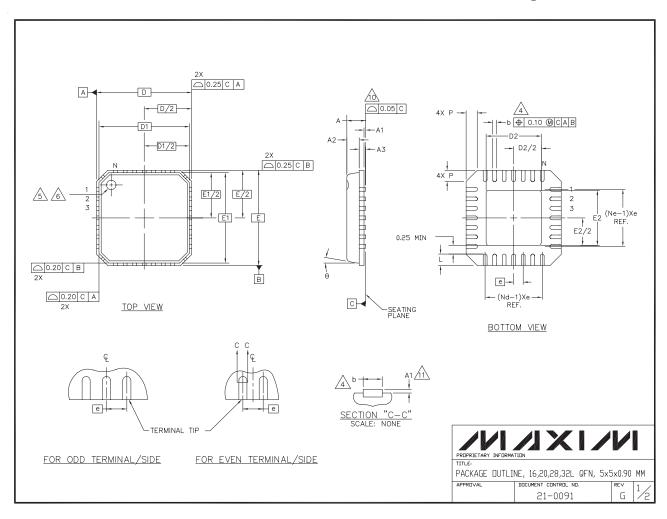

The MAX1996A has the same pin configuration as the MAX1895, but with modified SMBus slave address (0x58) and command bytes. In addition, the lamp-out protection timer has been reduced to approximately 1s and the DPWM frequency is guaranteed from 200Hz to 220Hz over the operating temperature range without external components or trimming. The MAX1996A is available in the space-saving 28-pin QFN package and operates over a -40°C to +85°C temperature range.

## **Applications**

Notebook Computers Multibulb LCD Monitors Portable Display Electronics

## Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE  |

|-------------|----------------|--------------|

| MAX1996AEGI | -40°C to +85°C | 28 QFN 5 × 5 |

SMBus is a trademark of Intel Corp.

### **Features**

- ♦ SMBus Slave Address (0x58) for Wide Dimming Range Inverters

- ♦ Guaranteed 200Hz to 220Hz DPWM Frequency

- ♦ Externally Synchronizable DPWM Frequency

- **♦ Lamp-Out Protection with 1s Timeout**

- ♦ Synchronized to Resonant Frequency Good Crest Factor for Longer Lamp Life **Ensures Maximum Strike Capability**

- ♦ High Power-to-Light Efficiency

- Wide Dimming Range (3 Methods)

Lamp Current Adjust: >3 to 1 DPWM: >10 to 1

Combined: >30 to 1

- ♦ Feed-Forward for Fast Response to Step Change of Input Voltage

- ♦ Wide Input-Voltage Range (4.6V to 28V)

- ◆ Transformer Secondary Voltage Limiting to **Reduce Transformer Stress**

- ♦ Protected Against Short-Circuit and Other Single-**Point Faults**

- ◆ Dual-Mode Brightness Control Interface

- ♦ Small Footprint 28-Pin QFN (5mm × 5mm) **Package**

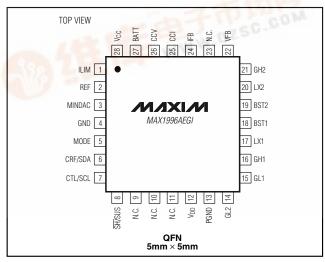

## Pin Configuration

Maxim Integrated Products

## **ABSOLUTE MAXIMUM RATINGS**

| BATT to GND<br>BST1, BST2 to GND         |                           |

|------------------------------------------|---------------------------|

| BST1 to LX1, BST2 to LX2                 |                           |

| GH1 to LX1                               | 0.3V to (BST1 + 0.3V)     |

| GH2 to LX2                               | 0.3V to (BST2 + 0.3V)     |

| V <sub>CC</sub> , V <sub>DD</sub> to GND | 0.3V to +6V               |

| REF, ILIM to GND                         | 0.3V to $(V_{CC} + 0.3V)$ |

| GL1, GL2 to GND                          | 0.3V to $(V_{DD} + 0.3V)$ |

| MINDAC, IFB, CCV, CCI to GND             | 0.3V to +6V               |

| MODE to GND                                           | 6V to +12V     |

|-------------------------------------------------------|----------------|

| VFB to GND                                            | 6V to +6V      |

| CRF/SDA, CTL/SCL, SH/SUS to GND                       | 0.3V to +6V    |

| PGND to GND                                           | 0.3V to +0.3V  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 28-Pin QFN (derate 20.84mW/°C above +                 | 70°C)1667mW    |

| Operating Temperature Range                           | 40°C to +85°C  |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VBATT = 12V, MINDAC = GND,  $V_{CC} = V_{DD}$ ,  $V_{\overline{SH}/SUS} = 5.3V$ , **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                | CONDITIONS                                                          |                                          | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------|------|------|------|-------|

| Va. — Input Voltage Dange                                | V <sub>CC</sub> = V <sub>DD</sub> = V <sub>BATT</sub>               |                                          | 4.6  |      | 5.5  | V     |

| VBATT Input Voltage Range                                | V <sub>CC</sub> = V <sub>DD</sub> = open                            |                                          | 5.5  |      | 28   | V     |

| VBATT Quiescent Current                                  | V <del>SH</del> /sus = 5.5V                                         | V <sub>BATT</sub> = 28V                  |      | 3.2  | 6    | mA    |

| ARATI Griesceur Criterir                                 | VSH/SUS = 5.5V                                                      | V <sub>BATT</sub> = V <sub>CC</sub> = 5V |      |      | 6    | IIIA  |

| VBATT Quiescent Current, Shutdown                        | SH/SUS = 0                                                          |                                          |      | 6    | 20   | μΑ    |

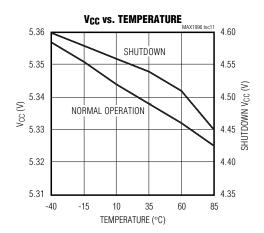

| V <sub>CC</sub> Output Voltage, Normal Operation         | $V_{\overline{SH}/SUS} = 5.5V, 6V < 0 < I_{LOAD} < 20mA$            | < V <sub>BATT</sub> < 28V                | 5.0  | 5.35 | 5.5  | ٧     |

| V <sub>CC</sub> Output Voltage, Shutdown                 | SH/SUS = GND, no l                                                  | oad                                      | 3.5  | 4.6  | 5.5  | V     |

| V <sub>CC</sub> Undervoltage Lockout (UVLO)              | V <sub>CC</sub> rising (leaving lo                                  | ockout)                                  |      |      | 4.5  | V     |

| Threshold                                                | V <sub>CC</sub> falling (entering lockout)                          |                                          | 4.0  |      |      | ĺ     |

| V <sub>CC</sub> UVLO Lockout Hysteresis                  |                                                                     |                                          |      | 200  |      | mV    |

| V <sub>CC</sub> Power-On Reset (POR) Threshold           | Rising edge                                                         |                                          | 0.9  | 1.75 | 2.7  | V     |

| V <sub>CC</sub> POR Hysteresis                           | Falling edge                                                        |                                          |      | 50   |      | mV    |

| REF Output Voltage, Normal Operation                     | $4.5V < V_{CC} < 5.5V$ , $I_{LOAD} = 40\mu A$                       |                                          | 1.96 | 2.00 | 2.04 | V     |

| GH1, GH2, GL1, GL2 On-Resistance                         | I <sub>TEST</sub> = 100mA, V <sub>CC</sub> = V <sub>DD</sub> = 5.3V |                                          |      | 2    | 6    | Ω     |

| GH1, GH2, GL1, GL2 Maximum Output<br>Current             |                                                                     |                                          |      | 1    |      | А     |

| BST1, BST2 Leakage Current                               | BST_ = 12V, LX_ = 7                                                 | V                                        |      |      | 5    | μΑ    |

| Input Resonant Frequency                                 | Guaranteed by design                                                | jn                                       | 20   |      | 300  | kHz   |

| Minimum Off-Time                                         |                                                                     |                                          | 210  | 315  | 420  | ns    |

| Maximum Off-Time                                         |                                                                     |                                          | 21   | 31.5 | 42   | μs    |

| Maximum Current-Limit Threshold LX1-GND, LX2-GND (Fixed) | ILIM = V <sub>CC</sub>                                              |                                          | 180  | 200  | 220  | mV    |

| Maximum Current-Limit Threshold                          | V <sub>ILIM</sub> = 0.5V                                            |                                          | 80   | 100  | 120  | ma\ / |

| LX1-GND, LX2-GND (Adjustable) $V_{\text{ILIM}} = 2.0V$   |                                                                     |                                          | 370  | 400  | 430  | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(VBATT = 12V, MINDAC = GND, VCC = VDD,  $V\overline{SH}/SUS = 5.3V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                                                                           |                                                                                    | CONDITIONS                                                     | MIN                   | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------|------|------|-------|

| Minimum Current-Crossing Threshold LX1-GND, LX2-GND                                                                 |                                                                                    |                                                                |                       | 6    |      | mV    |

| Current-Limit Leading-Edge Blanking                                                                                 |                                                                                    |                                                                | 210                   | 315  | 420  | ns    |

| D/A Converter Resolution                                                                                            | Guaranteed r                                                                       | monotonic                                                      | 5                     |      |      | Bits  |

| MINDAC Input Voltage Range                                                                                          |                                                                                    |                                                                | 0                     |      | 2    | V     |

| MINDAC Input Bias Current                                                                                           |                                                                                    |                                                                | -2                    |      | 2    | μΑ    |

| MINDAC Digital PWM Disable Threshold                                                                                | MINDAC = V                                                                         | CC                                                             | 2.4                   | 3.5  | 4    | V     |

| IFB Input Voltage Range                                                                                             |                                                                                    |                                                                | 0                     |      | 1.7  | V     |

|                                                                                                                     | VMINDAC = 0                                                                        | V, DAC code = 11111 binary                                     | 368                   | 388  | 408  |       |

| IFB Regulation Point                                                                                                | VMINDAC = 0                                                                        | V, DAC code = 00100 binary                                     | 30                    | 50   | 70   | mV    |

|                                                                                                                     | VMINDAC = 1                                                                        | V, DAC code = 00000 binary                                     | 180                   | 200  | 220  |       |

| IFB Input Bias Current                                                                                              |                                                                                    |                                                                | -2                    |      | 2    | μΑ    |

| IFB Lamp-Out Threshold                                                                                              |                                                                                    |                                                                | 125                   | 150  | 175  | mV    |

| IFB to CCI Transconductance                                                                                         | 1V < V <sub>CCI</sub> < 2                                                          | 2.5V                                                           |                       | 100  |      | μS    |

| CCI Output Impedance                                                                                                |                                                                                    |                                                                |                       | 20   |      | МΩ    |

| V <sub>FB</sub> Input Voltage Range                                                                                 |                                                                                    |                                                                | -2                    |      | 2    | V     |

| V <sub>FB</sub> Input Bias Current                                                                                  | V <sub>FB</sub> = 0V                                                               |                                                                | -0.5                  |      | 0.5  | μΑ    |

| V <sub>FB</sub> Regulation Point                                                                                    |                                                                                    |                                                                |                       | 510  | 530  | mV    |

| V <sub>FB</sub> to CCV Transconductance                                                                             | 1V < V <sub>CCV</sub> <                                                            | 2.7V                                                           |                       | 40   |      | μS    |

| V <sub>FB</sub> Zero-Voltage Crossing Threshold                                                                     |                                                                                    |                                                                | -10                   |      | +10  | mV    |

| CCV Output Impedance                                                                                                |                                                                                    |                                                                |                       | 20   |      | МΩ    |

|                                                                                                                     | No AC signal                                                                       | on MODE                                                        | 200                   | 210  | 220  |       |

| Digital PWM Chop-Mode Frequency                                                                                     | 32kHz AC signal on MODE                                                            |                                                                |                       | 250  |      | Hz    |

|                                                                                                                     | 100kHz AC signal on MODE                                                           |                                                                |                       | 781  |      |       |

| MODE-to-DPWM Sync Ratio                                                                                             | fMODE/fDPWN                                                                        | 1                                                              |                       | 128  |      |       |

|                                                                                                                     |                                                                                    | No AC signal on MODE                                           | 1.14                  | 1.22 | 1.30 |       |

| Lamp-Out Detection Timeout Timer                                                                                    | V <sub>IFB</sub> < 0.1V                                                            | 32kHz AC signal on MODE                                        |                       | 1.02 |      | s     |

| (Note 2)                                                                                                            |                                                                                    | 100kHz AC signal on MODE                                       |                       | 0.33 |      |       |

| MODE Operating Voltage Range                                                                                        |                                                                                    |                                                                | -5.5                  |      | 11   | V     |

| MODE Input Current                                                                                                  | MODE = GND or V <sub>CC</sub>                                                      |                                                                | -1                    |      | 1    | μΑ    |

| Positive Analog Interface Mode,<br>MODE = GND Threshold (V <sub>CTL/SCL</sub> = 0V<br>Sets Minimum Brightness)      | Sync clock average value on MODE to sync DPWM oscillator, not in shutdown (Note 3) |                                                                |                       |      | 0.6  | V     |

| Negative Analog Interface Mode,<br>MODE = REF Threshold (V <sub>CTL/SCL</sub> = 0V<br>Sets Maximum Brightness = 0V) | Sync clock average value on MODE to sync DPWM oscillator, not in shutdown (Note 3) |                                                                | 1.4                   |      | 2.6  | V     |

| SMBus Interface Mode, MODE = V <sub>CC</sub> Threshold                                                              | ,                                                                                  | verage value on MODE to sync<br>ator, not in shutdown (Note 3) | V <sub>CC</sub> - 0.6 |      |      | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{BATT} = 12V, MINDAC = GND, V_{CC} = V_{DD}, V_{\overline{SH}/SUS} = 5.3V, T_A = 0^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                          | CONDITIONS                               | MIN | TYP | MAX      | UNITS |  |

|--------------------------------------------------------------------|------------------------------------------|-----|-----|----------|-------|--|

| MODE AC Signal Amplitude                                           | Peak-to-peak (Note 4)                    | 2   |     | 5        | V     |  |

| MODE AC Signal Synchronization Range                               | Chopping oscillator synchronized to MODE | 32  |     | 100      | kHz   |  |

| CRF/SDA Input Range                                                |                                          | 2.7 |     | 5.5      | V     |  |

| CDE/CDA Input Current                                              | VCRF/SDA = 5.5V, SH/SUS = VCC            |     |     | 20       | μΑ    |  |

| CRF/SDA Input Current                                              | VCRF/SDA = 5.5V, SH/SUS = 0V             | -1  |     | 1        |       |  |

| CTL/SCL Input Range                                                |                                          | 0   |     | VCRF/SDA | V     |  |

| CTL/SCL Input Current                                              | MODE = REF or GND                        | -1  |     | 1        | μΑ    |  |

| A/D Converter Resolution                                           | Guaranteed monotonic                     |     | 5   |          | Bits  |  |

| A/D Converter Hysteresis                                           |                                          |     | 1   |          | LSB   |  |

| SH/SUS Input Low Voltage                                           |                                          |     |     | 0.8      | V     |  |

| SH/SUS Input High Voltage                                          |                                          | 2.1 |     |          | V     |  |

| SH/SUS Input Hysteresis                                            |                                          |     | 300 |          | mV    |  |

| SH/SUS Input Bias Current                                          |                                          | -1  |     | 1        | μΑ    |  |

| SDA, SCL Input Low Voltage                                         |                                          |     |     | 0.8      | V     |  |

| SDA, SCL Input High Voltage                                        |                                          | 2.1 |     |          | V     |  |

| SDA, SCL Input Hysteresis                                          |                                          |     | 300 |          | mV    |  |

| SDA Output Low Sink Current                                        | VCRF/SDA = 0.4V                          | 4   |     |          | mA    |  |

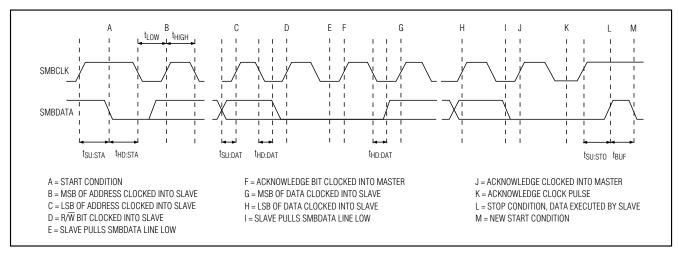

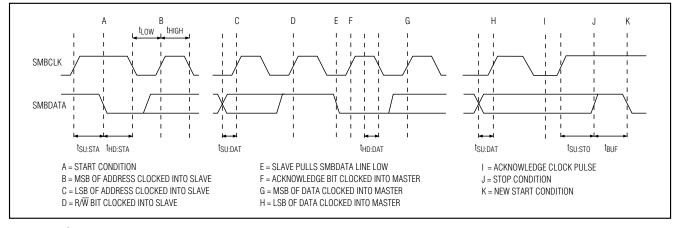

| SCL Serial Clock High Period                                       | THIGH                                    | 4   |     |          | μs    |  |

| SCL Serial Clock Low Period                                        | TLOW                                     | 4.7 |     |          | μs    |  |

| Start Condition Setup Time                                         | tsu:sta                                  | 4.7 |     |          | μs    |  |

| Start Condition Hold Time                                          | thd:sta                                  | 4   |     |          | μs    |  |

| SDA Valid to SCL Rising-Edge Setup<br>Time, Slave Clocking in Data | tsu:DAT                                  | 250 |     |          | ns    |  |

| SCL Falling Edge to SDA Transition                                 | thd:dat                                  | 0   |     |          | ns    |  |

| SCL Falling Edge to SDA Valid, Reading Out Data                    | T <sub>DV</sub>                          |     | 700 |          | ns    |  |

### **ELECTRICAL CHARACTERISTICS**

$(V_{BATT} = 12V, MINDAC = GND, V_{CC} = V_{DD}, V_{\overline{SH}/SUS} = 5.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                     | CONDITIONS                                            |                                          | MIN | TYP | MAX | UNITS |

|-----------------------------------------------|-------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| Vo arra Input Voltago Pango                   | V <sub>CC</sub> = V <sub>DD</sub> = V <sub>BATT</sub> |                                          | 4.6 |     | 5.5 | \/    |

| V <sub>BATT</sub> Input Voltage Range         | V <sub>CC</sub> = V <sub>DD</sub> = open              |                                          | 5.5 |     | 28  | V     |

| Value Ouissant Current                        | V <sub>BATT</sub> = 28V                               |                                          |     |     | 6   | m ^   |

| VBATT Quiescent Current                       | V <del>SH</del> /SUS = 5.5V                           | V <sub>BATT</sub> = V <sub>CC</sub> = 5V |     |     | 6   | mA    |

| V <sub>BATT</sub> Quiescent Current, Shutdown | VSH/SUS = 0V                                          |                                          |     | •   | 20  | μΑ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(VBATT = 12V, MINDAC = GND, VCC = VDD, VSH/SUS = 5.3V, TA = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                | CONDITIONS                                            | MIN  | TYP | MAX  | UNITS |  |

|----------------------------------------------------------|-------------------------------------------------------|------|-----|------|-------|--|

| V <sub>CC</sub> Output Voltage, Normal Operation         | VSH/SUS = 5.5V, 6V < VBATT < 28V,<br>0 < ILOAD < 20mA | 5.0  |     | 5.5  | V     |  |

| V <sub>CC</sub> Output Voltage, Shutdown                 | SH/SUS = GND, no load                                 | 3.5  |     | 5.5  | V     |  |

| Vac IIVI O Threehold                                     | V <sub>CC</sub> rising (leaving lockout)              |      |     | 4.5  | \/    |  |

| VCC UVLO Threshold                                       | V <sub>CC</sub> rising (entering lockout)             | 4.0  |     |      | V     |  |

| V <sub>CC</sub> POR Threshold                            | Rising edge                                           | 0.9  |     | 2.7  | V     |  |

| REF Output Voltage, Normal Operation                     | $4.5V < V_{CC} < 5.5V$ , $I_{LOAD} = 40\mu A$         | 1.96 |     | 2.04 | V     |  |

| GH1, GH2, GL1, GL2 On-Resistance                         | I <sub>TEST</sub> = 100mA                             |      |     | 10   | Ω     |  |

| Maximum Current-Limit Threshold LX1-GND, LX2-GND (Fixed) | ILIM = VCC                                            | 180  |     | 220  | mV    |  |

| Maximum Current-Limit Threshold                          | V <sub>ILIM</sub> = 0.5V                              | 80   |     | 120  | \/    |  |

| LX1-GND, LX2-GND (Adjustable)                            | $V_{ILIM} = 2.0V$                                     | 360  |     | 440  | mV    |  |

| IFB Input Voltage Range                                  |                                                       | 0    |     | 1.7  | V     |  |

| IFB Regulation Point                                     | V <sub>MINDAC</sub> = 0V, DAC code = 11111 binary     | 335  |     | 440  | mV    |  |

| IFB Input Bias Current                                   |                                                       | -2   |     | 2    | μΑ    |  |

| IFB Lamp-Out Threshold                                   |                                                       | 120  |     | 180  | mV    |  |

| VFB Input Voltage Range                                  |                                                       | -2   |     | 2    | V     |  |

| VFB Input Bias Current                                   | VFB = 0V                                              | -0.5 |     | 0.5  | μΑ    |  |

| VFB Regulation Point                                     |                                                       | 480  |     | 540  | mV    |  |

| VFB Zero-Voltage Crossing Threshold                      |                                                       | -20  |     | +20  | mV    |  |

| SHVSUS Input Low Voltage                                 |                                                       |      |     | 0.8  | V     |  |

| SHVSUS Input High Voltage                                |                                                       | 2.1  |     |      | V     |  |

| SDA, SCL Input Low Voltage                               |                                                       |      |     | 0.8  | V     |  |

| SDA, SCL Input High Voltage                              |                                                       | 2.1  |     |      | V     |  |

| SDA Output Low Sink Current                              | V <sub>CRF/SDA</sub> = 0.4V                           | 4    |     |      | mA    |  |

- Note 1: Specifications to -40°C are guaranteed by design based on final test characterization results.

- Note 2: Corresponds to 256 DPWM cycles or 32768 MODE cycles.

- Note 3: The MODE pin thresholds are only valid while the part is operating. When in shutdown, V<sub>REF</sub> = 0 and the part only differentiates between SMB mode and ADC mode. When in shutdown and with ADC mode selected, the CRF/SDA and CTL/SCL pins are at high impedance and do not cause extra supply current when their voltages are not at GND or V<sub>CC</sub>.

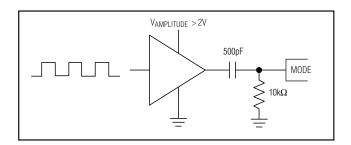

- Note 4: The amplitude is measured with the following circuit:

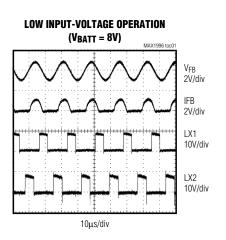

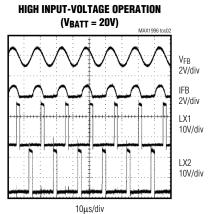

## **Typical Operating Characteristics**

(VBATT = 12V, VCTL = VCRF, VMINDAC = 1V, MODE = GND, circuit of Figure 1, Table 4.)

## Typical Operating Characteristics (continued)

(VBATT = 12V, VCTL = VCRF, VMINDAC = 1V, MODE = GND, circuit of Figure 1, Table 4.)

## **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ILIM    | Current-Limit Threshold Adjustment. Bias ILIM with a resistive voltage-divider between REF or V <sub>CC</sub> and GND. The current-limit threshold measured between LX_ and GND is 1/5th the voltage at ILIM; ILIM adjustment range is 0V to 3V. Connect ILIM to V <sub>CC</sub> to set the default current-limit threshold to 0.2V.                                                                                                                                                                                                                                                                       |

| 2   | REF     | 2V Reference Output. Bypass REF to GND with a 0.1μF capacitor. REF is discharged to GND when shut down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | MINDAC  | DAC Zero-Scale Input. $V_{MINDAC}$ sets the D/A converter's minimum-scale output voltage. Disable DPWM by connecting MINDAC to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | GND     | System Ground. The GND input to the maximum and minimum current-limit comparators. The comparators sense the low-side FET NL1 and NL2 for zero-current crossing and current limit.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | MODE    | Interface Selection Input and Sync Input for DPWM Chopping. The average voltage on the MODE pin selects one of three CCFL brightness control interfaces:  MODE = V <sub>CC</sub> enables SMBus serial interface.  MODE = GND enables the analog interface (positive analog interface mode), V <sub>CTL/SCL</sub> = 0V sets minimum brightness.  MODE = REF enables the analog interface (reverse analog interface mode), V <sub>CTL/SCL</sub> = 0V sets maximum brightness.  An AC clocking signal superimposed on the DC average MODE pin voltage can be used to synchronize the DPWM chopping frequency. |

| 6   | CRF/SDA | Reference and Serial Data Input. In analog interface mode, pin 6 is the reference input to the 5-bit brightness control ADC. Bypass CRF to GND with a 0.1µF capacitor. In SMBus interface mode, SDA is an SMBus serial data input/open-drain output.                                                                                                                                                                                                                                                                                                                                                       |

## Pin Description (continued)

| PIN           | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | CTL/SCL  | Brightness Control and Serial Clock Input. In analog interface mode, pin 7 is a CCFL brightness control input. CTL varies from 0V to REF to linearly control lamp brightness. In SMBus interface mode, SCL is an SMBus serial clock input.                                                                                                                                                  |

| 8             | SH/SUS   | Shutdown and Suspend Mode Control. In analog interface mode, pin 8 is an active-low shutdown input. In SMBus interface mode, pin 8 is an SMBus suspend control input.                                                                                                                                                                                                                       |

| 9, 10, 11, 23 | N.C.     | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                    |

| 12            | $V_{DD}$ | Power Supply for Gate Drivers. Connect V <sub>DD</sub> to the output of the linear regulator (V <sub>CC</sub> ). Bypass V <sub>DD</sub> with a 0.1µF capacitor to PGND.                                                                                                                                                                                                                     |

| 13            | PGND     | Power Ground. Gate-driver current flows through this pin.                                                                                                                                                                                                                                                                                                                                   |

| 14            | GL2      | Low-Side FET NL2 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                                         |

| 15            | GL1      | Low-Side FET NL1 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                                         |

| 16            | GH1      | High-Side FET NH1 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                                        |

| 17            | LX1      | Switching Node Connection. LX1 is the internal lower supply rail for the GH1 high-side gate driver. LX1 is also the sense input to the current comparators.                                                                                                                                                                                                                                 |

| 18            | BST1     | High-Side FET NH1 Driver Bootstrap Input. Connect BST1 through a diode to V <sub>DD</sub> and through a 0.1μF capacitor to LX1 (Figure 1).                                                                                                                                                                                                                                                  |

| 19            | BST2     | High-Side FET NH2 Driver Bootstrap Input. Connect BST2 through a diode to V <sub>DD</sub> and through a 0.1μF capacitor to LX2 (Figure 1).                                                                                                                                                                                                                                                  |

| 20            | LX2      | Switching Node Connection. LX2 is the internal lower supply rail for the GH2 high-side gate driver. LX2 is also the sense input to the current comparators.                                                                                                                                                                                                                                 |

| 21            | GH2      | High-Side FET NH2 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                                        |

| 22            | VFB      | Lamp-Output Feedback-Sense Input. The average value on VFB is regulated during startup and open-lamp conditions to 0.5V by controlling the on-time of high-side switches. A capacitive voltage-divider between the CCFL lamp output and GND is sensed to set the maximum average lamp output voltage.                                                                                       |

| 24            | IFB      | Lamp Current-Sense Input. The voltage on IFB is used to regulate the lamp current. If the IFB input falls below 150mV for 1s, then the MAX1996A signals an open-lamp fault.                                                                                                                                                                                                                 |

| 25            | CCI      | Current-Loop Compensation Pin. CCI is the output of the current-loop transconductance amplifier (GMI) that regulates the CCFL current. The CCI voltage controls the time interval in which full-bridge applies the input voltage (BATT) to transformer network. Connect CCI to GND through a 0.1µF capacitor. CCI is internally discharged to GND in shutdown.                              |

| 26            | CCV      | Voltage-Loop Compensation Pin. CCV is the output of the voltage-loop transconductance amplifier (GMV) that regulates the maximum average secondary transformer voltage. Connect CCV to GND with a 10nF capacitor. The CCV voltage controls the time interval that the full bridge applies the input voltage (BATT) to transformer network. CCV is internally discharged to GND in shutdown. |

| 27            | BATT     | Supply Input. Input to the internal 5.3V linear regulator that provides power (V <sub>CC</sub> ) to the chip. Bypass BATT to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                    |

| 28            | Vcc      | 5.3V Linear-Regulator Output. $V_{CC}$ is the supply voltage for the MAX1996A. Bypass $V_{CC}$ to GND with a 0.47µF ceramic capacitor. $V_{CC}$ can also be connected to BATT if $V_{BATT}$ < 5.5V.                                                                                                                                                                                         |

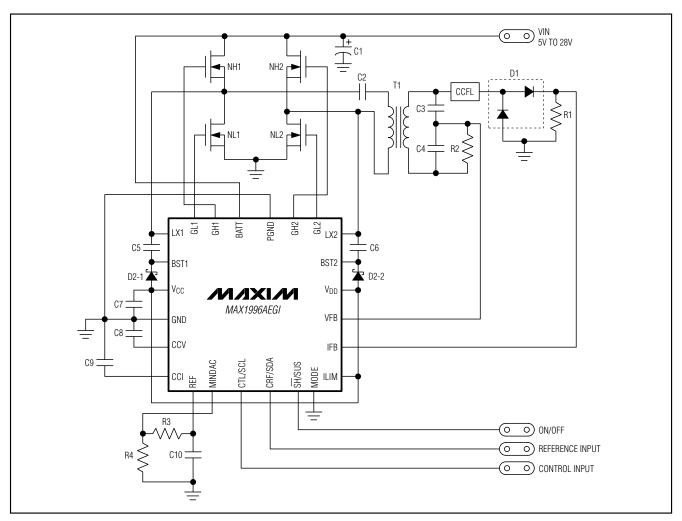

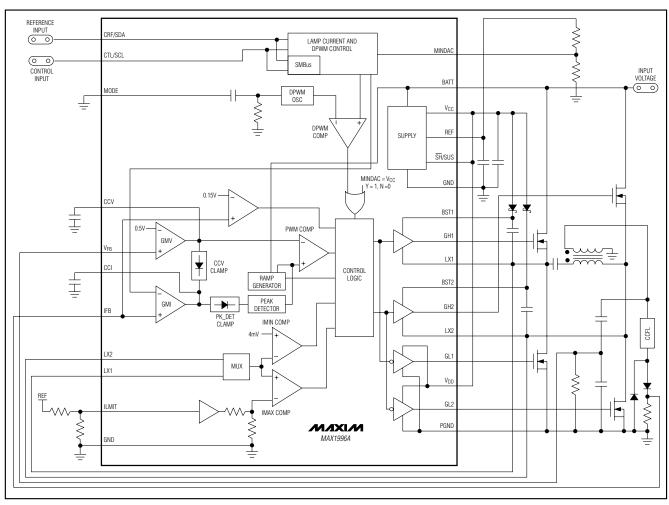

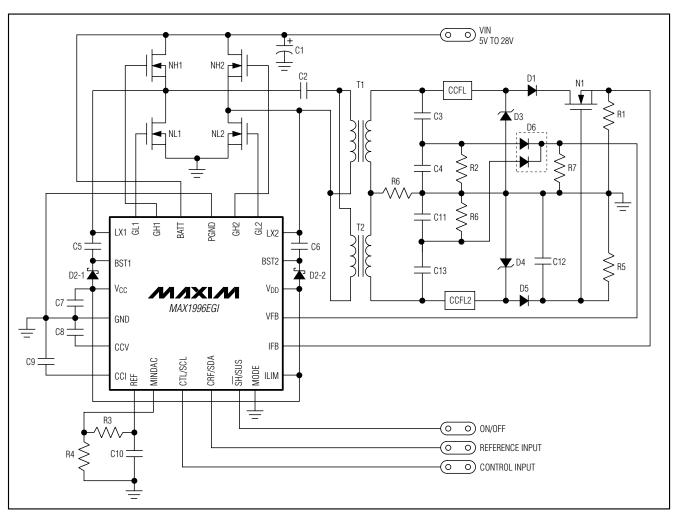

Figure 1. Standard Application Circuit

## Detailed Description

The MAX1996A is optimized to drive CCFLs using a synchronized full-bridge inverter architecture. The drive to the full-bridge MOSFETs is synchronized to the resonant frequency of the tank circuit so that the CCFL's full-strike voltage develops for all operating conditions. The synchronized architecture provides near sinusoidal drive waveforms over the entire input range to maximize the life of CCFLs. The MAX1996A operates over a wide input voltage range (4.6V to 28V), achieves high efficiency, and maximizes dimming range.

The MAX1996A regulates the brightness of a CCFL in three ways:

1) Linearly controlling the lamp current.

- Digitally pulse-width modulating (or chopping) the lamp current (DPWM).

- Using both methods simultaneously for widest dimming range.

DPWM is implemented by pulse-width modulating the lamp current at a rate faster than the eye can detect.

The MAX1996A includes a 5.3V linear regulator to power the drivers for full-bridge switches, the synchronizable DPWM oscillator, and most of the internal circuitry. The MAX1996A is very flexible and can be controlled with an analog interface or with an SMBus interface.

Figure 2. Resonant Operation

#### **Resonant Operation**

The MAX1996A drives the four N-channel power MOSFETs that make up the zero-voltage switching (ZVS) full-bridge inverter as shown in Figure 1. The LX1 and LX2 switching nodes are AC coupled to the primary side of the transformer.

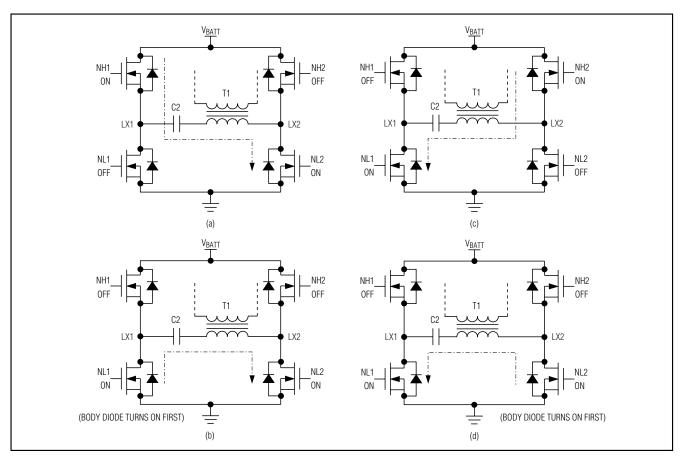

Assume that NH1 and NL2 are turned on at the beginning of the cycle as shown in Figure 2(a). The primary current flows through MOSFET NH1, DC blocking cap C2, the primary side of transformer T1, and finally MOSFET NL2. During this interval, the primary current ramps up until the controller turns off NH1. When NH1 is off, the primary current forward biases the body diode of NL1 and brings the LX1 node down as shown in Figure 2(b). When the controller turns on NL1, its drain-to-source voltage is near zero because its forward-biased body diode clamps the drain. Since NL2 is still on, the primary current flows through NL1, C2, the primary side of T1, and finally NL2. Once the primary current drops

to the minimum current threshold (6mV/RDSON), the controller turns off NL2. The remaining energy in T1 charges up the LX2 node until the body diode of NH2 is forward biased. When NH2 turns on, it does so with near zero drain-to-source voltage. The primary current reverses polarity as shown in Figure 2(c), beginning a new cycle with the current flowing in the opposite direction, with NH2 and NL1 on. The primary current ramps up until the controller turns off NH2. When NH2 is off, the primary current forward biases the body diode of NL2, and brings the LX2 node down as shown in Figure 2(d). After the LX2 node goes low, the controller losslessly turns on NL2. Once the primary current drops to the minimum current threshold, the controller turns off NL1. The remaining energy charges up the LX1 node until the body diode of NH1 is forward biased. Finally, NH1 losslessly turns on, beginning a new cycle as shown in Figure 2(a).

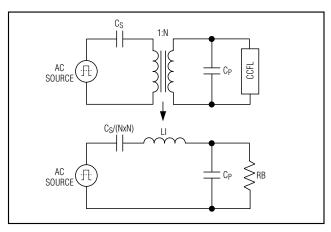

Figure 3. Equivalent Circuit

Note that switching transitions on all four power MOSFETs occur under ZVS conditions, which reduces transient power losses and EMI.

The equivalent circuit of the resonant tank is shown in Figure 3. The resonant frequency is determined by the RLC resonant tank elements: CS, CP, LL, and RB. CS is the series capacitance on the primary side of the transformer. CP is the parallel cap on the transformer's secondary.  $L_L$  is the transformer secondary leakage inductance. RB is an idealized resistance that models the CCFL load in normal operation.

#### **Current and Voltage-Control Loops**

The MAX1996A uses a current loop and a voltage loop to control the energy applied to the CCFL. The current loop is the dominant control in setting the lamp brightness. The rectified lamp current is measured with a sense resistor in series with the CCFL. The voltage across this resistor is applied to the IFB input to regulate the average lamp current. The voltage loop controls the voltage across the lamp and is active during the beginning of DPWM on-cycles and the open-lamp fault condition. It limits the energy applied to the resonant network once the transformer secondary voltage is above the threshold of 500mV average measured at VFB.

Both voltage and current circuits use transconductance-error amplifiers to compensate the loops. The voltage-error amplifier creates an error current based upon the voltage difference between VFB and the internal reference level (typically 500mV) (Figure 4). The error current is then used to charge and discharge a capacitor at the CCV output to create an error voltage VCCV. The current loop produces a similar signal at CCI based on the voltage difference between IFB and the dimming control signal. This signal is set by either the

SMBus interface or the analog interface (see the *Dimming Range* section). This error voltage is called V<sub>CCI</sub>. In normal operation, the current loop is in control of the regulator so long as V<sub>CCI</sub> is less than V<sub>CCV</sub>. The control signal is compared with an internal ramp signal to set the high-side switch on time (t<sub>ON</sub>).

When DPWM is employed, the two control loops work together to limit the transformer voltage and to allow a wide dimming range with good line rejection. During the DPWM off-cycle, VCCV is set to 1.2V and the current-loop error amplifier output is high impedance. VVFB is set to 0.6V to create a soft-start at the beginning of each DPWM on-cycle in order to avoid overshoot on the transformer's secondary. When the transconductance amplifier in the current loop is high impedance, it acts like a sample-and-hold circuit to keep VCCI from changing during the off-cycles. This action allows the current-control loop to regulate the average lamp current.

See the *Current-Sense Resistor* and the *Voltage-Sense Capacitors* sections for information regarding setting the current- and voltage-loop thresholds.

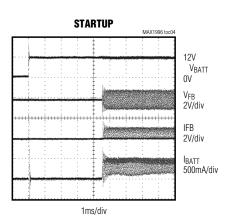

#### Startup

Operation during startup differs from the steady-state condition described in the *Current and Voltage-Control Loops* section. Upon power-up, V<sub>CCI</sub> slowly rises, increasing the duty cycle, which provides soft-start. During this time, V<sub>CCV</sub>, which is the faster control loop, is limited to 150mV above V<sub>CCI</sub>. Once the secondary voltage reaches the strike voltage, the lamp current begins to increase. When the lamp current reaches the regulation point, V<sub>CCI</sub> exceeds V<sub>CCV</sub> and it reaches steady state. With MINDAC = V<sub>CC</sub>, DPWM is disabled and the current loop remains in control regulating the lamp current.

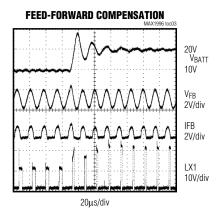

#### Feed-Forward Control

The MAX1996A has a feed-forward control circuit, which influences both control loops. Feed-forward control instantly adjusts the ton time to changes in input voltage. This feature provides immunity to changes in input voltage at all brightness levels and makes compensation over wide input ranges easier. The feed-forward circuit improves line regulation for short DPWM on-times and makes startup transients less dependent on input voltage.

Feed-forward control is implemented by varying the internal voltage ramp rate. This has the effect of varying ton as a function of input voltage while maintaining about the same signal levels at VCCI and VCCV. Since the required voltage change across the compensation capacitors is minimal, the controller's response to change in VBATT is essentially instantaneous.

Figure 4. Functional Diagram

# Transient Overvoltage Protection from Dropout

The MAX1996A is designed to maintain tight control of the transformer secondary under all transient conditions including dropout. To maximize run time, it is desirable to allow the circuit to operate in dropout at extremely low battery voltages where the backlight's performance is not critical. When VBATT is very low, the controller can lose regulation and run at maximum duty cycle. Under these circumstances, a transient overvoltage condition can occur when the AC adapter is suddenly applied to power the circuit. The feed-forward circuitry minimizes variations in lamp voltage due to such input voltage steps. The regulator also clamps the voltage on VCCI. Both features ensure that overvoltage transients

do not appear on the transformer when leaving dropout.

The V<sub>CCI</sub> clamp is unique in that it limits at the peaks of the voltage-ramp generator. As the circuit reaches dropout, V<sub>CCI</sub> approaches the peaks of the ramp generator in order to reach maximum t<sub>ON</sub>. If V<sub>BATT</sub> decreases further, the control loop loses regulation and V<sub>CCI</sub> tries to reach its positive supply rail. The clamp on V<sub>CCI</sub> prevents this from happening and V<sub>CCI</sub> rides just above the peaks of the PWM ramp. If V<sub>BATT</sub> continues to decrease, the feed-forward PWM ramp generator loses amplitude and the clamp drags V<sub>CCI</sub> down with it to a voltage below where V<sub>CCI</sub> would have been if the circuit were not in dropout. When V<sub>BATT</sub> suddenly steps out of dropout, V<sub>CCI</sub> is still low and the MAX1996A maintains the drive on the transformer at the old dropout level. The control

**Table 1. Interface Modes**

|         | DIGITAL INTERFACE      | ANALOG INTERFACE                                                 |                                                             |  |  |

|---------|------------------------|------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| PIN     | MODE = V <sub>CC</sub> | MODE = REF<br>V <sub>CTL/SCL</sub> = 0 = maximum brightness      | MODE = GND<br>V <sub>CTL/SCL</sub> = 0 = minimum brightness |  |  |

| SH/SUS  | SMBus suspend          | Logic level shutdown control input                               |                                                             |  |  |

| CRF/SDA | SMBus data I/O         | Reference input for minimum brightness                           | Reference input for maximum brightness                      |  |  |

| CTL/SCL | SMBus clock input      | Analog control input to set brightness (range from 0 to CRF/SDA) |                                                             |  |  |

loop then slowly corrects the lamp current by increasing  $V_{\text{CCI}}$ , which brings the circuit back into regulation.

#### **Interface Selection**

Table 1 describes the functionality of SH/SUS, CRF/SDA, and CTL/SCL in each of the MAX1996A's three interface modes. The MAX1996A features both an SMBus digital interface and an analog interface. Note that the MODE signal can also synchronize the DPWM frequency. (See *Synchronizing the DPWM Frequency*.)

#### **Dimming Range**

The brightness is controlled by either the Analog Interface (see the *Analog Interface* section) or the SMBus Interface (see the *SMBus Interface* section). The brightness of the CCFL is adjusted in the following three ways:

- Lamp-current control, where the magnitude of the average lamp current is adjusted.

- 2) DPWM control, where the average lamp current is pulsed to the set level with a variable duty cycle.

- 3) The combination of the first two methods.

In each of the three methods, a 5-bit brightness code is generated from the selected interface and is used to set the lamp current and/or DPWM duty cycle.

The 5-bit brightness code defines the lamp current level with 00000\b representing minimum lamp current and 11111\b representing maximum lamp current. The average lamp current is measured across an external sense resistor (see the *Current-Sense Resistor* section). The voltage on the sense resistor is measured at IFB. The brightness code adjusts the regulation voltage at IFB (VIFB). The minimum average VIFB is VMINDAC/5, where VMINDAC varies between 0 to 2V, and the maximum average is set by the following formula:

VIFB = VREF × 31 / 160 + VMINDAC / 160,

which is between 387.5mV and 400mV.

If VIFB does not exceed 150mV peak (which is about 47.7mV/R1 RMS lamp current) for greater than 1s, the

MAX1996A assumes a lamp-out condition and shuts down (see the *Lamp-Out Detection* section).

The equation relating brightness code to IFB regulation voltage is:

$V_{IFB} = V_{REF} \times n / 160 + V_{MINDAC} \times (32 - n) / 160$

where n is the brightness code.

To always use maximum average lamp current when using DPWM control, set V<sub>MINDAC</sub> to V<sub>REF</sub>.

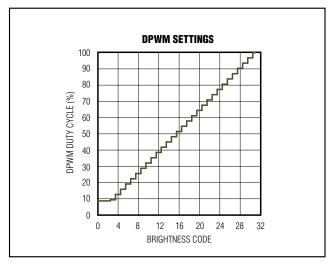

DPWM control is similar to lamp-current control in that it also responds to the 5-bit brightness code. A brightness code of 00000\b corresponds to a 9% DPWM duty cycle and a brightness code of 11111\b corresponds to a 100% DPWM duty cycle. The duty cycle changes by 3.125% per step, but codes 00000\b to 00011\b all produce 9% (Figure 5).

To disable DPWM and always use 100% duty cycle, set  $V_{MINDAC}$  to  $V_{CC}$ . Note that with DPWM disabled, the equations shown above should assume  $V_{MINDAC} = 0$  instead of  $V_{MINDAC} = V_{CC}$ . Table 2 describes MINDAC's functionality and Table 3 shows some typical settings for the brightness adjustment.

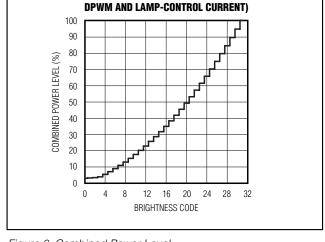

In normal operation,  $V_{MINDAC}$  is set between zero and  $V_{REF}$  and the MAX1996A uses both lamp-current control and DPWM control to vary the lamp brightness (Figure 6). In this mode, lamp-current control regulates the average lamp current during a DPWM on-cycle.

### **Analog Interface and Brightness Code**

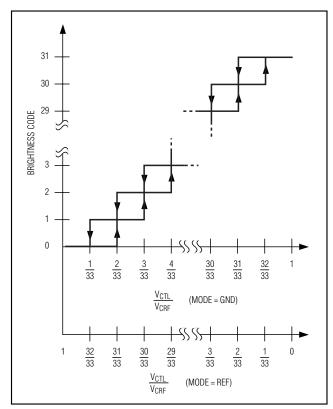

The MAX1996A's analog interface uses an internal ADC with 1-bit hysteresis to generate the brightness code used to dim the lamp (see the *Dimming Range* section). CTL/SCL is the ADC's input and CRF/SDA is its reference voltage. The ADC can operate in either positive-scale ADC mode or negative-scale ADC mode. In positive-scale ADC mode, the brightness code increases from 0 to 31 as VCTL increases from zero to VCRF.

In negative-scale mode, the brightness scale decreases from 31 to zero as VCTL increases from zero to VCRF.

**COMBINED POWER LEVEL (BOTH**

Figure 5. DPWM Settings

Figure 6. Combined Power Level

## **Table 2. MINDAC Functionality**

| CONDITION                                  | FUNCTION                                                                                                                          |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| MINDAC = V <sub>CC</sub>                   | DPWM disabled (always on 100% duty cycle). Operates in lamp-current control only. (Use V <sub>MINDAC</sub> = 0 in the equations.) |

| MINDAC = REF                               | DPWM control enabled, duty cycle ranges from 9% to 100%.  Lamp-current control is disabled (always maximum current).              |

| 0 ≤ V <sub>MINDAC</sub> < V <sub>REF</sub> | The device uses both lamp-current control and DPWM.                                                                               |

## **Table 3. Brightness Adjustment Ranges**

| RANGE                 | POSITIVE-SCALE<br>ADC MODE                        | NEGATIVE-SCALE<br>ADC MODE                               | SMBus                                     | DAC<br>OUTPUT                           | DPWM<br>DUTY<br>CYCLE (%) | COMBINED<br>POWER<br>LEVEL (%) |  |

|-----------------------|---------------------------------------------------|----------------------------------------------------------|-------------------------------------------|-----------------------------------------|---------------------------|--------------------------------|--|

| Maximum<br>Brightness | MODE = GND,<br>VCRF/SDA =<br>VCTL/SCL             | MODE = REF,<br>VCRF/SDA = 0                              | Bright [4:0] = 11111                      | Full-scale<br>DAC output =<br>387.5mV   | 100                       | 100                            |  |

| Minimum<br>Brightness | MODE = GND,<br>VCRF/SDA = 0,<br>VMINDAC = 1/3VREF | MODE = REF,<br>VCRF/SDA = VCTL/SCL,<br>VMINDAC = 1/3VREF | Bright [4:0] = 00000<br>VMINDAC = 1/3VREF | Zero-scale<br>DAC output =<br>VMINDAC/5 | 9                         | 3                              |  |

Note: The current level range is solely determined by the MINDAC to REF ratio and is externally set.

The analog interface's internal ADC uses 1-bit hysteresis to keep the lamp from flickering between two codes.  $V_{CTL}$ 's positive threshold ( $V_{CTL(TH)}$ ) is the voltage required to transition the brightness code as  $V_{CTL}$  increases and can be calculated as follows:

VCTL(TH) = (n + 2) / 33 VCRF (Positive-Scale ADC mode, MODE = GND)

VCTL(TH) = (33 - n) / 33 VCRF (Negative-Scale ADC mode, MODE = REF)

VCTL's negative threshold is the voltage required to transition the brightness code as VCTL decreases and can be calculated as follows:

VCTL(TH) = n / 33 VCRF (Positive-Scale ADC mode, MODE = GND)

VCTL(TH) = (31 - n) / 33 VCRF (Negative-Scale ADC mode, MODE = REF)

where n is the brightness code. See Figure 7 for a graphical representation of the thresholds.

Figure 7. Brightness Code

Figure 8. Analog Interface for Dimming

See the *Digital Interface* section for instructions on using the SMBus interface.

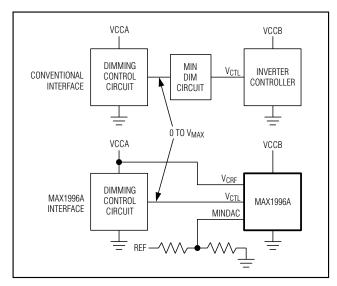

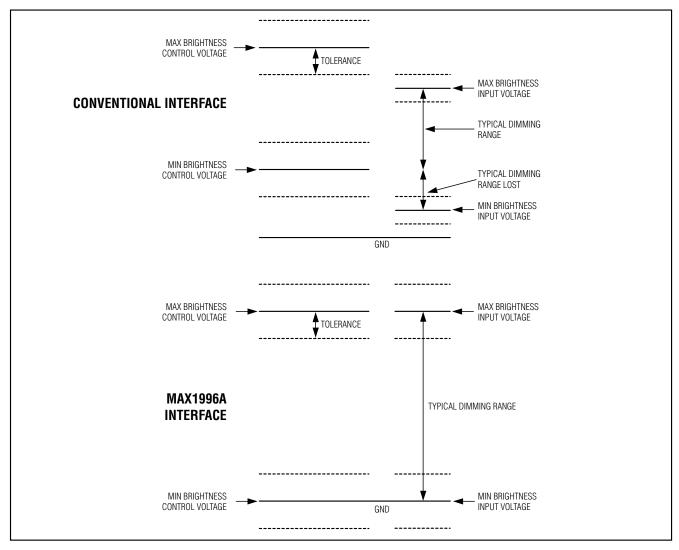

Unlike conventional dimming control circuits that have separate supplies and require additional minimum brightness circuitry, the MAX1996A provides dedicated pins for dimming control. The advantages of the MAX1996A's analog interface are illustrated in Figure 8. The analog interface is very simple in that the output voltage range of the dimming control circuit matches the input voltage range of the inverter control IC. With this method, it is possible to guarantee the maximum dimming range (Figure 9). For the conventional interface, the control voltage and the input voltage have different ranges. To avoid nonuniform lighting across the CCFL tube, or the thermometer effect, the lower limits of maximum and minimum control voltages have to be above the upper limits of the maximum and minimum input voltages, respectively. Therefore, the useful dimming range is reduced. For the MAX1996A's analog interface, the control voltage has the same range as the input voltage, so the useful dimming range is maximized.

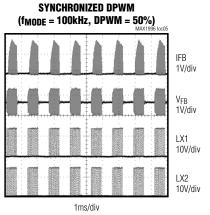

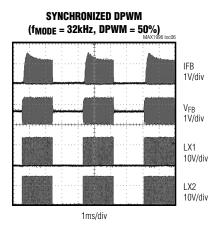

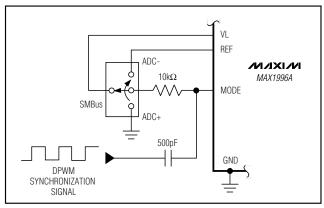

#### Synchronizing the DPWM Frequency

MODE has two functions: one is to select the interface mode as described in the *Interface Selection* section and the other is to synchronize the DPWM chopping frequency to an external signal to prevent unwanted artifacts in the display screen.

To synchronize the DPWM frequency, connect MODE to VCC, REF, or GND through a  $10 k \Omega$  resistor. Then connect

Figure 9. Useful Dimming Range

a 500pF capacitor from an AC signal source to MODE as shown in Figure 10. The amplitude of the AC signal must be at least 2VP-P but no greater than 5VP-P for accurate operation. The transition time of the AC signal should be less than 200µs. The synchronization range is 32kHz to 100kHz, which corresponds to a DPWM frequency range of 250Hz to 781Hz (128 MODE pulses per DPWM cycle). High DPWM frequencies limit the dimming range. See the *Loop Compensation* section for more information concerning high DPWM frequencies.

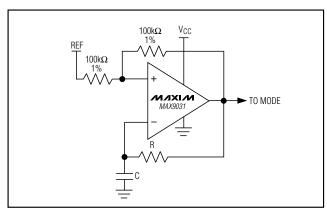

A simple oscillator circuit as shown in Figure 11 can be used to generate the synchronization signal. The core of the oscillator is the MAX9031, which is a low-cost, single-

supply comparator in a 5-pin SC70 package. The  $V_{CC}$  and REF of the MAX1996A provide the supply voltage and the reference voltage for the oscillator. The positive threshold of the oscillator is:  $V_{TH+} = (V_{CC} + V_{REF})/2$ . The negative threshold is given by:  $V_{TH-} = V_{REF}/2$ . The frequency of the oscillator is:

$$f = \frac{1}{RCIn \frac{V_{TH+}(V_{CC} - V_{TH-})}{V_{TH-}(V_{CC} - V_{TH+})}}$$

For C = 330pF and R = 13k $\Omega$ , the resulting oscillator frequency is 100kHz. For C = 330pF and R = 39k $\Omega$ , the oscillator frequency is 32kHz.

Figure 10. DPWM Synchronization

### **POR and UVLO**

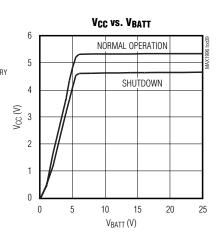

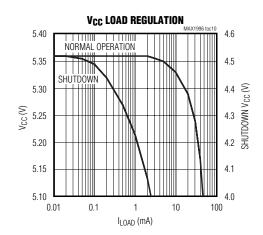

The MAX1996A includes POR and UVLO circuits. The POR resets all internal registers such as DAC output, fault conditions, and all SMBus registers. POR occurs when V<sub>CC</sub> is below 1.5V. The SMBus input-logic thresholds are only guaranteed to meet electrical characteristic limits for V<sub>CC</sub> as low as 3.5V, but the interface continues to function down to the POR threshold.

The UVLO is activated and disables both high-side and low-side switch drivers when V<sub>CC</sub> is below 4.2V (typ).

#### **Low-Power Shutdown**

When the MAX1996A is placed in shutdown, all functions of the IC are turned off except for the 5.3V linear regulator that powers all internal registers and the SMBus interface. The SMBus interface is accessible in shutdown. In shutdown, the linear regulator output voltage drops to about 4.5V and the supply current is 6µA (typ), which is the required power to maintain all internal register states. While in shutdown, lamp-out detection and short-circuit detection latches are reset. The device can be placed into shutdown by either writing to the shutdown mode register (SMBus mode only) or with SH/SUS.

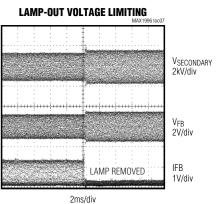

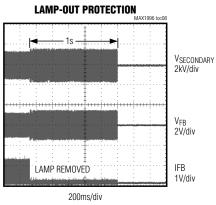

#### **Lamp-Out Detection**

For safety, the MAX1996A monitors the lamp current to detect the open-lamp fault. When the peak voltage on IFB drops below 150mV (IFB regulation point must be set above 48mV) the lamp-out timer starts. Before the timer times out, V<sub>CCI</sub> increases the secondary voltage in an attempt to maintain lamp-current regulation. As V<sub>CCI</sub> rises, V<sub>CCV</sub> rises with it until the secondary voltage reaches its preset limit. At this point, V<sub>CCV</sub> stops and limits the secondary voltage by limiting t<sub>ON</sub>. Because V<sub>CCV</sub> is limited to 150mV above V<sub>CCI</sub>, the voltage control loop is able to quickly limit the secondary voltage.

Figure 11. Simple RC Oscillator

Without this clamping feature, the transformer voltage would overshoot to dangerous levels because VCCV would take more time to slew down from its supply rail. If the peak voltage on IFB does not rise above 150mV before timeout, the MAX1996A shuts down the full bridge.

#### Overcurrent Fault Detection and Protection

The MAX1996A senses overcurrent faults on each switching cycle. The current comparator monitors the voltage drop from LX\_ to GND. If the voltage exceeds the current-limit threshold, the regulator turns off the high-side switch to prevent the transformer primary current from increasing further.

## **Applications Information**

The MAX1996A's standard application circuit, shown in Figure 1, regulates the current of a 4.5W CCFL. The IC's analog voltage interface sets the lamp brightness with a greater than 30 to 1 power adjustment range. This circuit operates from a wide supply voltage range of 4.6V to 28V. Typical applications for this circuit include notebook, desktop monitor, and car navigation displays. Table 4 shows the recommended components for the power stage of the 4.5W application. To select the correct component values, several CCFL parameters (Table 6) and the DC input characteristics must be specified.

#### **MOSFETs**

The MAX1996A requires four external switches—NL1, NL2, NH1, and NH2—to form a full bridge to drive CCFL. The regulator senses drain-to-source voltage of NL1 and NL2 to detect the transformer primary minimum current crossing and overcurrent fault condition. RDSON of NL1 and NL2 should be matched. Select a dual logic-level N-

**Table 4. Components for the Standard Application Circuit**

| DESIGNATION         | DESCRIPTION                                   | RECOMMENDED DEVICE              | MANUFACTURER                                  |  |  |

|---------------------|-----------------------------------------------|---------------------------------|-----------------------------------------------|--|--|

| C1                  | 4.7uF 25V VED coromic conscitor               | TMK325BJ475MN                   | Taiyo Yuden<br>www.t-yuden.com                |  |  |

| CI                  | 4.7μF, 25V X5R ceramic capacitor              | C3225X7R1E475M                  | TDK<br>www.tdk.com                            |  |  |

| C2                  | 1μF, 25V X7R ceramic capacitor                | TMK316BJ105KL<br>C3216X7R1E105K | Taiyo Yuden<br>TDK                            |  |  |

| C3                  | 15pF, 3.1kV high-voltage ceramic capacitor    | GHM1038-SL-150J-3K              | Murata<br>www.murata.com                      |  |  |

|                     | Capacitoi                                     | C4520C0G3F150K                  | TDK                                           |  |  |

| C4                  | 0.015µF, 16V X7R ceramic capacitor            | EMK105BJ153KV                   | Taiyo Yuden                                   |  |  |

| 04                  | 0.015µF, 16V A/A Ceramic capacitor            | GRM36X7R153K016                 | Murata                                        |  |  |

|                     |                                               | LMK105BJ104MV                   | Taiyo Yuden                                   |  |  |

| C5-C8, C10          | 0.1µF,10V X5R ceramic capacitors              | GRM36X5R104K010                 | Murata                                        |  |  |

|                     |                                               | C10055R1A104K                   | TDK                                           |  |  |

| С9                  | 0.01µF, 16V X7R ceramic capacitor             | ECJ-0EB1C103K                   | Panasonic www.panasonic.com                   |  |  |

|                     |                                               | MMBD4148SE                      | Fairchild Semiconductor www.fairchildsemi.com |  |  |

| D1                  | 100mA dual-series diode                       | MMBD7000                        | General Semiconductor www.gensemi.com         |  |  |

|                     |                                               | CMPD7000                        | Central Semiconductor www.centralsemi.com     |  |  |

| D2                  | 100mA dual Schottky diode common anode        | BAT54AW                         | Diodes Incorporated www.diodes.com            |  |  |

|                     | diode common anode                            | CMSSH-3A                        | Central Semiconductor                         |  |  |

| NII 1 / NII 1       | D 111 1 1100555                               | FDC6561AN                       | Fairchild Semiconductor                       |  |  |

| NH1/NL1,<br>NH2/NL2 | Dual N-channel MOSFETs (30V, 0.095Ω, SOT23-6) | TPC6201                         | Toshiba<br>www.toshiba.com                    |  |  |

| R1                  | 150Ω ±1% resistor                             | _                               | _                                             |  |  |

| R2                  | 2kΩ ±5% resistor                              | _                               | _                                             |  |  |

| R3                  | 100kΩ ±1% resistor                            | _                               | _                                             |  |  |

| R4                  | 49.9kΩ ±1% resistor                           | _                               | _                                             |  |  |

| T1                  | 1:100 transformer                             | T912MG-1018                     | Toko<br>www.tokoam.com                        |  |  |

channel MOSFET with low R<sub>DSON</sub> to minimize conduction loss for NL1/NL2 and NH1/NH2 (Fairchild FDC6561). The regulator softly turns on each of four switches in the full bridge. ZVS occurs when the external power MOSFETs are turned on while their respective drain-to-source voltages are near zero volts. ZVS effectively eliminates the MOSFET transition losses caused by CRSS (drain-to-

source capacitance) and parasitic capacitance discharge. ZVS improves efficiency and reduces switching-related EMI.

#### **Current-Sense Resistor**

The MAX1996A regulates the CCFL average current through sense resistor R1 in Figure 1. The voltage at

IFB is the half-wave rectified representation of the current through the lamp. The inverter regulates the average voltage at IFB, which is controlled by either the analog interface or the SMBus interface. To set the maximum lamp RMS current, determine R1 as follows: R1 = 0.444V/ICCFL, RMS, MAX, where ICCFL, RMS, MAX is the maximum RMS lamp current. MINDAC and the wave shape influence the actual maximum RMS lamp current. If necessary, use an RMS current meter to make final adjustments to R1.

#### **Voltage-Sense Capacitors**

The MAX1996A limits the transformer secondary voltage during open-lamp fault through the capacitive divider C3/C4. The voltage of VFB is proportional to CCFL voltage. To set the maximum RMS secondary transformer voltage, choose C3 around 10pF to 22pF, and select C4 such that C4 =  $V_{T(MAX)}/1.11V \times C3$ , where  $V_{T(MAX)}$  comprises the maximum RMS secondary transformer voltage (above the strike voltage). R2 sets the VFB DC bias point to zero volts. Choose R2 =  $10/(C4 \times 6.28 \times F_{SW})$ , where FSW is the nominal resonant operating frequency.

#### **Loop Compensation**

CCI sets the speed of the current loop that is used during startup, maintaining lamp-current regulation, and during transients, caused by changing the lamp-current settling. The typical CCI capacitor value is 0.1µF. Larger values limit lamp-current overshoot, but increase setting time. Smaller values speed up its response time, but extremely small values can lead to instability.

CCV sets the speed of the voltage loop that affects start-up, DPWM transients, and operation in an open-tube fault condition. If DPWM is not used, the voltage control loop should only be active during startup or an open-lamp fault. The CCV capacitors typical value is 0.01µF. Use the smallest value of CCV capacitor necessary to set an acceptable fault-transient response and not cause excessive ringing at the beginning of a DPWM pulse. Larger CCV capacitor values reduce transient overshoot, but can degrade regulation at low DPWM duty cycles by increasing the delay to strike voltage.

#### **Resonant Components**

The MAX1996A works well with air-gap transformers with turns ratio N in the order of Np:Ns = 1:90 to 1:100 for most applications. The transformer secondary resonant frequency must be controlled. A low-profile CCFL transformer typically operates between 50kHz ( $F_{min}$ ) and 200kHz ( $F_{max}$ ). Transformer T1, DC blocking capacitor C2, parallel capacitor C3, and the CCFL lamp form a resonant tank. The resonant frequency is

determined by the transformer secondary leakage inductance L, C2, and C3. The tank is a bandpass filter whose lower frequency is bounded by L, N, and C2. N is the transformer's turns ratio. Choose  $C2 \le N^2$  (10 ×  $F^2_{MIN} \times L$ ). The upper frequency is bounded by L and C3. Choose  $C3 \ge 1/(40 \times F^2_{MIN} \times L)$ .

### **Other Components**

The high-side MOSFET drivers (GH1 and GH2) are powered by the external bootstrap circuit formed by D2, C5, and C6. Connect BST1/BST2 through a dual signal-level Schottky diode D2 to V<sub>DD</sub>, and connect it to LX1/LX2 with 0.1µF ceramic capacitors. Use a dual-series signal-level diode (D1) to generate the half-wave rectified current-sense voltage across R1. The current through these diodes is the lamp current.

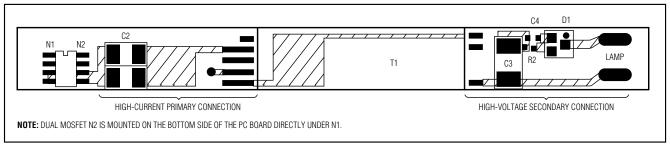

#### **Dual-Lamp Regulator**

The MAX1996A can be used to drive two CCFL tubes as shown in Figure 12. See Table 5 for component selection. The circuit consists of two identical transformers with primary windings connected in parallel and secondary windings in series. The two transformers can also be replaced with a single transformer, which has one primary winding and two secondary windings. The advantage of the series secondary windings is that the same current flows through both lamps, resulting in approximately the same brightness.

In normal operation, C12 is charged to approximately 6V biasing N1 on, which permits current to flow in the loop as follows: in the first half cycle, current flows through the secondary winding of T1, CCFL1, diode D1, MOSFET N1, sense resistor R1, zener diode D4 (forward bias), CCFL2, and finally returning to T2. In the second half cycle, the lamp current flows through T2, CCFL2, D4 (breakdown), D3 (forward bias), CCFL1, and back to T1.