19-1489; Rev 0; 12/00

##

## GSM Cellular/PCN Handset RF Power Management IC

#### **General Description**

The MAX1727 is a radio frequency (RF) power-management IC intended for Global Satellite Mobile (GSM) communication cellular and personal cellular network (PCN) handsets using a single lithium-ion (Li+) cell battery with inputs from +3.1V to +5.5V. The IC contains four low-noise, low-dropout (LDO) linear regulators to provide all the supply voltage requirements for the RF portion of the handset, and two high-speed, wide-bandwidth op amps for the power amplifier (PA) power control loop.

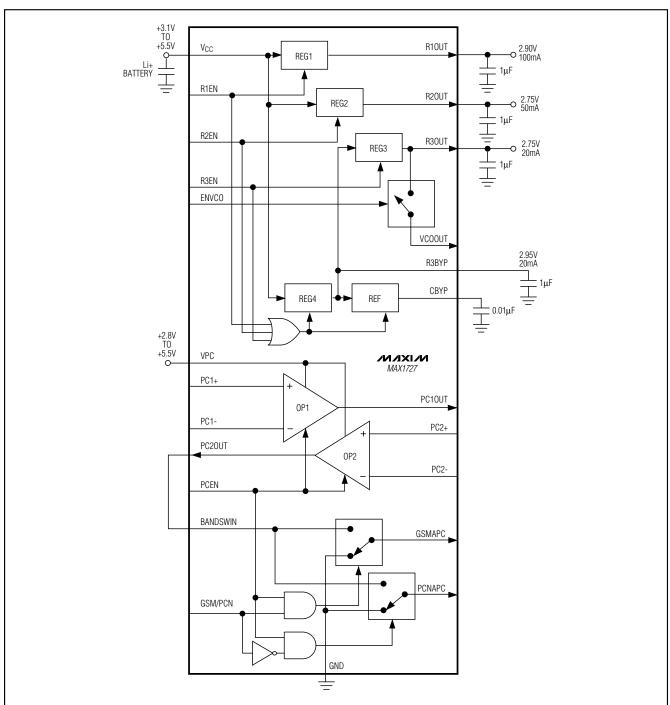

Each LDO has its own individual on/off control to maximize design flexibility. All LDOs are internally trimmed to a fixed output voltage and are optimized for low noise and high crosstalk isolation. LDO1 (R1OUT) is rated for 100µA and is optimized for lowest quiescent current. It is intended to power the transmitter, receiver, and synthesizer. LDO2 (R2OUT) is rated for 50mA. It is intended to power the TCXO, GSM, and PCN highpower voltage-controlled oscillators (VCOs). LDO3 (R3OUT) is rated for 20mA and is optimized to suppress line transients. It is intended to power the UHF offset VCO. LDO3 has an auxiliary  $2.5\Omega$  switched output to allow the VCO to be powered up with precise timing. LDO4 (R3BYP) is rated for 20mA. It is intended to power this IC's reference and LDO3 for superior line rejection. LDO4 and the reference will be powered on if any of the R1EN, R2EN, and R3EN enable inputs are logic high.

The op amps have wide bandwidth, high DC accuracy. high slew rate, and Rail-to-Rail® inputs and outputs. The op amps can sink and source 3mA, and include two  $2.5\Omega$  switched outputs. The op amps and switched outputs may be used independently or may be configured to provide optimized power for a PA control loop.

## **Applications**

GSM Cellular or PCN Handsets Single-Cell Li+ Systems 3-Cell NiMH, NiCD, or Alkaline Systems

Typical Application Circuit and Functional Diagram appear at end of data sheet.

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

#### **Features**

- One 2.90V, 100mA Low IQ LDO

- One 2.75V, 50mA Low IQ LDO

- One 2.75V, 20mA Low IQ LDO

- ♦ Low-Noise LDOs

- <90µVRMS from 10Hz to 100kHz >80dB Crosstalk Isolation at 10kHz >70dB PSRR at 1kHz

- ±5% Accuracy Over Line, Load, and Temperature

- ◆ Three 2.5Ω Switched Outputs

- **Current and Thermal Limit**

- ♦ Two Undedicated Op Amps Rail-to-Rail CMR Inputs and Outputs >120dB Channel Separation >85dB PSRR at 1kHz

- ♦ 10µA (max) Shutdown Current

## Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1727EUG | -40°C to +85°C | 24 TSSOP    |

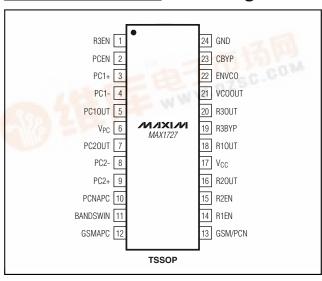

## Pin Configuration

#### **ABSOLUTE MAXIMUM RATINGS**

| V V to CND                     | 0.01/+071/                       |

|--------------------------------|----------------------------------|

| VCC, VPC to GND                |                                  |

| PC1-, PC1+, PC2-, PC2+ to GND. | 0.3V to +7V                      |

| GSM/PCN, BANDSWIN to GND       | 0.3V to +7V                      |

| PC1OUT, PC2OUT to GND          | 0.3V to +7V                      |

| R1OUT, R2OUT, R3BYP to GND     | 0.3V to (V <sub>CC</sub> + 0.3V) |

| R3OUT, CBYP to GND             | 0.3V to (VR3BYP + 0.3V)          |

| R1EN, R2EN, R3EN, ENVCO,       | · ·                              |

| PCEN to GND                    | 0.3V to (VCC + 0.3V)             |

| VCOOUT to GND                  | 0.3V to (VR3QUT + 0.3V)          |

| GSMAPC, PCNAPC to GND0.3V to (VBANDSWIN               | + 0.3V) |

|-------------------------------------------------------|---------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |         |

| 24-Pin TSSOP (derate 12.2mW/°C above +70°C)           | 975mW   |

| Operating Temperature Range40°C to                    | +85°C   |

| Junction Temperature                                  | +150°C  |

| Storage Temperature Range65°C to                      |         |

| Lead Temperature(soldering, 10s)                      | +300°C  |

|                                                       |         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.1 \text{V to } +5.5 \text{V}, V_{PC} = +2.8 \text{V to } +5.5 \text{V}, \text{GND} = 0, C_{BYP} = 0.01 \mu\text{F}, \textbf{T_A} = \textbf{0}^{\circ}\textbf{C} \text{ to } +\textbf{85}^{\circ}\textbf{C}, \text{ unless otherwise noted. Typical values are at T_A = +25°C.})$

| PARAMETER                                        | CONDITIONS                                                       | MIN      | TYP   | MAX   | UNITS |

|--------------------------------------------------|------------------------------------------------------------------|----------|-------|-------|-------|

| V <sub>CC</sub> Operating Voltage                |                                                                  | 3.1      |       | 5.5   | V     |

| V <sub>PC</sub> Operating Voltage                |                                                                  | 2.8      |       | 5.5   | V     |

| UVLO Falling                                     | V <sub>CC</sub> falling                                          | 2.3      | 2.4   |       | V     |

| UVLO Rising                                      | V <sub>CC</sub> rising                                           |          | 2.5   | 2.62  | V     |

| SUPPLY CURRENT                                   | ·                                                                | <u> </u> |       |       |       |

| Supply Current in Shutdown                       | All regulators and op amps off, V <sub>CC</sub> = +3.6V          |          | 0.01  | 10    | μА    |

| V <sub>CC</sub> + V <sub>PC</sub> Supply Current | All regulators and op amps on, V <sub>CC</sub> = V <sub>PC</sub> |          | 1.80  | 3.0   | mA    |

| REFERENCE                                        |                                                                  |          |       |       |       |

| Reference Bypass Output                          | ICBYP = 0, do not draw current from this pin                     | 1.225    | 1.250 | 1.275 | V     |

| REF Supply Rejection                             | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V                                  |          | 0.2   | 5     | mV    |

| REGULATOR R1                                     |                                                                  |          |       |       |       |

| R1OUT Output Voltage                             | 0.1mA ≤ I <sub>R1OUT</sub> ≤ 100mA                               | 2.80     | 2.90  | 3.00  | V     |

| Dung suit Valta su                               | I <sub>R1OUT</sub> = 1mA                                         |          | 1     |       | mV    |

| Dropout Voltage                                  | I <sub>R1OUT</sub> = 100mA                                       |          | 100   | 225   |       |

| Load Regulation                                  | 0.1mA ≤ I <sub>R1OUT</sub> ≤ 100mA                               |          | 8     | 45    | mV    |

| Line Regulation                                  | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V, I <sub>R1OUT</sub> = 10mA       |          | 0.5   | 10    | mV    |

| R10UT Leakage Current                            | R1EN, R1OUT = 0, V <sub>CC</sub> = +5.5V                         |          |       | 2     | μΑ    |

| REGULATOR R2                                     | ·                                                                | <u> </u> |       |       |       |

| R2OUT Output Voltage                             | 0.1mA ≤ I <sub>R2OUT</sub> ≤ 50mA                                | 2.61     | 2.75  | 2.90  | V     |

| Dung suit Valta su                               | I <sub>R2OUT</sub> = 1mA                                         |          | 1     |       | mV    |

| Dropout Voltage                                  | $I_{R2OUT} = 50mA$                                               |          | 100   | 225   |       |

| Load Regulation                                  | 0.1mA ≤ I <sub>R2OUT</sub> ≤ 50mA                                |          | 8     | 45    | mV    |

| Line Regulation                                  | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V, I <sub>R2OUT</sub> = 10mA       |          | 0.5   | 10    | mV    |

| R2OUT Leakage Current                            | R2EN, R2OUT = 0, V <sub>CC</sub> = +5.5V                         |          |       | 2     | μΑ    |

| REGULATOR R3                                     |                                                                  | <u> </u> |       |       |       |

| R3OUT Output Voltage                             | 0.1mA ≤ I <sub>R3OUT</sub> ≤ 20mA                                | 2.61     | 2.75  | 2.90  | V     |

| Drawa ut Valtaga                                 | IR3OUT = 1mA                                                     |          | 1     |       | mV    |

| Dropout Voltage                                  | I <sub>R3OUT</sub> = 20mA                                        |          | 45    | 100   |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.1V \text{ to } +5.5V, V_{PC} = +2.8V \text{ to } +5.5V, \text{GND} = 0, C_{BYP} = 0.01 \mu\text{F}, \textbf{T}_{A} = \textbf{0}^{\circ}\textbf{C} \textbf{ to } +\textbf{85}^{\circ}\textbf{C}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}\text{C}.)$

| PARAMETER                | CONDITIONS                                                                     | MIN  | TYP  | MAX                   | UNITS |

|--------------------------|--------------------------------------------------------------------------------|------|------|-----------------------|-------|

| Load Regulation          | 0.1mA ≤ I <sub>R3OUT</sub> ≤ 20mA                                              |      | 5    | 45                    | mV    |

| Line Regulation          | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V, I <sub>R3OUT</sub> = 10mA                     |      | 0.2  | 10                    | mV    |

| R3OUT Leakage Current    | R3EN, R3OUT = 0, V <sub>CC</sub> = +5.5V                                       |      |      | 2                     | μΑ    |

| VCOOUT SWITCH (R3 SWITCH | <del> </del>                                                                   |      |      |                       |       |

| On-Resistance            |                                                                                |      | 2.4  | 5.1                   | Ω     |

| REGULATOR R4 (R3BYP)     | •                                                                              |      |      |                       |       |

| R3BYP Output Voltage     | $0.1\text{mA} \le I_{\text{R3BYP}} \le 20\text{mA}$                            | 2.85 | 2.95 | 3.05                  | V     |

| Dropout Voltage          | I <sub>R3BYP</sub> = 1mA                                                       |      | 1    |                       | mV    |

| Dropout Voltage          | $I_{R3BYP} = 20mA$                                                             |      | 45   | 100                   | 1110  |

| Load Regulation          | 0.1mA ≤ I <sub>R3BYP</sub> ≤ 20mA                                              |      | 10   | 45                    | mV    |

| Line Regulation          | $+3.1V \le V_{CC} \le +5.5V$ , $I_{R3BYP} = 10mA$                              |      | 0.7  | 10                    | mV    |

| R3BYP Leakage Current    | R1EN, R2EN, R3EN = 0, R3BYP = 0, V <sub>CC</sub> = +5.5V                       |      |      | 2                     | μА    |

| PA CONTROL OP AMPS (PC1, | PC2)                                                                           |      |      |                       | _     |

| Input Offset Voltage     |                                                                                |      |      | 2                     | mV    |

| Input Bias Current       | $V_{CM} = +0.3V \text{ to } (V_{PC} - 0.3V)$                                   |      |      | 150                   | nA    |

| Input Bias Current       | $V_{CM} = 0$ to $V_{CC}$ ,                                                     |      |      | _                     | ^     |

| Shutdown Mode            | V <sub>PC</sub> = 0, PCEN = GND                                                |      |      | 5                     | μΑ    |

| Input Offset Current     |                                                                                |      |      | 30                    | nA    |

| Input Common-Mode Range  |                                                                                | 0.3  |      | V <sub>PC</sub> - 0.3 | V     |

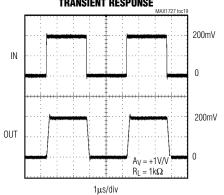

| Gain-Bandwidth Product   | $R_{LOAD}$ = 1kΩ connected to V <sub>PC</sub> /2, $C_{LOAD}$ = 100pF to GND    |      | 4    |                       | MHz   |

| Slew Rate                |                                                                                |      | 1    |                       | V/µs  |

| PSRR                     | 10Hz ≤ f ≤ 1kHz                                                                |      | 85   |                       | dB    |

| CMRR                     | 10Hz ≤ f ≤ 1kHz                                                                |      | 80   |                       | dB    |

| Output Voltage Swing     | I <sub>LOAD</sub> = ±3 mA                                                      | 0.2  |      | 2.62                  | V     |

| BAND SWITCH (GSMAPC, PCI | NAPC)                                                                          | I .  |      |                       |       |

| On-Resistance GSMAPC     | 0.3V < V <sub>GSMAPC</sub> < V <sub>PC</sub> - 0.3V, I <sub>LOAD</sub> = ±3 mA |      | 2.2  | 5                     | Ω     |

| On-Resistance PCNAPC     | 0.3V < V <sub>PCNAPC</sub> < V <sub>PC</sub> - 0.3V, I <sub>LOAD</sub> = ±3 mA |      | 2.2  | 5                     | Ω     |

| LOGIC AND CONTROL INPUT  | S (R1EN, R2EN, R3EN, ENVCO, GSM/PCN, PCEN)                                     | 1    |      |                       |       |

| Input Low Level          |                                                                                |      |      | 0.4                   | V     |

| Input High Level         |                                                                                | 2.0  |      |                       | V     |

| Logic Input Current      | 0 < V <sub>IN</sub> < +5.5V                                                    |      |      | 1                     | μА    |

| THERMAL SHUTDOWN (R3 S)  | I .                                                                            | 1    |      |                       |       |

| Threshold Rising         | · ·                                                                            |      | 150  |                       | °C    |

| Hysteresis               | I <sub>OUT</sub> = 1mA                                                         |      | 20   |                       | °C    |

| •                        |                                                                                | 1    |      |                       | 1     |

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.1 \text{V to } +5.5 \text{V}, V_{PC} = +2.8 \text{V to } +5.5 \text{V}, \text{GND} = 0, C_{BYP} = 0.01 \mu\text{F}, \text{T}_{A} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                         | CONDITIONS                                                 | MIN   | MAX   | UNITS |

|-----------------------------------|------------------------------------------------------------|-------|-------|-------|

| V <sub>CC</sub> Operating Voltage |                                                            | 3.1   | 5.5   | V     |

| V <sub>PC</sub> Operating Voltage |                                                            | 2.8   | 5.5   | V     |

| UVLO Falling                      | V <sub>CC</sub> falling                                    | 2.3   |       | V     |

| UVLO Rising                       | V <sub>CC</sub> rising                                     |       | 2.62  | V     |

| SUPPLY CURRENT                    |                                                            |       |       |       |

| Supply Current in Shutdown        | All regulators and op amps off, V <sub>CC</sub> = +3.6V    |       | 10    | μΑ    |

| V <sub>CC</sub> Supply Current    | All regulators and op amps on                              |       | 3.0   | mA    |

| REFERENCE                         |                                                            |       |       |       |

| Reference Bypass Output           | ICBYP = 0, do not draw current from this pin               | 1.219 | 1.281 | V     |

| REF Supply Rejection              | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V                            |       | 5     | mV    |

| REGULATOR R1                      |                                                            |       |       |       |

| R10UT Output Voltage              | 0.1mA ≤ I <sub>R1OUT</sub> ≤ 100mA                         | 2.80  | 3.00  | V     |

| Dropout Voltage                   | I <sub>R1OUT</sub> = 100mA                                 |       | 225   | mV    |

| Load Regulation                   | 0.1mA ≤ I <sub>R1OUT</sub> ≤ 100mA                         |       | 45    | mV    |

| Line Regulation                   | $+3.1V \le V_{CC} \le +5.5V$ , $I_{R1OUT} = 10mA$          |       | 10    | mV    |

| R1OUT Leakage Current             | R1EN, R1OUT = 0, V <sub>CC</sub> = +5.5V                   |       | 2     | μА    |

| REGULATOR R2                      |                                                            |       |       |       |

| R2OUT Output Voltage              | 0.1mA ≤ I <sub>R2OUT</sub> ≤ 50mA                          | 2.61  | 2.90  | V     |

| Dropout Voltage                   | $I_{R2OUT} = 50mA$                                         |       | 225   | mV    |

| Load Regulation                   | 0.1mA ≤ I <sub>R2OUT</sub> ≤ 50mA                          |       | 45    | mV    |

| Line Regulation                   | $+3.1V \le V_{CC} \le +5.5V$ , $I_{R2OUT} = 10mA$          |       | 10    | mV    |

| R2OUT Leakage Current             | R2EN, R2OUT = 0, V <sub>CC</sub> = +5.5V                   |       | 2     | μΑ    |

| REGULATOR R3                      |                                                            |       |       |       |

| R3OUT Output Voltage              | 0.1mA ≤ I <sub>R3OUT</sub> ≤ 20mA                          | 2.61  | 2.90  | V     |

| Dropout Voltage                   | $I_{R3OUT} = 20mA$                                         |       | 100   | mV    |

| Load Regulation                   | 0.1mA ≤ I <sub>R3OUT</sub> ≤ 20mA                          |       | 45    | mV    |

| Line Regulation                   | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V, I <sub>R3OUT</sub> = 10mA |       | 10    | mV    |

| R3OUT Leakage Current             | R3EN, R3OUT = 0, V <sub>CC</sub> = +5.5V                   |       | 2     | μΑ    |

| VCOOUT SWITCH (R3 SWITC           | CH)                                                        |       |       |       |

| On-Resistance                     |                                                            |       | 5.1   | Ω     |

| REGULATOR R4 (R3BYP)              |                                                            |       |       |       |

| R3BYP Output Voltage              | 0.1mA ≤ I <sub>R3BYP</sub> ≤ 20mA                          | 2.85  | 3.05  | V     |

| Dropout Voltage                   | $I_{R3BYP} = 20mA$                                         |       | 100   | mV    |

| Load Regulation                   | 0.1mA ≤ I <sub>R3BYP</sub> ≤ 20mA                          |       | 45    | mV    |

| Line Regulation                   | +3.1V ≤ V <sub>CC</sub> ≤ +5.5V, I <sub>R3BYP</sub> = 10mA |       | 10    | mV    |

| R3BYP Leakage Current             | R1EN, R2EN, R3EN = 0, R3BYP = 0, V <sub>CC</sub> = +5.5V   |       | 2     | μА    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.1 \text{V to } +5.5 \text{V}, V_{PC} = +2.8 \text{V to } +5.5 \text{V}, \text{GND} = 0, C_{BYP} = 0.01 \mu\text{F}, \textbf{T_A} = -40 ^{\circ} \textbf{C} \text{ to } +85 ^{\circ} \textbf{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                           | CONDITIONS                                                                     | MIN | TYP | MAX                      | UNITS |

|-------------------------------------|--------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| PA CONTROL OP AMPS (PC1,            | PC2)                                                                           | •   |     |                          |       |

| Input Offset Voltage                |                                                                                |     |     | 2                        |       |

| Input Bias Current                  | $V_{CM} = 0.3V \text{ to } (V_{PC} - 0.3V)$                                    |     |     | 150                      | nA    |

| Input Bias Current<br>Shutdown Mode | $V_{CM} = 0$ to $V_{CC}$ ,<br>$V_{PC} = 0$ , $PCEN = GND$                      |     |     | 5                        | μА    |

| Input Offset Current                |                                                                                |     |     | 30                       | nA    |

| Input Common-Mode Range             |                                                                                | 0.3 |     | V <sub>PC</sub><br>- 0.3 | V     |

| Output Voltage Swing                | I <sub>LOAD</sub> = ±3 mA                                                      | 0.2 |     | 2.62                     | V     |

| BAND SWITCH (GSMAPC, PCI            | NAPC)                                                                          |     |     |                          |       |

| On-Resistance GSMAPC                | 0.3V < V <sub>GSMAPC</sub> < V <sub>PC</sub> - 0.3V, I <sub>LOAD</sub> = ±3 mA |     |     | 5                        | Ω     |

| On-Resistance PCNAPC                | 0.3V < VPCNAPC < VPC- 0.3V, ILOAD = ±3 mA                                      |     |     | 5                        | Ω     |

| LOGIC AND CONTROL INPUT             | S (R1EN, R2EN, R3EN, ENVCO, GSM/PCN, PCEN)                                     |     |     |                          |       |

| Input Low Level                     |                                                                                |     |     | 0.4                      | V     |

| Input High Level                    |                                                                                | 2.0 |     |                          | V     |

| Logic Input Current                 | $0 < V_{IN} < +5.5V$                                                           |     |     | 1                        | μΑ    |

Note 1: Specifications to -40°C are guaranteed by design, not production tested.

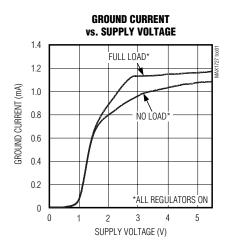

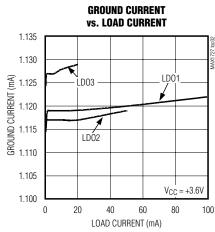

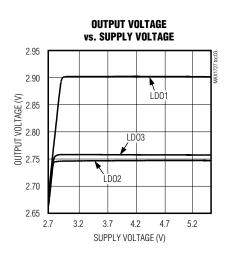

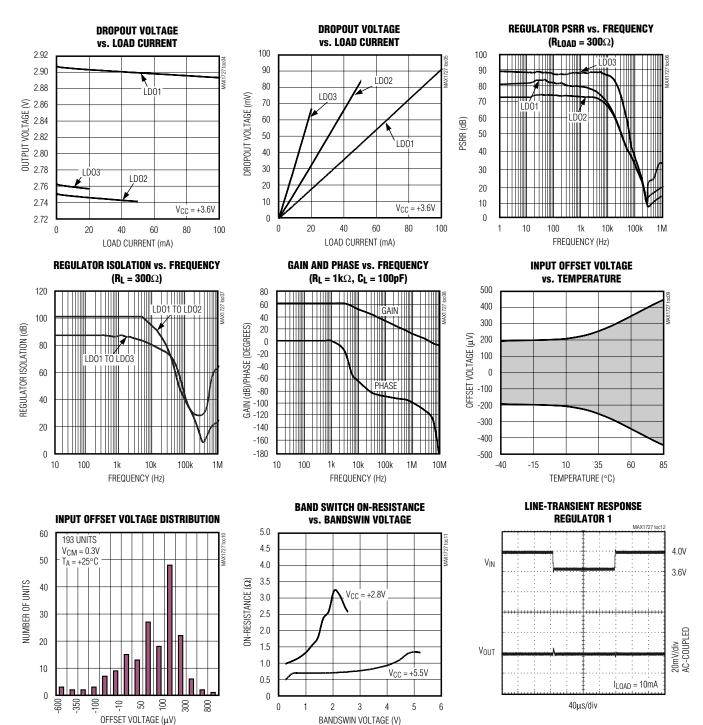

## Typical Operating Characteristics

$(T_A = +25$ °C, unless otherwise noted.)

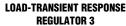

#### Typical Operating Characteristics (continued)

$(T_A = +25$ °C, unless otherwise noted.)

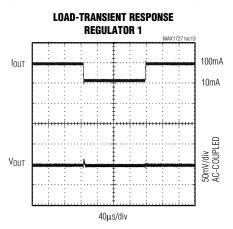

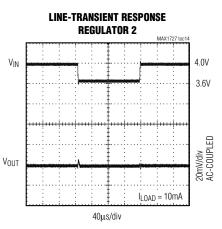

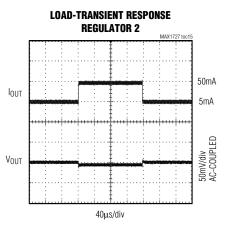

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

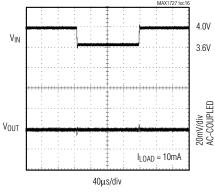

## LINE-TRANSIENT RESPONSE REGULATOR 3

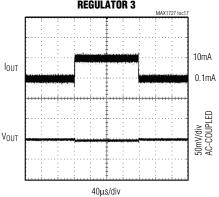

## OP AMP LARGE-SIGNAL TRANSIENT RESPONSE

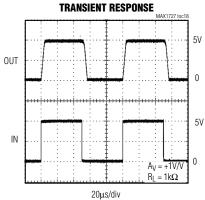

## OP AMP SMALL-SIGNAL TRANSIENT RESPONSE

## Pin Description

| PIN | NAME     | FUNCTION                                                                                                                      |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | R3EN     | Regulator R3 Enable Input                                                                                                     |  |

| 2   | PCEN     | Op Amp and Band Switch Mux Enable Input                                                                                       |  |

| 3   | PC1+     | Op Amp 1 Noninverting Input                                                                                                   |  |

| 4   | PC1-     | Op Amp 1 Inverting Input                                                                                                      |  |

| 5   | PC10UT   | Op Amp 1 Output                                                                                                               |  |

| 6   | VPC      | Op Amp Power Supply                                                                                                           |  |

| 7   | PC2OUT   | Op Amp 2 Output                                                                                                               |  |

| 8   | PC2-     | Op Amp 2 Inverting Input                                                                                                      |  |

| 9   | PC2+     | Op Amp 2 Noninverting Input                                                                                                   |  |

| 10  | PCNAPC   | Band Switch PCN Output. Normally connected to PCN PA APC. Internally shorts to ground when not selected.                      |  |

| 11  | BANDSWIN | Band Switch Input. Normally connected to PC2OUT.                                                                              |  |

| 12  | GSMAPC   | Band Switch GSM Output. Normally connected to GSM PA APC. Internally shorts to ground when not selected.                      |  |

| 13  | GSM/PCN  | Band Switch Control Input. With logic high, BANDSWIN is connected to GSMAPC. With logic low, BANDSWIN is connected to PCNAPC. |  |

| 14  | R1EN     | Regulator R1 Enable Input                                                                                                     |  |

| 15  | R2EN     | Regulator R2 Enable Input                                                                                                     |  |

| 16  | R2OUT    | Output of Linear Regulator 2. 50mA output current. Use 1µF low ESR bypass capacitor to GND.                                   |  |

| 17  | Vcc      | Regulator Power Supply                                                                                                        |  |

| 18  | R1OUT    | Output of Linear Regulator 1. 100mA output current. Use 1µF low ESR bypass capacitor to GND.                                  |  |

| 19  | R3BYP    | Output of Linear Regulator 4. Power supply for regulator R3 and 1.25V reference. Use 1µF low ESR bypass capacitor to GND.     |  |

| 20  | R3OUT    | Output of Linear Regulator 3. 20mA output current. Use 1µF low ESR bypass capacitor to GND.                                   |  |

| 21  | VCOOUT   | Switched R3 Output                                                                                                            |  |

| 22  | ENVCO    | VCO Switch Control Input. With logic high, VCOOUT is connected to R3OUT. With logic low, VCOOUT is high impedance.            |  |

| 23  | СВҮР     | 1.25V Voltage Reference Bypass Pin. Connect low-leakage, 0.01μF bypass capacitor to GND to minimize noise at the output.      |  |

| 24  | GND      | Ground                                                                                                                        |  |

### **Detailed Description**

The MAX1727 is an ideal RF power management IC for the GSM cellular phone. The MAX1727 contains four LDOs, three switches, and two high-speed, high-bandwidth op amps. The LDOs power transmitter, receiver, synthesizer, TCXO, and VCOs. The switches are used to optimize power consumption and to sequence power properly. The op amps provide essential loop control for the PA. The MAX1727 contains all the building blocks necessary to design a high-performance RF circuit (see *Typical Application Circuit*).

The MAX1727 has an input voltage range of +3.1V to +5.5V, perfect for single-cell Li+ cell or 3-cell NiMH battery applications. If any one of LDO1 through LDO3 is enabled, LDO4 and the internal 1.25V reference are powered on. Once LDO4 and the reference voltage reach regulation, the commanded LDOs are powered on. All three LDOs (LDO1, LDO2, LDO3) must be disabled to shut down the internal reference. LDO4 is used as a preregulator to provide extremely high PSRR of 90dB at 1kHz for LDO3. The output current capability of LDO3 and LDO4 is limited to 20mA. LDO4 output can be loaded as long as total current demand by LDO4 load and LDO3 load is less than 20mA.

Clear transmission and reception can only be achieved with a low-noise power supply. All the LDOs of the MAX1727 are designed with <90 $\mu$ VRMS noise from 10Hz to 100kHz, and each LDO achieves >70dB PSRR.

The band switches of the MAX1727 are both grounded when PCEN is in logic low state. When PCEN is in logic high state, GSM/PCN determines the switch positions. If GSM/PCN is low, PCNAPC is engaged. If GSM/PCN is high, GSMAPC output is engaged.

#### **Linear Regulators**

Regulators 1-4 are low-noise, low-dropout, low-quiescent-current linear regulators. Each regulator consists of an error amplifier, internal feedback voltage-divider, and P-channel MOSFET pass transistor. All regulators share a 1.25V reference. The reference is connected to the inverting input of each of the regulator's error amplifiers. The error amplifiers compare the reference with the feedback voltage from each of the regulator outputs and amplify the difference. If the feedback voltage is lower than the reference voltage, the pass transistor gate is pulled lower, which allows more current to pass into the output load to increase the output voltage. If the feedback voltage is too high, the pass transistor gate is pulled up, allowing less current into the load. The feedback is provided by an internal, trimmed resistor-divider connected at each of the regulator outputs.

All the regulators feature high PSRR and excellent load and line regulation characteristics and are designed for single Li+ battery applications where a pulsed current demand is required from the battery. For a load requiring significant isolation from transients on the input, REG3 should be used with REG4 configured as a preregulator to provide improved rejection.

The minimum I/O voltage differential (dropout voltage) determines the lowest usable supply voltage. Once dropout has been reached, the series pass transistor is fully on, and regulation ceases. The output will track the input voltage as the input voltage is further lowered. For a P-channel series pass element (as used here), dropout voltage is a function of drain-to-source on-resistance multiplied by the load current.

Each regulator features a P-channel MOSFET series pass transistor sized to deliver the rated output current for each regulator. A P-channel MOSFET requires almost no drive current to the gate. This significantly reduces the quiescent current compared to bipolar PNP series pass transistor regulators, particularly in dropout when the DC current gain of the PNP transistor is reduced to nearly unity. A MOSFET design retains its low quiescent current even in dropout, with and without load.

#### Reference Bypass

An external bypass capacitor is connected to CBYP to reduce the inherent reference noise. The capacitor forms a lowpass filter in conjunction with an internal network. Use a 0.01µF nonpolarized capacitor connected as close to the CBYP pin as possible. For lowest noise, increase the bypass capacitor to 0.1µF. Values above 100nF provide no performance improvement and are therefore not recommended. Do not place any additional loading on this pin.

#### Regulator Short-Circuit Protection

Each regulator has a separate current-limit circuit within the overall feedback loop. The typical values for current limit are: REG1 = 250mA; REG2/REG3/REG4 = 125mA. Each regulator will survive a continuous short circuit at the output, until the IC thermal limit control powers down all the regulators.

#### **Thermal Overload Protection**

Thermal overload protection limits the total power dissipation by measuring the die temperature. When +150°C is reached, the thermal sensor signals the shutdown logic for all the regulators. Once the die temperature cools by 20°C, the regulators will restart. If the overload persists, the regulators will cycle on and off as the die temperature fluctuates.

#### Capacitor Selection and Regulator Stability

Minimum recommended output capacitance for all the regulators is 1 $\mu$ F with a maximum ESR of 0.4 $\Omega$ . For lower noise requirements, use a 10 $\mu$ F capacitor on each regulator.

Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature. Z5U and Y5V dielectrics may require a minimum value of 2.2µF nominal output capacitance, especially a low temperature operation.

#### **Op Amps**

Two uncommitted unity-gain-stable op amps are available for use in the MAX1727. Gain bandwidth is typically 4MHz and slew rate  $1V/\mu s$ . Gain and phase margins are typically 8dB and 63° when loaded with  $1k\Omega$  and 100pF at the output. The input stages are differential CMOS transistors providing an input common-mode range extending to 300mV within the positive supply rail (VPC) and ground. Input offset voltage is 2mV (max), with bias current of 150nA (max).

A separate supply input is provided for the two op amps, allowing them to be powered by supplies different from REG1–REG4. The amplifier's excellent PSRR to beyond 1kHz allows the supply to be connected directly to the battery. Decouple the supply pin (VPC) with a 0.1µF ceramic capacitor in parallel with at least 1µF. Place the 0.1µF as close to the supply pin as possible. Both op amps have a common logic-controlled shutdown pin, allowing the inputs to remain connected to a supply while reducing quiescent current to a very low level. The op amp supply current is reduced to 5µA during shutdown mode.

The output stages are all CMOS, allowing rail-to-rail swing at the output (load dependent). For a ±3mA load, the output will swing to within 200mV of either the positive supply (VPC) or ground. If an op amp is unused, the positive input should be connected to ground, and the output should be connected back to the negative input. Connecting an unused op amp as a grounded unitygain buffer prevents oscillation and saturation, which causes inconsistent supply-current consumption.

#### **Power Switches**

The MAX1727 contains three  $2.5\Omega$  CMOS switches. One is connected to the REG3 output and is suitable for fast enabling of a load. The other two switches are wired as SPDT switches and are used to route the APC outputs from a loop amplifier. When not required, the APC control is grounded. This prevents spurious power-up of the unused PA and eliminates a low onresistance, high-current switch in series with the PA

power supply. The logic-controlled changeover is gated by the op amp enable line (PCEN).

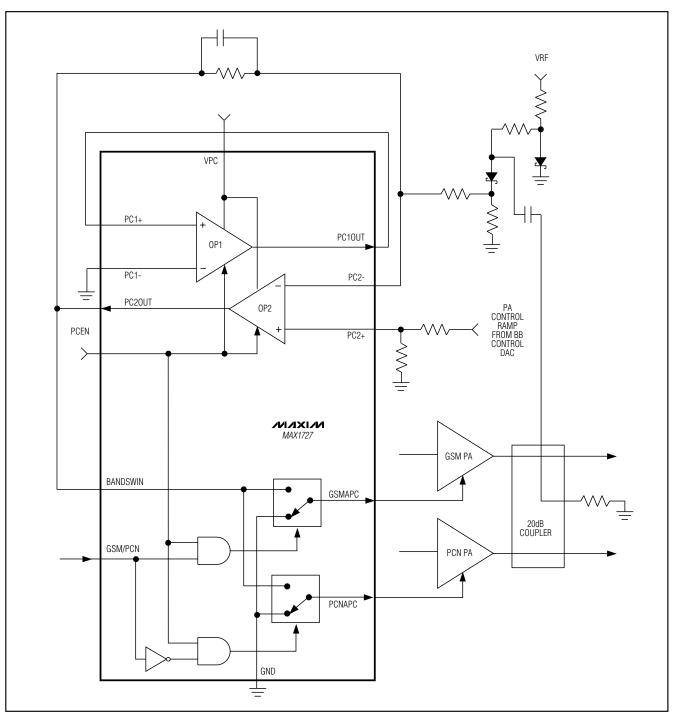

Figure 1 shows a single op amp within the MAX1727 used in a dual PA APC loop. The RF envelope at the active PA output is sampled by the 20dB coupler and detected by the temperature-compensated dual Schottky diode pair. The baseband DAC ramp control is summed with the averaged detected envelope by an inverting integrator stage to produce an APC signal. This is connected to the operational PA by the SPDT switch. The unused PA APC line is grounded. This prevents the unused PA from accidentally powering up. Also, a grounded APC line keeps the PA in a low-quiescent-current standby mode.

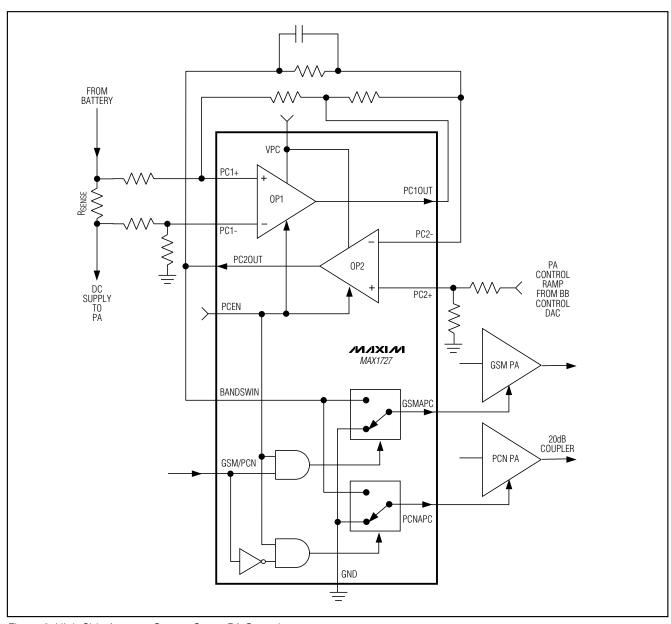

Figure 2 shows an alternative method of PA control where the average DC supply current to the active PA is used as a measure of the average RF power into the load (antenna). The circuit takes advantage of the rail-to-rail performance and CMRR of the op amps. The PA average DC current is sampled by the sense resistor and amplified differentially before summation into the second integrating stage with the baseband ramp DAC signal. As shown in Figure 1, the APC signal is routed through the SPDT switches to the active PA.

Chip Information

TRANSISTOR COUNT: 1324

Figure 1. Single Op Amp PA Automatic Power Control Loop

Figure 2. High-Side Average Current-Sense PA Control

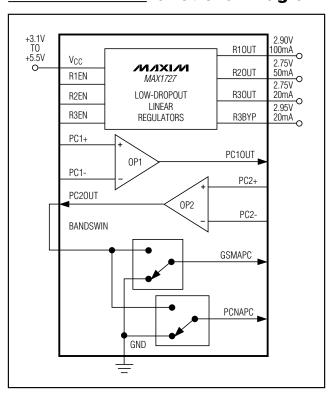

## Typical Application Circuit

## Functional Diagram

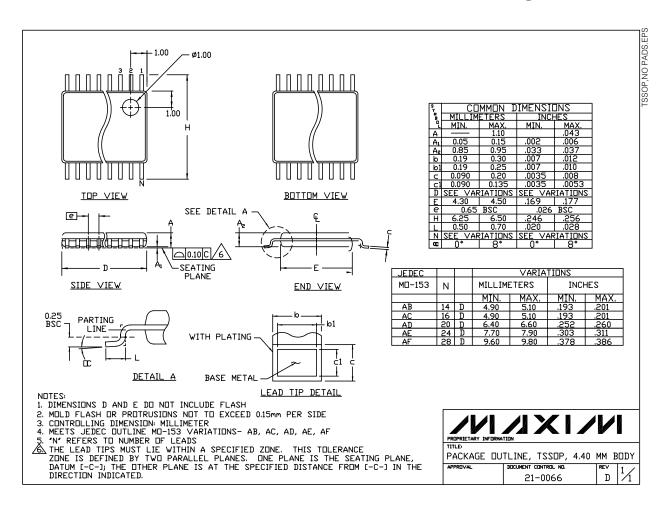

#### **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.