## MULTI-HDLC WITH n x 64 SWITCHING MATRIX ASSOCIATED

- 32 TxHDLCs WITH BROADCASTING CAPA-BILITY AND/OR CSMA/CR FUNCTION WITH AUTOMATIC RESTART IN CASE OF TX FRAME ABORT

- 32 RxHDLCs INCLUDING ADDRESS REC-OGNITION

- 16 COMMAND/INDICATE CHANNELS (4 OR 6-BIT PRIMITIVE)

- 16 MONITOR CHANNELS PROCESSED IN ACCORDANCE WITH GCI OR V\*

- 256 x 256 SWITCHING MATRIX WITHOUT BLOCKING AND WITH TIME SLOT SE-QUENCE INTEGRITY AND LOOPBACK PER BIDIRECTIONAL CONNECTION

- DMA CONTROLLER FOR 32 Tx CHANNELS

AND 32 Rx CHANNELS

- HDLCs AND DMA CONTROLLER ARE CAPA-BLE OF HANDLING A MIX OF LAPD, LAPB, SS7, CAS AND PROPRIETARY SIGNALLINGS

- EXTERNAL SHARED MEMORY ACCESS BE-TWEEN DMA CONTROLLER AND MICRO-PROCESSOR

- SINGLE MEMORY SHARED BETWEEN n x MULTI-HDLCs AND SINGLE MICRO-PROCESSOR ALLOWS TO HANDLE n x 32 CHANNELS

- BUS ARBITRATION

- INTERFACE FOR VARIOUS 8,16 OR 32 BIT MICROPROCESSORS

- RAM CONTROLLER ALLOWS TO INTER-FACE UP TO:

- -16 MEGABYTES OF DYNAMIC RAM OR

- -1 MEGABYTE OF STATIC RAM

- INTERRUPT CONTROLLER TO STORE AUTOMATICALLY EVENTS IN SHARED MEMORY

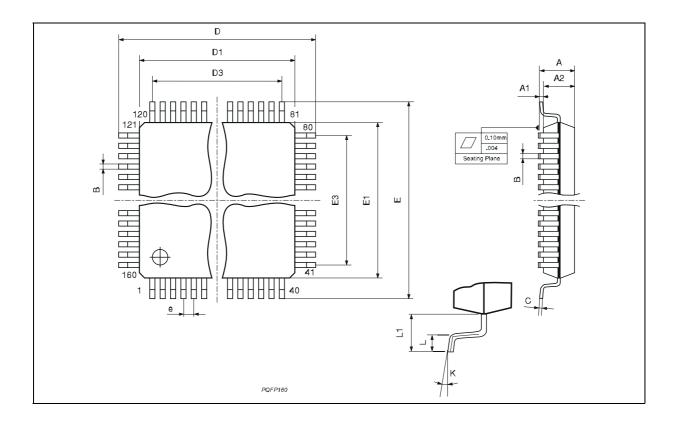

- PQFP160 PACKAGE

- BOUNDARY SCAN FOR TEST FACILITY

#### DESCRIPTION

The STLC5465B is a Subscriber line interface card controller for Central Office, Central Exchange, NT2 and PBX capable of handling:

- 16 U Interfaces or

- 2 Megabits line interface cards or

- 16 SLICs (Plain Old Telephone Service) or

- Mixed analogue and digital Interfaces (SLICs or U Interfaces) or

- 16 S Interfaces

- Switching Network with centralized processing

| TABLE OF CONTENTS Pa                                    | age  |

|---------------------------------------------------------|------|

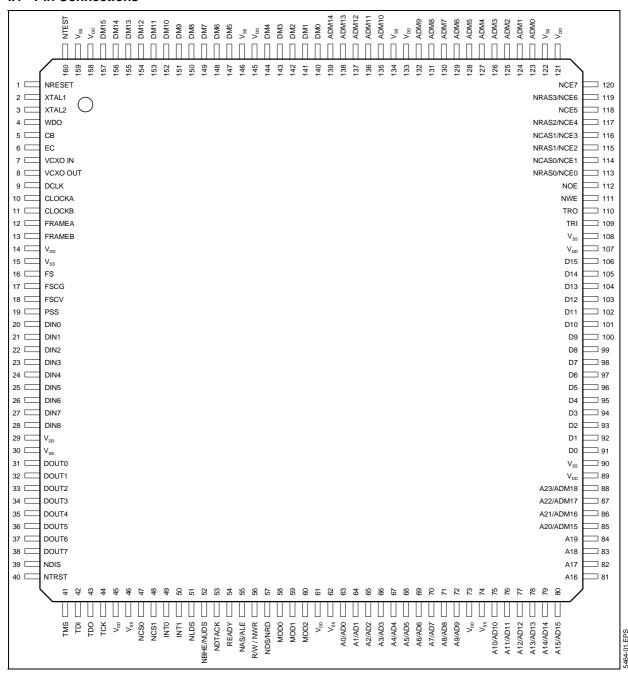

| I - PIN INFORMATION                                     | . 8  |

| I.1 - Pin Connections                                   |      |

| I.2 - Pin Description                                   | . 9  |

| I.3 - Pin Definition                                    |      |

| I.3.1 - Input Pin Definition                            | . 13 |

| I.3.2 - Output Pin Definition                           | . 13 |

| I.3.3 - Input/Output Pin Definition                     |      |

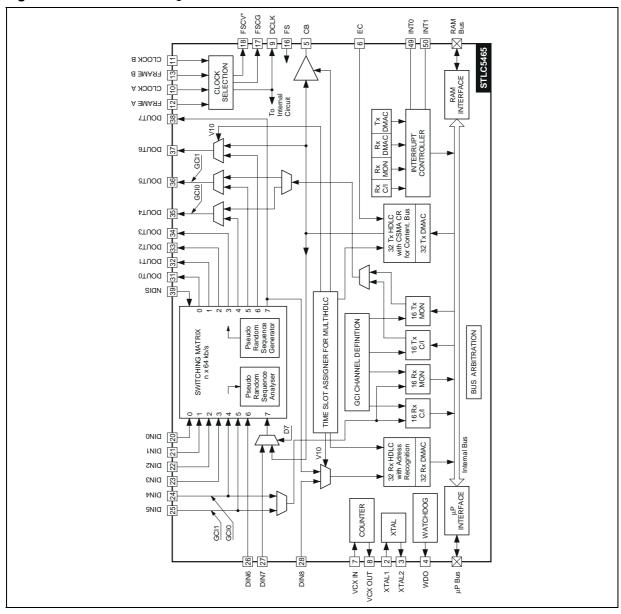

| II - BLOCK DIAGRAM                                      |      |

| III - FUNCTIONAL DESCRIPTION                            |      |

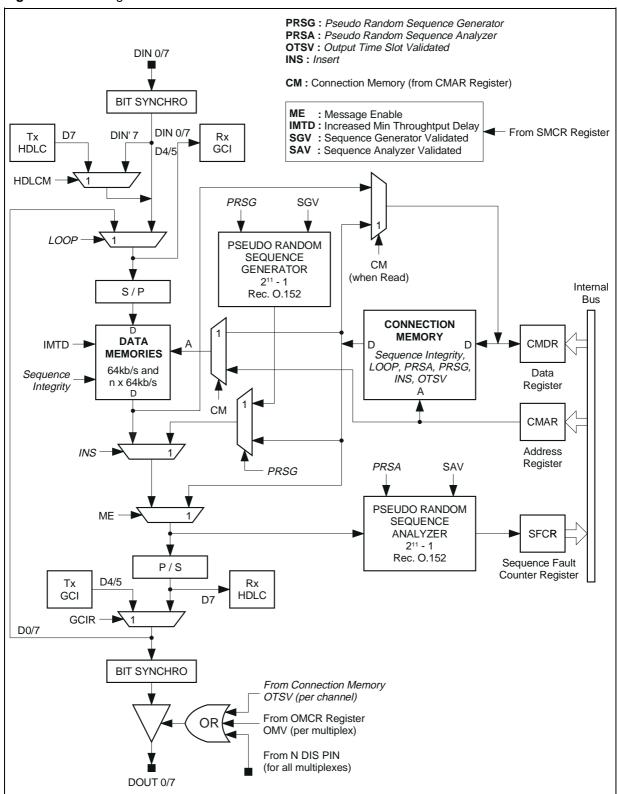

| III.1 - The Switching Matrix N x 64 KBits/S             |      |

| III.1.1 - Function Description                          |      |

| III.1.2 - Architecture of the Matrix                    |      |

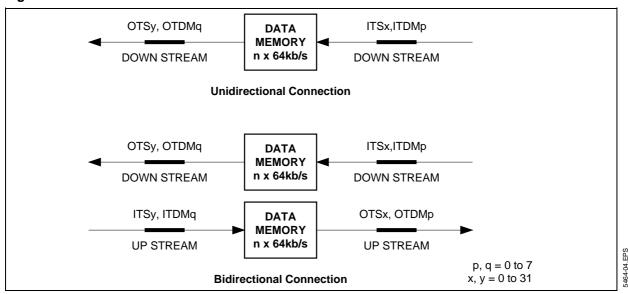

| III.1.3 - Connection Function                           | . 15 |

| III.1.4 - Loop Back Function                            |      |

| III.1.5 - Delay through the Matrix                      |      |

| III.1.5.1 - Variable Delay Mode                         |      |

| III.1.5.2 - Sequence Integrity Mode                     | 17   |

| III.1.6 - Connection Memory                             |      |

| III.1.6.1 - Description                                 |      |

| III.1.6.2 - Access to Connection Memory                 |      |

| III.1.6.3 - Access to Data Memory                       |      |

| III.1.6.4 - Switching at 32 Kbit/s                      |      |

| III.1.6.5 - Switching at 16 kbit/s                      |      |

| III.2 - HDLC Controller                                 |      |

| III.2.1 - Function Description                          |      |

| III.2.1.1 - Format of the HDLC Frame                    |      |

| III.2.1.2 - Composition of an HDLC Frame                |      |

| III.2.1.3 - Description and Functions of the HDLC Bytes |      |

| III.2.2 - CSMA/CR Capability                            |      |

| III.2.3 - Time Slot Assigner Memory                     |      |

| III.2.4 - Data Storage Structure                        | 27   |

| III.2.4.1 - Reception                                   |      |

| III.2.4.2 - Transmission                                |      |

| III.2.4.3 - Frame Relay                                 |      |

| III.2.5 - Transparent Modes                             | 20   |

| III.2.6 - Command of the HDLC Channels                  | 20   |

| III.2.6.1 - Reception Control                           |      |

| III.2.6.2 - Transmission Control                        | 20   |

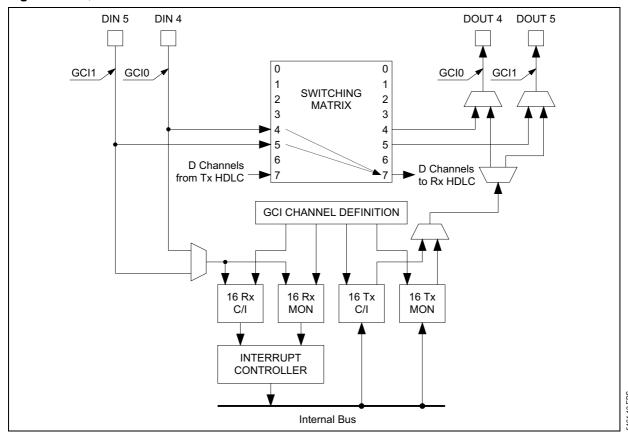

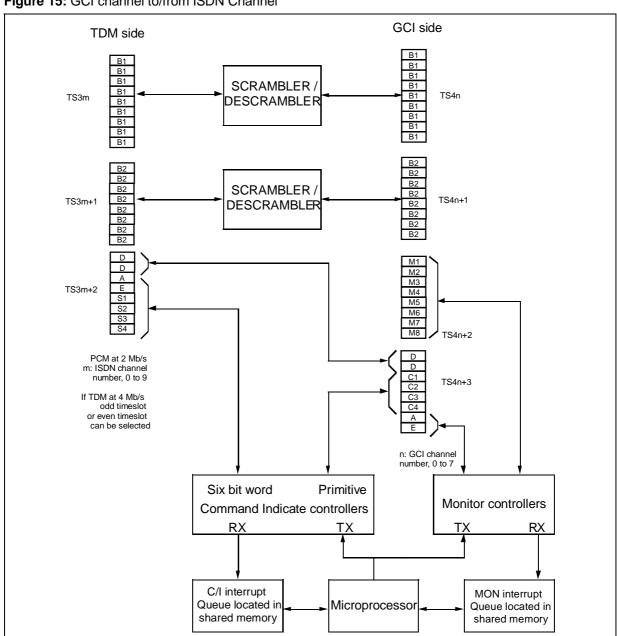

| III.3 - C/I and Monitor                                 |      |

| III.3 - C/I and Monitor                                 |      |

| III.3.1 - Function Description                          |      |

| III.3.2 - GOI and V Protocoi                            |      |

| TABLE OF CONTENTS (continued)                                           | Page |

|-------------------------------------------------------------------------|------|

| III - FUNCTIONAL DESCRIPTION (continued)                                |      |

| III.3.4 - CI and Monitor Channel Configuration                          | 30   |

| III.3.5 - CI and Monitor Transmission/Reception Command                 |      |

| III.4 - Microprocessor Interface                                        |      |

| III.4.1 - Description                                                   |      |

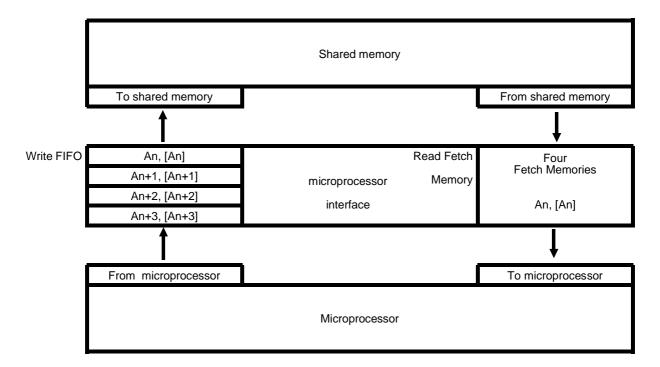

| III.4.2 - Exchange with the shared memory                               |      |

| III.4.2.1 - Write FIFO                                                  |      |

| III.4.2.2 - Read Fetch Memory                                           |      |

| III.4.3 - Definition of the Interface for the different microprocessors |      |

| III.5 - Memory Interface                                                |      |

| III.5.1 - Function Description                                          |      |

| III.5.2 - Choice of memory versus microprocessor and capacity required  |      |

| III.5.3 - Memory Cycle                                                  |      |

| III.5.4 - SRAM interface                                                |      |

| III.5.5 - DRAM Interface                                                |      |

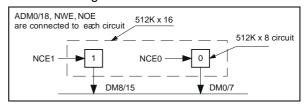

| III.5.4.2 - 512K x n SRAM                                               |      |

| III.5.5.2 - 1M x n DRAM Signals                                         |      |

| III.5.5.3 - 4M x n DRAM Signals                                         |      |

| III.6 - Bus Arbitration                                                 |      |

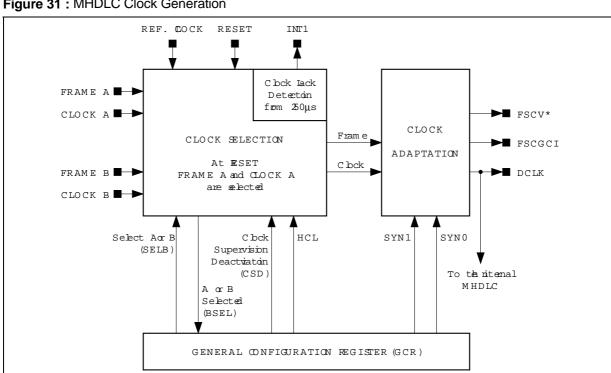

| III.7 - Clock Selection and Time Synchronization                        |      |

| III.7.1 - Clock Distribution Selection and Supervision                  |      |

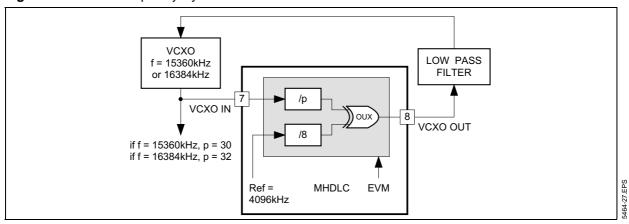

| III.7.2 - VCXO Frequency Synchronization                                |      |

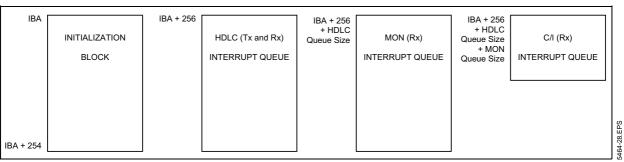

| III.8 - Interrupt Controller                                            |      |

| III.8.1 - Description                                                   |      |

| III.8.2 - Operating Interrupts (INT0 Pin)                               |      |

| III.8.3 - Time Base Interrupts (INT1 Pin)                               |      |

| III.8.4 - Emergency Interrupts (WDO Pin)                                |      |

| III.8.5 - Interrupt Queues                                              |      |

| III.9 - Watchdog                                                        |      |

| III.10 - Reset                                                          |      |

| III.11 - Boundary Scan                                                  |      |

| IV - DC SPECIFICATIONS                                                  |      |

| IV.1 - Absolute Maximum Ratings                                         |      |

| IV.2 - Power Dissipation                                                |      |

| IV.3 - Recommended DC Operating Conditions                              |      |

| IV.4 - TTL Input DC Electrical Characteristics                          |      |

| IV.5 - CMOS Output DC Electrical Characteristics                        |      |

| IV.6 - Protection                                                       |      |

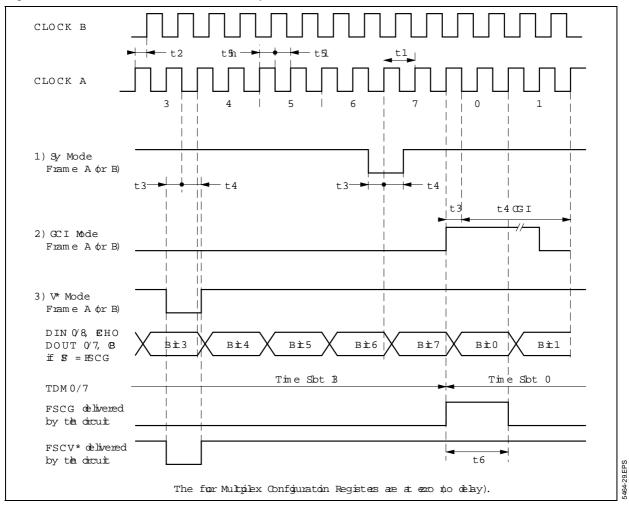

| V - CLOCK TIMING                                                        |      |

| V.1 - Synchronization Signals delivered by the system                   |      |

|                                                                         |      |

| V.2 - TDM Synchronization                                               |      |

|                                                                         | 48   |

| v 4 - v muellace                                                        | 46   |

| TABLE OF CON   | TENTS (continued)                                     | Page   |

|----------------|-------------------------------------------------------|--------|

| V1 - MEMORY T  | IMING                                                 | <br>49 |

|                | nic Memories                                          |        |

|                | Memories                                              |        |

|                | CESSOR TIMING                                         |        |

| VII.1 - ST9 F  | amily MOD0=1, MOD1=0, MOD2=0                          | <br>53 |

| VII.2 - ST10/0 | C16x mult. A/D, MOD0 = 1, MOD1 = 0, MOD2 = 1          | <br>55 |

| VII.3 - ST10/0 | C16x demult. A/D, MOD0 = 1, MOD1 = 0, MOD2 = 1        | <br>57 |

|                | 38 MOD0=1, MOD1=1, MOD2=0                             |        |

| VII.5 - 80C18  | 36 MOD0=1, MOD1=1, MOD2=1                             | <br>61 |

| VII.6 - 68000  | MOD0=0, MOD1=0, MOD2=1                                | <br>63 |

|                | MOD0=0, MOD1=0, MOD2=0                                |        |

|                | Ring Timing                                           |        |

|                | r Clock Timing                                        |        |

|                | REGISTERS                                             |        |

|                | fication and Dynamic Command Register - IDCR (00)H    |        |

| VIII.2 - Gene  | ral Configuration - GCR (02)H                         | <br>68 |

| VIII.3 - Input | Multiplex Configuration Register 0 - IMCR0 (04)H      | <br>70 |

| VIII.4 - Input | Multiplex Configuration Register 1 - IMCR1 (06)H      | <br>70 |

|                | ut Multiplex Configuration Register 0 - OMCR0 (08)H   |        |

|                | ut Multiplex Configuration Register 1 - OMCR1 (0A)H   |        |

|                | hing Matrix Configuration Register - SMCR (0C)H       |        |

|                | ection Memory Data Register - CMDR (0E)H              |        |

|                | ection Memory Address Register - CMAR (10)H           |        |

|                | uence Fault Counter Register - SFCR (12)H             |        |

|                | e Slot Assigner Address Register - TAAR (14)H         |        |

|                | e Slot Assigner Data Register - TADR (16)H            |        |

|                | .C Transmit Command Register - HTCR (18)H             |        |

|                | .C Receive Command Register - HRCR (1A)H              |        |

|                | ress Field Recognition Address Register - AFRAR (1C)H |        |

|                | ress Field Recognition Data Register - AFRDR (1E)H    |        |

|                | Character Register - FCR (20)H                        |        |

|                | Channels Definition Register 0 - GCIR0 (22)H          |        |

|                | Channels Definition Register 1 - GCIR1 (24)H          |        |

|                | Channels Definition Register 2 - GCIR2 (26)H          |        |

|                | Channels Definition Register 3 - GCIR3 (28)H          |        |

| VIII.22 - Tran | nsmit Command / Indicate Register - TCIR (2A)H        | <br>86 |

| Tran           | smit Command/Indicate Register (after reading)        | <br>86 |

|                | nsmit Monitor Address Register - TMAR (2C)H           |        |

|                | smit Monitor Address Register (after reading)         |        |

|                | smit Monitor Data Register - <b>TMDR (2E)H</b>        |        |

|                | smit Monitor Interrupt Register - TMIR (30)H          |        |

|                | nory Interface Configuration Register - MICR (32)H    |        |

| Men            |                                                       | <br>80 |

| TABLE OF CONTENTS (continued)                              | Page |

|------------------------------------------------------------|------|

| VIII - INTERNAL REGISTERS (continued)                      |      |

| VIII.27 - Initiate Block Address Register - IBAR (34)H     | 90   |

| VIII.28 - Interrupt Queue Size Register - IQSR (36)H       | 90   |

| VIII.29 - Interrupt Register - IR (38)H                    |      |

| VIII.30 - Interrupt Mask Register - IMR (3A)H              |      |

| VIII.31 - Timer Register - TIMR (3C)H                      |      |

| VIII.32 - Test Register - TR (3E)H                         |      |

| IX - EXTERNAL REĞISTERS                                    |      |

| IX.1 - Initialization Block in External Memory             | 93   |

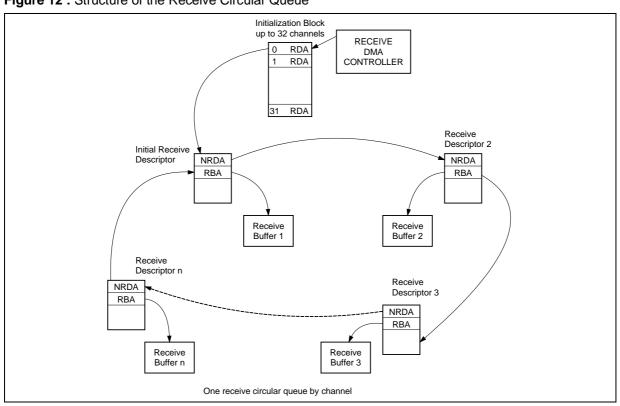

| IX.2 - Receive Descriptor                                  | 94   |

| IX.2.1 - Bits written by the Microprocessor only           |      |

| IX.2.2 - Bits written by the Rx DMAC only                  |      |

| IX.2.3 - Receive Buffer                                    |      |

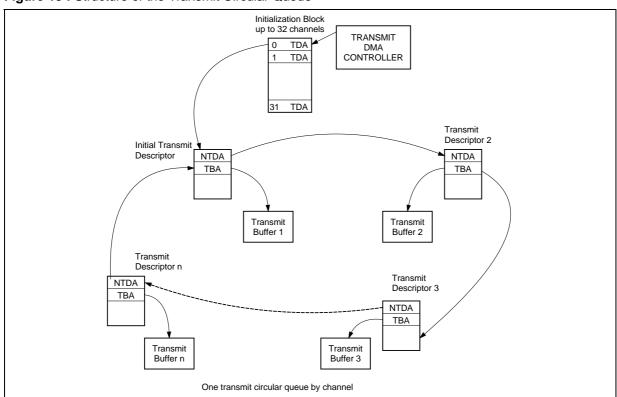

| IX.3 - Transmit Descriptor                                 | 95   |

| IX.3.1 - Bits written by the Microprocessor only           | 95   |

| IX.3.2 - Bits written by the DMAC only                     |      |

| IX.3.3 - Transmit Buffer                                   |      |

| IX.4 - Receive & Transmit HDLC Frame Interrupt             | 96   |

| IX.5 - Receive Command / Indicate Interrupt                |      |

| IX.5.1 - Receive Command / Indicate Interrupt when TSV = 0 | 97   |

| IX.5.2 - Receive Command / Indicate Interrupt when TSV = 1 | 98   |

| IX.6 - Receive Monitor Interrupt                           |      |

| IX.6.1 - Receive Monitor Interrupt when TSV = 0            |      |

| IX.6.2 - Receive Monitor Interrupt when TSV = 1            |      |

| X - POEP160 PACKAGE MECHANICAL DATA                        | 400  |

| LIST OF FIGURES                                                                 | Page |

|---------------------------------------------------------------------------------|------|

| I - PIN INFORMATION                                                             |      |

| II - BLOCK DIAGRAM                                                              |      |

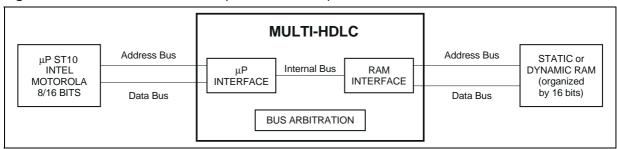

| Figure 1: General Block Diagram                                                 |      |

| III - FUNCTIONAL DESCRIPTION                                                    |      |

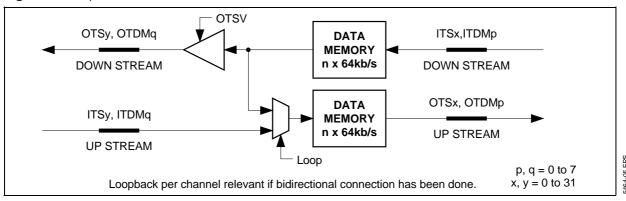

| Figure 2: Switching Matrix Data Path                                            |      |

| Figure 3: Unidirectional and Bidirectional Connections                          | 17   |

| Figure 4: Loop Back                                                             | 17   |

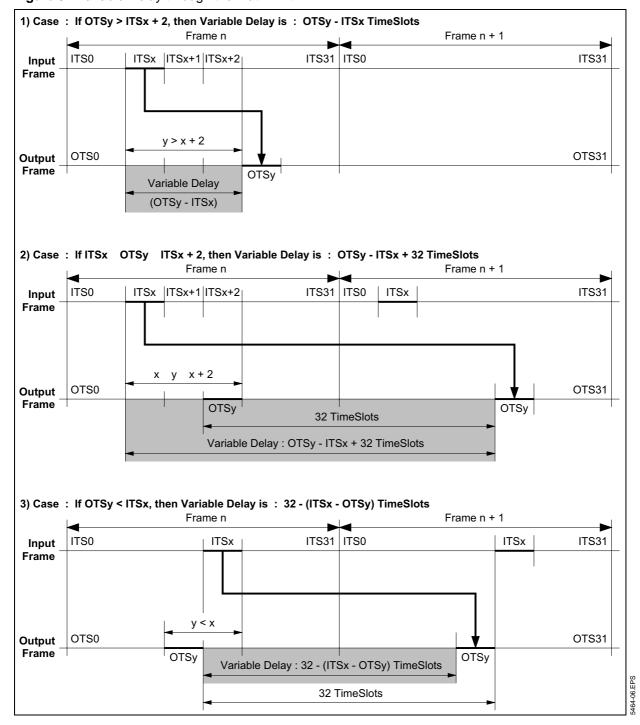

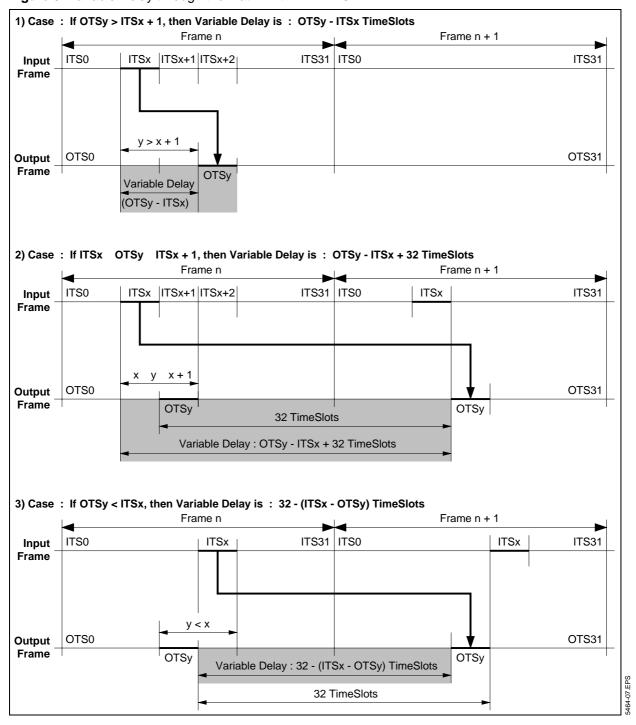

| Figure 5: Variable Delay through the matrix with ITDM = 1                       |      |

| Figure 6: Variable Delay through the matrix with ITDM = 0                       |      |

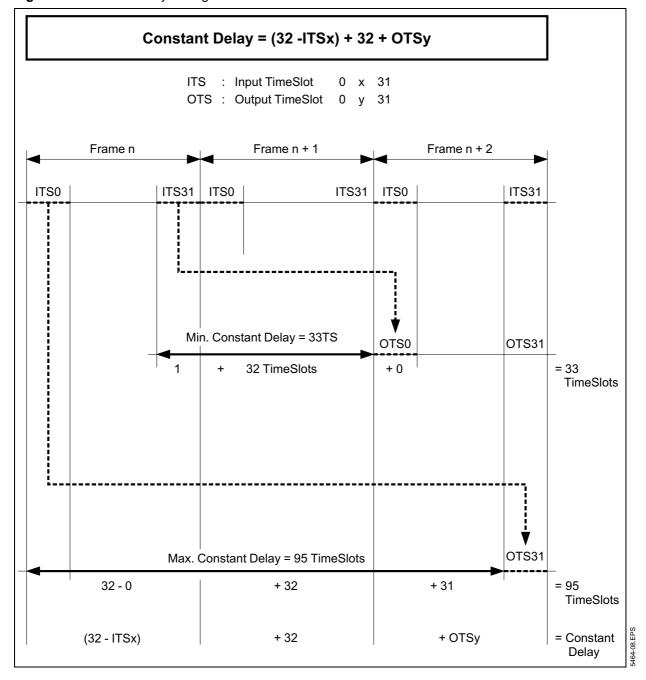

| Figure 7: Constant Delay through the matrix with SI = 1                         |      |

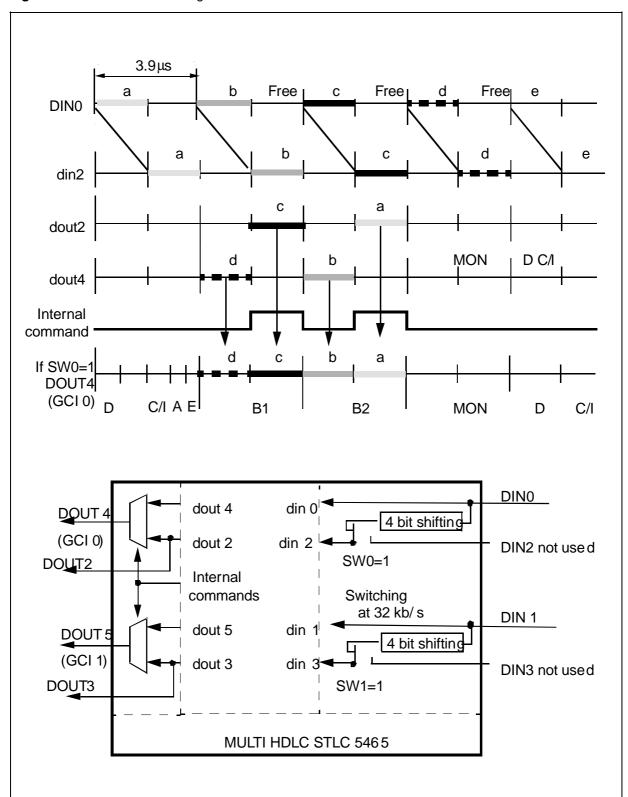

| Figure 8: Downstream Switching at 32kb/s                                        |      |

| Figure 9: Upstream Switching at 32kb/s                                          |      |

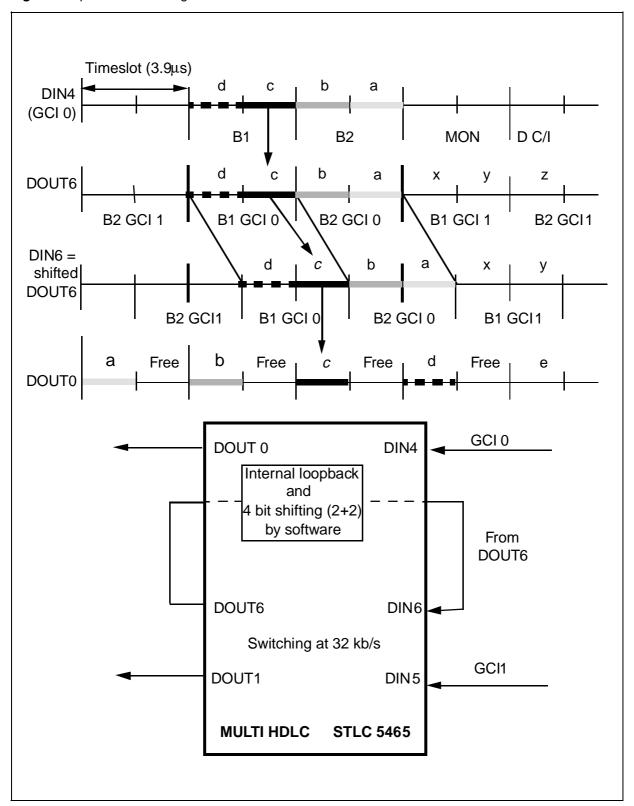

| Figure 10: Upstream and Downstream Switching at 16kb/s                          |      |

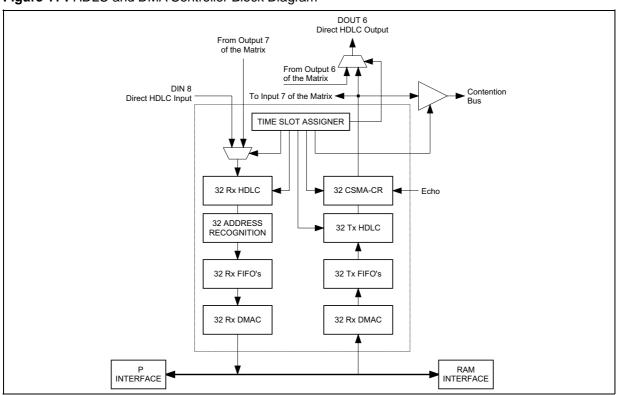

| Figure 11: HDLC and DMA Controller Block Diagram                                |      |

| Figure 12: Structure of the Receive Circular Queue                              |      |

| Figure 13: Structure of the Transmit Circular Queue                             |      |

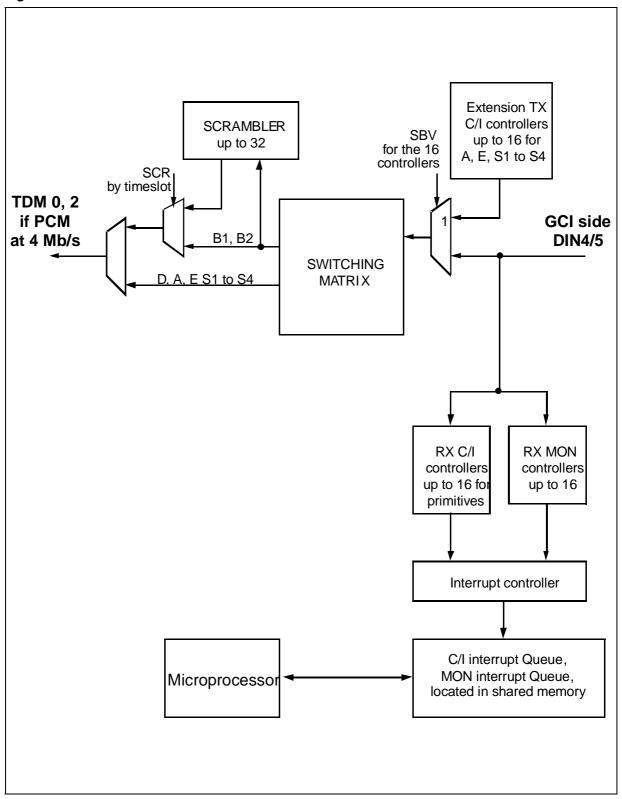

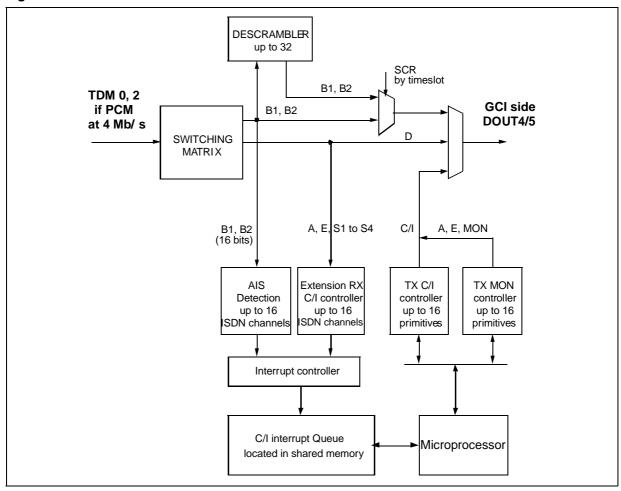

| Figure 14: D, C/I and Monitor Channel Path                                      |      |

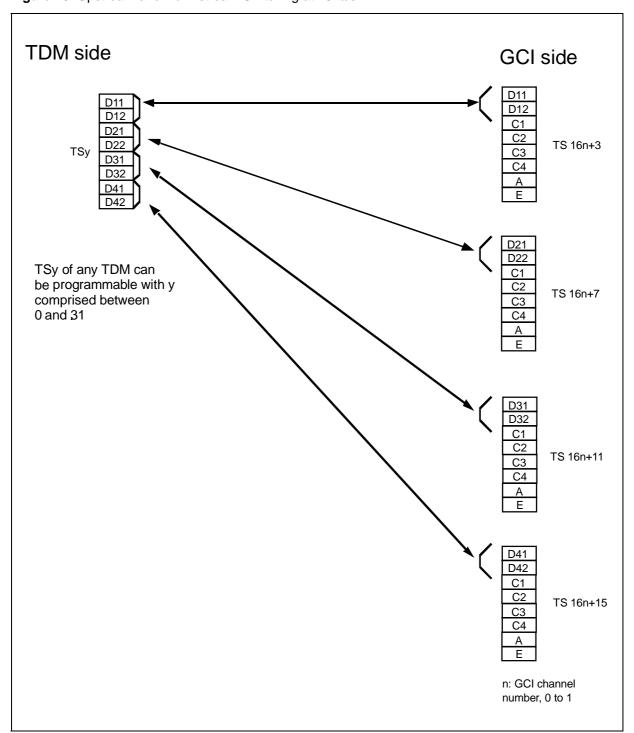

| Figure 15: GCI channel to/from ISDN Channel                                     |      |

| Figure 16: From GCI Channels to ISDN Channels                                   |      |

| Figure 17: From ISDN channels to GCI Channels                                   |      |

| Figure 17.1: Write FIFO and Fetch Memories                                      |      |

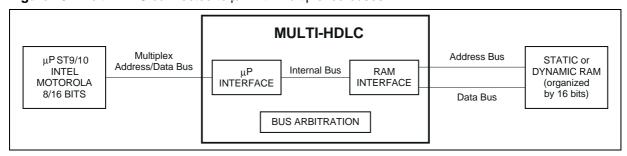

| Figure 18: Multi-HDLC connected to μP with multiplexed buses                    |      |

| <b>Figure 19 :</b> <i>Multi-HDLC</i> connected to μP with non-multiplexed buses |      |

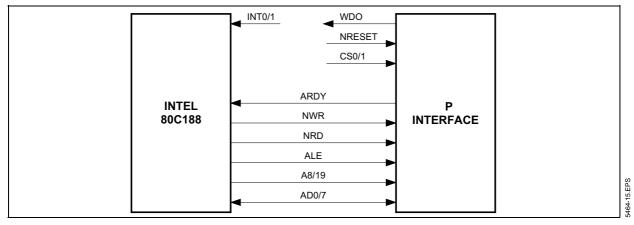

| Figure 20: Microprocessor Interface for INTEL 80C188                            |      |

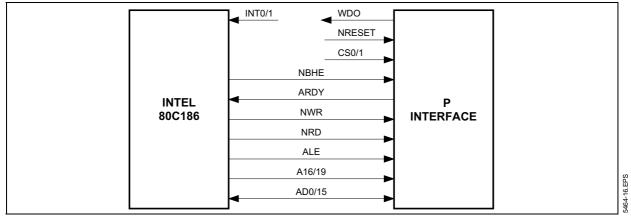

| Figure 21: Microprocessor Interface for INTEL 80C186                            |      |

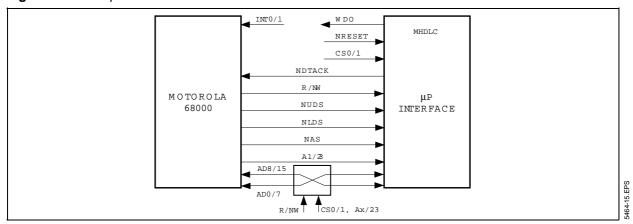

| Figure 22: Microprocessor Interface for MOTOROLA 68000                          |      |

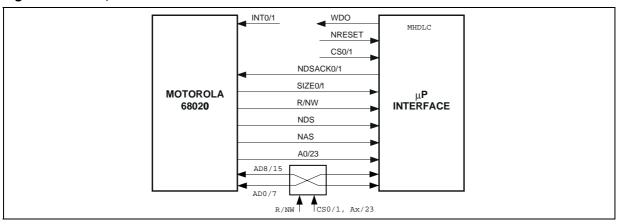

| Figure 23: Microprocessor Interface for MOTOROLA 68020                          |      |

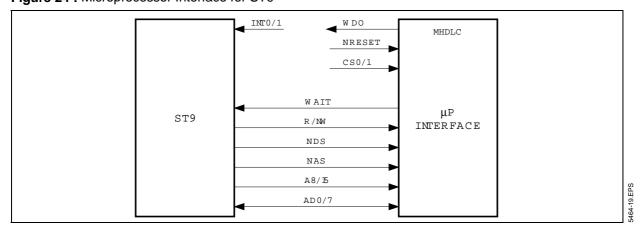

| Figure 24: Microprocessor Interface for ST9                                     |      |

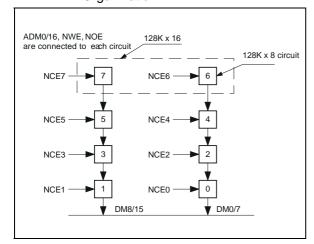

| Figure 25: n x 128K x 16 SRAM Memory Organization                               |      |

| Figure 26: 512K x 8 SRAM Circuit Memory Organization                            |      |

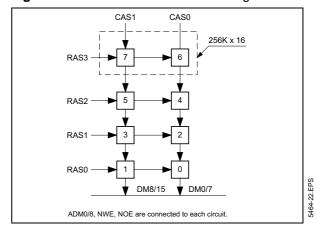

| Figure 27: 256K x 16 DRAM Circuit Organization                                  |      |

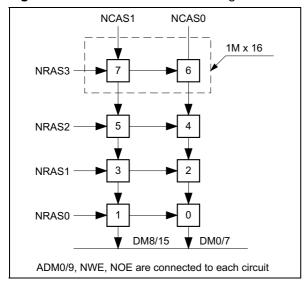

| Figure 28: 1M x 16 DRAM Circuit Organization                                    |      |

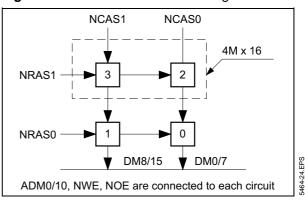

| Figure 29: 4M x 16 DRAM Circuit Organization                                    |      |

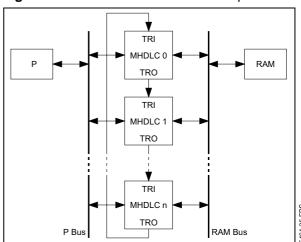

| Figure 30 : Chain of n Multi-HDLC Components                                    |      |

| Figure 31: MHDLC Clock Generation                                               |      |

| Figure 32: VCXO Frequency Synchronization                                       |      |

| Figure 33: The Three Circular Interrupt Memories                                |      |

| IV - DC SPECIFICATIONS                                                          |      |

| V - CLOCK TIMING                                                                | 45   |

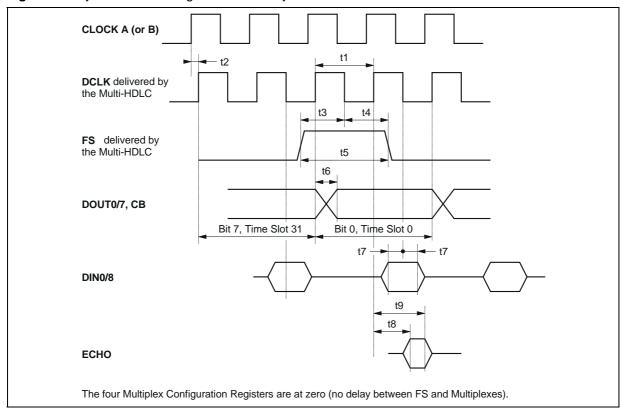

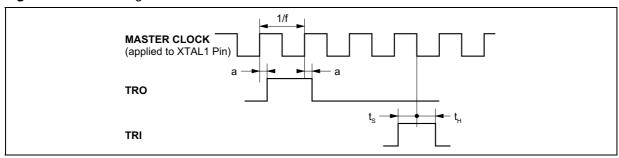

| Figure 34: Clocks received and delivered by the Multi-HDLC                      |      |

| Figure 35 : Synchronization Signals received by the <i>Multi-HDLC</i>           |      |

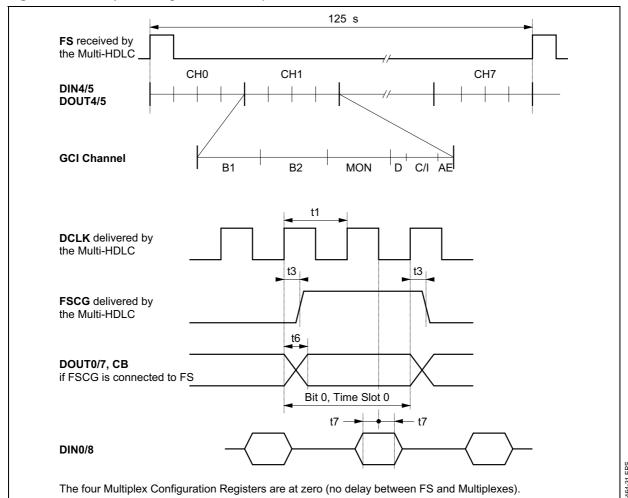

| Figure 36 : GCI Synchro Signal delivered by the Multi-HDLC                      |      |

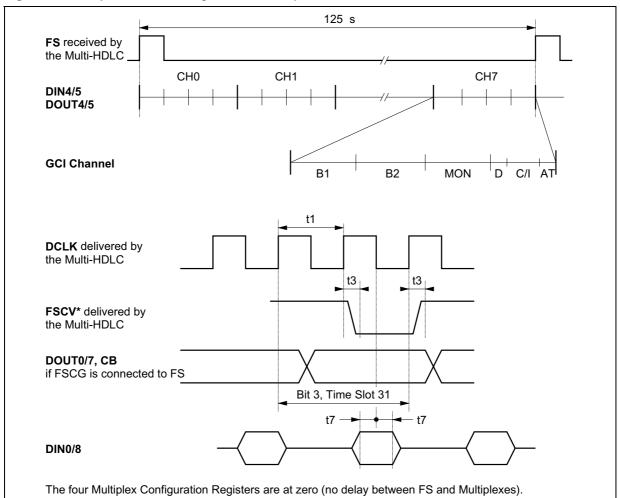

| Figure 37: V* Synchronization Signal delivered by the Multi-HDLC                | 48   |

| LIST OF FIGURES (continued)                                 | Page |

|-------------------------------------------------------------|------|

| VI - MEMORY TIMING                                          |      |

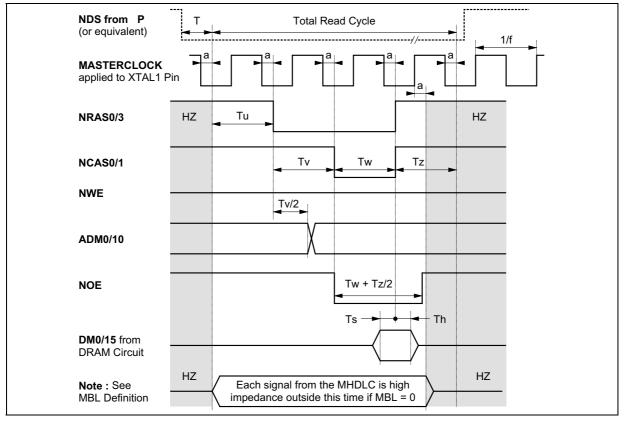

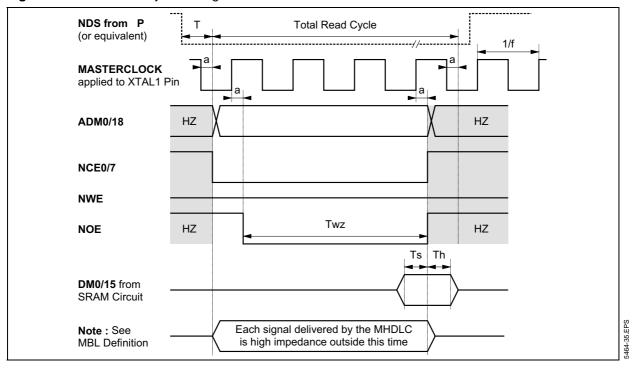

| Figure 38: Dynamic Memory Read Signals from the Multi-HDLC  | 49   |

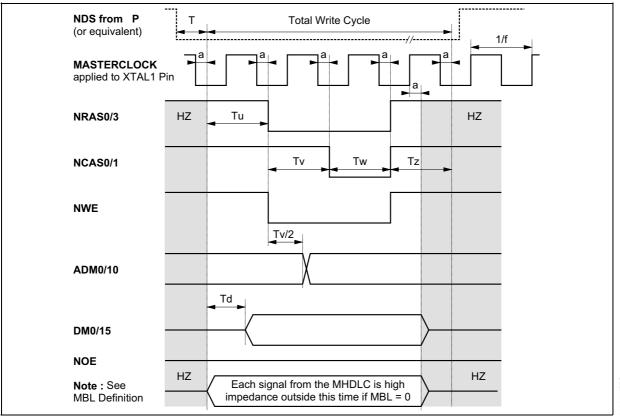

| Figure 39: Dynamic Memory Write Signals from the Multi-HDLC | 50   |

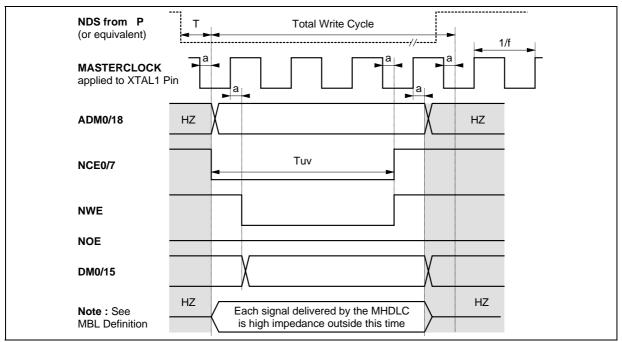

| Figure 40: Static Memory Read Signals from the Multi-HDLC   | 51   |

| Figure 41: Static Memory Write Signals from the Multi-HDLC  | 52   |

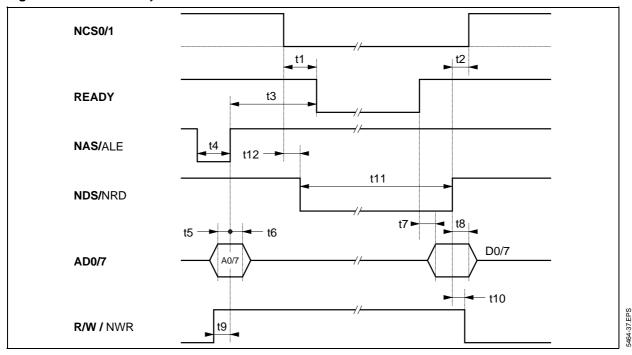

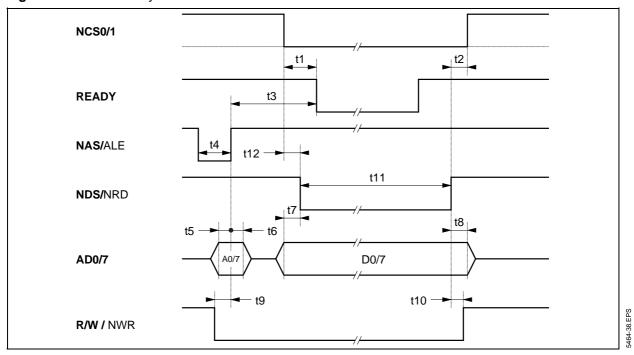

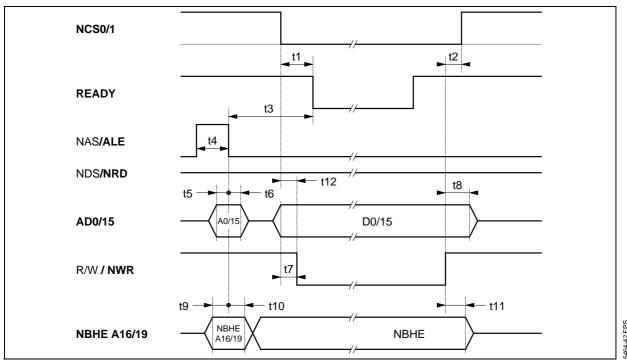

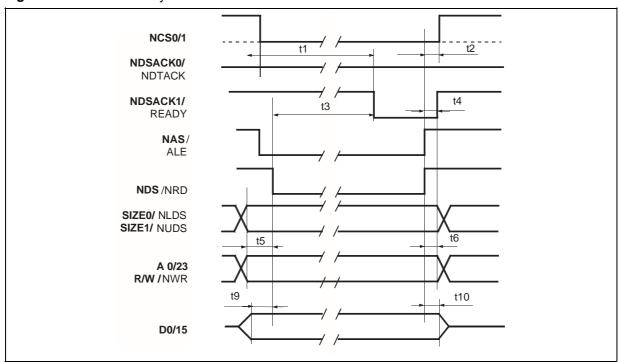

| Figure 42: ST9 Read Cycle                                   | 53   |

| VII - MICROPROCESSOR TIMING                                 | 53   |

| Figure 43: ST9 Write Cycle                                  |      |

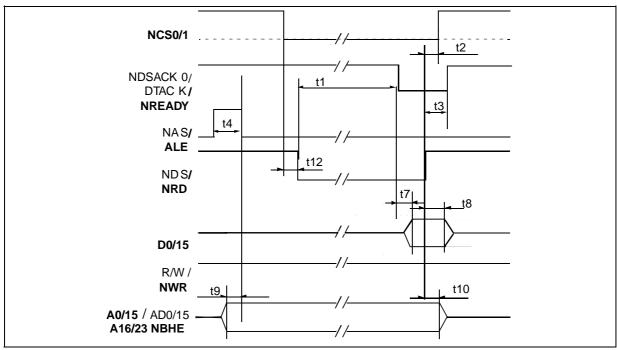

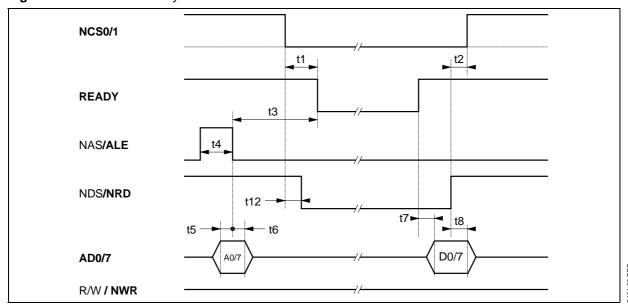

| Figure 44: ST10 (C16x) Read Cycle; Multiplexed A/D          |      |

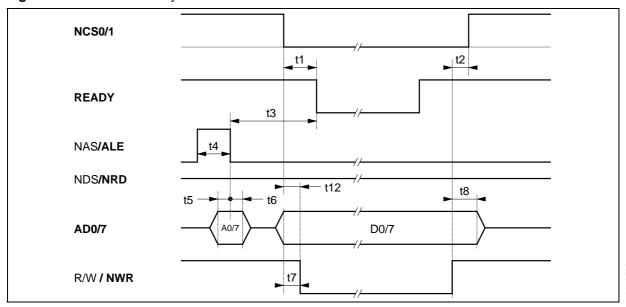

| Figure 45: ST10 (C16x) Write Cycle; Multiplexed A/D         | 56   |

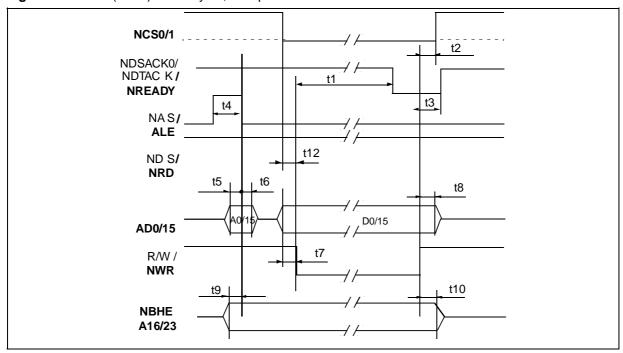

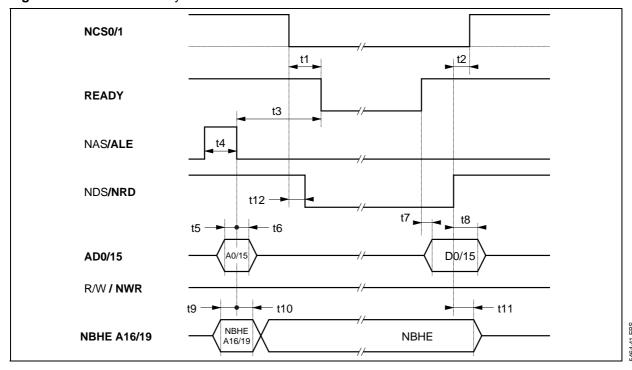

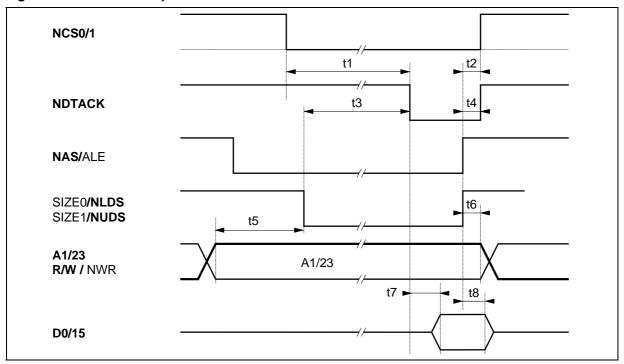

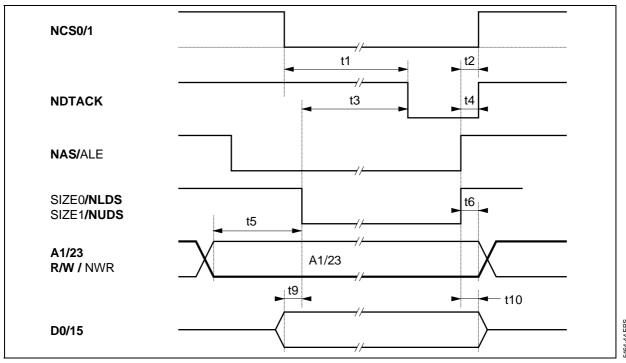

| Figure 46: ST10 (C16x) Read Cycle; Demultiplexed A/D        | 57   |

| Figure 47: ST10 (C16x) Write Cycle; Demultiplexed A/D       | 58   |

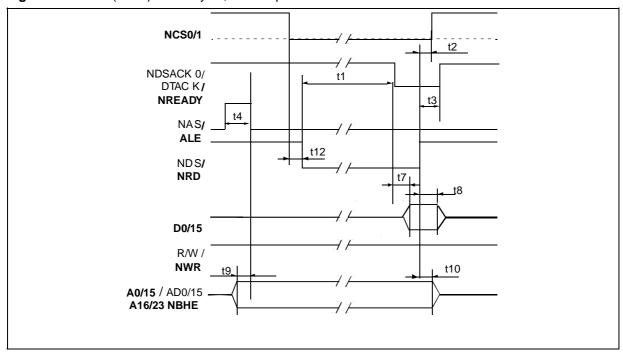

| Figure 48: 80C188 Read Cycle                                | 59   |

| Figure 49: 80C188 Write Cycle                               | 60   |

| Figure 50: 80C186 Read Cycle                                | 61   |

| Figure 51: 80C186 Write Cycle                               | 62   |

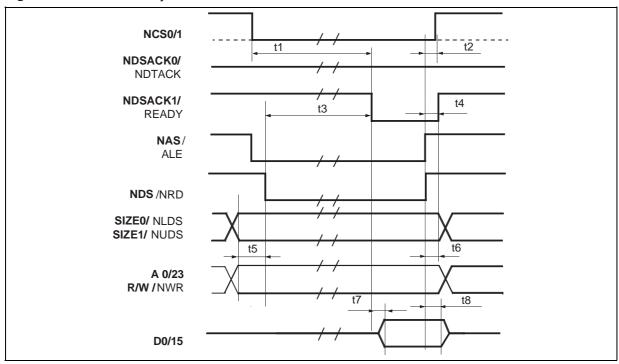

| Figure 52: 68000 Read Cycle                                 | 63   |

| Figure 53: 68000 Write Cycle                                | 64   |

| Figure 54: 68020 Read Cycle                                 | 65   |

| Figure 55: 68020 Write Cycle                                | 66   |

| Figure 56: Token Ring                                       | 67   |

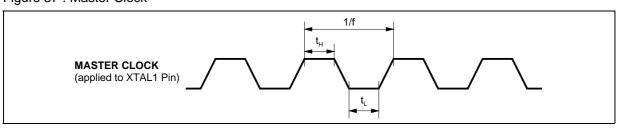

| Figure 57: Master Clock                                     | 67   |

#### I - PIN INFORMATION

#### I.1 - Pin Connections

**577**

## I.2 - Pin Description

| Pin N° | Symbol            | Туре   | Function                                                                                                                                                                                                                       |

|--------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                   |        |                                                                                                                                                                                                                                |

|        | · ·               |        | ound pins must be connected)                                                                                                                                                                                                   |

| 14     | $V_{DD1}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 15     | V <sub>SS1</sub>  | Ground | DC ground                                                                                                                                                                                                                      |

| 29     | $V_{DD2}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 30     | $V_{SS2}$         | Ground | DC ground                                                                                                                                                                                                                      |

| 45     | $V_{DD3}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 46     | $V_{SS3}$         | Ground | DC ground                                                                                                                                                                                                                      |

| 61     | $V_{DD4}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 62     | $V_{SS4}$         | Ground | DC ground                                                                                                                                                                                                                      |

| 73     | $V_{DD5}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 74     | $V_{SS5}$         | Ground | DC ground                                                                                                                                                                                                                      |

| 89     | $V_{DD6}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 90     | V <sub>SS6</sub>  | Ground | DC ground                                                                                                                                                                                                                      |

| 107    | $V_{DD7}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 108    | V <sub>SS7</sub>  | Ground | DC ground                                                                                                                                                                                                                      |

| 121    | $V_{DD8}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 122    | V <sub>SS8</sub>  | Ground | DC ground                                                                                                                                                                                                                      |

| 133    | $V_{DD9}$         | Power  | DC supply                                                                                                                                                                                                                      |

| 134    | V <sub>SS9</sub>  | Ground | DC ground                                                                                                                                                                                                                      |

| 145    | $V_{DD10}$        | Power  | DC supply                                                                                                                                                                                                                      |

| 146    | V <sub>SS10</sub> | Ground | DC ground                                                                                                                                                                                                                      |

| 158    | V <sub>DD11</sub> | Power  | DC supply                                                                                                                                                                                                                      |

| 159    | V <sub>SS11</sub> | Ground | DC ground (Total 22)                                                                                                                                                                                                           |

| CLOCKS |                   |        |                                                                                                                                                                                                                                |

| 2      | XTAL1             | I      | Crystal 1. A clock pulse at $f_{Min.}$ = 32000kHz can be applied to this input (or one pin of two crystal pins) with : -50.10 <sup>-6</sup> < $\Delta f$ < +50.10 <sup>-6</sup> .                                              |

| 3      | XTAL2             | 0      | Crystal 2. If the internal crystal oscillator is used, the second crystal pin is applied to this output.                                                                                                                       |

| 7      | VCXO IN           | 13     | VCXO input signal. This signal is compared to clock A(or B) selected inside the <i>Multi-HDLC</i> .                                                                                                                            |

| 8      | VCXO OUT          | 04     | VCXO error signal. This pin delivers the result of the comparison.                                                                                                                                                             |

| 10     | CLOCKA            | 13     | Input Clock A (4096kHz or 8192kHz)                                                                                                                                                                                             |

| 11     | CLOCKB            | 13     | Input Clock B (4096kHz or 8192kHz)                                                                                                                                                                                             |

| 12     | FRAMEA            | 13     | Clock A at 8kHz                                                                                                                                                                                                                |

| 13     | FRAMEB            | 13     | Clock B at 8kHz                                                                                                                                                                                                                |

| 9      | DCLK              | O8     | Data Clock issued from Input Clock A (or B). This clock is delivered by the circuit at 4096kHz (or 2048kHz). DOUT0/7 are transmitted on the rising edge of this signal. DIN0/7 are sampled on the falling edge of this signal. |

| 17     | FSCG              | O8     | Frame synchronization for GCI at 8kHz. This clock is issued from FRAME A (or B).                                                                                                                                               |

| 18     | FSCV*             | O8     | Frame synchronization for V Star at 8kHz                                                                                                                                                                                       |

| 16     | FS                | 13     | Frame synchronization. This signal synchronizes DIN0/7 and DOUT0/7.                                                                                                                                                            |

| 19     | PSS               | 08     | Programmable synchronization Signal. The PS bit of connection memory is read in real time.                                                                                                                                     |

**Type:** I1 = Input TTL; O4 = Output CMOS 4mA; I2 = I1 + Pull-up;

I3 = I1 + Hysteresis;

I4 = I3 + Pull-up;

O8D = Output CMOS 8mA, Open Drain; O8T = Output CMOS 8mA, Tristate

O4T = O4 + Tristate;

O8 = Output CMOS 8mA, "1" and "0" at Low Impedance; O8DT = Output CMOS 8mA, Open Drain or Tristate;

I1 and I3 must be connected to VDD and VSS if not used

## I.2 - Pin Description (continued)

| impedance. Wired at VDD if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin N°   | Symbol                          | Type     | Function                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------|----------|--------------------------------------------------------------------------------------------------------------------|--|--|

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIME DIV | TIME DIVISION MULTIPLEXES (TDM) |          |                                                                                                                    |  |  |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20       | DIN0                            | I1       | TDM0 Data Input 0                                                                                                  |  |  |

| 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21       | DIN1                            | I1       | TDM1 Data Input 1                                                                                                  |  |  |

| 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22       | DIN2                            | I1       | TDM2 Data Input 2                                                                                                  |  |  |

| 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23       | DIN3                            | I1       | TDM3 Data Input 3                                                                                                  |  |  |

| DIN6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24       | DIN4                            | I1       | TDM4 Data Input 4                                                                                                  |  |  |

| 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25       | DIN5                            | l1       | TDM5 Data Input 5                                                                                                  |  |  |

| 28    DIN8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26       | DIN6                            | I1       | TDM6 Data Input 6                                                                                                  |  |  |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27       | DIN7                            | l1       | TDM7 Data Input 7                                                                                                  |  |  |

| 32   DOUT1   O8DT   TDM1 Data Output 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28       | DIN8                            | I1       | TDM8 Data Input 8                                                                                                  |  |  |

| 33   DOUT2   O8DT   TDM2 Data Output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31       | DOUT0                           | O8DT     | TDM0 Data Output 0                                                                                                 |  |  |

| 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32       | DOUT1                           | O8DT     | TDM1 Data Output 1                                                                                                 |  |  |

| 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33       | DOUT2                           | O8DT     | TDM2 Data Output 2                                                                                                 |  |  |

| 36    DOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34       | DOUT3                           | O8DT     | TDM3 Data Output 3                                                                                                 |  |  |

| 37   DOUT6   O8DT   TDM6 Data Output 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35       | DOUT4                           | O8DT     | TDM4 Data Output 4                                                                                                 |  |  |

| 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36       | DOUT5                           | O8DT     | TDM5 Data Output 5                                                                                                 |  |  |

| 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37       | DOUT6                           | O8DT     | TDM6 Data Output 6                                                                                                 |  |  |

| impedance. Wired at VDD if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38       | DOUT7                           | O8DT     | TDM7 Data Output 7                                                                                                 |  |  |

| BOUDARY SCAN   40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39       | NDIS                            | I1       | DOUT 0/7 Not Disable. When this pin is at 0V, the Data Output 0/7 are at high impedance. Wired at VDD if not used. |  |  |

| BOUDARY SCAN   40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5        | СВ                              | O8D      | Contention Bus for CSMA/CR                                                                                         |  |  |

| 40         NTRST         I4         Reset for boundary scan           41         TMS         I2         Mode Selection for boundary scan           42         TDI         I2         Input Data for boundary scan           43         TDO         O4         Output Data for boundary scan           44         TCK         I2         Clock for boundary scan           MICROPROCESSOR INTERFACE           58         MOD0         I1         1         1         0         0         1         1         0           59         MOD1         I1         1         1         0         0         0         1         1         0         0         1         1         0         0         1         1         0         0         0         1         1         0         0         0         1         1         0         0         0         1         1         0         0         0         1         1         0         0         0         1         1         0         0         0         1         1         0         0         0         0         1         1         0         0         0         0         0< | 6        | EC                              | I1       | Echo                                                                                                               |  |  |

| 41         TMS         I2         Mode Selection for boundary scan           42         TDI         I2         Input Data for boundary scan           43         TDO         O4         Output Data for boundary scan           MICROPROCESSOR INTERFACE           58         MOD0         I1         1         1         0         0         1         1         0           59         MOD1         I1         1         1         0         0         0         1         1           60         MOD2         I1         0         1         1         1         0         0         1         1         1         1         0         0         0         1         1         1         0         0         0         1         1         1         0         0         0         1         1         1         0         0         0         1         1         0         0         1         1         1         0         0         0         1         1         1         0         0         0         1         1         0         0         0         0         1         1         0         0         0             | BOUDAR   | Y SCAN                          |          |                                                                                                                    |  |  |

| 42   TDI   12   Input Data for boundary scan     43   TDO   O4   Output Data for boundary scan     44   TCK   12   Clock for boundary scan     MICROPROCESSOR INTERFACE     58   MODO   I1   1   1   0   0   1   1   0     59   MOD1   I1   1   1   0   0   0   0   1     60   MOD2   I1   O   1   1   0   0   0   1   1     80C188 80C186 68000 68020 ST9   ST10m   ST10Nm     1   NRESET   I3   Circuit Reset     47   NCSO   I3   Chip Select 0 : internal registers are selected     48   NCS1   I3   Chip Select 1 : external memory is selected     49   INTO   O4   Interrupt generated by HDLC, RxC/I or RxMON. Active high.     50   INT1   O4   Interrupt1. This pin goes to 5V when the selected clock A (or B) has disappeare 250µs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                     | 40       | NTRST                           | 14       | Reset for boundary scan                                                                                            |  |  |

| 43   TDO   O4   Output Data for boundary scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41       | TMS                             | 12       | Mode Selection for boundary scan                                                                                   |  |  |

| MICROPROCESSOR INTERFACE   58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42       | TDI                             | 12       | Input Data for boundary scan                                                                                       |  |  |

| MICROPROCESSOR INTERFACE   58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43       | TDO                             | O4       | Output Data for boundary scan                                                                                      |  |  |

| 58         MOD0         I1         1         1         0         0         1         1         0           59         MOD1         I1         1         1         0         0         0         0         1           60         MOD2         I1         0         1         1         0         0         1         1           80C188         80C186         68000         68020         ST9         ST10m         ST10Nm           1         NRESET         I3         Circuit Reset           47         NCS0         I3         Chip Select 0 : internal registers are selected           48         NCS1         I3         Chip Select 1 : external memory is selected           49         INT0         O4         Interrupt generated by HDLC, RxC/I or RxMON. Active high.           50         INT1         O4         Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                              | 44       | TCK                             | 12       | Clock for boundary scan                                                                                            |  |  |

| 59         MOD1         I1         1         1         0         0         0         0         1           60         MOD2         I1         0         1         1         0         0         1         1           80C188         80C186         68000         68020         ST9         ST10m         ST10Nm           1         NRESET         I3         Chip Select 0: internal registers are selected           48         NCS1         I3         Chip Select 1: external memory is selected           49         INT0         O4         Interrupt generated by HDLC, RxC/I or RxMON. Active high.           50         INT1         O4         Interrupt1. This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                     | MICROPF  | ROCESSOR II                     | NTERFACE | E                                                                                                                  |  |  |

| 60 MOD2 II 0 1 1 0 0 1 1  80C188 80C186 68000 68020 ST9 ST10m ST10Nm  1 NRESET I3 Circuit Reset  47 NCS0 I3 Chip Select 0 : internal registers are selected  48 NCS1 I3 Chip Select 1 : external memory is selected  49 INT0 O4 Interrupt generated by HDLC, RxC/I or RxMON. Active high.  50 INT1 O4 Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58       | MOD0                            | I1       | 1 1 0 0 1 1 0                                                                                                      |  |  |

| 80C188 80C186 68000 68020 ST9 ST10m ST10Nm  1 NRESET I3 Circuit Reset  47 NCS0 I3 Chip Select 0 : internal registers are selected  48 NCS1 I3 Chip Select 1 : external memory is selected  49 INTO O4 Interrupt generated by HDLC, RxC/I or RxMON. Active high.  50 INT1 O4 Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250µs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59       | MOD1                            | I1       | 1 1 0 0 0 1                                                                                                        |  |  |

| 1 NRESET I3 Circuit Reset 47 NCS0 I3 Chip Select 0 : internal registers are selected 48 NCS1 I3 Chip Select 1 : external memory is selected 49 INT0 O4 Interrupt generated by HDLC, RxC/I or RxMON. Active high. 50 INT1 O4 Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60       | MOD2                            | I1       | 0 1 1 0 0 1 1                                                                                                      |  |  |

| <ul> <li>NCS0 I3 Chip Select 0 : internal registers are selected</li> <li>NCS1 I3 Chip Select 1 : external memory is selected</li> <li>INT0 O4 Interrupt generated by HDLC, RxC/I or RxMON. Active high.</li> <li>INT1 O4 Interrupt1. This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                 |          | 80C188 80C186 68000 68020 ST9 ST10m ST10Nm                                                                         |  |  |

| 48 NCS1 I3 Chip Select 1 : external memory is selected 49 INT0 O4 Interrupt generated by HDLC, RxC/I or RxMON. Active high. 50 INT1 O4 Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1        | NRESET                          | 13       | Circuit Reset                                                                                                      |  |  |

| 48 NCS1 I3 Chip Select 1 : external memory is selected 49 INT0 O4 Interrupt generated by HDLC, RxC/I or RxMON. Active high. 50 INT1 O4 Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47       | NCS0                            | 13       | Chip Select 0 : internal registers are selected                                                                    |  |  |

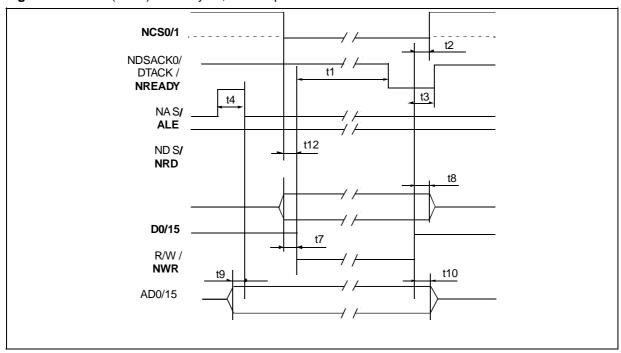

| 50 INT1 O4 Interrupt1.This pin goes to 5V when the selected clock A (or B) has disappeare 250μs after reset this pin goes to 5V also if clock A is not present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48       | NCS1                            | 13       | Chip Select 1 : external memory is selected                                                                        |  |  |