# 2A SWITCH STEP DOWN SWITCHING REGULATOR

- 2A INTERNAL SWITCH

- OPERATING INPUT VOLTAGE FROM 4.4V TO 36V

- 3.3V / (±2%) REFERENCE VOLTAGE

- OUTPUT VOLTAGE ADJUSTABLE FROM 1.235V TO 35V

- LOW DROPOUT OPERATION: 100% DUTY CYCLE

- 500KHz INTERNALLY FIXED FREQUENCY

- VOLTAGE FEEDFORWARD

- ZERO LOAD CURRENT OPERATION

- INTERNAL CURRENT LIMITING

- INHIBIT FOR ZERO CURRENT CONSUMPTION

- SYNCHRONIZATION

- PROTECTION AGAINST FEEDBACK DISCONNECTION

- THERMAL SHUTDOWN

#### **APPLICATIONS:**

zsc.com

- CONSUMER: STB, DVD, TV, VCR,CAR RADIO, LCD MONITORS

- NETWORKING: XDSL, MODEMS, DC-DC MODULES

- COMPUTER: PRINTERS, AUDIO/GRAPHIC CARDS, OPTICAL STORAGE, HARD DISK DRIVE

- INDUSTRIAL: CHARGERS, CAR BATTERY DC-DC CONVERTERS

HSOP8 - EXPOSED PAD ORDERING NUMBERS: Tube: L5973AD Tape & Reel: L5973ADTR

#### DESCRIPTION

The L5973AD is a step down monolithic power switching regulator with a switch current limit of 2A so it is able to deliver more than 1.5A DC current to the load depending on the application conditions.

The output voltage can be set from 1.235V to 35V. The high current level is also achieved thanks to an SO8 package with exposed frame, that allows to reduce the  $R_{th(j-amb)}$  down to approximately 40°C/W

The device uses an internal P-Channel D-MOS transistor (with a typical of  $200m\Omega$ ) as switching element to avoid the use of bootstrap capacitor and guarantee high efficiency.

An internal oscillator fixes the switching frequency at 500KHz to minimize the size of external components. Having a minimum input voltage of 4.4V only, it is particularly suitable for 5V bus, available in all computer related applications.

Pulse by pulse current limit with the internal frequency modulation offers an effective constant current short circuit protection.

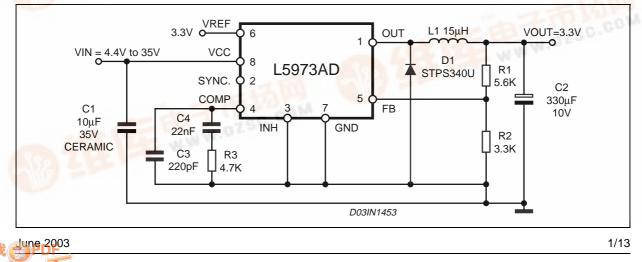

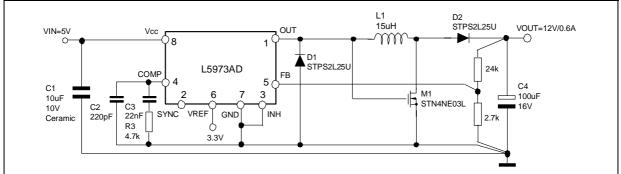

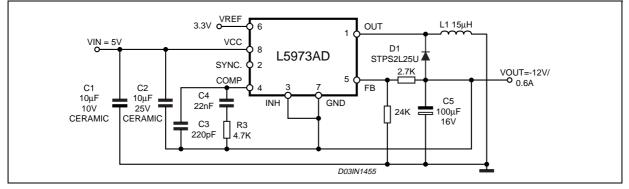

#### **TEST APPLICATION CIRCUIT**

## THERMAL DATA

| Symbol                  | Parameter                                   | Value  | Unit |

|-------------------------|---------------------------------------------|--------|------|

| R <sub>th (j-amb)</sub> | Thermal Resistance Junction to ambient Max. | 40 (*) | °C/W |

(\*) Package mounted on board

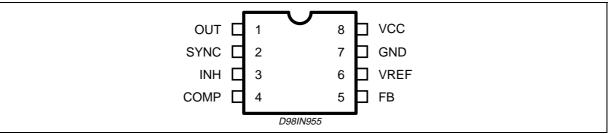

# **PIN CONNECTION**

# **PIN DESCRIPTION**

| Ν. | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | OUT             | Regulator Output.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2  | SYNC            | Master/Slave Synchronization. When it is open, a signal synchronous with the turn-off of the inter-<br>nal power is present at the pin. When connected to an external signal at a frequency higher than<br>the internal one, then the device is synchronized by the external signal.<br>Connecting together the SYNC pin of two devices, the one with the higher frequency works as<br>master and the other one, works as slave. |

| 3  | INH             | A logical signal (active high) disables the device. With IHN higher than 2.2V the device is OFF and with INH lower than 0.8V, the device is ON. If INH is not used the pin must be grounded. When it is open, an internal pull-up disables the device.                                                                                                                                                                           |

| 4  | COMP            | E/A output to be used for frequency compensation.                                                                                                                                                                                                                                                                                                                                                                                |

| 5  | FB              | Stepdown feedback input. Connecting the output voltage directly to this pin results in an output voltage of 1.235V. An external resistor divider is required for higher output voltages (the typical value for the resistor connected between this pin and ground is 4.7K).                                                                                                                                                      |

| 6  | $V_{REF}$       | Reference voltage of 3.3V. No filter capacitor is needed to stability.                                                                                                                                                                                                                                                                                                                                                           |

| 7  | GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8  | V <sub>CC</sub> | Unregulated DC input voltage.                                                                                                                                                                                                                                                                                                                                                                                                    |

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                             | Value                    | Unit   |

|------------------|-------------------------------------------------------|--------------------------|--------|

| V <sub>8</sub>   | Input Voltage                                         | 40                       | V      |

| V <sub>1</sub>   | Output DC voltage<br>Output peak voltage at t = 0.1µs | -1 to 40<br>-5 to 40     | V<br>V |

| l <sub>1</sub>   | Maximum output current                                | int. limit.              |        |

| V4, V5           | Analog pins                                           | 4                        | V      |

| V <sub>3</sub>   | INH                                                   | -0.3V to V <sub>CC</sub> |        |

| V <sub>2</sub>   | SYNC                                                  | -0.3 to 4                | V      |

| P <sub>tot</sub> | Power dissipation at $T_{amb} \le 60^{\circ}C$        | 2.25                     | W      |

| Tj               | Operating junction temperature range                  | -40 to 150               | °C     |

| T <sub>stg</sub> | Storage temperature range                             | -55 to 150               | °C     |

| Symbol                | Parameter                         | Test Condition                                               | Min.         | Тур.  | Max.         | Unit     |

|-----------------------|-----------------------------------|--------------------------------------------------------------|--------------|-------|--------------|----------|

| Vcc                   | Operating input voltage range     | V <sub>o</sub> = 1.235V; I <sub>o</sub> = 2A                 | 4.4          |       | 36           | V        |

| R <sub>DSON</sub>     | Mosfet on Resistance              |                                                              |              | 0.200 |              | Ω        |

| lı                    | Maximum limiting current          | $V_{CC} = 4.4V$ to 36V                                       |              | 2.3   |              | Α        |

| fs                    | Switching frequency               |                                                              |              | 500   |              | KHz      |

|                       | Duty cycle                        |                                                              | 0            |       | 100          | %        |

| DYNAMIC               | CHARACTERISTICS (see test circ    | uit ).                                                       |              | l     | l            |          |

| $V_5$                 | Voltage feedback                  | 4.4V < V <sub>CC</sub> < 36V                                 | 1.220        | 1.235 | 1.25         | V        |

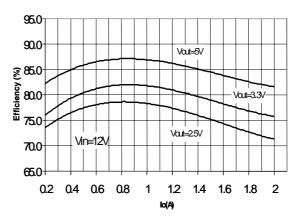

| η                     | Efficiency                        | $V_{O} = 5V, V_{CC} = 12V$                                   |              | 90    |              | %        |

| DC CHAR               | ACTERISTICS                       |                                                              |              |       |              |          |

| I <sub>qop</sub>      | Total Operating Quiescent Current |                                                              |              | 5     | 7            | mA       |

| lq                    | Quiescent current                 | Duty Cycle = 0; V <sub>FB</sub> = 1.5V                       |              |       | 2.7          | mA       |

| I <sub>qst-by</sub>   | Total stand-by quiescent current  | V <sub>inh</sub> > 2.2V                                      |              | 50    | 100          | μA       |

| INHIBIT               | I                                 |                                                              |              |       |              | <u></u>  |

|                       | INH Threshold Voltage             | Device ON                                                    |              |       | 0.8          | V        |

|                       |                                   | Device OFF                                                   | 2.2          |       |              | V        |

| ERROR A               | MPLIFIER                          |                                                              |              | l     | l            |          |

| VOH                   | High level output voltage         | VFB = 1V                                                     | 3.5          |       |              | V        |

| V <sub>OL</sub>       | Low level output voltage          | VFB = 1.5V                                                   |              |       | 0.4          | V        |

| I <sub>o source</sub> | Source output current             | V <sub>COMP</sub> = 1.9V; V <sub>FB</sub> = 1V               | 200          | 300   |              | μA       |

| I <sub>o sink</sub>   | Sink output current               | V <sub>COMP</sub> = 1.9V; V <sub>FB</sub> = 1.5V             | 1            | 1.5   |              | mA       |

| I <sub>b</sub>        | Source bias current               |                                                              |              | 2.5   | 4            | μA       |

|                       | DC open loop gain                 | R <sub>L</sub> = ∞                                           | 50           | 57    |              | dB       |

| gm                    | Transconductance                  | $I_{comp}$ = -0.1mA to 0.1mA<br>V <sub>COMP</sub> = 1.9V     |              | 2.3   |              | mS       |

| SYNC FU               | NCTION                            |                                                              |              | l     | l            |          |

|                       | High Input Voltage                | $V_{CC} = 4.4V$ to 36V                                       | 2.5          |       | $V_{REF}$    | V        |

|                       | Low Input Voltage                 | V <sub>CC</sub> = 4.4V to 36V                                |              |       | 0.74         | V        |

|                       | Slave Sink Current                | $V_{sync} = 0.74V$<br>$V_{sync} = 2.33V$                     | 0.11<br>0.21 |       | 0.25<br>0.45 | mA<br>mA |

|                       | Master Output Amplitude           | I <sub>source</sub> = 3mA                                    | 2.75         | 3     |              | V        |

|                       | Output Pulse Width                | no load, V <sub>sync</sub> = 1.65V                           | 0.20         | 0.35  |              | μs       |

| REFEREN               |                                   |                                                              | I            | I     | I            | <u> </u> |

|                       | Reference Voltage                 |                                                              | 3.234        | 3.3   | 3.366        | V        |

|                       |                                   | I <sub>REF</sub> = 0 to 5mA<br>V <sub>CC</sub> = 4.4V to 36V | 3.2          | 3.3   | 3.399        | V        |

|                       | Line Regulation                   | $I_{REF} = 0mA$<br>$V_{CC} = 4.4V$ to 36V                    |              | 5     | 10           | mV       |

|                       | Load Regulation                   | I <sub>REF</sub> = 0 to 5mA                                  |              | 8     | 15           | mV       |

|                       | Short Circuit Current             |                                                              | 10           | 18    | 30           | mA       |

# **ELECTRICAL CHARACTERISTICS** ( $T_j = 25^{\circ}C$ , $V_{CC} = 12V$ , unless otherwise specified.)

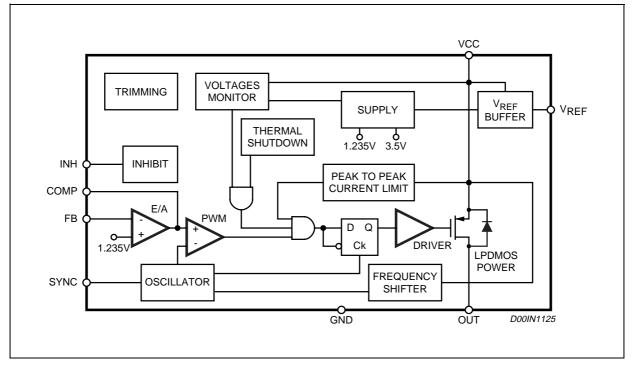

# FUNCTIONAL DESCRIPTION

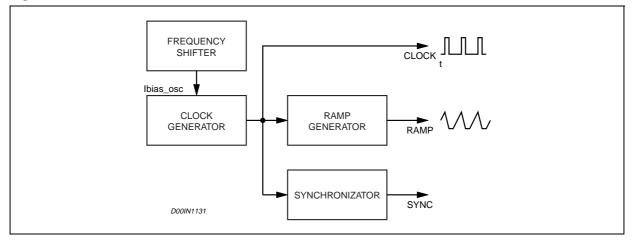

The main internal blocks are shown in Fig. 1, where is reported the device block diagram. They are:

- A voltage regulator that supplies the internal circuitry. From this regulator, a 3.3V reference voltage is externally available.

- A voltage monitor circuit that checks the input and internal voltages.

- A fully integrated sawtooth oscillator whose frequency is500KHz

- Two embedded current limitations circuitries which control the current that flows through the power switch. The Pulse by Pulse Current Limit forces the power switch OFF cycle by cycle if the current reaches an internal threshold, while the Frequency Shifter reduces the switching frequency in order to strongly reduce the duty cycle.

- A transconductance error amplifier.

- A pulse width modulator (PWM) comparator and the relative logic circuitry necessary to drive the internal power.

- An high side driver for the internal P-MOS switch.

- An inhibit block for stand-by operation.

- A circuit to realize the thermal protection function.

# Figure 1. Block Diagram

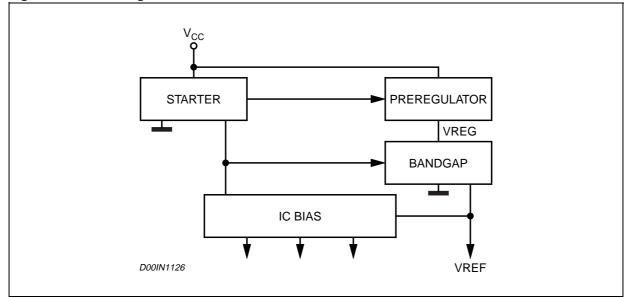

# **POWER SUPPLY & VOLTAGE REFERENCE**

The internal regulator circuit (shown in Figure 2) consists of a start-up circuit, an internal voltage Preregulator, the Bandgap voltage reference and the Bias block that provides current to all the blocks.

The Starter gives the start-up currents to the whole device when the input voltage goes high and the device is enabled (inhibit pin connected to ground).

The Preregulator block supplies the Bandgap cell with a preregulated voltage  $V_{REG}$  that has a very low supply voltage noise sensitivity.

## **VOLTAGES MONITOR**

An internal block senses continuously the V<sub>cc</sub>, V<sub>ref</sub> and V<sub>bg</sub>. If the voltages go higher than their thresholds, the regulator starts to work. There is also an hysteresis on the V<sub>CC</sub> (UVLO).

Figure 2. Internal Regulator Circuit

## **OSCILLATOR & SYNCHRONIZATOR**

Figure 3 shows the block diagram of the oscillator circuit.

The Clock Generator provides the switching frequency of the device that is internally fixed at 500KHz. The frequency shifter block acts reducing the switching frequency in case of strong overcurrent or short circuit. The clock signal is then used in the internal logic circuitry and is the input of the Ramp Generator and Synchronizator blocks.

The Ramp Generator circuit provides the sawtooth signal, used to realize the PWM control and the internal voltage feed forward, while the Synchronizator circuit generates the synchronization signal. Infact the device has a synchronization pin that can works both as Master and Slave.

As Master to synchronize external devices to the internal switching frequency.

As Slave to synchronize itself by external signal.

In particular, connecting together two devices, the one with the lower switching frequency works as Slave and the other one works as Master.

To synchronize the device, the SYNC pin has to pass from a low level to a level higher than the synchronization threshold with a duty cycle that can vary approximately from 10% to 90%, depending also on the signal frequency and amplitude.

The frequency of the synchronization signal must be at least higher than the internal switching frequency of the device (500KHz).

# Figure 3. Oscillator Circui

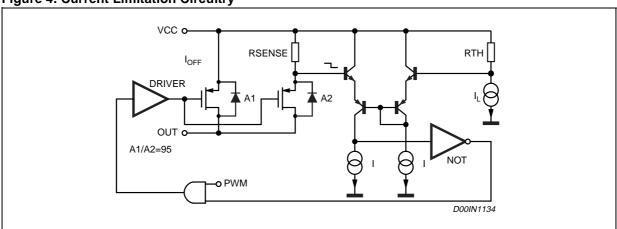

# **CURRENT PROTECTION**

The L5973AD has two current limit protections, pulse by pulse and frequency fold back.

The schematic of the current limitation circuitry for the pulse by pulse protection is shown in figure 4.

The output power PDMOS transistor is split in two parallel PDMOS. The smallest one has a resistor in series, R<sub>SENSE</sub>. The current is sensed through Rsense and if reaches the threshold, the mirror is unbalanced and the PDMOS is switched off until the next falling edge of the internal clock pulse.

Due to this reduction of the ON time, the output voltage decreases.

Since the minimum switch ON time (necessary to avoid false overcurrent signal) is not enough to obtain a sufficiently low duty cycle at 500KHz, the output current, in strong overcurrent or short circuit conditions, could increase again. For this reason the switching frequency is also reduced, so keeping the inductor current under its maximum threshold. The Frequency Shifter (see fig. 3) depends on the feedback voltage. As the feedback voltage decreases (due to the reduced duty cycle), the switching frequency decreases too.

# Figure 4. Current Limitation Circuitry

# ERROR AMPLIFIER

The voltage error amplifier is the core of the loop regulation. It is a transconductance operational amplifier whose non inverting input is connected to the internal voltage reference (1.235V), while the inverting input (FB) is connected to the external divider or directly to the output voltage. The output (COMP) is connected to the external

compensation network.

The uncompensated error amplifier has the following characteristics:

| Transconductance            | 2300µS       |  |  |

|-----------------------------|--------------|--|--|

| Low frequency gain          | 65dB         |  |  |

| Minimum sink/source voltage | 1500μΑ/300μΑ |  |  |

| Output voltage swing        | 0.4V/3.65V   |  |  |

| Input bias current          | 2.5µA        |  |  |

The error amplifier output is compared with the oscillator sawtooth to perform PWM control.

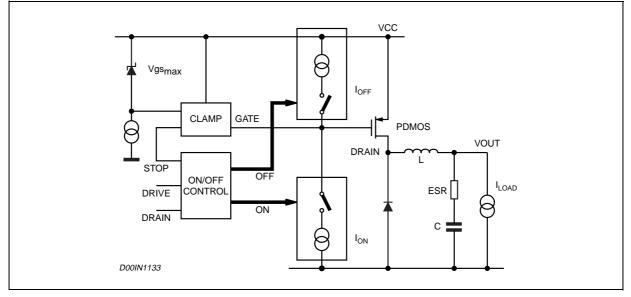

## **PWM COMPARATOR AND POWER STAGE**

This block compares the oscillator sawtooth and the error amplifier output signals generating the PWM signal for the driving stage.

The power stage is a very critical block cause it has to guarantee a correct turn on and turn off of the PD-MOS.

The turn on of the power element, or better, the rise time of the current at turn on, is a very critical parameter to compromise.

At a first approach, it looks like the faster it is the rise time, the lower are the turn on losses.

But there is a limit introduced by the recovery time of the recirculation diode.

In fact when the current of the power element equals the inductor current, the diode turns off and the drain of the power is free to go high. But during its recovery time, the diode can be considered as an high value capacitor and this produces a very high peak current, responsible of many problems:

Spikes on the device supply voltage that cause oscillations (and thus noise) due to the board parasitics.

Turn on overcurrent causing a decrease of the efficiency and system reliability.

Big EMI problems.

Shorter freewheeling diode life.

The fall time of the current during the turn off is also critical. In fact it produces voltage spikes (due to the parasitics elements of the board) that increase the voltage drop across the PDMOS.

In order to minimize all these problems, a new topology of driving circuit has been used and its block diagram is shown in fig. 5.

The basic idea is to change the current levels used to turn on and off the power switch, according with the PDMOS status and with the gate clamp status.

This circuitry allow to turn off and on quickly the power switch and to manage the above question related to the freewheeling diode recovery time problem. The gate clamp is necessary to avoid that Vgs of the internal switch goes higher than Vgsmax. The ON/OFF Control block avoids any cross conduction between the supply line and ground.

# Figure 5. Driving Circuitry

# INHIBIT FUNCTION

The inhibit feature allows to put in stand-by mode the device. With INH pin higher than 2.2V the device is disabled and the power consumption is reduced to less than  $100\mu$ A. With INH pin lower than 0.8V, the device is enabled. If the INH pin is left floating, an internal pull up ensures that the voltage at the pin reaches the inhibit threshold and the device is disabled. The pin is also Vcc compatible.

# THERMAL SHUTDOWN

The shutdown block generates a signal that turns off the power stage if the temperature of the chip goes higher than a fixed internal threshold (150°C). The sensing element of the chip is very close to the PDMOS area, so ensuring an accurate and fast temperature detection. An hysteresis of approximately 20°C avoids that the devices turns on and off continuously

# ADDITIONAL FEATURES AND PROTECTIONS

# FEEDBACK DISCONNECTION

In case of feedback disconnection, the duty cycle increases versus the maximum allowed value, bringing the output voltage close to the input supply. This condition could destroy the load.

To avoid this dangerous condition, the device is turned off if the feedback pin remains floating.

# OUTPUT OVERVOLTAGE PROTECTION

The overvoltage protection, OVP, is realized by using an internal comparator, which input is connected to the feedback, that turns off the power stage when the OVP threshold is reached. This threshold is typically 30% higher than the feedback voltage.

When a voltage divider is requested for adjusting the output voltage (see test application circuit), the OVP intervention will be set at:

$$V_{OVP} = 1.3 \cdot \frac{R_1 + R_2}{R_2} \cdot V_{FB}$$

Where  $R_1$  is the resistor connected between the output voltage and the feedback pin, while  $R_2$  is between the feedback pin and ground.

# ZERO LOAD

Due to the fact that the internal power is a PDMOS, no boostrap capacitor is required and so, the device works properly also with no load at the output. In this condition it works in burst mode, with random repetition rate of the burst.

# **APPLICATION CIRCUIT**

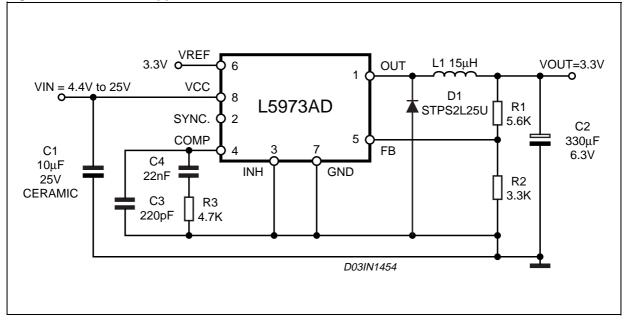

In figure 6 is shown the demo board application circuit, where the input supply voltage,  $V_{cc}$ , can range from 4.4V to 25V due to the rated voltage of the input capacitor and the output voltage is adjustable from 1.235V to  $V_{cc}$ .

# Figure 6. Demo board Application Circuit

#### Table 1. Component List

| Reference | Part Number     | Description         | Manufacturer |

|-----------|-----------------|---------------------|--------------|

| C1        |                 | 10μF, 25V           | TOKIN        |

| C2        | POSCAP 6TPB330M | 330μF, 6.3V         | Sanyo        |

| C3        | C1206C221J5GAC  | 220pF, 5%, 50V      | KEMET        |

| C4        | C1206C223K5RAC  | 22nF, 10%, 50V      | KEMET        |

| R1        |                 | 5.6K, 1%, 0.1W 0603 | Neohm        |

| R2        |                 | 3.3K, 1%, 0.1W 0603 | Neohm        |

| R3        |                 | 4.7K, 1%, 0.1W 0603 | Neohm        |

| D1        | STPS2L25U       | 2A, 25V             | ST           |

| L1        | DO3316P-153     | 15µH, 3A            | COILCRAFT    |

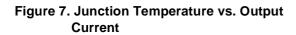

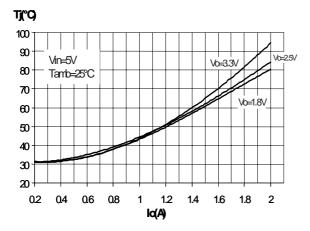

Figure 8. Junction Temperature vs Output Current

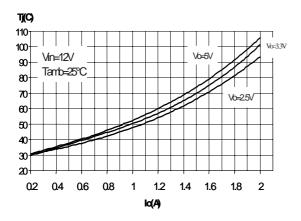

Figure 9. Efficiency vs. Output Current

Figure 10. Efficiency vs. Output Current

57

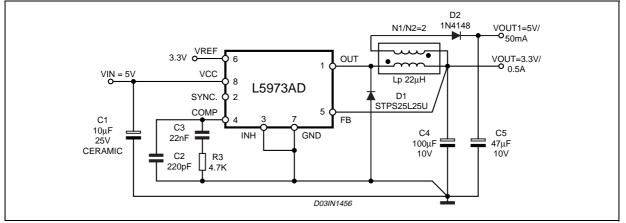

# APPLICATION IDEAS

# Figure 11. Positive Buck-Boost regulator

# Figure 12. Buck-Boost regulator

Refer to L5973AD application note (AN1723) to have additional information, details, and more application ideas.

L5973AD belongs to L597x family.

Related part numbers are:

- L5970D: 1.5A (I<sub>sw</sub>), 250KHz Step Down DC-DC Converter in SO8

- L5972D: 2A (I<sub>sw</sub>), 250KHz Step Down DC-DC Converter in SO8

- L5972D: 2.5A (I<sub>sw</sub>), 250KHz Step Down DC-DC Converter in HSOP8

- In case higher current is needed, the nearest DC-DC Converter family is L497x.

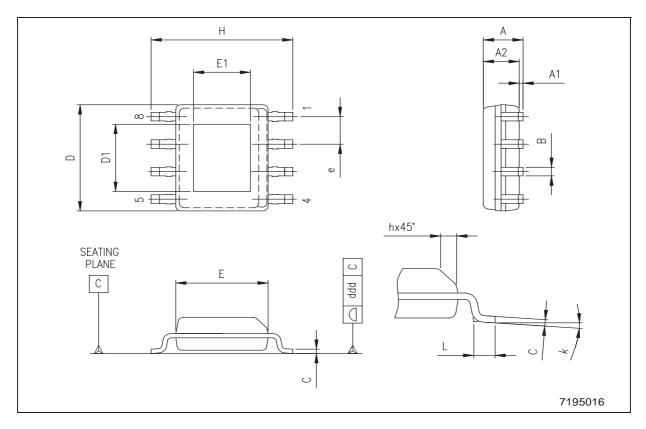

| DIM.                                                                                                                          | mm                 |       |       | inch  |      |       |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|-------|-------|------|-------|--|

|                                                                                                                               | MIN.               | TYP.  | MAX.  | MIN.  | TYP. | MAX.  |  |

| А                                                                                                                             | 1.350              |       | 1.750 | 0.531 |      | 0.069 |  |

| A1                                                                                                                            | 0.100              |       | 0.250 | 0.004 |      | 0.010 |  |

| A2                                                                                                                            | 1.100              |       | 1.650 | 0.043 |      | 0.065 |  |

| В                                                                                                                             | 0.330              |       | 0.510 | 0.013 |      | 0.020 |  |

| С                                                                                                                             | 0.190              |       | 0.250 | 0.07  |      | 0.010 |  |

| D                                                                                                                             | 4.800              |       | 5.000 | 0.189 |      | 0.197 |  |

| E                                                                                                                             | 3.800              |       | 4.000 | 0.150 |      | 0.157 |  |

| е                                                                                                                             |                    | 1.270 |       |       | 0.05 |       |  |

| н                                                                                                                             | 5.800              |       | 6.200 | 0.228 |      | 0.244 |  |

| h                                                                                                                             | 0.250              |       | 0.500 | 0.010 |      | 0.020 |  |

| L                                                                                                                             | 0.400              |       | 1.270 | 0.016 |      | 0.05  |  |

| k                                                                                                                             | 0° (min), 8° (max) |       |       |       |      |       |  |

| ddd                                                                                                                           |                    |       | 0.100 |       |      | 0.010 |  |

| <ol> <li>Dimension D does not include mold flash, protusions<br/>or gate burrs shall not exeed 0.15mm (both side).</li> </ol> |                    |       |       |       |      |       |  |

# OUTLINE AND

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

STMicroelectronics acknowledges the trademarks of all companies referred to in this document.

The ST logo is a registered trademark of STMicroelectronics © 2003 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com