19-1215; Rev 1; 4/98

#

# 155Mbps Preamplifier for FDDI and ATM LAN Fiber Optic Receivers

## **General Description**

The MAX3963 is a low-noise transimpedance preamplifier for FDDI and 155Mbps ATM optical receivers. The MAX3963's dynamic range is optimized for use in multimode LED-based applications.

The preamplifier converts a small photodiode current to a differential voltage, with typical transimpedance of 22kΩ. Input-referred noise of only 21nA allows detection of signals as small as 267nA, while pulse-width distortion is only 85ps with a 60µA input signal. In a 1300nm multimode receiver, with responsivity of 0.7A/W, the MAX3963's dynamic range spans from -36dBm to -13.7dBm. The circuit operates from a single +5V supply, and typically consumes only 60mW power.

The MAX3963 die includes a filter connection, which provides positive bias for the photodiode through a  $1k\Omega$ resistor to VCC. This feature, combined with the small die size, allows the MAX3963 to fit easily into a TO-style package with a photodiode.

The differential outputs are back terminated with  $60\Omega$ per side, allowing the easy use of filters to improve sensitivity.

The MAX3963 is designed to be used with the MAX3964 limiting amplifier IC. It is available in an 8-pin SO package and as dice.

Applications

**FDDI**

155Mbps ATM

#### Features

- 21nA Total RMS Noise

- 22kΩ Differential Transimpedance

- 180MHz Bandwidth

- ♦ 60mW Typical Power Consumption

- ♦ 60µA Peak Input Current

- ◆ Low, 85ps Pulse-Width Distortion

## **Ordering Information**

| PART |            | TEMP. RANGE   | PIN-PACKAGE |

|------|------------|---------------|-------------|

|      | MAX3963CSA | 0°C to +70°C  | 8 SO        |

|      | MAX3963C/D | 0°C to +70°C* | Dice        |

\*Dice are designed to operate over a 0°C to +100°C junction temperature  $(T_i)$  range, but are tested and guaranteed at  $T_A =$ +25°C.

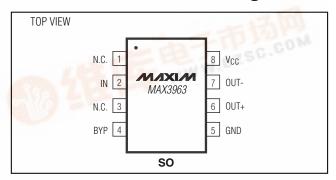

## Pin Configuration

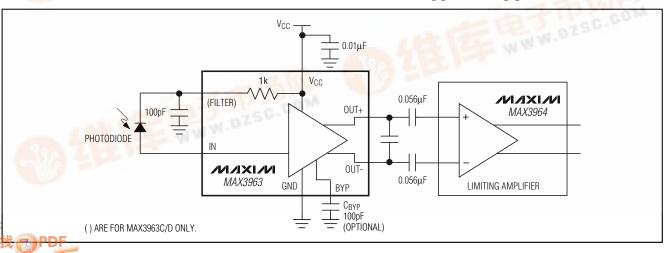

# Typical Application Circuit

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>C</sub> C                                      | 0.5V to +7.0V |

|-------------------------------------------------------|---------------|

| Continuous Current                                    |               |

| IN                                                    | 5mA           |

| OUT+, OUT                                             | 25mA          |

| BYP                                                   | 5mA           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

| SO (derate 5.88mW/°C above +70°C)                     | 471mW         |

| Storage Temperature Range            | 65°C to +150°C |

|--------------------------------------|----------------|

| Lead Temperature (soldering, 10sec)  | +300°C         |

| Operating Junction Temperature (die) |                |

| Processing Temperature (die)         | +400°C         |

|                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(VCC = +4.5V to +5.5V, CBYP = 100pF,  $1k\Omega$  load between OUT+ and OUT-,  $T_A = 0$ °C to +70°C. Typical values are at VCC = 5.0V,  $T_A = +25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER                              | SYMBOL                   | CONDITIONS                        | MIN  | TYP                    | MAX  | UNITS |

|----------------------------------------|--------------------------|-----------------------------------|------|------------------------|------|-------|

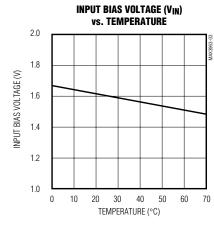

| Input Bias Voltage                     | VIN                      | Input = 0µA to 60µA               |      | 1.6                    | 1.8  | V     |

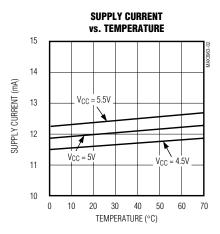

| Supply Current                         | Icc                      | Input = 0µA                       |      | 12                     | 20   | mA    |

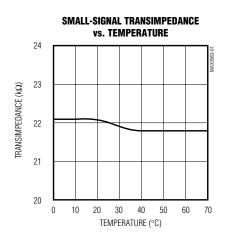

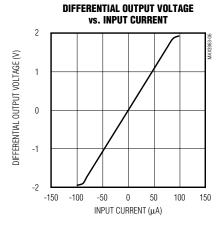

| Small-Signal Transimpedance            | Z21                      | Differential output, input < 60µA | 17.5 | 22                     | 26.3 | kΩ    |

| Output Common-Mode Voltage             |                          |                                   |      | V <sub>CC</sub> - 2.85 | 5    | V     |

| Power-Supply Rejection Ratio           | PSRR                     | f < 1MHz, referred to output      | 35   |                        |      | dB    |

| Output Resistance (per side)           | Rout                     |                                   | 45   | 60                     | 68   | Ω     |

| Maximum Differential Output<br>Voltage | V <sub>OD</sub><br>(MAX) | I <sub>IN</sub> = 80μA            |      |                        | 2.2  | V     |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +4.5V \text{ to } +5.5V, C_{BYP} = 100pF, C_{IN} = 1.15pF, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Notes 2, 3)

| PARAMETER                     | SYMBOL             | CONDITIONS                         | MIN | TYP | MAX  | UNITS |

|-------------------------------|--------------------|------------------------------------|-----|-----|------|-------|

| Small-Signal Bandwidth        | BW <sub>-3dB</sub> | C <sub>OUT</sub> = 5pF             | 100 | 180 | 220  | MHz   |

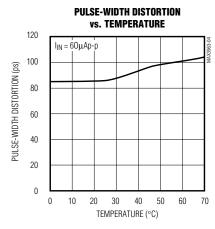

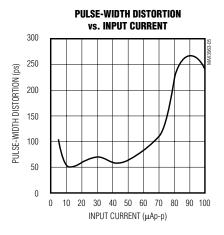

| Pulse-Width Distortion        | PWD                | I <sub>IN</sub> = 60µAp-p (Note 4) |     | 85  | 160  | ps    |

| RMS Noise Referred to Input   | t in               | (Note 5)                           |     | 21  | 24.5 | nA    |

| Tivio Noise Neterred to input |                    | (Note 6)                           |     | 37  |      | nA    |

- **Note 1:** Dice are tested at  $T_A = +25$ °C only.

- Note 2: AC characteristics are guaranteed by design.

- Note 3: CIN is the total capacitance at IN. COUT is the differential output capacitive load.

- Note 4: PWD = [(width of wider pulse) (width of narrower pulse)] / 2. Input is a 155Mbps 1-0 pattern, with rise time approximately 2ns

- Note 5: Measured with a 117MHz, 3-pole Bessel filter.

- **Note 6:** Measured with  $C_{OUT} = 5pF$ ,  $T_A = +25$ °C.

# **Typical Operating Characteristics**

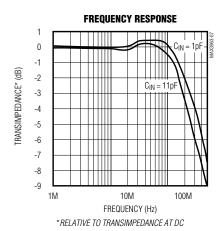

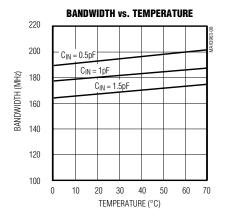

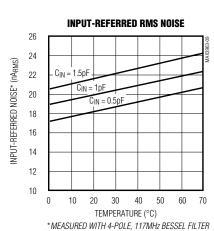

( $V_{CC} = 5.0V$ ,  $C_{BYP} = 100pF$ ,  $C_{IN} = 1.3pF$ ,  $T_A = +25$ °C, unless otherwise noted.)

# **Pin Description**

| PIN  | NAME    | FUNCTION                                                                                   |  |

|------|---------|--------------------------------------------------------------------------------------------|--|

| 1, 3 | N.C.    | No Connect. No internal connection to the die.                                             |  |

| 2    | IN      | Signal Input                                                                               |  |

| 4    | BYP     | Connection for optional noise-reducing capacitor                                           |  |

| 5    | GND     | Signal Ground                                                                              |  |

| 6    | OUT+    | Noninverting Voltage Output. Current flowing into IN causes V <sub>OUT+</sub> to increase. |  |

| 7    | OUT-    | Inverting Voltage Output. Current flowing into IN causes VOUT- to decrease.                |  |

| 8    | Vcc     | Supply Voltage                                                                             |  |

| _    | FILTER* | Connection for $1k\Omega$ filter resistor. This pad is accessible on the die only.         |  |

<sup>\*</sup>MAX3963C/D (die) only.

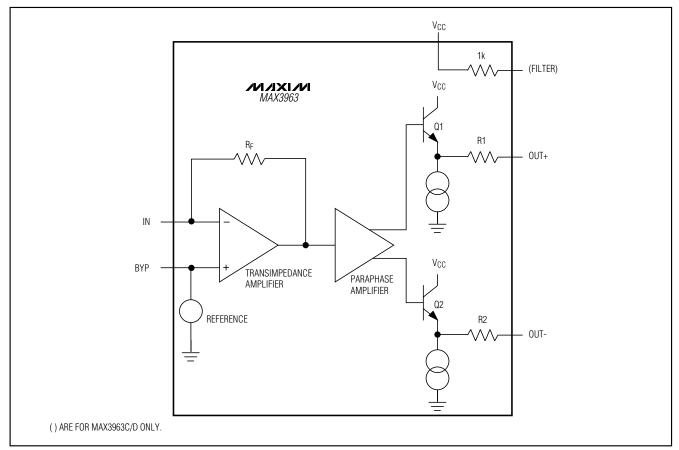

Figure 1. Functional Diagram

## **Detailed Description**

The MAX3963 transimpedance amplifier is designed for 155Mbps fiber optic applications. Figure 1 is a functional diagram of the MAX3963, which comprises a transimpedance amplifier and a paraphase amplifier with emitter-follower outputs.

#### **Transimpedance Amplifier**

The signal current at the input flows into the summing node of a high-gain amplifier. Shunt feedback through RF converts this current to a voltage with a  $10k\Omega$  gain.

#### **Paraphase Amplifier**

The paraphase amplifier converts single-ended signals to differential signals and introduces a 2x voltage gain. This signal drives a pair of internally biased emitter followers, Q1 and Q2, which form the output stage. Resistors R1 and R2 provide back termination at the output, providing a  $120\Omega$  differential output impedance.

The output emitter followers are designed to drive a  $1k\Omega$  differential load between OUT+ and OUT-. Higher output impedances can also be driven, resulting in slightly increased gain and output voltage swing. The MAX3963 will not drive a  $50\Omega$  grounded load. The MAX3963 outputs may be AC coupled to a limiting amplifier.

## Applications Information

#### **Optical-Power Relations**

Many of the MAX3963 specifications relate to the input signal amplitude. When working with fiber optic receivers, the input is usually expressed in terms of average optical power and extinction ratio. The relations shown in Table 1 are helpful for converting optical power to input signal when designing with the MAX3963. These relations are true if the average data duty cycle is 50%.

## **Calculating Sensitivity and Overload**

#### Sensitivity Calculation

The MAX3963's input-referred RMS noise current (in) generally dominates receiver sensitivity. In a system where the bit error rate is 1E-10, the signal-to-noise ratio must always exceed 12.7. The sensitivity, expressed in average power, can be estimated as shown in the following equation:

Sensitivity =

$$10\log \left(\frac{12.7 i_n (re + 1)}{2p (re - 1)} \times 1000\right) dBm$$

where  $\rho$  is the photodiode responsivity in A/W.

#### Input Overload

The overload is the largest input that the MAX3963 accepts while meeting specifications. A larger input causes increased pulse-width distortion.

Overload =

$$10\log\left(\frac{60\mu\text{A}}{2\rho} \times 1000\right)\text{dBm}$$

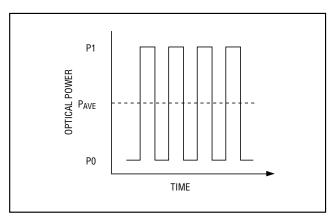

# Table 1. Optical-Power Relations\*

| PARAMETER              | SYMBOL         | RELATION                                                                |

|------------------------|----------------|-------------------------------------------------------------------------|

| Average<br>Power       | Pave           | PAVE = (P0 + P1) / 2                                                    |

| Extinction<br>Ratio    | r <sub>e</sub> | r <sub>e</sub> = P1 / P0                                                |

| Optical Power of a "1" | P1             | P1 = 2PAVE (r <sub>e</sub> ) / (r <sub>e</sub> + 1)                     |

| Optical Power of a "0" |                | P0 = 2P <sub>AVE</sub> / (r <sub>e</sub> + 1)                           |

| Signal<br>Amplitude    | PINPUT         | PINPUT = P1 - P0 =<br>2PAVE (r <sub>e</sub> - 1) / (r <sub>e</sub> + 1) |

<sup>\*</sup>Assuming 50% average data duty cycle

Figure 2. Optical-Power Definitions

#### **Output Filter**

The MAX3963's noise can be reduced by filtering the output signal. For digital communications systems, a linear-phase filter with -3dB lowpass response of (0.7 x data rate) is recommended.

A single-pole filter implemented with a capacitor across the outputs also reduces noise, and consumes less board space than a linear-phase filter. The following equation represents the filter frequency:

$$f_{-3dB} = \frac{1}{2\pi R_{OUT} C_{OUT}}$$

where  $R_{OUT}$  is the MAX3963 differential output resistance (typically 120 $\Omega$ ), and  $C_{OUT}$  is the differential output load capacitance. For 155Mbps receivers, an 11pF capacitor is recommended.

#### **Layout Considerations**

Use good high-frequency design and layout techniques. The use of a multilayer circuit board with separate ground and V<sub>CC</sub> planes is recommended. Bypass V<sub>CC</sub> and connect the GND pin to the ground plane with traces kept as short as possible. Ensure that commonmode output capacitance is less than 2pF per output.

# Low-Capacitance Input Design Considerations

Noise performance and bandwidth are adversely affected by stray capacitance on the input node. Every effort must be made to minimize capacitance on this pin. Select a low-capacitance photodiode, and use good high-frequency design and layout techniques. The MAX3963 is optimized for 1.0pF of capacitance on the input, approximately the capacitance of a photodetector diode packaged in a header.

When using the SO package version of the MAX3963, the package capacitance is about 0.3pF. This means that great care must be used to reduce input capacitance. The PC board between the MAX3963 input and the photodiode can add parasitic capacitance. Keep the input line short, and remove power and ground planes beneath it.

Assembling the MAX3963 in die form provides the best possible performance. Parasitic capacitance can be reduced to a minimum, resulting in the lowest noise and the best bandwidth.

#### Wire Bonding

For high current density and reliable operation, the MAX3963 uses gold metalization. Make connections to the die with gold wire only, using ball-bonding techniques. Wedge bonding is not recommended. Die-pad size is 4mils square, with 6mil pitch. Die thickness is 15mils.

## Chip Topography

TRANSISTOR COUNT: 116

SUBSTRATE CONNECTED TO GND

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.