查询MAX3968供应商

19-1314; Rev 0; 10/98

## EVALUATION KIT MANUAL FOLLOWS DATA SHEET

# +3.0V to +5.5V, 125Mbps to 266Mbps Limiting Amplifiers with Loss-of-Signal Detector

## **General Description**

The MAX3964 limiting amplifier, with 3.3mV input sensitivity and PECL data outputs, is ideal for low-cost ATM, FDDI, and Fast Ethernet fiber optic applications.

The MAX3964 features an integrated power detector that senses the input-signal power. It provides a received-signal-strength indicator (RSSI), which is an analog indication of the power level and complementary PECL loss-of-signal (LOS) outputs, which indicate when the power level drops below a programmable threshold. The threshold can be adjusted to detect signal amplitudes as low as 2.7mVp-p. An optional squelch function disables switching of the data outputs by holding them at a known state during an LOS condition.

The MAX3965 provides the same functionality, but offers TTL-compatible LOS outputs. The MAX3968 provides the same functionality as the MAX3964, but has data-output edge speed suitable for ESCON and 266Mbps fibre channel applications.

The MAX3964/MAX3965/MAX3968 are available in die form, as tested wafers, and in 20-pin QSOP packages.

### **Applications**

125Mbps FDDI Receivers

155Mbps LAN ATM Receivers

Fast Ethernet Receivers

ESCON Receivers

266Mbps Fibre Channel Receivers

- ♦ Single Supply: +3.0V to +5.5V

- ◆ 3.3mV Input Sensitivity

- ♦ 1.4ns Output Edge Speed

- Loss-of-Signal Detector with Programmable Threshold

捷多邦,专业PCB打样工厂,24小时加急出货

MVXVN

- Analog Received-Signal-Strength Indicator

- Output Squelch Function

- Choice of TTL or PECL LOS Outputs

- Compatible with 4B/5B Data Coding

### **Ordering Information**

Features

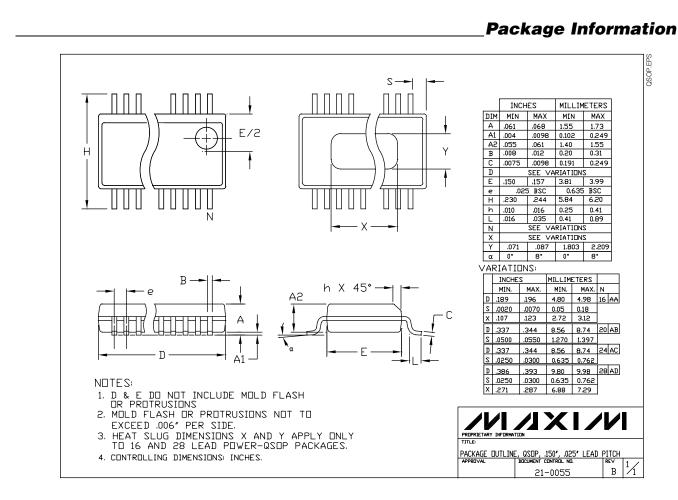

| PART        | TEMP. RANGE  | PIN-PACKAGE |

|-------------|--------------|-------------|

| MAX3964CEP  | 0°C to +70°C | 20 QSOP     |

| MAX3964C/D  | 0°C to +70°C | Dice*       |

| MAX3964C/DW | 0°C to +70°C | Wafers*     |

| MAX3965CEP  | 0°C to +70°C | 20 QSOP     |

| MAX3965C/D  | 0°C to +70°C | Dice*       |

| MAX3965C/DW | 0°C to +70°C | Wafers*     |

| MAX3968CEP  | 0°C to +70°C | 20 QSOP     |

| MAX3968C/D  | 0°C to +70°C | Dice*       |

| MAX3968C/DW | 0°C to +70°C | Wafers*     |

\*Dice and wafers are designed to operate over a 0°C to +100°C junction temperature ( $T_j$ ) range, but are tested and guaranteed only at  $T_A = +25$ °C.

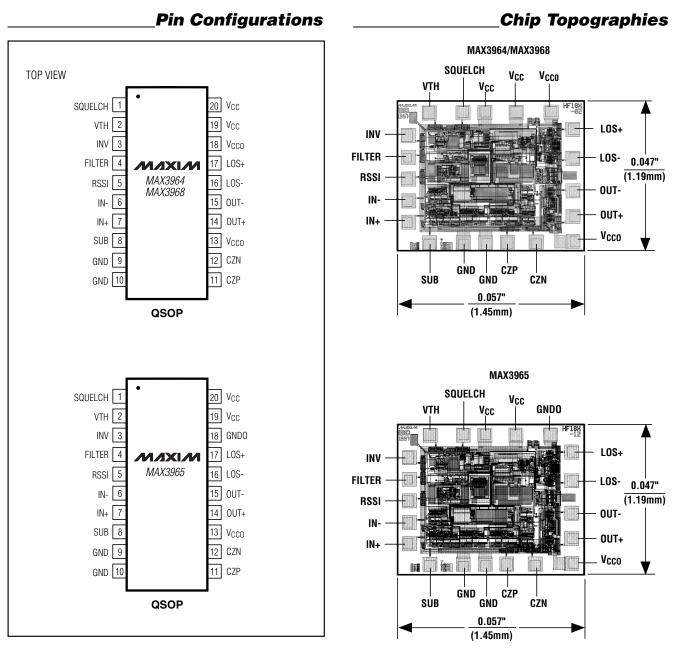

#### Pin Configurations appear at end of data sheet.

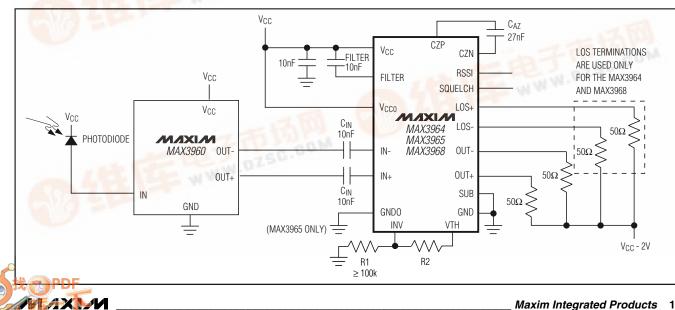

## \_Typical Operating Circuit

If.dzsc.com For free samples and the latest literature, visit www.maxim-ic.com or phone 1-800-998-8800.

| MAX3964/MAX3965/MAX396        | <b>WAX3964/MAX3965/MAX3</b> ( | Q                     |

|-------------------------------|-------------------------------|-----------------------|

| <b>WAX3964/MAX3965/MAX3</b> ( | <b>WAX3964/MAX3965/MAX3</b> ( | Ó                     |

| <b>WAX3964/MAX3965/MAX3</b> ( | <b>WAX3964/MAX3965/MAX3</b> ( | X                     |

| <b>WAX3964/MAX3965/MAX</b> ;  | <b>WAX3964/MAX3965/MAX</b> ;  | 5                     |

| <b>WAX3964/MAX3965/MAX</b>    | <b>WAX3964/MAX3965/MAX</b>    | $\boldsymbol{\sigma}$ |

| <b>WAX3964/MAX3965/MA</b> .   | <b>WAX3964/MAX3965/MA</b> .   |                       |

| <b>WAX3964/MAX3965/M</b> /    | <b>WAX3964/MAX3965/M</b> /    |                       |

| <b>WAX3964/MAX3965/M</b>      | <b>WAX3964/MAX3965/M</b>      | 5                     |

| <b>WAX3964/MAX3965/I</b>      | <b>WAX3964/MAX3965/I</b>      |                       |

| <b>WAX3964/MAX3965/</b>       | <b>WAX3964/MAX3965/</b>       |                       |

| <b>WAX3964/MAX396</b> {       | <b>WAX3964/MAX396</b> {       |                       |

| MAX3964/MAX3                  | MAX3964/MAX3                  | 2                     |

| MAX3964/MAX3                  | MAX3964/MAX3                  | 0                     |

| MAX3964/MAX                   | MAX3964/MAX                   | Ó                     |

| MAX3964/MAX                   | MAX3964/MAX                   | Ň                     |

| <b>WAX3964/MAX</b>            | <b>WAX3964/MAX</b>            | N                     |

| MAX3964/MA                    | MAX3964/MA                    | <b>X</b>              |

| MAX3964/M                     | MAX3964/M                     | đ                     |

| MAX3964/N                     | MAX3964/N                     | 2                     |

| MAX3964/                      | MAX3964/                      |                       |

| <b>WAX3964</b>                | <b>WAX3964</b>                |                       |

| MAX                           | MAX                           |                       |

| MAX                           | MAX                           | Õ                     |

| MAX                           | MAX                           | X                     |

| MAX                           | MAX                           | 2                     |

| MAX                           | MAX                           |                       |

| MA.                           | MA.                           |                       |

| Š                             | Š                             |                       |

| 5                             | 5                             | P                     |

|                               |                               | ₹                     |

|                               |                               |                       |

### **ABSOLUTE MAXIMUM RATINGS**

(SUB, GND, GNDO tied to ground)

V<sub>CC</sub>, V<sub>CCO</sub>.....-0.5V to +7.0V FILTER, RSSI, IN+, IN-, CZP, CZN, SQUELCH, LOS+, LOS-, INV, VTH, OUT+, OUT-....-0.5V to (V<sub>CC</sub> + 0.5V) PECL Output Current (OUT+, OUT-, LOS+, LOS-) ..........50mA Differential Voltage Between CZP and CZN.......-1.5V to +1.5V Differential Voltage Between IN+ and IN-......-1.5V to +1.5V Continuous Power Dissipation ( $T_A = +70^{\circ}$ C) QSOP (derate 6.7mW/°C above +70°C)......500mW Operating Temperature Range.....-40°C to +85°C Operating Junction Temperature Range (die)....-40°C to +150°C Processing Temperature (die).....+400°C Storage Temperature Range .....-65°C to +160°C Lead Temperature (soldering, 10sec).....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +5.5V, \text{PECL} \text{ outputs terminated with } 50\Omega \text{ to } (V_{CC} - 2V), T_A = 0^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                    | CONDITIONS                                  | MIN   | ТҮР | MAX   | UNITS |

|------------------------------|---------------------------------------------|-------|-----|-------|-------|

| Supply Current               | Excludes PECL output current                |       | 22  | 40    | mA    |

| LOS Hysteresis               | (Note 2)                                    | 3.8   | 5   | 8.0   | dB    |

| SQUELCH Input Current        | VSQUELCH = VCC, TA = +25°C                  |       | 27  | 100   | μA    |

| PECL Output Voltage High     | (Note 3)                                    | -1025 |     | -880  | mV    |

| PECL Output Voltage Low      | (Note 3)                                    | -1810 |     | -1620 | mV    |

| PECL LOS Output Voltage High | (Note 3)                                    | -1035 |     | -880  | mV    |

| PECL LOS Output Voltage Low  | (Note 3)                                    | -1810 |     | -1620 | mV    |

| LOS Assert Accuracy          | Input = 7mVp-p or 90mVp-p                   | -2.5  |     | 2.5   | dB    |

| Minimum LOS Assert Input     |                                             |       |     | 2.7   | mVp-p |

| Maximum LOS Deassert Input   |                                             | 143   |     |       | mVp-p |

| Input Sensitivity            |                                             |       | 2.0 | 3.3   | mVp-p |

| Input Overload               |                                             | 1.5   |     |       | Vp-p  |

| Data Output Edge Speed       | 20% to 80% transition time, MAX3964/MAX3965 | 0.92  | 1.2 | 2.2   | - ns  |

|                              | MAX3968                                     | 0.4   | 0.8 | 1.2   |       |

| Pulse-Width Distortion       | (Note 4)                                    |       | 50  | 200   | ps    |

| TTL Output High              | I <sub>OH</sub> = -200μA                    | 2.4   | 3.1 | Vcc   | V     |

| TTL Output Low               | I <sub>OL</sub> = 200μA                     | 0     | 0.3 | 0.4   | V     |

**Note 1:** Dice are tested and guaranteed at  $T_A = +25^{\circ}C$  only.

Note 2: LOS hysteresis = 20log(VLOS-DEASSERT / VLOS-ASSERT). Input = 3.3mVp-p to 90mVp-p.

Note 3: Voltage measurements are relative to supply voltage (V<sub>CC</sub>).

Note 4: PWD = [(width of wider pulse) - (width of narrower pulse)] / 2, measured with 100Mbps 1-0 pattern.

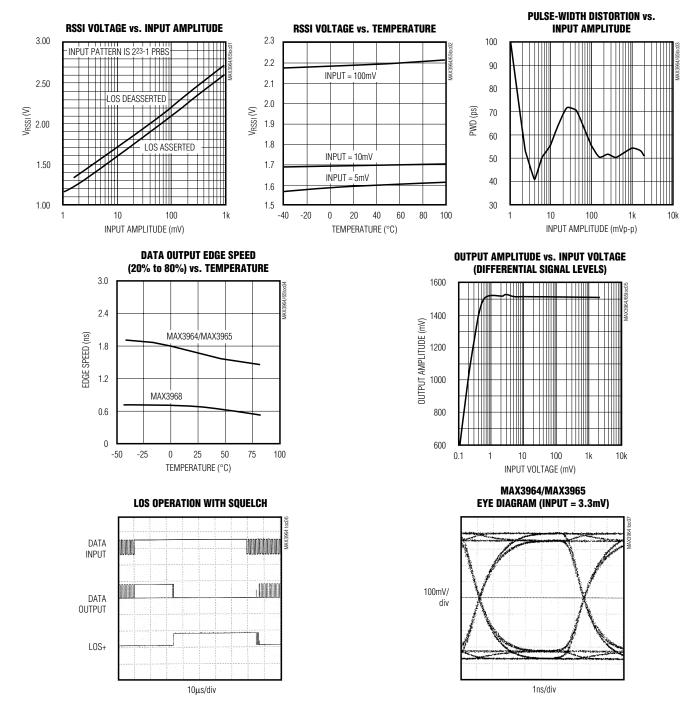

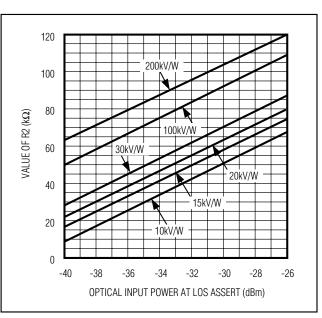

### Typical Operating Characteristics

(MAX3964 evaluation kit,  $V_{CC}$  = +3.3V, decibels (dB) calculated as 20 log  $\Delta V$ , PECL outputs terminated with 50 $\Omega$  to (V<sub>CC</sub> - 2V), T<sub>A</sub> = +25°C, unless otherwise noted.)

MAX3964/MAX3965/MAX3968

### **Pin Description**

| PIN    | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                            |  |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | SQUELCH | Squelch Input. The squelch function disables the data outputs by forcing OUT- low and OUT+ high during a loss-of-signal condition. Connect to GND or leave unconnected to disable. Connect to V <sub>CC</sub> to enable squelching.                                                                                 |  |

| 2      | VTH     | Output of Internal Op Amp that Sets Loss-of-Signal Threshold Voltage (Figure 1). Connect a resistor from VTH to INV, and from INV to ground (minimum resistance $100k\Omega$ ) to program the desired threshold voltage.                                                                                            |  |

| 3      | INV     | Inverting Input of Internal Op Amp that Sets Loss-of-Signal Threshold Voltage (Figure 1). Connect a resistor from VTH to INV, and from INV to ground (minimum resistance $100k\Omega$ ) to program the desired threshold voltage.                                                                                   |  |

| 4      | FILTER  | Filter Output of Full-Wave Logarithmic Detectors (FWDs). The FWD outputs are summed together at FILTER to generate the received-signal-strength indicator (RSSI). Connect a capacitor from FILTER to $V_{CC}$ for proper operation.                                                                                 |  |

| 5      | RSSI    | Received-Signal-Strength Indicator Output. The analog DC voltage at RSSI indicates the input signal power. The RSSI output is reduced approximately 120mV when LOS+ is asserted.                                                                                                                                    |  |

| 6      | IN-     | Inverting Data Input                                                                                                                                                                                                                                                                                                |  |

| 7      | IN+     | Noninverting Data Input                                                                                                                                                                                                                                                                                             |  |

| 8      | SUB     | Substrate. Connect to ground.                                                                                                                                                                                                                                                                                       |  |

| 9, 10  | GND     | Ground                                                                                                                                                                                                                                                                                                              |  |

| 11     | CZP     | Auto-Zero Capacitor Input. Connect a capacitor between CZP and CZN to determine the offset-<br>correction-loop bandwidth.                                                                                                                                                                                           |  |

| 12     | CZN     | Auto-Zero Capacitor Input. Connect a capacitor between CZP and CZN to determine the offset-<br>correction-loop bandwidth.                                                                                                                                                                                           |  |

| 13     | Vcco    | Output Buffer Supply Voltage. Connect to the same potential as $V_{CC},$ but filter $V_{CCO}$ and $V_{CC}$ separately.                                                                                                                                                                                              |  |

| 14     | OUT+    | Noninverting PECL Data Output. Terminate with 50 $\Omega$ to (V <sub>CC</sub> - 2V).                                                                                                                                                                                                                                |  |

| 15     | OUT-    | Inverting PECL Data Output. Terminate with 50 $\Omega$ to (V <sub>CC</sub> - 2V).                                                                                                                                                                                                                                   |  |

| 16     | LOS-    | Inverting Loss-of-Signal Output. LOS- is asserted low when input power drops below the LOS threshold. For the MAX3964/MAX3968, this pin is PECL-compatible and should be terminated with 50 $\Omega$ to (V <sub>CC</sub> - 2V). For the MAX3965, this output is TTL-compatible and does not require termination.    |  |

| 17     | LOS+    | Noninverting Loss-of-Signal Output. LOS+ is asserted high when input power drops below the LOS threshold. For the MAX3964/MAX3968, this pin is PECL-compatible and should be terminated with $50\Omega$ to (V <sub>CC</sub> - 2V). For the MAX3965, this output is TTL-compatible and does not require termination. |  |

| 18     | Vcco    | MAX3964/MAX3968: This pin may be left open or connected to the positive supply.                                                                                                                                                                                                                                     |  |

| 10     | GNDO    | MAX3965: This pin must be connected to ground.                                                                                                                                                                                                                                                                      |  |

| 19, 20 | Vcc     | +3.0V to +5.5V Supply Voltage                                                                                                                                                                                                                                                                                       |  |

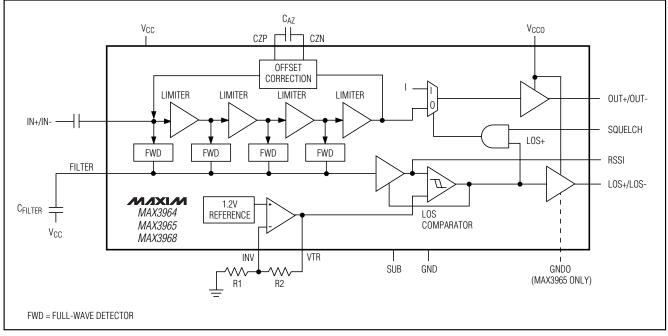

Figure 1. Functional Diagram

### **Detailed Description**

The MAX3964 contains a series of limiting amplifiers and power detectors, offset correction, data-squelch circuitry, and PECL output buffers for data and loss-ofsignal (LOS) outputs. The MAX3965 is functionally the same, but it provides TTL buffers on the LOS outputs. The MAX3968 provides PECL LOS outputs with data outputs suitable for 266Mbps. Figure 1 shows a functional diagram of the MAX3964/MAX3965/MAX3968.

#### **Limiting Amplifiers**

A series of four limiting amplifiers provides gain of approximately 65dB.

#### **Power Detector**

Each amplifier stage contains a full-wave logarithmic detector (FWD), which indicates the RMS input signal power. The FWD outputs are summed together at the FILTER pin where the signal is filtered by an external capacitor (CFILTER) connected between FILTER and VCC. The FILTER signal generates the RSSI output voltage, which is proportional to the input power in decibels. When LOS+ is low, VRSSI is approximated by the following equation:

$V_{RSSI}(V) = 1.2V + 0.5log(V_{IN})$

where VIN is measured in mVp-p.

This relation translates to a 25mV increase in VRSSI for every 1dB increase in VIN (25mV/dB). The RSSI output is reduced approximately 120mV when LOS+ is asserted.

#### **PECL Outputs**

The data outputs (OUT+, OUT-) and the MAX3964/MAX3968 loss-of-signal outputs (LOS+, LOS-) are supply-referenced PECL outputs. Standard PECL termination at each output of 50 $\Omega$  to (V<sub>CC</sub> - 2V) is recommended for best performance.

### TTL Outputs

The MAX3965 LOS outputs (LOS+, LOS-) are implemented with open-collector Schottky-clamped TTL-compatible outputs. The LOS outputs are pulled to V<sub>CC</sub> internally with  $2k\Omega$  resistors and do not require external pull-up resistors.

#### **Input Offset Correction**

A low-frequency feedback loop around the limiting amplifier improves receiver sensitivity and powerdetector accuracy. The offset-correction loop's bandwidth is determined by an external capacitor (CAZ) connected between the CZP and CZN pins.

The offset correction is optimized for data streams with a 50% duty cycle. A different average duty cycle results in increased pulse-width distortion and loss of

sensitivity. The offset-correction circuitry is less sensitive to variations of input duty cycle (for example, the 40% to 60% duty cycle encountered in 4B/5B coding) when the input is less than 30mVp-p.

#### **Loss-of-Signal Comparator**

The LOS comparator indicates when the input signal power is below the programmed LOS threshold. To ensure supply and temperature independence, VTH is generated by a 1.2V bandgap reference. The op amp's external gain-setting resistors (R1 and R2) can be chosen to set VTH between 1.2V and 2.4V. To ensure chatter-free operation, the LOS comparator is designed with approximately 5dB of hysteresis.

**Squelch** The squelch function disables the data outputs by forcing OUT- low and OUT+ high during a LOS condition. This function ensures that when there is a loss of signal, the limiting amplifier (and all downstream devices) does not respond to input noise or corrupt data. Connect SQUELCH to GND or leave it unconnected to disable squelch. Connect SQUELCH to V<sub>CC</sub> to enable data squelching.

## **Applications Information**

### **Program the LOS Threshold**

Figure 2 provides information for selecting the LOS threshold voltage (V<sub>TH</sub>). If R1 is 100k $\Omega$  and if the responsivities of the photodiode and preamplifier are known, then the value of R2 can be selected from Figure 2 to provide LOS assert at the desired input power.

#### **Select Capacitors**

A typical MAX3964/MAX3965/MAX3968 implementation requires four external capacitors (C<sub>AZ</sub>, C<sub>FILTER</sub>, and two input coupling capacitors). For all applications up to 266Mbps, Maxim recommends the following:

$C_{AZ} = 27nF$  $C_{FILTER} = 10nF$  $C_{IN} = 10nF$

#### Wire Bonding

For high-current density and reliable operation, the MAX3964 series uses gold metalization. Make connections to the dice with gold wire only, using ball-bonding techniques (wedge bonding is not recommended). Diepad size is 4mils square with a 6mil pitch. Die thickness is 15mils.

Figure 2. LOS Assert Programming Resistor vs. LOS Assert Power (for various PIN-TIA gains )

TRANSISTOR COUNT: 915 SUBSTRATE CONNECTED TO SUB