# SONY CXK77910ATM/AYM -10/12

## 131,072-word by 9-bit High-Speed Synchronous Static RAM

#### Description

The CXK77910ATM/AYM are high-speed CMOS synchronous static RAMs with common I/O pins, 131,072-word-by-9-bit. organized These synchronous SRAMs integrate input registers, high speed SRAM and output registers onto a single monolithic IC. All input signals are latched at the positive edge of an external clock (CLK). The RAM data from the previous cycle is presented at the positive edge of the subsequent clock cycle. Write operation is initiated by the positive edge of CLK and is internally self-timed. This feature eliminates complex off-chip write pulse generation and provides increased flexibility for incoming signals. 100MHz operation is obtained from a single 5V power supply.

#### **Function**

There are three possible user transactions with the STRAM — read operation, write operation and deselect operation.

\_\_\_\_The read operation requires WE = "HIGH" and OE = CE = "LOW" on the positive edge of CLK.

The memory location pointed to by the contents of the Address registers is read internally and the contents of the location are captured in the Data-out registers on the next positive edge of CLK. The state of Data-out will reflect the contents of the Data-out registers.

The write operation requires CE = WE = "LOW" on the positive edge of CLK. The memory location pointed to by the contents of the Address registers is written with the contents of the Data-in registers. The write operation is entirely self-timed, eliminating critical timing edges.

The deselect cycle requires CE = "HIGH" or OE = WE = "HIGH" on the positive edge of CLK. Write operation and internal read operation are disabled during the clock

cycle. The data outputs are forced to a high impedance state during the next clock cycle. During the deselect cycle by CE = "HIGH", STRAM turns to power down mode.

#### **Structure**

Silicon gate CMOS IC

#### **Features**

Fast cycle time: (Cycle) (Frequency)

CXK77910ATM/AYM-10 10.0ns 100MHz

CXK77910ATM/AYM-12 12.5ns 80MHz

Fast clock to data valid

CXK77910ATM/AYM-10 5.5ns

CXK77910ATM/AYM-12 6.5ns

- High speed, low power consumption

- Single +5V power supply: 5V ± 5%

- Separate output power supply: 3.15V to 5.25V

- Inputs and outputs are TTL compatible (3.3V I/O compatible)

- Common data input and output

- All inputs and outputs are registered on a single clock edge

- · Self-timed write cycle

- Package line-up: 400mil 44 pin TSOP II with 0.8mm pitch

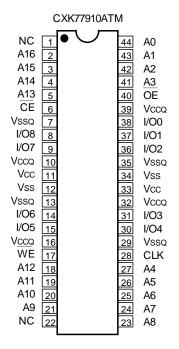

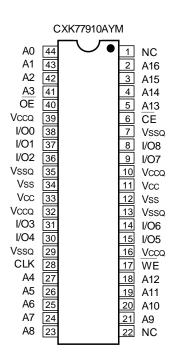

## Pin Configurations (Top View)

#### Pin Description (1)

| Symbol       | Description         |  |  |  |

|--------------|---------------------|--|--|--|

| A0 to A16    | Address input       |  |  |  |

| I/O0 to I/O8 | Data input/output   |  |  |  |

| CLK          | Clock               |  |  |  |

| CE           | Chip enable input   |  |  |  |

| WE           | Write enable input  |  |  |  |

| ŌE           | Output enable input |  |  |  |

| Vccq         | Output power supply |  |  |  |

| Vcc          | +5V power supply    |  |  |  |

| Vss/Vssq     | Ground              |  |  |  |

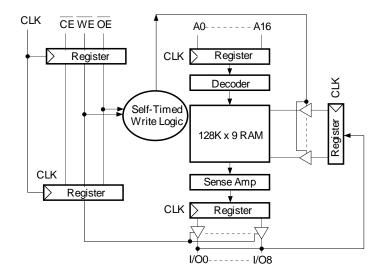

#### **Block Diagram**

#### Pin Description (2)

#### CLK (Clock, Positive Edge Triggered)

All timing is controlled by the rising or positive edge of CLK. All synchronous input and output signals are registered on the positive edge of CLK with set-up and hold times referenced to that edge. Since only one edge of CLK is referenced, the duty cycle of CLK is not critical.

#### A0 to A16 (Address)

The Address inputs are decoded on-chip to select one of 131,072 words. The state of the Address inputs is registered into the Address register on the positive edge of CLK. The Address inputs must be valid during every positive edge with all set-up and hold times referenced to that edge.

#### I/O0 to I/O8 (Data Input/Output)

I/O terminals are three-state and data input/output common. The state is defined by the Control block (refer to the truth table on page 4).

The data inputs for write operation must be valid during every positive edge of CLK with all set-up and hold times referenced to that edge. The data outputs are triggered by the positive edge of CLK and the contents of the Output-Registers are presented.

#### WE (Synchronous Write Enable, Active Low)

WE is used to indicate whether a read or write operation is to be performed. WE is "LOW" to perform a write operation. WE is registered on every positive edge of CLK with set-up and hold times referenced to that edge. The internal timing required to store data into the memory array is self-timed.

### CE (Synchronous Chip Enable, Active Low)

CE is used to select the Synchronous SRAM when low (or deselect when high). When selected, the Synchronous SRAM will perform a read or write operation (refer to the truth table on page 4). The state of CE is registered on every positive edge of CLK with set-up and hold times referenced to that edge.

#### OE (Synchronous Output Enable, Active Low)

OE is used to indicate that a read operation is to be performed. If the Synchronous SRAM is selected, the OE is low to perform a read operation (refer to the truth table on page 4). The state of OE is registered on every positive edge of CLK with set-up and hold times referenced to that edge.

## **Absolute Maximum Ratings**

| Item                         | Symbol  | Rating           | Unit     |

|------------------------------|---------|------------------|----------|

| Supply voltage               | Vcc     | -0.5 to +7.0     | V        |

| Input voltage                | Vin     | -0.5 to Vcc +0.5 | V        |

| Output voltage               | Vo      | -0.5 to Vcc +0.5 | V        |

| Allowable power dissipation  | PD      | 1                | W        |

| Operating temperature        | Topr    | 0 to 70          | °C       |

| Storage temperature          | Tstg    | -55 to +150      | °C       |

| Soldering temperature • time | Tsolder | 235 • 10         | °C • sec |

## **Truth Table**

| CLK | CE (tn) | WE (tn) | OE (tn) | Mode     | I/O to 8  | Vcc<br>Current |

|-----|---------|---------|---------|----------|-----------|----------------|

|     | Н       | X       | X       | Deselect | Hi-Z      | Isa            |

|     | L       | Н       | Η       | Read     | Hi-Z      | Icc            |

|     | L       | Н       | L       | Read     | Data out* | Icc            |

|     | L       | L       | X       | Write    | Data in   | Icc            |

## **DC Recommended Operating Conditions**

| 1 | (Ta | = | $+25^{\circ}$ | $^{\circ}$ C | GN  | D            | = | O١           | / | ١ |

|---|-----|---|---------------|--------------|-----|--------------|---|--------------|---|---|

|   | ııа | _ | TZJ           | <b>U</b> .   | UIV | $\mathbf{L}$ | _ | $\mathbf{v}$ | , | , |

| Item                  | Symbol | Min.  | Тур. | Max.     | Unit |

|-----------------------|--------|-------|------|----------|------|

| Supply voltage        | Vcc    | 4.75  | 5.0  | 5.25     | V    |

| Output supply voltage | Vccq   | 3.15  | _    | 5.25     | V    |

| Input high voltage    | ViH    | 2.2   | _    | Vcc +0.3 | V    |

| Input low voltage     | VIL    | -0.3* | _    | 0.8      | V    |

<sup>\*</sup>VIL = -3.0V min. for pulse width less than 20ns.

X: "H" or "L"  $$^*\mbox{Data}$  come out on the next positive edge of CLK.

#### **Electrical Characteristics**

## **DC and Operating Characteristics**

$(Vcc = 5V \pm 5\%, GND = 0V, Ta = 0 to +70°C)$

| Item                                                | Symbol | Test conditions                      | Min. | Max. | Unit |

|-----------------------------------------------------|--------|--------------------------------------|------|------|------|

| Input leakage current                               | ILI    | Vin = Gnd to Vcc                     | -1   | 1    |      |

| Output leakage current                              | ILO    | Vo = GND to Vcc<br>OE = ViH          | -1   | 1    | μA   |

| Average operating current                           | Icc    | Duty = 100%<br>Iout = 0mA            | _    | 150  | mA   |

| Standby current ISB CE ≥ VIH<br>Cycle = Min. Duty = |        | CE ≥ VIH<br>Cycle = Min. Duty = 100% | _    | 130  | IIIA |

| Output high voltage                                 | Vон    | Iон = −2.0mA                         | 2.4  | _    | V    |

| Output low voltage                                  | Vol    | IoL = 4.0mA                          | 1    | 0.4  | V    |

## I/O Capacitance

$(Ta = +25^{\circ}C, f = 1MHz)$

| Item              | Symbol | Test Conditions | Min. | Max. | Unit |

|-------------------|--------|-----------------|------|------|------|

| Input capacitance | CIN    | VIN = 0V        |      | 5    | рF   |

| I/O capacitance   | Cı/o   | V1/0 = 0V       | _    | 7    | рF   |

Note) These parameters are sampled and are not 100% tested.

#### **AC Characteristics**

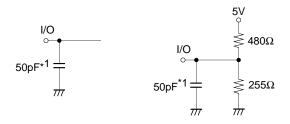

• AC Test Conditions (Vcc = 5V  $\pm$ 5%, Ta = 0 to  $\pm$ 70°C)

| Item                         | Conditions |

|------------------------------|------------|

| Input pulse high level       | VIH = 3.0V |

| Input pulse low level        | VIL = 0V   |

| Input rise time              | tr = 3ns   |

| Input fall time              | tf = 3ns   |

| Input/output reference level | 1.5V       |

| Output load conditions       | Fig. 1     |

Output Load (1) Out

Output Load (2) \*2

- \*1. Including scope and jig capacitance.

- \*2. For tckhqz, tckhqx.

Fig. 1

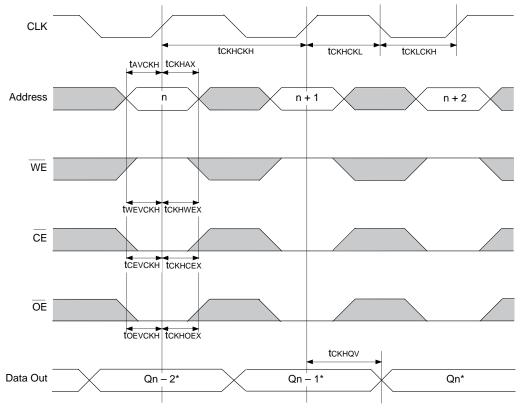

# • Read Cycle (WE = "H")

|                                    |         | -10  |      | -12  |      |      |

|------------------------------------|---------|------|------|------|------|------|

| Item                               | Symbol  | Min. | Max. | Min. | Max. | Unit |

| Read cycle time                    | tскнскн | 10   | _    | 12.5 | _    |      |

| Clock high pulse width             | tckhckl | 3.5  | _    | 4    | _    |      |

| Clock low pulse width              | tcklckh | 3.5  | _    | 4    | _    |      |

| Clock to data valid                | tckhqv  |      | 5.5  | _    | 6.5  |      |

| Address setup to clock high        | tavckh  | 2.5  | _    | 2.5  | _    |      |

| Address hold from clock high       | tCKHAX  | 0.5  | _    | 0.5  | _    | ns   |

| Chip enable setup to clock high    | tcevckh | 2.5  | _    | 2.5  | _    | 113  |

| Chip enable hold from clock high   | tckhcex | 0.5  | _    | 0.5  | _    |      |

| Output enable setup to clock high  | toevckh | 2.5  | _    | 2.5  |      |      |

| Output enable hold from clock high | tckhoex | 0.5  | _    | 0.5  | _    |      |

| Clock high to output low-Z         | tckhqx* | 1.5  | _    | 1.5  | _    |      |

| Clock high to output high-Z        | tckhqz* | _    | 4.5  |      | 5    |      |

<sup>\*</sup>Transition is measured ±200mV from steady voltage with specfified loading in Fig. 1-(2). This parameter is sampled and is not 100% tested.

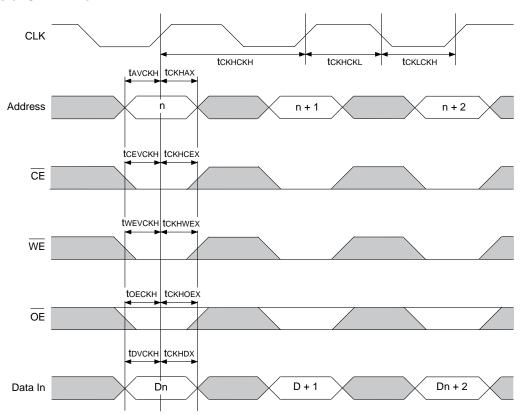

## • Write Cycle

|                                   |         | -1   | 0    | -1   | 2    |      |

|-----------------------------------|---------|------|------|------|------|------|

| Item                              | Symbol  | Min. | Max. | Min. | Max. | Unit |

| Write cycle time                  | tскнскн | 10   | _    | 12.5 | _    |      |

| Clock high pulse width            | tCKHCKL | 3.5  | _    | 4    | _    |      |

| Clock low pulse width             | tCKLCKH | 3.5  | _    | 4    | _    |      |

| Address setup to clock high       | tavckh  | 2.5  | _    | 2.5  | _    |      |

| Address hold from clock high      | tCKHAX  | 0.5  | _    | 0.5  | _    |      |

| Chip enable setup to clock high   | tCEVCKH | 2.5  | _    | 2.5  | _    | ns   |

| Chip enable hold from clock high  | tCKHCEX | 0.5  | _    | 0.5  | _    |      |

| Write enable setup to clock high  | tWEVCKH | 2.5  | _    | 2.5  | _    |      |

| Write enable hold from clock high | tCKHWEX | 0.5  | _    | 0.5  | _    |      |

| Input data setup to clock high    | tDVCKH  | 2.5  | _    | 2.5  | _    |      |

| Input data hold from clock high   | tCKHDX  | 0.5  | _    | 0.5  | _    |      |

## **Timing Waveform**

## • Read Cycle

\*Valid data from CLK high is the data from the previous cycle

## • Write Cycle: OE = VIH or VIL

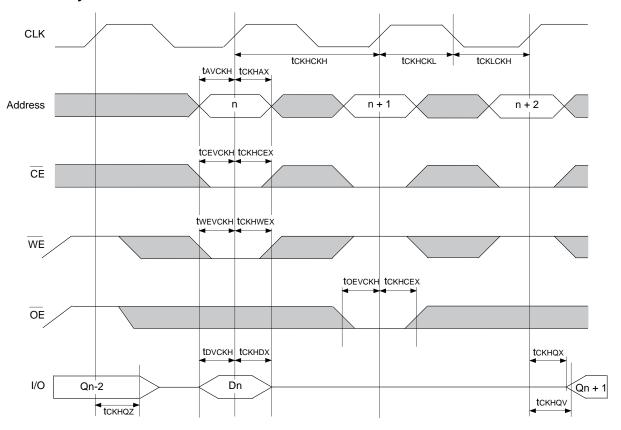

## • Read/Write Cycle

4.5

4.75

5.0

5.25

5.5

0

20

40

lcc

VccÅÅ5.0V

Vcc = 5.0V

Ta = +25°C

Vcc = 5.0V

80

60

100

75

80

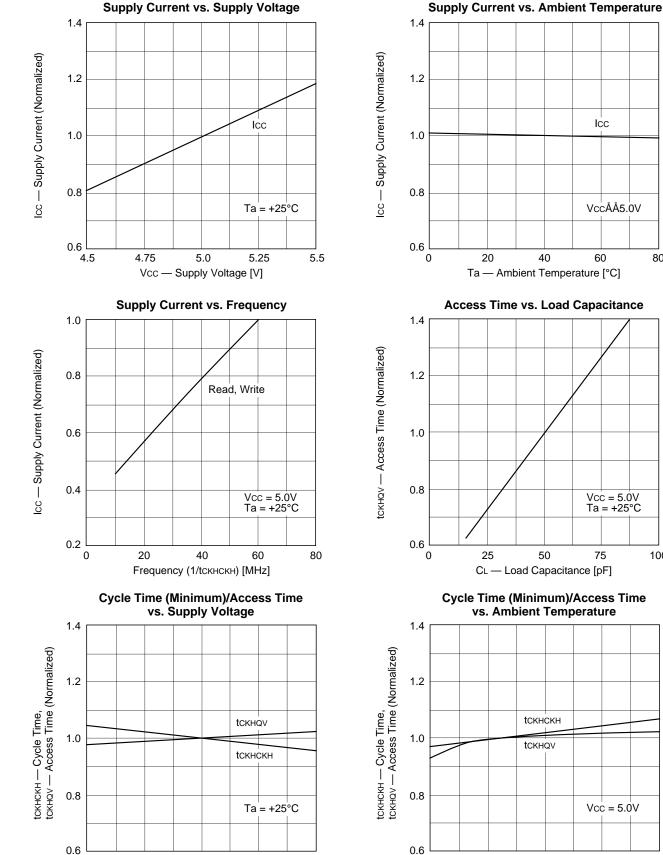

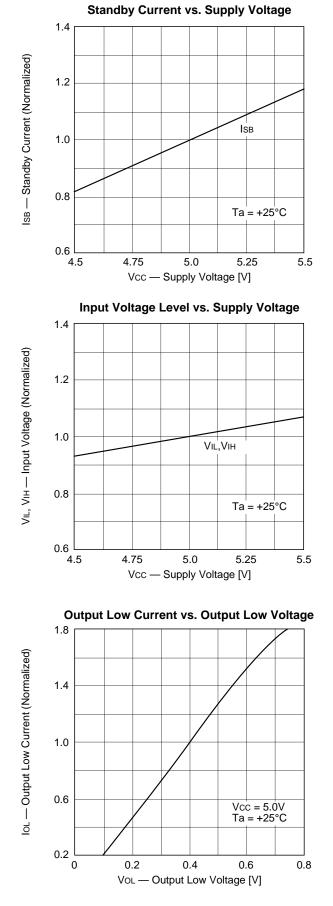

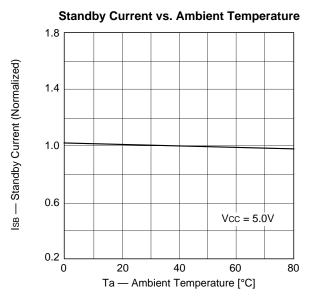

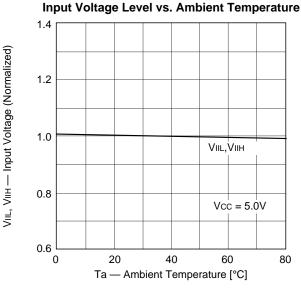

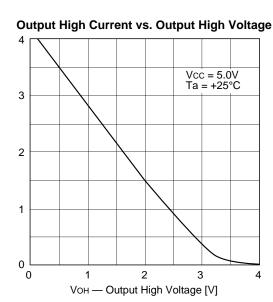

#### **Example of Representative Characteristics**

loн — Output High Current (Normalized)

SONY CXK77910ATM/AYM

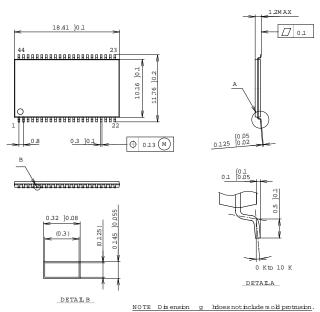

## **Package Outline**

Unit: mm

**CXK77910ATM**

44 PIN TSOP (II) (PLASTIC) 400 m il

PACKAGE STRUCTURE

|            |                       | PACKAGE MATERIAL | EPOXY RESIN    |

|------------|-----------------------|------------------|----------------|

| SONY CODE  | TSOP(II)-44P-L01      | LEAD TREATMENT   | SOLDER PLATING |

| EMJCODE    | TSOP (II)044-P-0400-A | LEAD MATERIAL    | 42 ALLO Y      |

| JEDEC CODE |                       | PACKAGE W EIGHT  | 0.5g           |

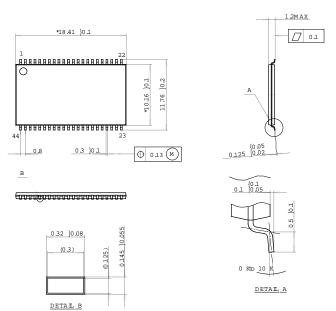

#### CXK77910AYM

44PIN TSOP(II) (PLASTIC) 400m il

NOTE Dimension g bridges not include mobil protrusion.

## PACKAGE STRUCTURE

|            |                      | PACK |

|------------|----------------------|------|

| SONY CODE  | TSOP(II)-44P-L01R    | LEAD |

| EMJCODE    | TSOP(II)044-P-0400-B | LEAD |

| JEDEC CODE |                      | PACK |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE W EIGHT  | 0.5g           |

|                  |                |