**THS7530**

SLOS405A - DECEMBER 2002- REVISED APRIL 2003

# HIGH-SPEED, FULLY DIFFERENTIAL, CONTINUOUSLY VARIABLE GAIN AMPLIFIER

## **FEATURES**

- Low Noise: V<sub>n</sub> = 1.1 nV/ Hz,

Noise Figure = 9 dB

- Low Distortion:

- $HD_2 = -65 \text{ dBc}$ ,  $HD_3 = -61 \text{ dBc}$  at 32 MHz

- $IMD_3 = -62 dBc, OIP_3 = 21 dBm at 70 MHz$

- 300 MHz Bandwidth

- Continuously Variable Gain Range: 11.6 dB to 46.5 dB

- Gain Slope: 38.8 dB/V

- Fully Differential Input and Output

- Output Common-Mode Voltage Control

- Output Voltage Limiting

## **APPLICATIONS**

- Time Gain Amplifiers in Ultra Sound, Sonar, and Radar

- Automatic Gain Control in Communication and Video

- System Gain Calibration in Communications

- Variable Gain in Instrumentation

### DESCRIPTION

The THS7530 is fabricated using Texas Instruments' state-of-the-art BiCom III SiGe complementary bipolar process. The THS7530 is a dc-coupled wide bandwidth amplifier with voltage-controlled gain. The amplifier has high impedance differential inputs and low impedance differential outputs with high bandwidth gain control, output common mode control, and output voltage clamping.

Signal channel performance is exceptional with 300-MHz bandwidth, and third harmonic distortion of -61 dBc at 32 MHz with 1  $V_{PP}$  output into 400  $\Omega$ .

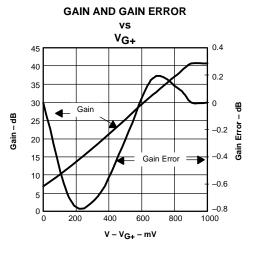

Gain control is linear in dB with 0 V to 0.9 V varying the gain from 11.6 dB to 46.5 dB with 38.8-dB/V gain slope.

Output voltage limiting is provided to limit the output voltage swing, and prevent saturating following stages.

The device is characterized for operation over the industrial temperature range: -40°C to 85°C.

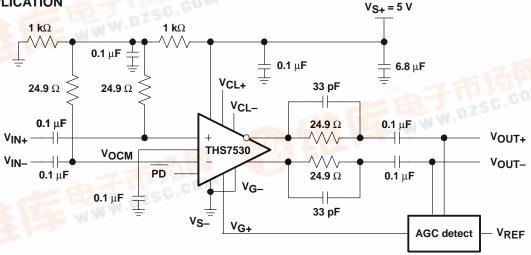

## AGC APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **THS7530**

#### SLOS405A DECEMBER 2002- REVISED APRIL 2003

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGING/ORDERING INFORMATION

| PRODUCT   | PACKAGE        | PACKAGE<br>DESIGNATOR | SYMBOL    | TEMPERATURE<br>RANGE, T <sub>A</sub> | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA |

|-----------|----------------|-----------------------|-----------|--------------------------------------|--------------------|--------------------|

| TI 107500 | T000D DDAD     | DIMD 44               | TI 107500 | 4000 1 - 0500                        | THS7530PWP         | Tube               |

| THS7530   | TSSOP PowerPAD | PWP-14                | THS7530   | –40°C to 85°C                        | THS7530PWPR        | Tape and reel      |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                     |                                                  | TH\$7530                     |

|-------------------------------------|--------------------------------------------------|------------------------------|

| Supply voltage, V <sub>S+</sub> - ' | 5.5 V                                            |                              |

| Input voltage, V <sub>I</sub>       |                                                  | ±VS                          |

| Output current, IO (2)              |                                                  | 65 mA                        |

| Differential input voltage          | e, V <sub>ID</sub>                               | ±4 V                         |

| Continuous power dissi              | ipation                                          | See Dissipation Rating Table |

| Maximum junction temp               | perature, T <sub>J</sub>                         | 150°C                        |

| Maximum junction temp               | perature for long term stability, T <sub>J</sub> | 125°C                        |

| Operating free-air temp             | erature range, T <sub>A</sub>                    | −40°C to 85°C                |

| Storage temperature ra              | nge, T <sub>Stg</sub>                            | −65°C to 150°C               |

| Lead temperature 1,6 n              | nm (1/16 inch) from case for 10 seconds          | 300°C                        |

|                                     | НВМ                                              | 3000 V                       |

| ESD                                 | CDM                                              | 1500 V                       |

|                                     | MM                                               | 200 V                        |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                                                        | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| Supply voltage, [V <sub>S</sub> _ to V <sub>S+</sub> ] |                                             | 4.5 | 5   | 5.5 | V    |

| Operating free–air temperature, T <sub>A</sub>         |                                             | -40 |     | 85  | °C   |

| Input common mode voltage                              | $[V_{S-} \text{ to } V_{S+}] = 5 \text{ V}$ |     | 2.5 |     | V    |

| Output common mode voltage                             | $[V_{S-} \text{ to } V_{S+}] = 5 \text{ V}$ |     | 2.5 |     | V    |

## PACKAGE THERMAL DATA

| PACKAGE | PCB                                                                      | <sup>⊝</sup> JA<br>( C/W) | ( C/W)<br>⊝JC | T <sub>A</sub> = 25°C<br>POWER RATING |

|---------|--------------------------------------------------------------------------|---------------------------|---------------|---------------------------------------|

| 14PWP   | See Layout Considerations in the application section of this data sheet. | 37.5                      | 2.07          | 3 W                                   |

<sup>(2)</sup> The THS7530 incorporates a PowerPAD™ on the underside of the chip. This acts as a heatsink and must be connected to a thermally dissipative plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature which could permanently damage the device. See TI technical brief SLMA002 and SLMA004 for more information about utilizing the PowerPAD thermally enhanced package.

## **SPECIFICATIONS: MAIN AMPLIFIER**

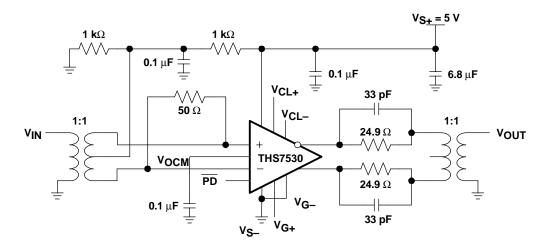

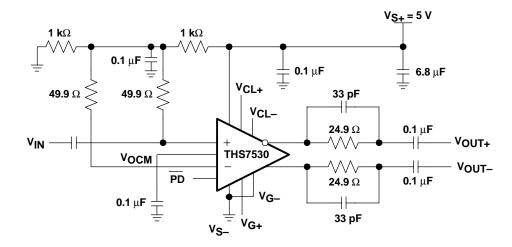

$V_{S+} = 5 \text{ V}, V_{S-} = 0 \text{ V}, V_{OCM} = 2.5 \text{ V}, V_{ICM} = 2.5 \text{ V}, V_{G-} = 0 \text{ V}, V_{G+} = 1 \text{ V}$  (maximum gain),  $T_A = 25^{\circ}\text{C}$ , ac performance measured using the ac test circuit shown in Figure 1 (unless otherwise noted). DC performance is measured using the dc test circuit shown in Figure 2 (unless otherwise noted)

|                                        |                                                                       | TYP        | <u> </u> | OVER TEMPERATURE |                        |             |

|----------------------------------------|-----------------------------------------------------------------------|------------|----------|------------------|------------------------|-------------|

| PARAMETER                              | TEST CONDITIONS                                                       | 25 C       | 25 C     | -40 C to<br>85 C | UNITS                  | MIN/<br>MAX |

| AC PERFORMANCE (See Figure 1)          |                                                                       |            | •        |                  |                        |             |

| Small-signal bandwidth                 | All gains, P <sub>IN</sub> = –45 dBm                                  | 300        |          |                  | MHz                    | Тур         |

| Slew rate(1)                           | 1 Vpp Step, 25% to 75%,<br>minimum gain                               | 1250       |          |                  | V/μs                   | Тур         |

| Settling time to 1% <sup>(1)</sup>     | 1 Vpp Step, minimum gain                                              | 11         |          |                  | ns                     | Тур         |

| Harmonic distortion                    | $V_{O(PP)} = 1 \text{ V, } R_{L(diff)} = 400 \Omega$                  |            |          |                  |                        |             |

| 2 <sup>nd</sup> Harmonic               | f = 32 MHz                                                            | -65        |          |                  | dBc                    | Тур         |

| 3 <sup>rd</sup> Harmonic               | f = 32 MHz                                                            | -61        |          |                  | dBc                    | Тур         |

| Third-order intermodulation distortion | $P_O = -10$ dBm each tone,<br>$f_C = 70$ MHz,<br>200 kHz tone spacing | -62        |          |                  | dBc                    | Тур         |

| Third-order output intercept point     | f <sub>C</sub> =70 MHz,<br>200 kHz tone spacing                       | 21         |          |                  | dBm                    | Тур         |

| Noise figure (with input termination)  | Source impedance: 50 $\Omega$                                         | 9          |          |                  | dB                     | Тур         |

| Total input voltage noise              | f > 100 kHz                                                           | 1.1        |          |                  | nV/√Hz                 | Тур         |

| OC PERFORMANCE—INPUTS (See Figure 2)   |                                                                       |            |          |                  | •                      |             |

| Input bias current                     |                                                                       | 20         | 39       | 40               | μΑ                     | Max         |

| Input bias current offset              |                                                                       | <150       |          |                  | pА                     | Тур         |

| Minimum input voltage                  | Minimum gain                                                          | 1.5        | 1.6      | 1.7              | V                      | Max         |

| Maximum input voltage                  | Minimum gain                                                          | 3.5        | 3.35     | 3.2              | V                      | Min         |

| Common-mode rejection ratio            |                                                                       | 114        | 56       | 44               | dB                     | Min         |

| Differential input impedance           |                                                                       | 8.5    3.0 |          |                  | $k\Omega \parallel pF$ | Тур         |

| OC PERFORMANCE—OUTPUTS (See Figure     | 2)                                                                    |            |          |                  |                        |             |

| Output offset voltage                  | All gains                                                             | ±100       | ±340     | ±480             | mV                     | Max         |

| Maximum output voltage high            |                                                                       | 3.5        | 3.275    | 3.25             | V                      | Min         |

| Minimum output voltage low             |                                                                       | 1.5        | 1.7      | 1.8              | V                      | Max         |

| Output current                         |                                                                       | ±37        | ±16      | ±16              | mA                     | Min         |

| Output impedance                       |                                                                       | 15         |          |                  | Ω                      | Тур         |

| OUTPUT COMMON-MODE VOLTAGE CONTR       | OL (See Figure 2)                                                     |            | •        |                  |                        |             |

| Small-signal bandwidth                 |                                                                       | 32         |          |                  | MHz                    | Тур         |

| Gain                                   |                                                                       | 1.00       |          |                  | V/V                    | Тур         |

| Common-mode offset voltage             |                                                                       | 4.5        | 12       | 13.8             | mV                     | Max         |

| Minimum input voltage                  |                                                                       | 1.75       |          |                  | V                      | Тур         |

| Maximum input voltage                  |                                                                       | 3.25       |          |                  | V                      | Тур         |

| Input impedance                        |                                                                       | 25    1    |          |                  | $k\Omega \parallel pF$ | Тур         |

| Default voltage, with no connect       |                                                                       | 2.5        |          |                  | V                      | Тур         |

| Input bias current                     |                                                                       | <1         |          |                  | μА                     | Тур         |

<sup>(1)</sup> Slew rate and settling time measured at amplifier output.

## **SPECIFICATIONS: MAIN AMPLIFIER (CONTINUED)**

$V_{S+} = 5 \text{ V}, V_{S-} = 0 \text{ V}, V_{OCM} = 2.5 \text{ V}, V_{ICM} = 2.5 \text{ V}, V_{G-} = 0 \text{ V}, V_{G+} = 1 \text{ V}$  (maximum gain),  $T_A = 25^{\circ}C$ , ac performance measured using the ac test circuit shown in Figure 1 (unless otherwise noted). DC performance is measured using the dc test circuit shown in Figure 2 (unless otherwise noted)

|                                                                             |                                   | TYP                                  |      | OVER TEMPERATURE |                        |             |

|-----------------------------------------------------------------------------|-----------------------------------|--------------------------------------|------|------------------|------------------------|-------------|

| PARAMETER                                                                   | TEST CONDITIONS                   | 25 C                                 | 25 C | -40 C to<br>85 C | UNITS                  | MIN/<br>MAX |

| GAIN CONTROL (See Figure 2)                                                 |                                   |                                      |      | •                |                        |             |

| Gain control differential voltage range                                     | V <sub>G+</sub>                   | 0 to 1                               |      |                  | V                      | Тур         |

| Minus gain control voltage                                                  | V <sub>G</sub> V <sub>S</sub> -   | -0.6 to 0.8                          |      |                  | V                      | Тур         |

| Minimum gain                                                                | V <sub>G+</sub> = 0 V             | 11.6                                 |      |                  | dB                     | Тур         |

| Maximum gain                                                                | V <sub>G+</sub> = 0.9 V           | 46.5                                 |      |                  | dB                     | Тур         |

| Gain slope                                                                  | V <sub>G+</sub> = 0 V to 0.9 V    | 38.8                                 |      |                  | dB/V                   | Тур         |

| Gain slope variation                                                        | V <sub>G+</sub> = 0 V to 0.9 V    | ±1.5                                 |      |                  | dB/V                   | Тур         |

| 0.:                                                                         | V <sub>G+</sub> = 0 V to 0.15 V   | ±4                                   |      |                  | dB                     | Тур         |

| Gain error                                                                  | V <sub>G+</sub> = 0.15 V to 0.9 V | ±2.25                                |      |                  | dB                     | Тур         |

| Gain control input bias current                                             |                                   | <1                                   |      |                  | μΑ                     | Тур         |

| Gain control input resistance                                               |                                   | 40                                   |      |                  | kΩ                     | Тур         |

| Gain control bandwith                                                       | Small signal –3 dB                | 15                                   |      |                  | MHz                    | Тур         |

| VOLTAGE CLAMPING (See Figure 2)                                             |                                   |                                      |      | •                |                        |             |

| Output voltages ( $V_{OUT\pm}$ ) relative to clamp voltages ( $V_{CL\pm}$ ) | In voltage limiting mode          | ±25                                  | ±38  | ±60              | mV                     | Max         |

| V <sub>CL±</sub> input resistance                                           |                                   | 3.3                                  |      |                  | kΩ                     | Тур         |

| V <sub>CL±</sub> voltage limits                                             |                                   | V <sub>S</sub> - to V <sub>S</sub> + |      |                  | V                      | Тур         |

| POWER SUPPLY (See Figure 2)                                                 |                                   |                                      |      | •                |                        |             |

| Specified operating voltage                                                 |                                   | 5                                    | 5.5  | 5.5              | V                      | Max         |

| Maximum quiescent current                                                   |                                   | 40                                   | 48   | 49               | mA                     | Max         |

| Power supply rejection (±PSRR)                                              |                                   | 77                                   | 70   | 45               | dB                     | Min         |

| POWERDOWN (See Figure 2)                                                    | -                                 | •                                    |      | •                |                        |             |

| Enable voltage threshold                                                    | TTL low = normal operation        | 1.4                                  |      | 1.0              | V                      | Min         |

| Disable voltage threshold                                                   | TTL high = shut down              | 1.4                                  |      | 1.65             | V                      | Max         |

| Power-down quiescent current                                                |                                   | 0.35                                 | 0.4  | 0.45             | mA                     | Max         |

| Input current high                                                          |                                   | 9                                    | 16   | 19               | μΑ                     | Max         |

| Input current low                                                           |                                   | 109                                  | 116  | 119              | μΑ                     | Max         |

| Input impedance                                                             |                                   | 50    1                              |      |                  | $k\Omega \parallel pF$ | Тур         |

| Turnon time delay                                                           | Measured to 50% quiescent         | 820                                  |      |                  | ns                     | Тур         |

| Turnoff time delay                                                          | current                           | 500                                  |      |                  | ns                     | Тур         |

| Forward isolation in power down                                             |                                   | 80                                   |      |                  | dB                     | Тур         |

| Input resistance in power down                                              |                                   | > 1                                  |      |                  | MΩ                     | Тур         |

| Output resistance in power down                                             |                                   | 16                                   |      |                  | kΩ                     | Тур         |

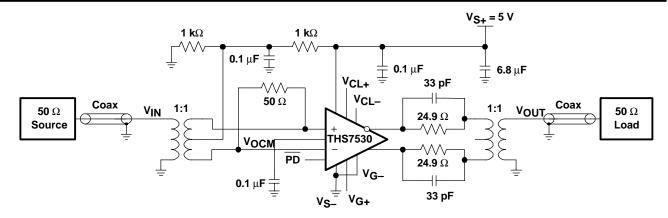

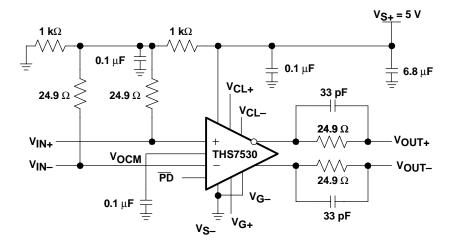

Figure 1. AC Test Circuit

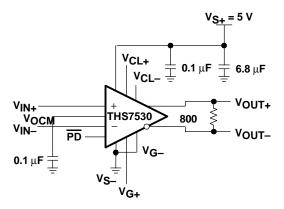

Figure 2. DC Test Circuit

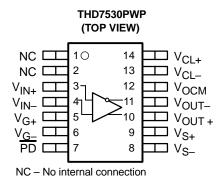

## **PIN ASSIGNMENTS**

## **Terminal Functions**

| TER | MINAL             | DECODINE                                                                                                                        |  |  |  |  |  |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO. | NAME              | DESCRIPTION                                                                                                                     |  |  |  |  |  |

| 1   | NC                | No internal connection                                                                                                          |  |  |  |  |  |

| 2   | NC                | No internal connection                                                                                                          |  |  |  |  |  |

| 3   | V <sub>IN+</sub>  | Noninverting amplifier input                                                                                                    |  |  |  |  |  |

| 4   | V <sub>IN</sub> _ | Inverting amplifier input                                                                                                       |  |  |  |  |  |

| 5   | V <sub>G+</sub>   | Gain setting positive input                                                                                                     |  |  |  |  |  |

| 6   | V <sub>G</sub> _  | Gain setting negative input                                                                                                     |  |  |  |  |  |

| 7   | PD                | Powerdown, $\overline{PD}$ = logic low puts part into low power mode, $\overline{PD}$ = logic high or open for normal operation |  |  |  |  |  |

| 8   | V <sub>S</sub> -  | Negative amplifier power supply input                                                                                           |  |  |  |  |  |

| 9   | V <sub>S+</sub>   | Positive amplifier power supply input                                                                                           |  |  |  |  |  |

| 10  | Vour+             | Noninverted amplifier output                                                                                                    |  |  |  |  |  |

| 11  | Vout-             | Inverted amplifier output                                                                                                       |  |  |  |  |  |

| 12  | VOCM              | Output common-mode voltage input                                                                                                |  |  |  |  |  |

| 13  | V <sub>CL</sub> – | Output negative clamp voltage input                                                                                             |  |  |  |  |  |

| 14  | V <sub>CL+</sub>  | Output positive clamp voltage input                                                                                             |  |  |  |  |  |

## **TYPICAL CHARACTERISTICS**

## **TABLE OF GRAPHS**

Measured using the ac test circuit shown in Figure 1 (unless otherwise noted).

|                                                 |                                | FIGURE |

|-------------------------------------------------|--------------------------------|--------|

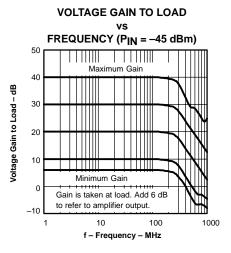

| Voltage Gain to Load                            | vs Frequency (Input at 45 dBm) | 3      |

| Gain and Gain Error                             | vs V <sub>G+</sub>             | 4      |

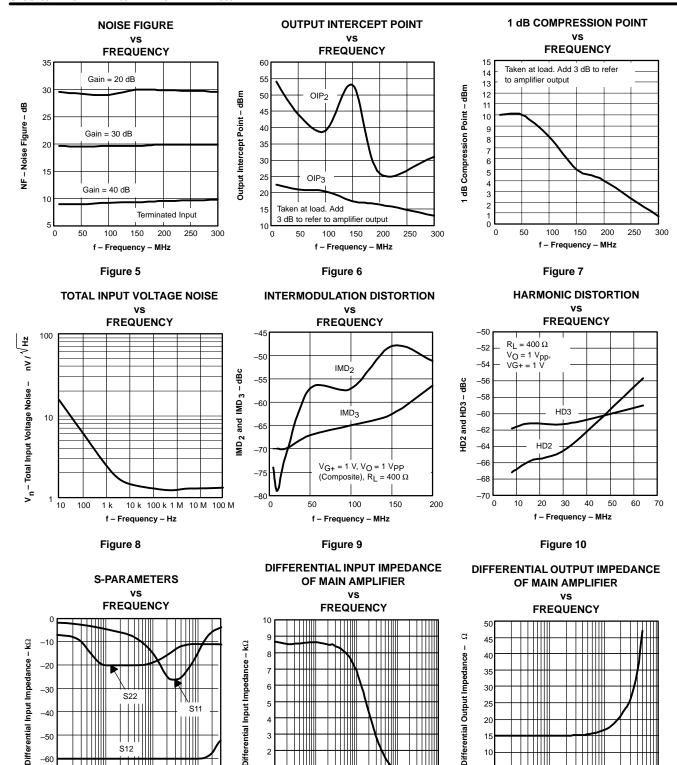

| Noise Figure                                    | vs Frequency                   | 5      |

| Output Intercept Point                          | vs Frequency                   | 6      |

| 1-dB Compression Point                          | vs Frequency                   | 7      |

| Total Input Voltage Noise                       | vs Frequency                   | 8      |

| Intermodulation Distortion                      | vs Frequency                   | 9      |

| Harmonic Distortion                             | vs Frequency                   | 10     |

| S-Parameters                                    | vs Frequency                   | 11     |

| Differential Input Impedance of Main Amplifier  | vs Frequency                   | 12     |

| Differential Output Impedance of Main Amplifier | vs Frequency                   | 13     |

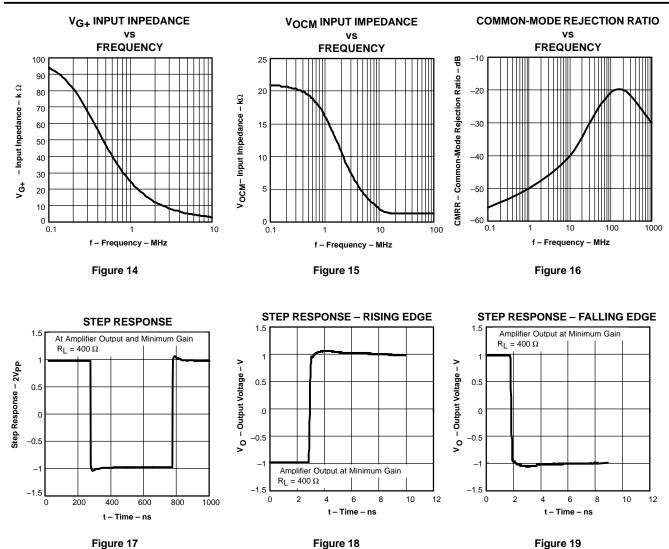

| V <sub>G+</sub> Input Impedance                 | vs Frequency                   | 14     |

| V <sub>OCM</sub> Input Impedance                | vs Frequency                   | 15     |

| Common-Mode Rejection Ratio                     | vs Frequency                   | 16     |

| Step Response – 2 V <sub>PP</sub>               | vs Time                        | 17     |

| Step Response – Rising Edge                     | vs Time                        | 18     |

| Step Response – Falling Edge                    | vs Time                        | 19     |

Figure 3

Figure 4

1000

f – Frequency – MHz

Figure 13

10

f - Frequency - MHz

Figure 12

-60 -70 0.1

100 300

10

f - Frequency - MHz

Figure 11

#### APPLICATION INFORMATION

The THS7530 is designed for nominal 5-V power supply from V<sub>S+</sub> to V<sub>S-</sub>.

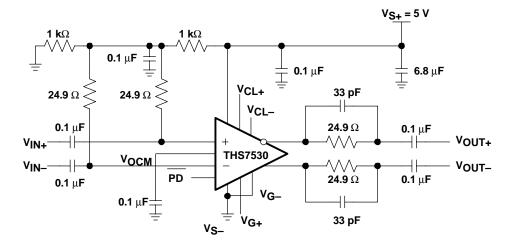

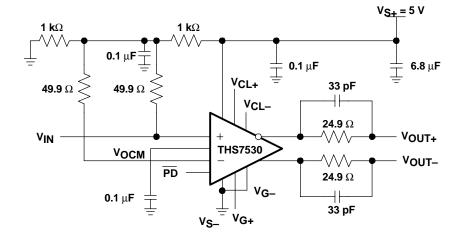

The amplifier has fully differential inputs,  $V_{IN+}$  and  $V_{IN-}$ , and fully differential outputs,  $V_{OUT+}$  and  $V_{OUT-}$  The inputs are high impedance and outputs are low impedance. External resistors are recommended for impedance matching and termination purposes.

The inputs and outputs can be dc-coupled, but for best performance, the input and output common-mode voltage should be maintained at the midpoint between the two supply pins. The output common-mode voltage is controlled by the voltage applied to  $V_{OCM}$ . Left unterminated,  $V_{OCM}$  is set to midsupply by internal resistors. A 0.1- $\mu$ F bypass capacitor should be placed between  $V_{OCM}$  and ground to reduce common-mode noise. The input common-mode voltage defaults to midrail when left unconnected. For voltages other than midrail,  $V_{OCM}$  must be biased by external means.  $V_{IN+}$  and  $V_{IN-}$  both require a nominal 30- $\mu$ A bias current for proper operation. Therefore, insure equal input impedance at each input to avoid generating an offset voltage that varies with gain.

Voltage applied from  $V_{G-}$  to  $V_{G+}$  controls the gain of the part with 38.8-dB/V gain slope. The input can be differential or single ended.  $V_{G-}$  must be maintained within -0.6 V and +0.8 V of  $V_{S-}$  for proper operation. The negative gain input should typically be tied directly to the negative power supply.

$V_{CL+}$  and  $V_{CL-}$  are inputs that limit the output voltage swing of the amplifier. The voltages applied set an absolute limit on the voltages at the output. Input voltages at  $V_{CL+}$  and  $V_{CL-}$  clamp the output insuring that neither output exceeds those values.

The power-down input is a TTL compatible input, referenced to the negative supply voltage. A logic low puts the THS7530 in power savings mode. In power-down mode the part consumes less than 1-mA current, the output goes high impedance, and a high amount of isolation is maintained between the input and output.

Power supply bypass capacitors are required for proper operation. A  $6.8-\mu F$  tantalum bulk capacitor is recommended if the amplifier is located far from the power supply and may be shared among other devices. A ceramic  $0.1-\mu F$  capacitor is recommended within 0.1" of the device power pin. The ceramic capacitors should be located on the same layer as the amplifier to eliminate the use of vias between the capacitors and the power pin.

The following circuits show some basic circuit configurations.

Figure 20. EVM Schematic: Designed for Use With Typical 50- RF Test Equipment

Figure 21. AC-Coupled Single-Ended Input With AC-Coupled Differential Output

Figure 22. AC-Coupled Differential Input With AC-Coupled Differential Output

Figure 23. DC-Coupled Single-Ended Input With DC-Coupled Differential Output

Figure 24. DC-Coupled Differential Input With DC-Coupled Differential Output

#### LAYOUT CONSIDERATIONS

The THS7530 comes in a thermally enhance PowerPAD™ package. Figure 25 shows the recommended number of vias and thermal land size recommended for best performance. Thermal vias connect the thermal land to internal or external copper planes and should have a drill diameter sufficiently small so that the via hole is effectively plugged when the barrel of the via is plated with copper. This plug is needed to prevent wicking the solder away from the interface between the package body and the thermal land on the surface of the board during solder reflow. The experiments conducted jointly with Solectron Texas indicate that a via drill diameter of 0.33mm (13 mils) or smaller works well when 1 ounce copper is plated at the surface of the board and simultaneously plating the barrel of the via. If the thermal vias are not plugged when the copper plating is performed, then a solder mask material should be used to cap the vias with a dimension equal to the via diameter + 0,1 mm minimum. This prevents the solder from being wicked through the thermal via and potentially creating a solder void in the region between the package bottom and the thermal land on the surface of the PCB.

Figure 25. Recommended Thermal Land Size and Thermal Via Patterns (dimensions in mm)

See TI's Technical Brief titled PowerPAD™ Thermally Enhanced Package (SLMA002) for a detailed discussion of the PowerPAD™ package, its dimensions, and recommended use.

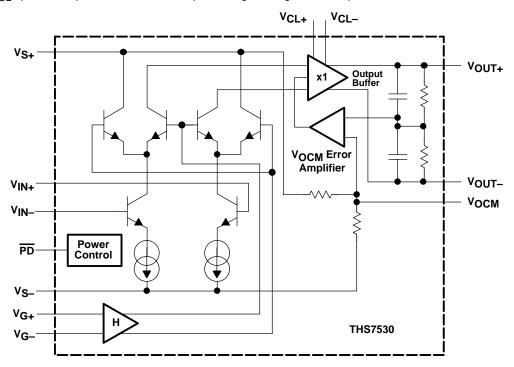

#### THEORY OF OPERATION

Figure 26 shows a simplified schematic of the THS7530.

The input architecture is a modified Gilbert Cell. The output from the Gilbert Cell is converted to a voltage and buffered to the output as a fully-differential signal. A summing node between the outputs is used to compare the output common-mode voltage to the  $V_{OCM}$  input. The  $V_{OCM}$  error amplifier then servos the output common-mode voltage to maintain it equal to the  $V_{OCM}$  input. Left unterminated,  $V_{OCM}$  is set to midsupply by internal resistors.

The gain control input is conditioned to give linear in dB gain control (block H). The gain control input is a differential signal from 0 V to 0.9 V which varies the gain from 11.6 dB to 46.5 dB.

V<sub>Cl</sub> + and V<sub>Cl</sub> - provide inputs that limit the output voltage swing of the amplifier.

Figure 26. THS7530 Simplified Schematic

#### SPICE MODEL

- \* [Disclaimer] (C) Copyright Texas Instruments Incorporated 1999-2002 All rights reserved

- \* Texas Instruments Incorporated hereby grants the user of this SPICE Macro-model a

- \* non-exclusive, nontransferable license to use this SPICE Macro-model under the following

- \* terms. Before using this SPICE Macro-model, the user should read this license. If the

- \* user does not accept these terms, the SPICE Macro-model should be returned to Texas

- \* Instruments within 30 days. The user is granted this license only to use the SPICE

- \* Macro-model and is not granted rights to sell, load, rent, lease or license the SPICE

- \* Macro-model in whole or in part, or in modified form to anyone other than user. User may

- \* modify the SPICE Macro-model to suit its specific applications but rights to derivative

- \* works and such modifications shall belong to Texas Instruments. This SPICE Macro-model is

- \* provided on an "AS IS" basis and Texas Instruments makes absolutely no warranty with

- \* respect to the information contained herein. TEXAS INSTRUMENTS DISCLAIMS AND CUSTOMER

- \* WAIVES ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING WARRANTIES OF MERCHANTABILITY

- \* OR FITNESS FOR A PARTICULAR PURPOSE. The entire risk as to quality and performance is with

- \* the Customer. ACCORDINGLY, IN NO EVENT SHALL THE COMPANY BE LIABLE FOR ANY DAMAGES,

- \* WHETHER IN CONTRACT OR TORT, INCLUDING ANY LOST PROFITS OR OTHER INCIDENTAL, CONSEQUENTIAL,

- \* EXEMPLARY, OR PUNITIVE DAMAGES ARISING OUT OF THE USE OR APPLICATION OF THE SPICE

- \* Macro-model provided in this package. Further, Texas Instruments reserves the right to

- \* discontinue or make changes without notice to any product herein to improve reliability,

- \* function, or design. Texas Instruments does not convey any license under patent rights or

- \* any other intellectual property rights, including those of third parties.

- \* THS7530 SUBCIRCUIT

- \* HIGH SPEED FULLY DIFFERENTIAL VARIABLE AMPLIFIER

- \* WRITTEN 11/26/02

- $\mbox{\scriptsize *}$  VG- is tied to VS- and output clamping is not modeled

- \* CONNECTIONS: IN+

| 4 | k              |   | IN- |     |     |      |      |      |     |

|---|----------------|---|-----|-----|-----|------|------|------|-----|

| 4 | k              |   |     | VS+ |     |      |      |      |     |

| 4 | k              |   |     |     | VS- |      |      |      |     |

| 4 | k              |   |     |     |     | OUT- |      |      |     |

| 4 | <b>k</b>       |   |     |     |     |      | OUT+ |      |     |

| 4 | <b>k</b>       |   |     |     |     |      |      | VOCM |     |

| 4 | k              |   |     |     |     |      |      |      | VG+ |

| 4 | <b>k</b>       |   |     |     |     |      |      |      |     |

|   | SUBCKT THS7530 | 1 | 2   | 3   | 4   | 5    | 6    | 7    | 8   |

\*INPUT\*

Q1 122 1 101 NPN\_IN 16 Q2 123 2 102 NPN\_IN 16 R1 102 101 25 I1 101 4 DC 4.85e-3 I2 102 4 DC 4.85e-3

```

*QUAD*

Q3

132 120 122 NPN 16

Q4

121 119 122 NPN 16

Q5

132 119 123 NPN 16

Q6

121 120 123 NPN 16

R2

132 3 250

R3

121 3 250

*CURRENT AMP*

128 129 VF1 6

132 121 0V

VF1

*Z NODE*

R4

128 129 2k

I3

129 4 DC 0.75e-3

128 4 DC 0.75e-3

Ι4

V9

128 328 0.7

129 329 0.7

V10

*FREQUENCY SHAPING*

E3

131 0 329 0 1

131 140 30

R5

140 133 7.5n

L3

133 0 24p

C6

E4

130 0 328 0 1

130 141 30

R9

141 125 10n

L4

C7

125 0 27p

*OUTPUT BUFFER*

Q9

4 133 117 PNP 5.12

Q10

3 133 127 NPN 5.12

Q11

3 117 134 NPN 81.92

4 127 135 PNP

Q12

81.92

4 125 116 PNP

Q13

5.12

3 125 126 NPN

5.12

Q14

Q15

3 116 136 NPN

81.92

Q16

4 126 137 PNP

81.92

Rб

138 134

5

R7

135 138

5

R10

139 136 5

R11

137 139 5

I5

3 117 DC 0.4e-3

16

127 4 DC 0.4e-3

I7

3 116 DC 0.4e-3

126 4 DC 0.4e-3

```

#### SLOS405A DECEMBER 2002- REVISED APRIL 2003

```

*OUTPUT Z*

R8

113 138 2

R12

115 139 2

L1

113 5 4n

115 6 4n

L2

6 5 2p

C1

*VOCM

115 114 8k

Rcm1

Ccm1

115 114 0.1p

Rcm2

114 113 8k

Ccm2

114 113 0.1p

118 0 114 7 1e3

E1

Rtop

3 7 50k

4 7 50k

Rbot

Q7

128 118 3 PNP 16

129 118 3 PNP 16

Q8

*GAIN CONTROL*

235 8 0.454

V8

231 0 235 4 0.51

E5

232 0 POLY(1) 231 0 0.0 1 1 0.5 3.5

Еб

233 0 232 0 0.115

E7

E8

234 0 POLY(1) 233 0 0.0 0 1 0 0.333

120 119 234 0 0.42

Ε9

V7

3 120 1.6

Rsupply 3 4 310

.MODEL NPN_IN NPN

+ KF=1E-12

.MODEL NPN NPN

.MODEL PNP PNP

```

.ENDS

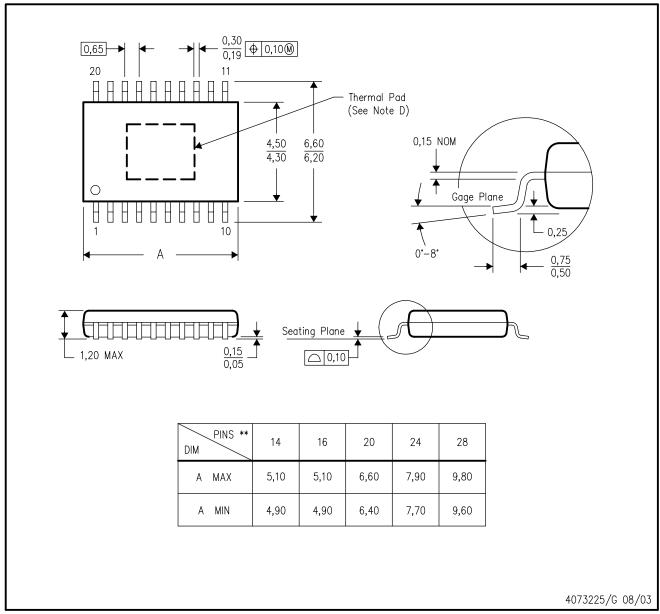

## PWP (R-PDSO-G\*\*)

## PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

20 PIN SHOWN

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265