## 8-PORT GIGABIT ETHERNET TRANSCEIVER

SLLS566A - MAY 2003 - REVISED JULY 2003

- Eight 1.0- to 1.3-Gigabits Per Second (Gbps) Synchronizable Transceivers

- Low Power Consumption <1.3 W at 1.25 Gbps

- IEEE 802.3z Gigabit Ethernet Compliant

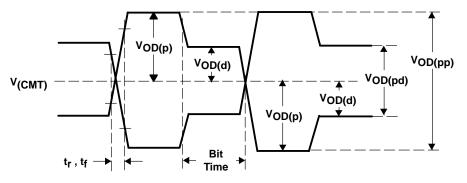

- Differential VML Transmit Outputs With No External Components Necessary. PECL Compatible Levels

- Programmable High-Speed Output Preemphasis Levels

- Selectable Parallel Interface Modes:

- Nibble-Wide Double Data Rate (DDR)

Clocking Interface

- Multiplexed Channel DDR Clock Interface

- Selectable Clock Tolerance Compensation

- Selectable On-Chip 8b/10b IEEE 802.3z

Compliant Encoder and Decoder

- JEDEC-Compliant 1.8-V LVCMOS (Extendable to 2.5 V)

- 3.6-V Tolerant Inputs on Parallel I/O

- Internal Series Termination on LVCMOS Outputs to Drive 50-Ω Lines

- Comprehensive Suite of Built-In Testability Features (PRBS Generation and Verification, Serial Loopback, and Far-End Loopback)

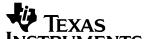

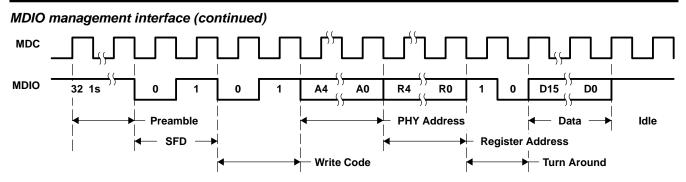

- IEEE 802.3 Clause 22 Management Data Interface (MDIO) Support

- IEEE 1149.1 JTAG Support

- Hot-Plug Protection on Serial I/O

- No External Filter Components Required for PLLs

- Small Footprint 19×19-mm, 289-Terminal, 1,0-mm Ball-Pitch BGA

- Advanced Low-Power 0.18-μm CMOS Technology

- Commercial Temperature Rating (0°C to 70°C)

## description

The TLK2208A is the third generation of Gigabit Ethernet transceivers from Texas Instruments combining high port density and ultralow power in a small form-factor footprint. The TLK2208A provides for high-speed full-duplex point-to-point data transmissions based on the IEEE 802.3z 1000-Mbps Ethernet specification. The TLK2208A supports data rates from 1.0 Gbps through 1.3 Gbps.

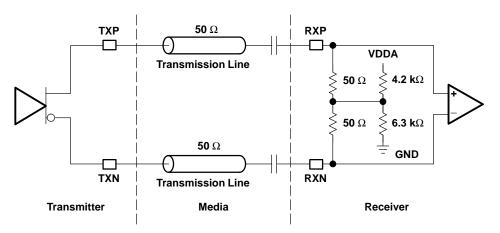

The primary application of this device is to provide building blocks for developing point-to-point baseband data transmission over controlled impedance media of  $50 \Omega$ . The transmission media can be printed circuit board traces, copper cables or fiber-optical interface modules. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

The TLK2208A performs the data encoding, decoding, serialization, deserialization, clock extraction, and clock tolerance compensation functions for a physical layer interface device. Each channel operates at up to 1.3 Gbps providing up to 8.32 Gbps of aggregate data bandwidth over copper or optical-media interfaces.

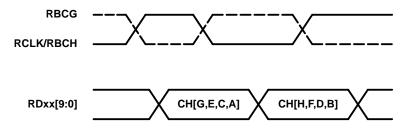

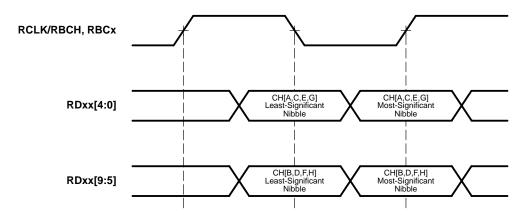

The TLK2208A supports two selectable reduced-pin-count double-data-rate (DDR) timing interfaces, nibble mode and multiplexed channel mode, to a protocol device.

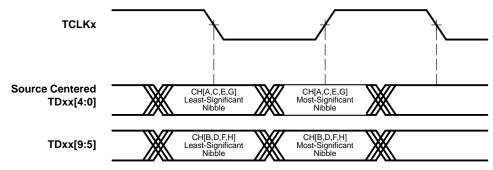

In the nibble interface mode, the parallel interface accepts nibble-wide unencoded or 8b/10b encoded data aligned to both the rising and falling edges of the transmit clock.

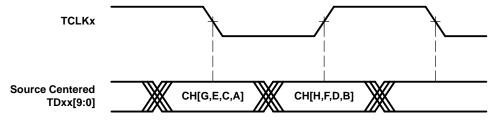

In the multiplexed channel mode, the parallel interface accepts 8-bit-wide unencoded or 10-bit-wide 8b/10b encoded data with channels A, C, E, and G aligned to the falling edge of the source synchronous transmit clock and channels B, D, F, and H aligned to the rising edge of the transmit clock. The receive path interface is done in the same manner.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### description (continued)

SLLS566A - MAY 2003 - REVISED JULY 2003

The TLK2208A aligns the recovered data clock frequency to the reference clock on each channel by means of a clock tolerance compensation circuit and internal FIFO that inserts or drops 20-bit IDLE codes as needed in the interpacket gap (IPG). In synchronous mode, the received data for all channels is aligned to a single receive data clock that is a buffered version of the reference clock.

The TLK2208A supports a selectable IEEE 802.3z compliant 8b/10b encoder/decoder in all its modes of operation.

The TLK2208A automatically locks onto incoming data without the need to pre-lock.

The TLK2208A provides a comprehensive series of built-in tests for self-test purposes including loopback and PRBS generation and verification. An IEEE 1149.1 JTAG port is also supported to aid in board-manufacturing testing.

The TLK2208A is housed in a small form-factor 19×19-mm, 289-terminal BGA with 1,0-mm ball pitch. The ball out and footprint are compatible with those of the PMC-Sierra PM8352 8-channel transceiver.

The TLK2208A is characterized to support the commercial temperature range of 0°C to 70°C.

The TLK2208A consumes 1.3 W when operating at nominal conditions.

The TLK2208A is designed to be hot-plug capable. A power-on reset puts the serial side output signal terminals TX+/TX— in the high-impedance state during power up.

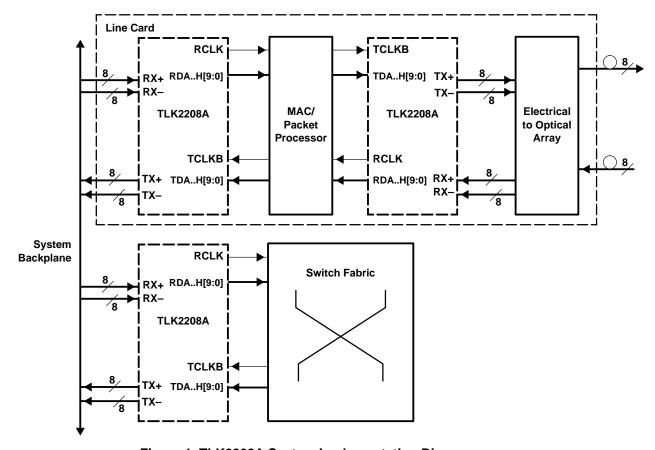

Figure 1. TLK2208A System Implementation Diagram

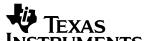

Figure 2. TLK2208A Block Diagram

Pin Out (Top View)

|    | Α     | В     | С          | D            | E     | F     | G     | н     | J             | к     | L     | М     | N     | Р          | R            | т     | U     |    |

|----|-------|-------|------------|--------------|-------|-------|-------|-------|---------------|-------|-------|-------|-------|------------|--------------|-------|-------|----|

| 17 | GNDA  | GNDA  | GNDA       | GNDA         | GNDA  | GNDA  | GNDA  | GNDA  | GNDA          | GNDA  | GNDA  | GNDA  | GNDA  | GNDA       | GNDA         | GNDA  | GNDA  | 17 |

| 16 | TXH+  | TXG+  | TXF+       | TXE+         | TXD+  | TXC+  | TXB+  | TXA+  | GNDA          | RXH+  | RXG+  | RXF+  | RXE+  | RXD+       | RXC+         | RXB+  | RXA+  | 16 |

| 15 | TXH-  | TXG-  | TXF-       | TXE-         | TXD-  | TXC-  | TXB-  | TXA-  | NC            | RXH-  | RXG-  | RXF-  | RXE-  | RXD-       | RXC-         | RXB-  | RXA-  | 15 |

| 14 | GNDA  | GNDA  | GNDA       | GNDA         | GNDA  | GNDA  | GNDA  | GNDA  | NC            | GNDA  | GNDA  | GNDA  | GNDA  | GNDA       | GNDA         | GNDA  | GNDA  | 14 |

| 13 | TDHG8 | TDHG9 | PRBS<br>EN | EN<br>ABLE   | VDDA  | VDDA  | VDDA  | VDDA  | VDDA          | VDDA  | VDDA  | VDDA  | VDDA  | DVAD2      | DVAD1        | RDHG9 | RDHG8 | 13 |

| 12 | TDHG6 | TDHG7 | REF<br>CLK | DVAD4        | VDD   | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDD   | MODE1      | DVAD0        | RDHG7 | RDHG6 | 12 |

| 11 | TDHG4 | TDHG5 | TMS        | DVAD3        | VDD   | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDD   | MODE0      | PLL_<br>LOCK | RDHG5 | RDHG4 | 11 |

| 10 | TDHG2 | TDHG3 | тск        | NC           | VDD   | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDD   | RSVD       | RCLK<br>RBCH | RDHG3 | RDHG2 | 10 |

| 9  | TDHG0 | TDHG1 | TDI        | TCLK_<br>SEL | VDDQ  | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDDQ  | BUSY<br>EN | RBCG         | RDHG1 | RDHG0 | 9  |

| 8  | TDFE8 | TDFE9 | GE_<br>MOD | TRST         | VDDQ  | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDDQ  | RSVD       | RBCF         | RDFE9 | RDFE8 | 8  |

| 7  | TDFE6 | TDFE7 | TDO        | LPBK         | VDDQ  | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDDQ  | RSVD       | RBCE         | RDFE7 | RDFE6 | 7  |

| 6  | TDFE4 | TDFE5 | TCLKH      | NC           | VDDQ  | T-GND | T-GND | T-GND | T-GND         | T-GND | T-GND | T-GND | VDDQ  | NC         | RBCD         | RDFE5 | RDFE4 | 6  |

| 5  | TDFE2 | TDFE3 | TCLKF      | NC           | VDDQ  | VDDQ  | VDDQ  | VDDQ  | VDDQ          | VDDQ  | VDDQ  | VDDQ  | VDDQ  | NC         | RBCC         | RDFE3 | RDFE2 | 5  |

| 4  | TDFE0 | TDFE1 | TCLKD      | NC           | GND   | GND   | GND   | GND   | GND           | GND   | GND   | GND   | GND   | RBCA       | RBCB         | RDFE1 | RDFE0 | 4  |

| 3  | TDDC8 | TDDC9 | TDDC6      | TDDC7        | TCLKB | RSVD  | RESET | MDC   | CV_<br>DIS_EN | NC    | NC    | NC    | NC    | RDDC7      | RDDC6        | RDDC9 | RDDC8 | 3  |

| 2  | TDDC4 | TDDC5 | TDDC1      | TDBA1        | TDBA3 | TDBA5 | TDBA7 | TDBA9 | CODE          | RDBA1 | RDBA3 | RDBA5 | RDBA7 | RDBA9      | RDDC1        | RDDC5 | RDDC4 | 2  |

| 1  | TDDC3 | TDDC2 | TDDC0      | TDBA0        | TDBA2 | TDBA4 | TDBA6 | TDBA8 | MDIO          | RDBA0 | RDBA2 | RDBA4 | RDBA6 | RDBA8      | RDDC0        | RDDC2 | RDDC3 | 1  |

|    | Α     | В     | С          | D            | E     | F     | G     | н     | J             | к     | L     | М     | N     | Р          | R            | т     | U     |    |

NOTE: Unused inputs that do not hold an integrated pullup or pulldown circuit need to be terminated to either VDDQ or GND, respectively, to avoid excessive currents and lifetime degradation.

Figure 3. Terminal Diagram

## **Signal Terminal Description**

## Serial I/O Signals

| SIGNAL               | LOCATION           | TYPE                         | DESCRIPTION                                                                                                                                                                                                        |

|----------------------|--------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX[A:H]+<br>TX[A:H]– | H16:A16<br>H15:A15 | VML<br>output                | Differential output transmit. TX[A:H]+ and TX[A:H]– are differential serial outputs that interface to a copper or an optical I/F module.                                                                           |

|                      |                    |                              | TX[A:H]+ and TX[A:H]- are put in a high-impedance state when LPBK = high or when the LOOPBACK bit for a particular channel in the MDIO registers is set.                                                           |

| RX[A:H]+<br>RX[A:H]– | U16:K16<br>U15:K15 | PECL-<br>compatible<br>input | Differential input receive. RX[A:H]+ and RX[A:H]– together are the differential serial input interface from a copper or an optical I/F module. Differential resistive termination is built-in for these terminals. |

## **Transmit Data Bus and Clock Signals**

| SIGNAL                 | LOCATION                   | TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK                 | C12                        | LVCMOS<br>input             | Reference clock. REFCLK is an external input clock that provides the clock reference for synchronizing the receiver and transmitter interfaces.                                                                                                                                                                                                                |

|                        |                            |                             | REFCLK is supposed to run from 100 MHz up to 130 MHz for 1 Gbps up to 1.3 Gbps operation of the serial interface.                                                                                                                                                                                                                                              |

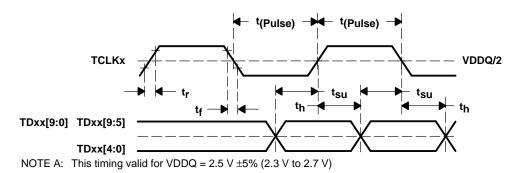

| TCLKB                  | E3                         | LVCMOS input with           | Transmit data clock. When in synchronized channel modes, the data on TDBA[9:0], TDFC[9:0], TDFE[9:0] and TDHG[9:0] is latched on both the rising and falling edges of TCLKB.                                                                                                                                                                                   |

|                        |                            | P/U                         | When in independent channel modes, TCLKB latches TDBA[9:0] data on both its rising and falling edges.                                                                                                                                                                                                                                                          |

| TCKD,<br>TCKF,<br>TCKH | C4,<br>C5,<br>C6           | LVCMOS<br>input with<br>P/U | Transmit data clock channels C and D, E and F, G and H. When in independent channel mode, these terminals are used to latch data for their perspective channels on both the rising and falling edges. TCKD applies to channels C and D, TCKF applies to channels E and F, and TCKH applies to channels G and H.                                                |

| TDBA[7:0]              | G2, G1, F2,<br>F1, E2, E1, | LVCMOS<br>input             | Transmit data channels A and B. The parallel data is clocked into the transceiver on the rising and falling edges of TCLKB and transmitted as a serial stream with TDBA0 sent as the first bit.                                                                                                                                                                |

|                        | D2, D1                     |                             | In multiplexed channel mode, data for channel B is aligned to the rising edge of TCLKB and data for channel A is aligned to the falling edge of TCLKB.                                                                                                                                                                                                         |

|                        |                            |                             | In nibble interface mode, data is input most-significant nibble first, aligned to the rising edge of TCLKB, followed by the least-significant nibble aligned to the falling edge. When CODE = high, TDBA3 acts as the K-character indicator for channel A.                                                                                                     |

| TDBA8                  | H2                         | LVCMOS<br>input             | Transmit data, K-generator channels A and B. In multiplexed channel mode, when CODE = low, this terminal is the 9 <sup>th</sup> bit of a 10-bit word to be transmitted. When CODE = high, this terminal acts as the K-character indicator. When TDBA8 = high, the data on TDBA[7:0] is encoded into a K-character.                                             |

|                        |                            |                             | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word to be transmitted on channel B. When CODE = high, this terminal acts as the K-character indicator for channel B. Data is latched on the rising and falling edges of TCLKB.                                                                         |

| TDBA9                  | H1                         | LVCMOS input with           | Transmit data channels A and B. When CODE = low, this terminal is the $10^{th}$ bit of a 10-bit word. When CODE = high, this terminal should be left floating or tied low to ground.                                                                                                                                                                           |

|                        |                            | P/D                         | Data is latched on the rising and falling edges of TCLKB.                                                                                                                                                                                                                                                                                                      |

| TDDC[7:0]              | D3, C3, B2,<br>A2, A1, B1, | LVCMOS<br>input             | Transmit data channels C and D. The parallel data is clocked into the transceiver on the rising and falling edges of the transmit clock and transmitted as a serial stream with bit 0 sent as the first bit.                                                                                                                                                   |

|                        | C2, C1                     |                             | In independent channel mode, the transmit clock that latches this input is TCLKD. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                                                                             |

|                        |                            |                             | In multiplexed channel mode, data for channel D is aligned to the rising edge of the transmit clock and data for channel C is aligned to its falling edge.                                                                                                                                                                                                     |

|                        |                            |                             | In nibble interface mode, data is input most-significant nibble first, aligned to the rising edge of the transmit clock, followed by the least-significant nibble aligned to the falling edge of the transmit clock. Channel C data is input on TDDC[4:0] and channel D on TDDC[9:5]. When CODE = high, TDDC3 acts as the K-character indicator for channel C. |

| SIGNAL    | LOCATION                   | TYPE              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDDC8     | А3                         | LVCMOS<br>input   | Transmit data, K-generator channels C and D. In multiplexed channel mode, when CODE = low, this terminal is the $9^{th}$ bit of a 10-bit word to be transmitted. When CODE = high, this terminal acts as the K-character indicator. When TDDC8 = high, the data on TDDC[7:0] is encoded into a K-character.                                                    |

|           |                            |                   | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word to be transmitted on channel D. When CODE = high, this terminal acts as the K-character indicator for channel D.                                                                                                                                   |

|           |                            |                   | In independent channel mode, the transmit clock that latches this input is TCLKD. In all other modes the transmit clock is TCLKB.                                                                                                                                                                                                                              |

| TDDC9     | В3                         | LVCMOS input with | Transmit data channels C and D. When CODE = low, this terminal is the 10 <sup>th</sup> bit of a 10-bit word. When CODE = high, this terminal should be left floating or tied low to ground.                                                                                                                                                                    |

|           |                            | P/D               | In independent channel mode, the transmit clock that latches this input is TCLKD. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                                                                             |

| TDFE[7:0] | B7, A7, B6,<br>A6, B5, A5, | LVCMOS<br>input   | Transmit data channels E and F. The parallel data is clocked into the transceiver on the rising and falling edges of the transmit clock and transmitted as a serial stream with bit 0 sent as the first bit.                                                                                                                                                   |

|           | B4, A4                     |                   | In independent channel mode, the transmit clock that latches this input is TCLKF. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                                                                             |

|           |                            |                   | In multiplexed channel mode, data for channel F is aligned to the rising edge of the transmit clock and data for channel E is aligned to its falling edge.                                                                                                                                                                                                     |

|           |                            |                   | In nibble interface mode, data is input most-significant nibble first, aligned to the rising edge of the transmit clock, followed by the least-significant nibble aligned to the falling edge of the transmit clock. Channel E data is input on TDFE[4:0] and channel F on TDFE[9:5]. When CODE = high, TDDC3 acts as the K-character indicator for channel E. |

| TDFE8     | A8                         | LVCMOS<br>input   | Transmit data, K-generator channels E and F. In multiplexed channel mode, when CODE = low, this terminal is the 9 <sup>th</sup> bit of a 10-bit word to be transmitted. When CODE = high, this terminal acts as the K-character indicator. When TDFE8 = high, the data on TDFE[7:0] is encoded into a K-character.                                             |

|           |                            |                   | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word to be transmitted on channel F. When CODE = high, this terminal acts as the K-character indicator for channel F.                                                                                                                                   |

|           |                            |                   | In independent channel mode, the transmit clock that latches this input is TCLKF. In all other modes the transmit clock is TCLKB.                                                                                                                                                                                                                              |

| TDFE9     | B8                         | LVCMOS input with | Transmit data channels E and F. When CODE = low, this terminal is the 10 <sup>th</sup> bit of a 10-bit word. When CODE = high, this terminal should be left floating or tied low to ground.                                                                                                                                                                    |

|           |                            | P/D               | In independent channel mode, the transmit clock that latches this input is TCLKF. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                                                                             |

| TDHG[7:0] | B12, A12,<br>B11, A11,     | LVCMOS input      | Transmit data channels G and H. The parallel data is clocked into the transceiver on the rising and falling edges of the transmit clock and transmitted as a serial stream with bit 0 sent as the first bit.                                                                                                                                                   |

|           | B10, A10,<br>B9, A9        |                   | In independent channel mode, the transmit clock that latches this input is TCLKD. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                                                                             |

|           |                            |                   | In multiplexed channel mode, data for channel H is aligned to the rising edge of the transmit clock and data for channel G is aligned to its falling edge.                                                                                                                                                                                                     |

|           |                            |                   | In nibble interface mode, data is input most-significant nibble first, aligned to the rising edge of the transmit clock, followed by the least-significant nibble aligned to the falling edge of the transmit clock. Channel G data is input on TDHG[4:0] and channel F on TDHG[9:5]. When CODE = high, TDHG3 acts as the K-character indicator for channel G. |

| SIGNAL | LOCATION | TYPE              | DESCRIPTION                                                                                                                                                                                                                                                                                                 |

|--------|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDHG8  | A13      | LVCMOS<br>input   | Transmit data, K-generator channels G and H. In multiplexed channel mode, when CODE = low, this terminal is the $9^{th}$ bit of a 10-bit word to be transmitted. When CODE = high, this terminal acts as the K-character indicator. When TDHG8 = high, the data on TDHG[7:0] is encoded into a K-character. |

|        |          |                   | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word to be transmitted on channel H. When CODE = high, this terminal acts as the K-character indicator for channel H.                                                                                |

|        |          |                   | In independent channel mode, the transmit clock that latches this input is TCLKH. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                          |

| TDHG9  | B13      | LVCMOS input with | Transmit data channels G and H. When CODE = low, this terminal is the $10^{th}$ bit of a 10-bit word. When CODE = high, this terminal should be left floating or tied low to ground.                                                                                                                        |

|        |          | P/D               | In independent channel mode, the transmit clock that latches this input is TCLKH. In all other modes, the transmit clock is TCLKB.                                                                                                                                                                          |

## **Receive Data Bus and Clock Signals**

| SIGNAL        | LOCATION                             | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|--------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

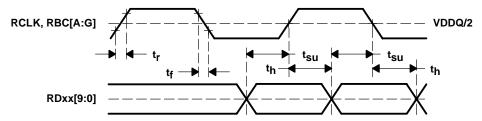

| RCLK/<br>RBCH | R10                                  | LVCMOS<br>output | Receive byte clock. In synchronized channel modes (nibble mode or multiplexed channel mode), RCLK is a buffered version of REFCLK used by the protocol device to latch the received data output on RDBA[9:0], RDDC[9:0], RDFE[9:0] and RDHG[9:0].                                                                                                                                                                                  |

|               |                                      |                  | With the internal CTC FIFO disabled (only valid for nibble interface mode), this clock is $1/10^{\text{th}}$ the clock recovered from the incoming data stream. If CTC is enabled, this clock is a buffered version of REFCLK.                                                                                                                                                                                                     |

|               |                                      |                  | This terminal is internally series-terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                     |

| RBC[G:A]      | R9, R8, R7,                          | LVCMOS           | Individual receive byte clock channels A through G. Recovered clock for channels A through G.                                                                                                                                                                                                                                                                                                                                      |

|               | R6, R5, R4,<br>P4                    | output           | When in independent channel mode, these clocks are used by the protocol device to latch the received data output for channels A through G. Data is aligned to both the rising and falling edges. When in nibble interface mode with the internal CTC FIFO disabled, these terminals are 1/10 <sup>th</sup> the clock recovered from the incoming data stream. If CTC is enabled, these clocks are all buffered versions of REFCLK. |

|               |                                      |                  | When in multiplexed channel mode, the RBCG clock becomes a complementary output to RCLK/RBCH. Similarly, RBCB and RBCA, RBCD and RBCC, RBCF and RBCE are paired clock copies of RCLK/RBCH and RBCG.                                                                                                                                                                                                                                |

|               |                                      |                  | These terminals are internally series-terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                 |

| RDBA[7:0]     | N2, N1,<br>M2, M1, L2,<br>L1, K2, K1 | LVCMOS output    | Receive data channels A and B. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                                           |

|               |                                      |                  | In multiplexed channel mode, data for channel B is aligned to the rising edge of RCLK and data for channel A is aligned to the falling edge of RCLK (see Figure 6 for clarity).                                                                                                                                                                                                                                                    |

|               |                                      |                  | In nibble mode, data is output least-significant nibble first, aligned to the falling edge of the receive clock, followed by the most-significant nibble aligned to the rising edge. Channel A is output on RDBA[4:0] and channel B is output on RDBA[9:5]. When CODE = high, RDBA3 acts as the K-flag bit for channel A on the rising edge of RCLK.                                                                               |

|               |                                      |                  | These terminals are internally series-terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                 |

| RDBA8         | P1                                   | LVCMOS output    | Receive data/K-flag, channels A and B. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                                   |

|               |                                      |                  | In multiplexed channel mode, when CODE = low, this terminal is the 9 <sup>th</sup> bit of a 10-bit word received. When CODE = high, this terminal acts as the K-flag bit. When RDBA8 = high, this terminal indicates that the data on RDBA[7:0] is a K-character.                                                                                                                                                                  |

|               |                                      |                  | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word received on channel B. When CODE = high, this terminal acts as the $4^{th}$ bit on the falling edge and as the K-flag bit on the rising edge for channel B. When RDBA8 = high, this terminal indicates that the data on RDBA[7:0], output on the rising and falling edges of the receive clock, is a K-character.      |

|               |                                      |                  | This terminal is internally series-terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                     |

| SIGNAL    | LOCATION                   | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDBA9     | P2                         | LVCMOS<br>output | Receive data 9, channels A and B <sub>=</sub> The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock. In multiplexed channel mode, when CODE = low, this terminal is the 10 <sup>th</sup> bit of a 10-bit word received.                                                                                                                                                    |

|           |                            |                  | In nibble interface mode, when CODE = low, this terminal is the $5^{th}$ and $10^{th}$ bits of a 10-bit word received on channel B.                                                                                                                                                                                                                                                                                           |

|           |                            |                  | This terminal is internally series-terminated-to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                |

| RDDC[7:0] | P3, R3, T2,<br>U2, U1, T1, | LVCMOS output    | Receive data channels C and D. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                                      |

|           | R2, R1                     |                  | In multiplexed channel mode, data for channel D is aligned to the rising edge of RCLK and data for channel C is aligned to the falling edge of RCLK (see Figure 6 for clarity).                                                                                                                                                                                                                                               |

|           |                            |                  | In nibble mode, data is output least-significant nibble first, aligned to the falling edge of the receive clock, followed by the most-significant nibble aligned to the rising edge. Channel C is output on RDDC[4:0] and channel D is output on RDDC[9:5]. When CODE = high, RDDC3 acts as the K-flag bit for channel C on the rising edge of RCLK.                                                                          |

|           |                            |                  | These terminals are internally series-terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                                                                            |

| RDDC8     | U3                         | LVCMOS output    | Receive data/K-flag, channels C and D. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                              |

|           |                            |                  | In multiplexed channel mode, when CODE = low, this terminal is the 9 <sup>th</sup> bit of a 10-bit word received. When CODE = high, this terminal acts as the K-flag bit. When RDDC8 = high, this terminal indicates that the data on RDDC[7:0] is a K-character.                                                                                                                                                             |

|           |                            |                  | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word received on channel D. When CODE = high, this terminal acts as the $4^{th}$ bit on the falling edge and as the K-flag bit on the rising edge for channel D. When RDDC8 = high, this terminal indicates that the data on RDDC[7:0], output on the rising and falling edges of the receive clock, is a K-character. |

|           |                            |                  | This terminal is internally series-terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                |

| RDDC9     | Т3                         | LVCMOS<br>output | Receive data 9, channels C and D. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock. In multiplexed channel mode, when CODE = low, this terminal is the 10 <sup>th</sup> bit of a 10-bit word received.                                                                                                                                                                |

|           |                            |                  | In nibble interface mode, when CODE = low, this terminal is the $5^{th}$ and $10^{th}$ bits of a 10-bit word received on channel D.                                                                                                                                                                                                                                                                                           |

|           |                            |                  | This terminal is internally series-terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                |

| RDFE[7:0] | T7, U7, T6,<br>U6, T5, U5, | LVCMOS output    | Receive data channels E and F. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                                      |

|           | T4, U4                     |                  | In multiplexed channel mode, data for channel F is aligned to the rising edge of RCLK and data for channel E is aligned to the falling edge of RCLK (see Figure 6 for clarity).                                                                                                                                                                                                                                               |

|           |                            |                  | In nibble mode, data is output least-significant nibble first, aligned to the falling edge of the receive clock, followed by the most-significant nibble aligned to the rising edge. Channel E is output on RDFE[4:0] and channel F is output on RDFE[9:5]. When CODE = high, RDFE3 acts as the K-flag bit for channel E on the rising edge of RCLK.                                                                          |

|           |                            |                  | These terminals are internally series-terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                             |

| RDFE8     | U8                         | LVCMOS output    | Receive data/K-flag, channels E and F. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                              |

|           |                            |                  | In multiplexed channel mode, when CODE = low, this terminal is the 9 <sup>th</sup> bit of a 10-bit word received. When CODE = high, this terminal acts as the K-flag bit. When RDFE8 = high, this terminal indicates that the data on RDFE[7:0] is a K-character.                                                                                                                                                             |

|           |                            |                  | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word received on channel F. When CODE = high, this terminal acts as the $4^{th}$ bit on the falling edge and as the K-flag bit on the rising edge for channel F. When RDFE8 = high, this terminal indicates that the data on RDFE[7:0], output on the rising and falling edges of the receive clock, is a K-character. |

|           |                            |                  | This terminal is internally series terminated to provide direct connection to a 50-Ω transmission line.                                                                                                                                                                                                                                                                                                                       |

| SIGNAL    | LOCATION               | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDFE9     | Т8                     | LVCMOS<br>output | Receive data 9, channels E and F. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock. In multiplexed channel mode, when CODE = low, this terminal is the 10 <sup>th</sup> bit of a 10-bit word received.                                                                                                                                                                |

|           |                        |                  | In nibble interface mode, when CODE = low, this terminal is the $5^{th}$ and $10^{th}$ bits of a 10-bit word received on channel F.                                                                                                                                                                                                                                                                                           |

|           |                        |                  | This terminal is internally series terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                                                                               |

| RDHG[7:0] | T12, U12,<br>T11, U11, | LVCMOS output    | Receive data channels G and H. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                                      |

|           | T10, U10,<br>T9, U9    |                  | In multiplexed channel mode, data for channel H is aligned to the rising edge of RCLK and data for channel G is aligned to the falling edge of RCLK (see Figure 6 for clarity).                                                                                                                                                                                                                                               |

|           |                        |                  | In nibble mode, data is output least-significant nibble first, aligned to the falling edge of the receive clock, followed by the most significant nibble aligned to the rising edge. Channel G is output on RDHG[4:0] and channel H is output on RDHG[9:5]. When CODE = high, RDHG3 acts as the K-flag bit for channel G on the rising edge of RCLK.                                                                          |

|           |                        |                  | These terminals are internally series terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                                                                            |

| RDHG8     | U13                    | LVCMOS output    | Receive data/K-flag, channels G and H. The parallel data is clocked out of the transceiver on the rising and falling edges of receive clock.                                                                                                                                                                                                                                                                                  |

|           |                        |                  | In multiplexed channel mode, when CODE = low, this terminal is the 9 <sup>th</sup> bit of a 10-bit word received. When CODE = high, this terminal acts as the K-flag bit. When RDFE8 = high, this terminal indicates that the data on RDHG[7:0] is a K-character.                                                                                                                                                             |

|           |                        |                  | In nibble interface mode, when CODE = low, this terminal is the $4^{th}$ and $9^{th}$ bits of a 10-bit word received on channel H. When CODE = high, this terminal acts as the $4^{th}$ bit on the falling edge and as the K-flag bit on the rising edge for channel H. When RDHG8 = high, this terminal indicates that the data on RDHG[7:0], output on the rising and falling edges of the receive clock, is a K-character. |

|           |                        |                  | This terminal is internally series-terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                                                                               |

| RDHG9     | T13                    | LVCMOS output    | Receive data 9, channels G and H. The parallel data is clocked out of the transceiver on the rising and falling edges of the receive clock.                                                                                                                                                                                                                                                                                   |

|           |                        |                  | In multiplexed channel mode, when CODE = low, this terminal is the 10 <sup>th</sup> bit of a 10-bit word received.                                                                                                                                                                                                                                                                                                            |

|           |                        |                  | In nibble interface mode, when CODE = low, this terminal is the $5^{th}$ and $10^{th}$ bits of a 10-bit word received on channel H.                                                                                                                                                                                                                                                                                           |

|           |                        |                  | This terminal is internally series-terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                                                                |

## **Management Data Interface Signals**

| SIGNAL    | LOCATION                      | TYPE                        | DESCRIPTION                                                                                                                                                                                                  |

|-----------|-------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

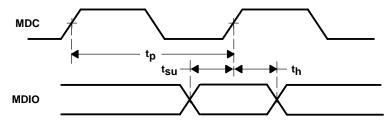

| MDIO      | J1                            | LVCMOS<br>I/O with<br>P/U   | Management data I/O. MDIO is the bidirectional serial data path for the transfer of management data to and from the protocol device.                                                                         |

| MDC       | НЗ                            | LVCMOS<br>input             | Management data clock. MDC is the clock reference for the transfer of management data to and from the protocol device.                                                                                       |

| DVAD[4:0] | D12, D11,<br>P13, R13,<br>R12 | LVCMOS<br>input with<br>P/D | Management address. Device address: DVAD[4:0] is the externally set physical address given to this device, used to distinguish one device from another. This address is latched on the rising edge of RESET. |

## JTAG Interface Signals

| SIGNAL | LOCATION | TYPE                        | DESCRIPTION                                                                                                                                              |

|--------|----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK    | C10      | LVCMOS<br>input             | Test clock. IEEE 1149.1 (JTAG) TCK is used to clock state information and test data into and out of the device during the operation of the test port.    |

| TDI    | C9       | LVCMOS<br>input with<br>P/U | Test data input. IEEE 1149.1 (JTAG) TDI is used to shift test data and test instructions into the device serially during the operation of the test port. |

# **TLK2208A**

# 8-PORT GIGABIT ETHERNET TRANSCEIVER SLLS566A - MAY 2003 - REVISED JULY 2003

| TDO  | C7  | LVCMOS<br>output            | Test data output. IEEE 1149.1 (JTAG) TDO is used to shift test data and test instructions out of the device serially during operation of the test port. When the JTAG port is not in use, TDO is in a high-impedance state. |

|------|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS  | C11 | LVCMOS<br>input<br>with P/U | Test mode select. IEEE 1149.1 (JTAG) TMS is used to control the state of the internal test-port controller.                                                                                                                 |

| TRST | D8  | LVCMOS<br>input<br>with P/U | JTAG reset. IEEE 1149.1 (JTAG) TRST is used to reset the internal JTAG controller.                                                                                                                                          |

## Miscellaneous Signals

| SIGNAL         | LOCATION | TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CODE           | J2       | LVCMOS<br>input<br>with P/D | Encode enable. When high, the 8b/10b encoder and decoder are enabled. The logic value of this terminal is logically ORed with MDIO register 17.7 (8b/10b_EN).                                                                                                                                                                                                                                                                                                 |

| CV_DIS_EN      | J3       | LVCMOS<br>input<br>with P/D | Code violation/disparity error code enable. When CV_DIS_EN is high, the outputs RDxx[9:0] are set to 1 when a code violation or disparity error is detected. The logic value of this terminal is logically ORed with the MDIO register 17.14 (CVDispEn).                                                                                                                                                                                                      |

|                |          |                             | This requires CODE to be enabled.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RESET          | G3       | LVCMOS<br>input with<br>P/D | Chip reset (FIFO clear). Pulling this terminal high recenters the transmit skew buffers, recenters receive channel synchronization FIFOs, and resets MDIO flags.                                                                                                                                                                                                                                                                                              |

| LPBK           | D7       | LVCMOS<br>input<br>with P/D | Serial loopback enable. When asserted high, the outputs of the 8b/10b encoder are looped into the inputs of the 8b/10b decoder for each channel. The serial transmit outputs are held in the high-impedance state and the serial inputs are ignored.                                                                                                                                                                                                          |

| MODE1<br>MODE0 | P12, P11 | LVCMOS<br>input<br>with P/D | Configuration terminals. These terminals put the device under one of the following operation modes:  MODE[1:0]  00 – Multiplexed channel mode  01 – Reserved  10 – Nibble interface mode  11 – Reserved                                                                                                                                                                                                                                                       |

| ENABLE         | D13      | LVCMOS<br>input<br>with P/U | Device enable. Pulling this terminal high enables all outputs of the device. A low on this terminal places all outputs for the device in the high-impedance state.                                                                                                                                                                                                                                                                                            |

| TCLKSEL        | D9       | LVCMOS<br>input             | Transfer clock select. This terminal controls clock selection mode between synchronized and independent channel mode.  In independent channel mode (TCLKSEL = 1) channels are clocked in and out by independent clocks TLCK[B:H] and RBC[A:H], respectively. In synchronized channel mode (TCLKSEL = 0) transmit and receive clocks are centered around TCLKB and RCLK/RBCH.  The logic value of this signal is ORed with TransClkMode, MDIO register R17.15. |

| BUSYEN         | P9       | LVCMOS<br>input<br>with P/U | Busy mode enable. When asserted high, /K28.5/D10.1/ are treated as valid data and passed through the FIFO. When in the low state it causes high /K28.5/D10.1/ to be treated as an IDLE sequence that can be deleted.                                                                                                                                                                                                                                          |

| PLL_LOCK       | R11      | LVCMOS<br>output            | PLL lock. When asserted high, this terminal provides an indication that sufficient time has elapsed after a power-cycle or power-down sequence to ensure that PLLs have achieved lock.                                                                                                                                                                                                                                                                        |

| GE_MOD | C8  | LVCMOS                      | Gigabit Ethernet mode. When driven high, the chip:                                                                                                                                                  |  |

|--------|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        |     | input                       | 1) Treats /K28.5/ followed by any valid data character as an IDLE sequence, except that when BMOD is asserted, the chip treats /K28.5/D10.1/ as described in the BMOD terminal description.         |  |

|        |     |                             | 2) Modifies IDLE to correct disparity by substituting /D5.6/ for /D16.2/ in a /K28.5/Dx.y/ transmit IDLE pair.                                                                                      |  |

|        |     |                             | The logic value of the GE_MOD terminal is ORed with GEMODE register 24.15.                                                                                                                          |  |

| PRBSEN | C13 | LVCMOS<br>input<br>with P/D | PRBS enable. When this terminal is asserted high, the pseudorandom bit stream generator and comparator circuits are inserted into the transmit and receive data paths on all channels respectively. |  |

|        |     |                             | If this terminal is not used it can be tied to the GND reference.                                                                                                                                   |  |

|        |     |                             | TX+/TX- are transmitting $2^7$ -1 PRBS. RX+/RX- are comparing incoming data to an internally generated $2^7$ -1 PRBS. Results of the RX comparison can be read from the MDIO.                       |  |

## **Power and Reference Terminal Descriptions**

| SIGNAL | LOCATION                                                                                                                                                                     | TYPE   | DESCRIPTION                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------|

| VDDQ   | E9, E8, E7, E6, E5, F5, G5,<br>H5, J5, K5, L5, M5, N5, N6,<br>N7, N8, N9                                                                                                     | Supply | I/O supply voltage. 1.8 V $\pm$ 0.2 V or 2.5 V $\pm$ 0.2 V                                                                   |

| VDD    | E10, E11, E12, N10, N11,<br>N12                                                                                                                                              | Supply | Digital logic power. Provides power for all digital circuitry. Nominally 1.8 V                                               |

| VDDA   | E13, F13, G13, H13, J13,<br>K13, L13, M13, N13                                                                                                                               | Supply | Analog power. VDDA provides a supply reference for the high-speed analog circuits, receiver and transmitter. Nominally 1.8 V |

| GROUND |                                                                                                                                                                              |        |                                                                                                                              |

| GNDA   | E14, F14, G14, H14, J16,<br>J17, K14, L14, M14, N14                                                                                                                          | Ground | Analog ground. GNDA provides a ground reference for the high-speed analog circuits, RX and TX.                               |

| GND    | E4, F4, G4, H4, J4, K4, L4,<br>M4, N4, A14, B14, C14,<br>D14, P14, R14, T14, U14,<br>A17, B17, C17, D17, E17,<br>F17, G17, H17, K17, L17,<br>M17, N17, P17, R17, T17,<br>U17 | Ground | Digital logic ground. Provides a ground for the logic circuits and digital I/O buffers.                                      |

## Reserved and NC Signals

| SIGNAL | LOCATION                                             | TYPE | DESCRIPTION                                                                                   |

|--------|------------------------------------------------------|------|-----------------------------------------------------------------------------------------------|

| RSVD   | F3, P7, P8, P10                                      | RSVD | Reserved. Terminals available to TI test. These terminals should not be externally connected. |

| NC     | D4, D5, D6, D10, J14, J15,<br>K3, L3, M3, N3, P5, P6 |      | NC. These signal terminals have no internal connection.                                       |

## **Terminal-to-Signal Map**

| TERMINAL<br>NUMBER | TERMINAL FUNCTION | MULTIPLEXED CHANNEL MODE              | NIBBLE INTERFACE SYNCHRONIZED AND INDEPENDENT CHANNEL MODES |

|--------------------|-------------------|---------------------------------------|-------------------------------------------------------------|

| A1                 | TDDC3             | Transmit bus channel D/C bit 3        | Transmit bus channel C bits 8, 3, K-bit                     |

| A2                 | TDDC4             | Transmit bus channel D/C bit 4        | Transmit bus channel C bits 9, 4                            |

| А3                 | TDDC8             | Transmit bus channel D/C bit 8, K-bit | Transmit bus channel D bits 8, 3, K-bit                     |

| A4                 | TDFE0             | Transmit bus channel F/E bit 0        | Transmit bus channel E bits 5, 0                            |

| A5                 | TDFE2             | Transmit bus channel F/E bit 2        | Transmit bus channel E bits 7, 2                            |

| A6                 | TDFE4             | Transmit bus channel F/E bit 4        | Transmit bus channel E bits 9, 4                            |

| A7                 | TDFE6             | Transmit bus channel F/E bit 6        | Transmit bus channel F bits 6, 1                            |

| A8                 | TDFE8             | Transmit bus channel F/E bit 8, K-bit | Transmit bus channel F bits 8, 3, K-bit                     |

| TERMINAL<br>NUMBER | TERMINAL<br>FUNCTION | MULTIPLEXED CHANNEL MODE              | NIBBLE INTERFACE SYNCHRONIZED AND INDEPENDENT CHANNEL MODES |  |

|--------------------|----------------------|---------------------------------------|-------------------------------------------------------------|--|

| A9                 | TDHG0                | Transmit bus channel H/G bit 0        | Transmit bus channel G bits 5, 0                            |  |

| A10                | TDHG2                | Transmit bus channel H/G bit 2        | Transmit bus channel G bits 7, 2                            |  |

| A11                | TDHG4                | Transmit bus channel H/G bit 4        | Transmit bus channel G bits 9, 4                            |  |

| A12                | TDHG6                | Transmit bus channel H/G bit 6        | Transmit bus channel H bits 6, 1                            |  |

| A13                | TDHG8                | Transmit bus channel H/G bit 8, K-bit | Transmit bus channel H bits 8, 3, K-bit                     |  |

| A14                | GNDA                 | Analog                                | ground                                                      |  |

| A15                | TXH-                 | Channel H s                           | erial output –                                              |  |

| A16                | TXH+                 | Channel H s                           | erial output +                                              |  |

| A17                | GNDA                 | Analog ground                         |                                                             |  |

| B1                 | TDDC2                | Transmit bus channel D/C bit 2        | Transmit bus channel C bits 7, 2                            |  |

| B2                 | TDDC5                | Transmit bus channel D/C bit 5        | Transmit bus channel D bits 5, 0                            |  |

| В3                 | TDDC9                | Transmit bus channel D/C bit 9        | Transmit bus channel D bits 9, 4                            |  |

| B4                 | TDFE1                | Transmit bus channel F/E bit 1        | Transmit bus channel E bits 6, 1                            |  |

| B5                 | TDFE3                | Transmit bus channel F/E bit 3        | Transmit bus channel E bits 8, 3, K-bit                     |  |

| B6                 | TDFE5                | Transmit bus channel F/E bit 5        | Transmit bus channel F bits 5, 0                            |  |

| B7                 | TDFE7                | Transmit bus channel F/E bit 7        | Transmit bus channel F bits 7, 2                            |  |

| B8                 | TDFE9                | Transmit bus channel F/E bit 9        | Transmit bus channel F bits 9, 4                            |  |

| В9                 | TDHG1                | Transmit bus channel H/G bit 1        | Transmit bus channel G bits 6, 1                            |  |

| B10                | TDHG3                | Transmit bus channel H/G bit 3        | Transmit bus channel G bits 8, 3, K-bit                     |  |

| B11                | TDHG5                | Transmit bus channel H/G bit 5        | Transmit bus channel H bits 5, 0                            |  |

| B12                | TDHG7                | Transmit bus channel H/G bit 7        | Transmit bus channel H bits 7, 2                            |  |

| B13                | TDHG9                | Transmit bus channel H/G bit 9        | Transmit bus channel H bits 9, 4                            |  |

| B14                | GNDA                 | Analog ground                         |                                                             |  |

| B15                | TXG-                 | Channel G serial output-              |                                                             |  |

| B16                | TXG+                 | Channel G serial output+              |                                                             |  |

| B17                | GNDA                 | Analog                                | ground                                                      |  |

| C1                 | TDDC0                | Transmit bus channel D/C bit 0        | Transmit bus channel C bits 5, 0                            |  |

| C2                 | TDDC1                | Transmit bus channel D/C bit 1        | Transmit bus channel C bits 6, 1                            |  |

| C3                 | TDDC6                | Transmit bus channel D/C bit 6        | Transmit bus channel D bits 6, 1                            |  |

| C4                 | TCLKD                | Unused                                | Channels C and D transmit bus clock                         |  |

| C5                 | TCLKF                | Unused                                | Channels E and F transmit bus clock                         |  |

| C6                 | TCLKH                | Unused                                | Channels G and H transmit bus clock                         |  |