UCN5841A - UCN5843A

SERIAL DATA IN 3

LOGIC GROUND 4

# THRU

# **BIMOS II 8-BIT SERIAL-INPUT.** LATCHED DRIVERS

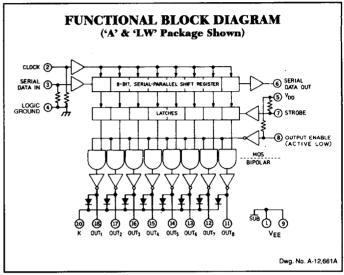

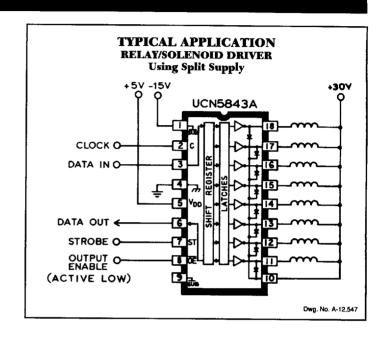

The merging of low-power CMOS logic and bipolar output power drivers permit Series UCN5840A/LW integrated circuits to be used in a wide variety of peripheral power driver applications. The three basic devices in this series each have an eight-bit CMOS shift register and CMOS control circuitry, eight CMOS data latches, and eight bipolar current-sinking Darlington output drivers. The 500 mA NPN Darlington outputs, with integral transient-suppression diodes, are suitable for use with relays, solenoids, and other inductive loads. Except for the maximum driver output voltage ratings, the UCN5841A/LW, UCN5842A/LW, and UCN5843A/LW are identical. The UCN5843A/LW offers premium performance with a minimum output-breakdown voltage rating of 100 V (50 V sustaining). All drivers can be operated with a split supply where the negative supply is up to -20 V.

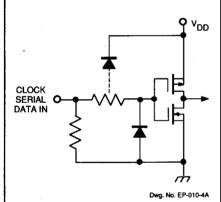

BiMOS II devices have higher data-input rates than the earlier BiMOS circuits. With a 5 V logic supply, they will typically operate at better than 5 MHz. With a 12 V supply, significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS and NMOS logic levels. TTL circuits may require the use of appropriate pullup resistors. By using the serial data output, drivers can be cascaded for interface applications requiring additional drive lines.

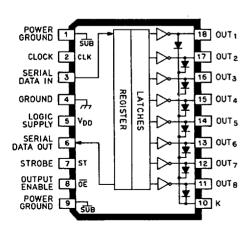

Suffix 'A' devices are furnished in a standard 18-pin plastic DIP: suffix 'LW' indicates an 18-lead wide-body SOIC.

# **FEATURES**

- 3.3 MHz Minimum Data-Input Rate

- CMOS, NMOS, TTL Compatible Inputs

- Internal Pull-Up/Pull-Down Resistors

- Low-Power CMOS Logic and Latches,

- High-Voltage Current-Sink Outputs

- Output Transient-Protection Diodes

- Single or Split Supply Operation

- DIP, PLCC, or SOIC Packaging

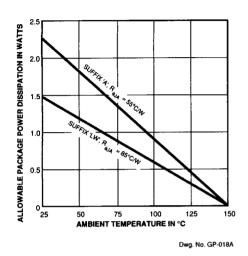

LOGIC SUPPLY 5 SERIAL DATA OUT 6 STROBE 7 OUTPUT ENABLE TE Dwg. No. A-12,659 ABSOLUTE MAXIMUM RATINGS at 25°C Free-Air Temperature Output Voltage, V<sub>CE</sub> (UCN5842A/LW) ..... 80 V (UCN5843A/LW) ..... 100 V Output Voltage, V<sub>CE(sus)</sub> (UCN5841A/LW) ..... 35 V+ (UCN5842A/LW) ...... 50 V† (UCN5843A/LW) . . . . . . . . . . . 50 V+ Logic Supply Voltage Range, V<sub>DD</sub> . . . . . . . . . . . . . . . 4.5 V to 15 V V<sub>DD</sub> with Reference to V<sub>EF</sub> . . . . . . . 25 V Emitter Supply Voltage, V<sub>FF</sub> . . . . . . . -20 V Input Voltage Range, V<sub>IN</sub> . . . . . . . . . -0.3 V to V<sub>DD</sub> + 0.3 V Continuous Output Current, Package Power Dissipation, Pp..... See Graph Operating Temperature Range, T<sub>A</sub> . . . . . . . . . . . -20°C to +85°C Storage Temperature Range, ്ര<sub>ട</sub> . . . . . . . . . . . -55°C to +150°C †For inductive load applications. Note that the Series UCN5840A (dual in-line package) and Series UCN5840LW (small-outline C package) are electrically identical and share a common pin number assignment.

Always order by complete part number, e.g., UCN5842LW

# 5841 thru 5843 Bimos II 8-bit serial-input, latched drivers

Caution: CMOS devices have input static protection but are susceptible to damage when exposed to extremely high static electrical charges.

## UCN5841LW - UCN5843LW

Dwg. No. A-14,438

Note that the Series UCN5840A (dual in-line package) and Series UCN5840LW (small-outline IC package) are electrically identical and share a common pin number assignment.

# 5841 thru 5843 Bimos II 8-Bit serial-input, latched drivers

# ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ , $V_{DD} = 5$ V, $V_{EE} = 0$ V (unless otherwise specified).

|                                |                      | Applicable |                                                    | Limits   |      |      |  |  |

|--------------------------------|----------------------|------------|----------------------------------------------------|----------|------|------|--|--|

| Characteristic                 | Symbol               | Devices*   | Test Conditions                                    | Min.     | Max. | Unit |  |  |

| Output Leakage Current         | I <sub>CEX</sub>     | UCN5841    | V <sub>OUT</sub> = 50 V                            | _        | 50   | μA   |  |  |

|                                |                      |            | V <sub>OUT</sub> = 50 V, T <sub>A</sub> = +70°C    | _        | 100  | μА   |  |  |

|                                |                      | UCN5842    | V <sub>OUT</sub> = 80 V                            | _        | 50   | μА   |  |  |

|                                |                      |            | V <sub>OUT</sub> = 80 V, T <sub>A</sub> = +70°C    | _        | 100  | μА   |  |  |

|                                |                      | UCN5843    | V <sub>OUT</sub> = 100 V                           | -        | 50   | μА   |  |  |

|                                |                      |            | V <sub>OUT</sub> = 100 V, T <sub>A</sub> = +70°C   | _        | 100  | μА   |  |  |

| Collector-Emitter              | V <sub>CE(SAT)</sub> | ALL        | l <sub>OUT</sub> = 100 mA                          |          | 1.1  | V    |  |  |

| Saturation Voltage             |                      |            | l <sub>OUT</sub> = 200 mA                          |          | 1.3  | ٧    |  |  |

|                                |                      |            | I <sub>OUT</sub> = 350 mA, V <sub>DD</sub> = 7.0 V | T        | 1.6  | V    |  |  |

| Collector-Emitter              | V <sub>CE(sus)</sub> | UCN5841    | I <sub>OUT</sub> = 350 mA, L = 2 mH                | 35       | _    | V    |  |  |

| Sustaining Voltage             |                      | UCN5842    | I <sub>OUT</sub> = 350 mA, L = 2 mH                | 50       |      | ٧    |  |  |

|                                |                      | UCN5843    | I <sub>OUT</sub> = 350 mA, L = 2 mH                | 50       | _    | ٧    |  |  |

| nput Voltage                   | V <sub>IN(0)</sub>   | ALL .      | ***                                                | -        | 0.8  | ٧    |  |  |

|                                | V <sub>IN(1)</sub>   | ALL        | V <sub>DD</sub> = 12 V                             | 10.5     | _    | ٧    |  |  |

|                                |                      |            | V <sub>DD</sub> = 10 V                             | 8.5      | _    | ٧    |  |  |

|                                | ľ                    |            | V <sub>DD</sub> = 5.0 V                            | 3.5      | _    | ٧    |  |  |

| nput Resistance                | R <sub>IN</sub>      | ALL        | V <sub>DD</sub> = 12 V                             | 50       | _    | kΩ   |  |  |

|                                |                      |            | V <sub>DD</sub> = 10 V                             | 50       | _    | kΩ   |  |  |

|                                |                      |            | V <sub>DD</sub> = 5.0 V                            | 50       | _    | kΩ   |  |  |

| Supply Current                 | I <sub>DD(ON)</sub>  | ALL        | All Drivers ON, V <sub>DD</sub> = 12 V             | <b>—</b> | 16   | mA   |  |  |

|                                |                      |            | All Drivers ON, V <sub>DD</sub> = 10 V             | _        | 14   | mA   |  |  |

|                                |                      |            | All Drivers ON, V <sub>DD</sub> = 5.0 V            | _        | 8.0  | mA   |  |  |

|                                | I <sub>DD(OFF)</sub> | ALL        | All Drivers OFF, V <sub>DD</sub> = 12 V            | _        | 2.9  | mA   |  |  |

|                                |                      |            | All Drivers OFF, V <sub>DD</sub> = 10 V            | -        | 2.5  | mA   |  |  |

|                                |                      |            | All Drivers OFF, V <sub>DD</sub> = 5.0 V           | -        | 1.6  | mA   |  |  |

| Clamp Diode                    | I <sub>R</sub>       | UCN5841    | V <sub>R</sub> = 50 V                              | _        | 50 , | μA   |  |  |

| Leakage Current                |                      | UCN5842    | V <sub>R</sub> = 80 V                              | _        | 50   | μA   |  |  |

|                                |                      | UCN5843    | V <sub>R</sub> = 100 V                             | _        | 50   | μA   |  |  |

| Clamp Diode<br>Forward Voltage | V <sub>F</sub>       | ALL        | I <sub>F</sub> = 350 mA                            |          | 2.0  | ٧    |  |  |

<sup>\*</sup> Complete part number includes a suffix to identify package style: A = DIP, LW = SOIC.

# 5841 thru 5843 Bimos II 8-Bit Serial-Input, latched drivers

# STROBE OUTPUT ENABLE Dwg. No. EP-010-3

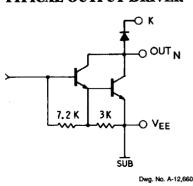

# TYPICAL OUTPUT DRIVER

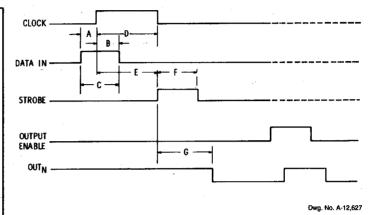

# TIMING CONDITIONS (T<sub>A</sub> = +25°C, Logic Levels are $V_{\rm DD}$ and Ground)

|    | V <sub>DO</sub> =                                              | = 5.0 V |

|----|----------------------------------------------------------------|---------|

| A. | Minimum Data Active Time Before Clock Pulse (Data Set-Up Time) | . 75 ns |

| В. | Minimum Data Active Time After Clock Pulse (Data Hold Time)    | . 75 ns |

| C. | Minimum Data Pulse Width                                       | 150 ns  |

| D. | Minimum Clock Pulse Width                                      | 150 ns  |

| E. | Minimum Time Between Clock Activation and Strobe               | 300 ns  |

| F. | Minimum Strobe Pulse Width                                     | 100 ns  |

| G. | Typical Time Between Strobe Activation and Output Transition   | 500 ns  |

Serial Data present at the input is transferred to the shift register on the logic "0" to logic "1" transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.

Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the ENABLE input be high during serial data entry.

When the ENABLE input is high, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the ENABLE input low, the outputs are controlled by the state of the latches.

# 5841 thru 5843 Bimos II 8-Bit serial-input, latched drivers

### TRUTH TABLE

| Serial<br>Data<br>Input | Clock<br>Input | Shift Register Contents |                |                |                                         | Serial         |                | Latch Contents  |                |                |                |                | Output Contents  |    |                |                |  |                |

|-------------------------|----------------|-------------------------|----------------|----------------|-----------------------------------------|----------------|----------------|-----------------|----------------|----------------|----------------|----------------|------------------|----|----------------|----------------|--|----------------|

|                         |                | I,                      | l <sub>2</sub> | l <sub>3</sub> | *************************************** | l <sub>8</sub> | Data<br>Output | Strobe<br>Input | I,             | l <sub>2</sub> | l <sub>3</sub> | I <sub>8</sub> | Output<br>Enable | 4  | l <sub>2</sub> | l <sub>3</sub> |  | l <sub>8</sub> |

| Н                       | 7              | Н                       | R,             | R <sub>2</sub> |                                         | R <sub>7</sub> | R <sub>7</sub> |                 |                |                |                |                |                  |    |                |                |  |                |

| L                       | 7              | L                       | R,             | R <sub>2</sub> | •••••                                   | R <sub>7</sub> | R <sub>7</sub> |                 |                |                |                |                | i                | ĺ  |                |                |  |                |

| Х                       | Z              | R,                      | R <sub>2</sub> | R <sub>3</sub> |                                         | R <sub>8</sub> | R <sub>8</sub> | 1               |                |                |                |                |                  | ŀ  |                |                |  |                |

|                         |                | Х                       | Х              | Х              |                                         | Х              | Х              | L               | R <sub>1</sub> | R <sub>2</sub> | $R_3$          | R <sub>8</sub> | 1                | ŀ  |                |                |  |                |

|                         |                | P,                      | P <sub>2</sub> | P <sub>3</sub> |                                         | P <sub>8</sub> | P <sub>8</sub> | Н               | Ρ,             | P <sub>2</sub> | P <sub>3</sub> | P <sub>8</sub> | L                | Ρ, | P <sub>2</sub> | P <sub>3</sub> |  | P <sub>8</sub> |

|                         |                |                         |                |                |                                         |                |                |                 | Х              | Х              | Х              | X              | Н                | Н  | Н              | Н              |  | Н              |

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State