# 64-BIT RANDOM-ACCESS READ/WRITE

D1416, DECEMBER 1972-REVISED FEBRUARY 1984

- For Application as a"Scratch Pad" Memory with Nondestructive Read-Out

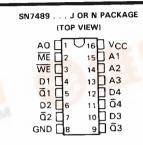

- Fully Decoded Memory Organized as 16 Words of Four Bits Each

- Fast Access Time . . . 33 ns Typical

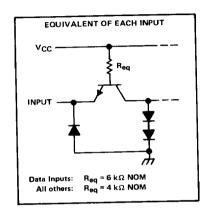

- Diode-Clamped, Buffered Inputs

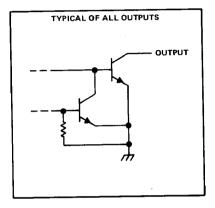

- Open-Collector Outputs Provide Wire-AND Capability

- Typical Power Dissipation . . . 375 mW

- Compatible with Most TTL Circuits

### description

This 64-bit active-element memory is a monolithic, high-speed, transistor-transistor logic (TTL) array of 64 flip-flop memory cells organized in a matrix to provide 16 words of four bits each. Each of the 16 words is addressed in straight binary with full on-chip decoding.

The buffered memory inputs consist of four address lines, four data inputs, a write enable, and a memory enable for controlling the entry and access of data. The memory has opencollector outputs which may be wired-AND connected to permit expansion up to 4704 words of N-bit length without additional output buffering. Access time is typically 33 nanoseconds; power dissipation is typically 375 milliwatts.

#### **FUNCTION TABLE**

| ME | WE | OPERATION       | CONDITION OF OUTPUTS        |

|----|----|-----------------|-----------------------------|

| L  | L  | Write           | Complement of Data Inputs   |

| L  | н  | Read            | Complement of Selected Word |

| Н  | L  | Inhibit Storage | Complement of Data Inputs   |

| Н  | н  | Do Nothing      | High                        |

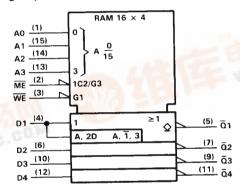

### logic symbol

## write operation

Information present at the data inputs is written into the memory by addressing the desired word and holding both the memory enable and write enable low. Since the internal output of the data input gate is common to the input of the sense amplifier, the sense output will assume the opposite state of the information at the data inputs when the write enable is low.

### read operation

zsc.com

The complement of the information which has been written into the memory is nondestructively read out at the four sense outputs. This is accomplished by holding the memory enable low, the write enable high, and selecting the desired address.

Pia

5

RAM

## schematics of inputs and outputs

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                   |                |

|----------------------------------------------------|----------------|

| Supply voltage, VCC (see Note 17.                  | 5.5 V          |

| Input voltage (see Note 1)                         | EEV            |

| will be at automorphisms. Vol. (see Notes 1 and 2) | , , ,          |

| Operating free-air temperature range               | 0°C to 70°C    |

| Operating free-air temperature range               | -65°C to 150°C |

| Storage temperature range                          |                |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. This is the maximum voltage that should be applied to any output when it is in the off state.

## recommended operating conditions

| MIN  | NOM        | MAX          | UNIT                                   |

|------|------------|--------------|----------------------------------------|

| 4.75 | 5          | 5.25         |                                        |

| 40   |            |              | ns                                     |

| 40   |            |              | ns                                     |

| 5    |            |              | ns                                     |

| 0    |            |              | ns                                     |

| 5    |            |              | ns                                     |

| 0    |            | 70           | °C                                     |

|      | 4.75<br>40 | 4.75 5<br>40 | 4.75 5 5.25<br>40<br>40<br>5<br>0<br>5 |

5

RAMs

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                              | TEST CONDITIONS†                                   |                                                           | MIN TYP‡       | MAX   | UNIT           |

|------------------|----------------------------------------|----------------------------------------------------|-----------------------------------------------------------|----------------|-------|----------------|

| VIH              | High-level input voltage               |                                                    |                                                           | 2              |       | V              |

| VIL              | Low-level input voltage                |                                                    |                                                           | <del>-  </del> | 0.8   | l v            |

| ViK              | Input clamp voltage                    | VCC = MIN,                                         | lj = -12 mA                                               |                | - 1.5 | <del>  ·</del> |

| ЮН               | High-level output current              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>V <sub>OH</sub> = 5.5 V         |                | 20    | μА             |

| VOL              | Low-level output voltage               | V <sub>CC</sub> = MIN, V <sub>IH</sub>             | = 2 V, I <sub>OL</sub> = 12 mA<br>I <sub>OL</sub> = 16 mA |                | 0.4   | V              |

| ĮĮ.              | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                                    |                | 1     | mA             |

| ΙН               | High-level input current               | V <sub>CC</sub> = MAX,                             | V <sub>f</sub> = 2.4 V                                    |                | 40    | μА             |

| I <sub>I</sub> L | Low-level input current                | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0.4 V                                    |                | -1.6  | mA             |

| ICC              | Supply current                         | V <sub>CC</sub> = MAX,                             | See Note 3                                                | 75             | 105   | mA             |

| Со               | Off-state output capacitance           | V <sub>CC</sub> = 5 V,<br>f = 1 MHz                | V <sub>O</sub> = 2.4 V,                                   | 6.5            |       | pF             |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^{\ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

NOTE 3: ICC is measured with the memory enable grounded, all other inputs at 4.5 V, and all outputs open.

## switching characteristics, VCC = 5 V, $T_A = 25 \,^{\circ}\text{C}$

|                  | PARAMETER                                                               | ₹                                          | TEST CONDITIONS                                  | MIN | TYP      | MAX      | UNIT |

|------------------|-------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------|-----|----------|----------|------|

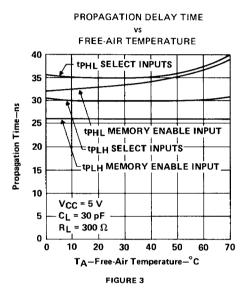

| <sup>t</sup> PLH | Propagation delay time,<br>output from memory en                        | -                                          |                                                  |     | 50       |          |      |

| <sup>t</sup> PHL | Propagation delay time,<br>output from memory en                        |                                            | $C_1 = 30 \text{ pF},$                           |     | 33       | 33 50    | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level output from any address input |                                            | $R_{L1} = 300 \Omega,$<br>$R_{L2} = 600 \Omega,$ |     | 30 60    |          |      |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level output from any address input |                                            | See Figure 1                                     |     | 35       | 60       | ns   |

| tSR              | Sense recovery time after writing                                       | Output initially high Output initially low |                                                  |     | 39<br>48 | 70<br>70 | ns   |

Liz

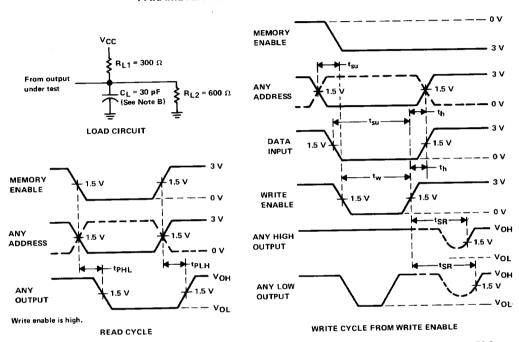

## PARAMETER MEASUREMENT INFORMATION

NOTES: A. The input pulse generators have the following characteristics:  $t_f \le 10$  ns,  $t_f \le 10$  ns, PRR = 1 MHz,  $z_{out} \approx 50 \ \Omega$ .

B. C<sub>L</sub> includes probe and jig capacitance.

FIGURE 1-SWITCHING CHARACTERISTICS

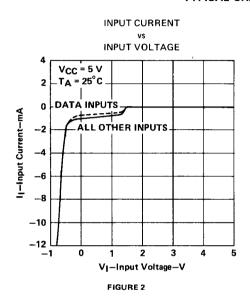

### TYPICAL CHARACTERISTICS

Lia

5

RAM