#### 查询HT1130供应商

#### 捷多邦,专业PCB打样工厂,24小时加急出货

# HT1130 4-bit Microcontroller

#### Features

Operating voltage: 2.4V~3.3V 12 input lines Four output lines Five working registers Sound effect circuit 4K 8 program ROM 128 4 bits data memory RAM size 32 4 segment LCD driver RC oscillator for system clock Halt feature reduces power consumption

#### **General Description**

The HT1130 is a processor from Holtek s 4-bit stand alone single chip microcontroller range specifically designed for LCD product applications. The device is ideally suited for multiple Internal timer overflow interrupt External interrupt One level subroutine nesting 8-bit timer with internal or external clock source 8-bit table read instruction Up to 4 s instruction cycle with 1MHz system clock at V<sub>DD</sub>=3V All instructions in 1 or 2 machine cycles

LCD low power applications among which are calculators, scales and hand-held LCD products.

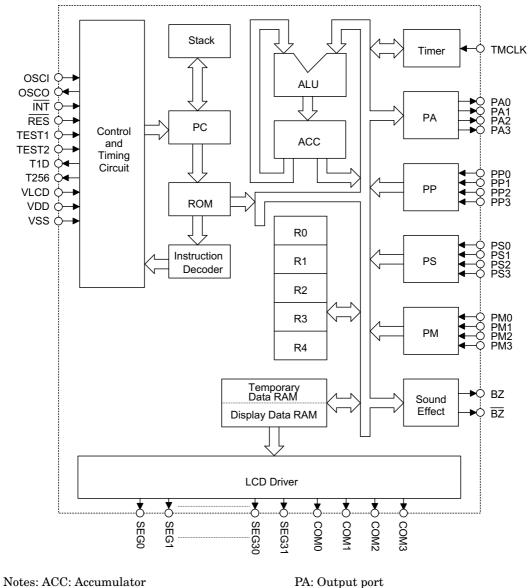

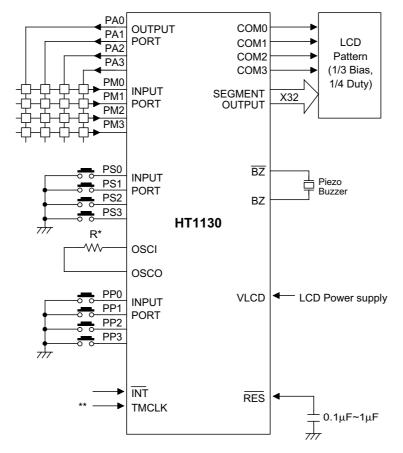

## **Block Diagram**

Notes: ACC: Accumulator PC: Program counter R0~R4: Working registers PA: Output port PS,PM,PP: Input ports

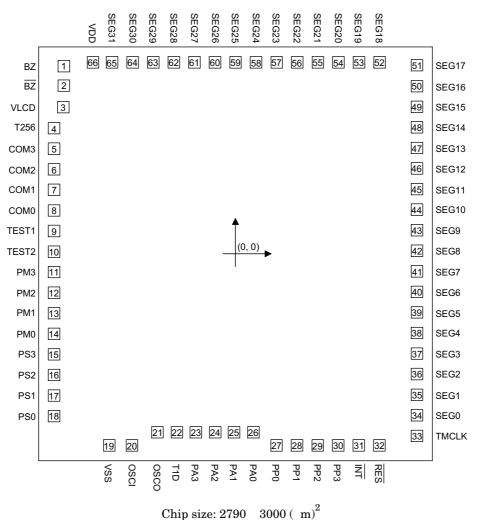

### **Pad Assignment**

\* The IC substrate should be connected to VSS in the PCB layout artwork.

| Pad Coord |         |         | 1       |         | Unit: m |

|-----------|---------|---------|---------|---------|---------|

| Pad No.   | X       | Y       | Pad No. | X       | Y       |

| 1         | 1192.10 | 1305.20 | 34*     | 1261.10 | 1122.30 |

| 2         | 1192.10 | 1169.80 | 35*     | 1261.10 | 979.80  |

| $3^*$     | 1196.70 | 1019.80 | 36*     | 1261.10 | 836.30  |

| 4*        | 1261.10 | 873.70  | 37*     | 1261.10 | 693.80  |

| 5         | 1261.10 | 731.20  | 38*     | 1261.10 | 550.30  |

| 6         | 1261.10 | 587.70  | 39*     | 1261.10 | 407.80  |

| 7         | 1261.10 | 445.20  | 40*     | 1261.10 | 264.30  |

| 8         | 1261.10 | 301.70  | 41*     | 1261.10 | 121.80  |

| 9*        | 1261.10 | 159.20  | 42*     | 1261.10 | 21.70   |

| 10*       | 1261.10 | 15.70   | 43*     | 1261.10 | 164.20  |

| 11        | 1261.10 | 126.80  | 44*     | 1261.10 | 307.70  |

| 12        | 1261.10 | 270.30  | 45*     | 1261.10 | 450.20  |

| 13        | 1261.10 | 412.80  | 46*     | 1261.10 | 593.70  |

| 14        | 1261.10 | 556.30  | 47*     | 1261.10 | 736.20  |

| 15        | 1261.10 | 698.80  | 48*     | 1261.10 | 879.70  |

| 16        | 1261.10 | 842.30  | 49*     | 1261.10 | 1022.20 |

| 17        | 1261.10 | 984.80  | 50*     | 1261.10 | 1165.70 |

| 18        | 1261.10 | 1128.30 | 51*     | 1261.10 | 1311.20 |

| 19*       | 876.70  | 1331.40 | 52*     | 1001.00 | 1331.40 |

| $20^*$    | 719.70  | 1331.40 | 53*     | 858.50  | 1331.40 |

| $21^*$    | 542.10  | 1241.00 | 54*     | 715.00  | 1331.40 |

| $22^{*}$  | 406.70  | 1241.00 | 55*     | 572.50  | 1331.40 |

| 23        | 276.30  | 1241.00 | 56*     | 429.00  | 1331.40 |

| 24        | 140.90  | 1241.00 | 57*     | 286.50  | 1331.40 |

| 25        | 10.50   | 1241.00 | 58*     | 143.00  | 1331.40 |

| 26        | 124.90  | 1241.00 | 59*     | 0.50    | 1331.40 |

| 27        | 284.90  | 1331.40 | 60      | 143.00  | 1331.40 |

| 28        | 427.40  | 1331.40 | 61      | 285.50  | 1331.40 |

| 29        | 570.90  | 1331.40 | 62      | 429.00  | 1331.40 |

| 30        | 713.40  | 1331.40 | 63      | 571.50  | 1331.40 |

| $31^{*}$  | 856.90  | 1331.40 | 64      | 715.00  | 1331.40 |

| $32^{*}$  | 999.40  | 1331.40 | 65      | 857.50  | 1331.40 |

| 33        | 1261.10 | 1265.80 | 66*     | 990.50  | 1331.40 |

These pins must be bonded out for function testing.

### **Pad Description**

| Pad No.            | Pad Name                      | I/O              | Mask Option                   | Function                                                                                                                                |

|--------------------|-------------------------------|------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2               | BZ, BZ                        | 0                | Note 1                        | Sound effect outputs                                                                                                                    |

| 3                  | VLCD                          | Ι                |                               | (+) LCD bias power supply                                                                                                               |

| 4<br>22<br>9<br>10 | T256<br>T1D<br>TEST1<br>TEST2 | 0<br>0<br>I<br>I |                               | For test mode only<br>TEST1 and TEST2 are left open when the HT1130<br>is in normal operation (with an internal pull high<br>resistor). |

| 5~8                | COM3~COM0                     | 0                | Note 2                        | Output for LCD panel common plate                                                                                                       |

| 11~14              | PM3~PM0                       | Ι                | Pull-high or<br>None. Note 3  | 4-bit port for input only                                                                                                               |

| 15~18              | PS3~PS0                       | Ι                | Pull-high or<br>None. Note 3  | 4-bit port for input only                                                                                                               |

| 19                 | VSS                           | Ι                |                               | Negative power supply, GND                                                                                                              |

| 20<br>21           | OSCI<br>OSCO                  | I<br>O           |                               | OSCI,OSCO are connected to an external resistor for an internal system clock                                                            |

| 23~26              | PA3~PA0                       | 0                | CMOS or<br>NMOS Open<br>drain | 4-bit latch port for output only                                                                                                        |

| 27~30              | PP0~PP3                       | Ι                | Pull-high or<br>None. Note 3  | 4-bit port for input only                                                                                                               |

| 31                 | INT                           | Ι                |                               | External interrupt input with pull high resistor<br>Active on edge-triggered high to low transition                                     |

| 32                 | RES                           | Ι                |                               | Input to reset an internal LSI<br>Reset is active on logical low level                                                                  |

| 33                 | TMCLK                         | Ι                | Pull-high or<br>None. Note 4  | Input for TIMER clock<br>TIMER can be clocked by an external clock or an<br>internal frequency source.                                  |

| 34~65              | SEG0~SEG31                    | 0                |                               | LCD driver outputs for LCD panel segment                                                                                                |

| 66                 | VDD                           | Ι                |                               | Positive power supply                                                                                                                   |

\*Notes: 1. The system clock provides six different sources selectable by mask option to drive the sound effect clock. If the Holtek sound library is used, only 128K and 64K are acceptable.

- 2. Either (1/4 duty;1/3 bias) or (1/3 duty:1/3 bias) should be specified by mask option.

- 3. Each bit of ports PM, PS and PP can be a trigger source of the HALT interrupt, selectable by mask option.

- 4. 13 internal clock sources can be selectable by mask option to drive TMCLK. Note that TMCLK should not be connected to a pull high resistor if an internal source is used.

Ta=25 C

### **Absolute Maximum Ratings**

| Supply Voltage      | $\mathrm{V_{DD}}$ 0.3V to 5.5V        |

|---------------------|---------------------------------------|

| Storage Temperature | $50\ \mathrm{C}$ to $125\ \mathrm{C}$ |

| Input Voltage         | $V_{SS}$ | 0.3V to | V <sub>DD</sub> +0 | .3V |

|-----------------------|----------|---------|--------------------|-----|

| Operating Temperature | ÷        | 0       | C to 7             | 0 C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **D.C. Characteristics**

|                  |                                            | ]               | Test Conditions                             | Min. | m    | 3.5  |      |

|------------------|--------------------------------------------|-----------------|---------------------------------------------|------|------|------|------|

| Symbol           | Parameter                                  | V <sub>DD</sub> | V <sub>DD</sub> Conditions                  |      | Тур. | Max. | Unit |

| V <sub>DD</sub>  | Operating Voltage                          |                 |                                             | 2.4  |      | 3.3  | V    |

| I <sub>DD</sub>  | Operating Current                          | 3V              | No load,<br>f <sub>SYS</sub> =500kHz        |      | 500  |      | Α    |

| $I_{STB}$        | Standby Current                            | 3V              | No load,<br>HALT mode                       |      |      | 1    | Α    |

| V <sub>IL</sub>  | Input Low Voltage                          | 3V              |                                             | 0    |      | 0.9  | V    |

| V <sub>IH</sub>  | Input High Voltage                         | 3V              |                                             | 2.1  |      | 3.0  | V    |

| I <sub>OL1</sub> | Port A, BZ and BZ Output<br>Sink Current   | 3V              | V <sub>DD</sub> =3V, V <sub>OL</sub> =0.3V  | 1.5  | 3.0  |      | mA   |

| I <sub>OH1</sub> | Port A, BZ and BZ Output<br>Source Current | 3V              | V <sub>DD</sub> =3V, V <sub>OH</sub> =2.7V  | 0.6  | 1.0  |      | mA   |

| I <sub>OL2</sub> | Segment Output Sink<br>Current             | 3V              | $V_{LCD}$ =3V, $V_{OL}$ =0.3V               | 30   | 55   |      | Α    |

| I <sub>OH2</sub> | Segment Output Source<br>Current           | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V | 20   | 40   |      | Α    |

| R <sub>PH</sub>  | Pull-high Resistance                       | 3V              | PS, PP, PM, <del>INT</del> ,<br>RES, TMCLK  | 30   |      | 300  | k    |

## A.C. Characteristics

| A.C. Characteristics Ta=25 G |                                |                 |                       |      |                 |      |      |

|------------------------------|--------------------------------|-----------------|-----------------------|------|-----------------|------|------|

| G1 -1                        | Demonster                      | Te              | st Conditions         | ъл.  |                 | Ъ    |      |

| Symbol                       | Parameter                      | V <sub>DD</sub> | Conditions            | Min. | Тур.            | Max. | Unit |

| f <sub>SYS</sub>             | System Clock                   | 3V              | R:620k ~36k           | 32   |                 | 1000 | kHz  |

| $\mathbf{f}_{\mathrm{LCD}}$  | LCD Clock                      | 3V              |                       |      | 256*            |      | Hz   |

| taare                        |                                |                 | 1/3 duty              |      | $(1/f_{LCD})$ 3 |      | s    |

| $t_{\rm COM}$                | LCD Common Period              |                 | 1/4 duty              |      | $(1/f_{LCD})$ 4 |      | s    |

| $t_{\rm CY}$                 | Cycle Time                     |                 | $f_{\rm SYS}$ =1.0MHz |      | 4.0             |      | s    |

| f <sub>TIMER</sub>           | Timer I/P Frequency<br>(TMCLK) | 3V              |                       | 0    |                 | 1000 | kHz  |

| t <sub>RES</sub>             | Reset Pulse Width              |                 |                       | 5    |                 |      | ms   |

| t <sub>INT</sub>             | Interrupt Pulse Width          |                 |                       | 1    |                 |      | s    |

| f <sub>SOUND</sub>           | Sound Effect Clock             |                 |                       |      | 64 or 128<br>** |      | kHz  |

Notes:

\*: In general,  $f_{\text{LCD}}$  is selected and optimized by Holtek depending upon  $f_{\text{SYS}}$  and the operating voltage.

$\ast\ast$ : Only these two clocking signal frequencies are supported by Holtek s sound library.

#### **Functional Description**

#### Program counter – PC

This counter addresses the program ROM and is arranged as a 12-bit binary counter from PC0 to PC11 of which contents specify a maximum of 4096 addresses. The program counter counts with an increment of 1 or 2 with each execution of an instruction.

When executing the jump instruction (JMP, JNZ, JC, JTMR,...), a subroutine call, initial reset, internal interrupt, external interrupt or returning from a subroutine, the program counter is loaded with the corresponding instruction data as shown in the table.

Note: P0~P11: Instruction code

@: PC11 keeps the current value S0~S11: Stack register bits

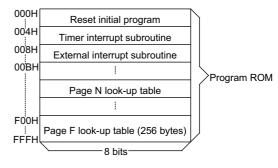

#### **Program memory – ROM**

The program memory is the executable memory and is arranged in a 4096 8 bit format. The address is specified by the program counter (PC). Four special locations are reserved and described as follows:

Location 0

Activating the processor RES pin causes the first instruction to be fetched from location 0.

#### Location 4

Contains the timer interrupt resulting from a TIMER overflow. If the interrupts are enabled it causes the program to jump to this subroutine.

Program memory

#### Location 8

Activating the INT input pin of the processor with the interrupts enabled causes the program to jump to this location.

Activating the PS, PP or PM input pins of the processor with the interrupts enabled during Halt mode also causes the program to jump to this location.

#### Locations n00H to nFFH

These are the 256 bytes of each page in the program memory. This area from n00H to nFFH and F00H to FFFH can be used as a look up table. Instructions such as READ R4A, READ MR0A, READF R4A, READF MR0A can read the table and transfer the contents of the table to ACC and R4 or to ACC and a data memory address specified by the register pair R1,R0. However as R1,R0 can only store 8 bits, these instructions cannot fully specify the full 12 bit

| Mode                   | Program Counter |      |     |     |     |     |     |     |     |     |     |     |

|------------------------|-----------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Mode                   | PC11            | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

| Initial reset          | 0               | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Internal interrupt     | 0               | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| External interrupt     | 0               | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   |

| Jump, call instruction | P11             | P10  | P9  | P8  | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Conditional branch     | @               | P10  | P9  | P8  | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

Program memory

program memory address. For this reason a jump instruction should first be used to place the program counter in the right page. The above instructions can then be used to read the look up table data.

Note that the page number n must be greater than zero as some locations in page 0 are reserved for specific usage. This area may function as a normal program memory when required.

The program memory mapping is shown in the diagram.

In the execution of an instruction the program counter is added before the execution phase, so careful manipulation of READ MR0A and READ R4A is needed in the page margin.

#### Stack register

The stack register is a group of registers used to save the contents of the program counter (PC) and is arranged in 13 bits 1 level. One bit is used to store the carry flag. An interrupt will force the contents of the PC and the carry flag onto the stack register. A subroutine call will also cause the PC contents to be pushed onto the stack; however the carry flag will not be stored. At the end of a subroutine or an interrupt (indicated by a return instruction RET or RETI), the contents of the stack register are returned to the PC.

Executing "RETI" instruction will restore the carry flag from the stack register, but RET does not.

#### Working registers - R0, R1, R2, R3, R4

There are five working registers (R0, R1, R2, R3, R4) used to store the frequently accessed intermediate results. Using the instructions INC Rn and DEC Rn, the working registers can increment (+1) or decrement (1). The JNZ Rn (n=0,1,4) instruction makes efficient use of the working registers as a program loop counter. The register pairs R0,R1 and R2,R3 are also used as a data memory pointer when the memory transfer instruction is executed.

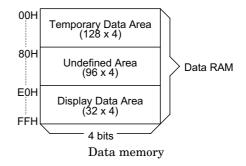

#### Data memory - RAM

The static data memory (RAM) is arranged in 256 4 bit format and is used to store data. All of the data memory locations are indirectly addressable through the register pair R1,R0 or R3,R2; for example MOV A,[R3R2] or MOV [R3R2],A.

There are two areas in the data memory, the temporary data area and the display data area. Access to the temporary data area is from 00H to 7FH. Locations E0H to FFH represent the display data area. The locations between the temporary and display data areas are undefined and cannot be used.

When data is written into the display data area, it is automatically read by the LCD driver which then generates the corresponding LCD driving signals.

#### Accumulator – ACC

The accumulator is the most important data register in the processor. It is one of the sources of input to the ALU and the destination of the results of the operations performed in the ALU. Data to and from the I/O ports and memory also pass through the accumulator.

#### Arithmetic and logic unit – ALU

This circuit performs the following arithmetic and logic operations ...

Add with or without carry Subtract with or without carry AND, OR, Exclusive-OR Rotate right, left through carry

BCD decimal adjust for addition

Increment, decrement Data transfers Branch decisions

The ALU not only outputs the results of data operations, but also sets the status of the carry flag (CF) in some instructions.

#### Timer/counter

The HT1130 contains a programmable 8-bit count-up counter which can be used to count external events or as a clock to generate an accurate time base.

If the 8-bit timer clock is supplied by an external source from pin TMCLK then synchronization problems may occur when reading the data from the timer. It is therefore suggested that the timer is stopped before retrieving the data. The 8-bit counter will increment on the rising edge of the clock whether internally or externally generated.

The timer/counter may be set and read with software instructions and stopped by a hardware reset or a TIMER OFF instruction. To restart the timer, load the counter with the value XXH and then issue a TIMER ON instruction. Note that XX is the desired start count immediate value for 8 bits. Once the timer/counter is started, it increments to a maximum count of FFH and then overflows to zero (00H). It then continues to count until stopped by a TIMER OFF instruction or a reset.

The increment from the maximum count of FFH to a zero (00H) triggers a timer flag TF and an internal interrupt request. The interrupt may be enabled or disabled by executing the EI and DI instruction. If the interrupt is enabled, the timer overflow will cause a subroutine call to location 4. The state of the timer flag is also testable with the conditional jump instruction JTMR. The timer flag is cleared after the interrupt or the JTMR instruction is executed.

If an internal source is used, the frequency is determined by the system clock and the parameter n as defined in the equation. The frequency of the internal frequency source can be selected by mask option. TIMER Frequency clock =  $\frac{\text{system clock}}{2^n}$

where n=0, 1, 2...13 selectable by mask option

Note that n cannot have the value of 6, which is reserved for internal use.

#### Interrupt

The HT1130 provides both internal and external interrupt modes. The DI and EI instructions are used to disable and enable the interrupts. When the INT pin is triggered on a high to low transition in the enable interrupt mode and the program is not within a CALL subroutine, the external interrupt is activated. This causes a subroutine call to location 8 and resets the interrupt latch.

Likewise when the timer flag is set in the enable interrupt mode and the program is not within a CALL subroutine the internal interrupt is activated. This causes a subroutine call to location 4 and resets the timer flag. If both external and internal interrupts arrive at the same time then the external interrupt will be serviced first.

When running under a CALL subroutine or DI the interrupt acknowledge is on hold until the RET or EI instruction is invoked. The CALL instruction should not be used within an interrupt routine as unpredictable result may occur. If within a CALL subroutine both internal and external interrupts occur, no matter what order they arrive in, the external interrupt will be serviced first after leaving the CALL subroutine. This also applies if the two interrupts arrive at the same time.

The interrupts are disabled by a hardware reset or a DI instruction. They remain disabled until the EI instruction is executed.

Each input port bit can be programmed by mask option to have an external interrupt function in the HALT mode.

#### Initial reset

The HT1130 provides an RES pin for system initialization. This pin is equipped with an internal pull high resistor and in combination with an external 0.1 ~1 F capacitor, provides an internal reset pulse of sufficient length to guarantee a reset to all internal circuits. If the reset pulse is generated externally, the RES pin must be held low for at least 5ms. Normal circuit operation will not commence until the RES pin returns high.

The reset performs the following functions:

Sets the program counter PC to 000H

Disables the interrupt mode

Stops the timer

Resets the timer and timer flag

Clears the carry flag

Sets the sound off and one sing mode

Sets port A high or floating

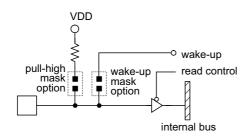

#### Halt

This is a special feature of the HT1130 to interrupt the chip s normal operation and reduce power consumption. When a HALT is executed the following happens ...

The system clock will be stopped.

The contents of the on-chip RAM and registers remain unchanged.

All of the LCD segments and commons will have the VLCD voltage so the LCD becomes blank.

The halt status can be terminated by an external interrupt or a hardware reset.

In the HALT mode any bit of ports PP, PS, PM can be used as external interrupts set by mask option to wake-up the system. This signal is active on a low-going transition.

When the halt status is terminated by an external interrupt, the following procedure takes place ... Case 1: If the system is in an interrupt-disable state before entering the halt state:

The instruction HALT is executed and the system enters a halt state

A falling edge transition on INT, or on any of the wake up pins on ports PP, PS or PM, will awaken the system and return to the main program instruction following the HALT command.

An interrupt signal, whether caused by  $\overline{INT}$  or the ports PP,PS or PM, will be held until the system receives an enable interrupt command at which point the held interrupt will be serviced.

Case 2: If the system is in an interrupt enable state:

The instruction HALT is executed and the system enters a halt state

A falling edge transition on INT, or on any of the wake up pins on ports PP, PS or PM, will awaken the system and execute the external interrupt subroutine

#### Sound effects

The HT1130 includes sound effect circuitry which offers up to 16 sounds with 3 tones, boom and noise effects. Holtek supports a sound library which has melodies, alarms, machine guns etc..

Whenever the instruction "SOUND n" or "SOUND A" is executed, the specified sound will begin. Whenever "SOUND OFF" is executed, it terminates the singing sound immediately.

There are two singing modes, SONE mode and SLOOP mode activated by SOUND ONE and SOUND LOOP. In SONE mode the specified sound plays just once. In SLOOP mode the specified sound keeps re-playing.

Since sounds 0~11 contain 32 notes and sounds 12~15 contain 64 notes the latter possesses better sound than the former.

The frequency of the sound effect circuit can be selected by mask option.

Frequency of sound effect circuit =  $\frac{\text{system clock}}{2^{\text{m}}}$

where m=0, 1, 2, 3, 4, 5

Holtek s sound library supports only sound clock frequencies of 128K or 64K. To use Holtek s sound library, the proper system clock and mask option should be selected.

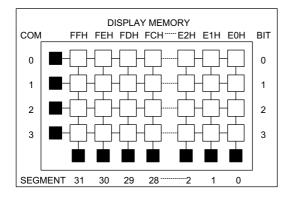

#### LCD display memory

As mentioned in the data memory section the LCD display memory is embedded in the data memory. It can be read and written to in the same way as normal data memory.

The figures show the mapping between the display memory and LCD pattern for the HT1130.

To turn the display on or off an 1/0 is written to the corresponding bit of the display memory.

The LCD display module may have any form as long as the number of commons does not exceed 4 and the number of segments does not exceed 32.

LCD display memory

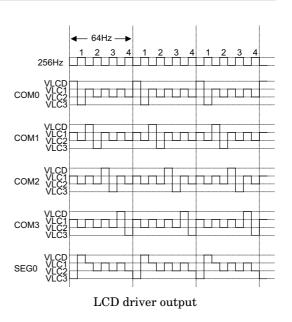

#### LCD driver output

All LCD segments are random after an initial clear. The bias voltage circuits of the LCD display is built-in and no external resistor is needed.

The output number of the HT1130 LCD driver is 32 4 which can directly drive an LCD with 1/4 (or 1/3 by mask option) duty cycle and 1/3 bias.

The frequency of the LCD driving clock is fixed at about 256Hz. This is set by Holtek according to the application and cannot be changed.

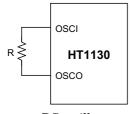

#### Oscillator

Only one external resistor is needed for the HT1130 oscillator circuit.

The system clock is also used as the reference signal of the LCD driving clock, sound effect clock and internal frequency source of the TIMER.

One HT1130 machine cycle consists of a sequence of four states numbered T1 to T4. Each state lasts for one oscillator period. The machine cycle is 4.0 s if the system frequency is up to 1.0MHz.

RC oscillator

#### Interfacing

The HT1130 microcontroller communicate with the outside world through three 4-bit input ports PP, PS and PM and one 4-bit output port PA.

#### Input ports - PP, PS, PM

All ports can have internal pull high resistors determined by mask option. Every bit of the input ports PP, PS and PM can be specified to be a trigger source to wake up the HALT interrupt by mask option. A high to low transition on one of these pins will wake up the device from a HALT status.

Input ports PP, PS, PM

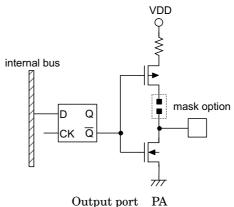

#### **Output port – PA**

A mask option is available to select whether the output is a CMOS or open drain NMOS type. After an initial clear the output port PA defaults to be high for CMOS or floating for NMOS.

#### Mask options

The following options are available by mask option which must be selected prior to manufacturing.

4-bit input ports PP, PS and PM with or without pull high resistors.

Each bit of PP, PS and PM can wake up the processor from a HALT state.

Output Port PA as CMOS or open drain NMOS.

8-bit programmable timer with external clock or internal frequency source. Thirteen internal frequency sources are available to provide an internal clock. Note that a value of n=6 cannot be used for the devices. If the internal frequency sources are used as a clocking signal then TMCLK cannot be connected to a pull-high resistor

Six kinds of sound clock frequency:  $f_{SYS}/2^{m}$ , m=0, 1, 2, 3, 4, 5

Two kinds of LCD applications: 1/4 duty 1/3 bias or 1/3 duty 1/3 bias

#### Software Tools

To make the programming task easier and to reduce development time Holtek supplies a development system for the HT1130. The system runs under an IBM PC-XT/AT environment and consists of both a hardware emulation board and a suite of programs including powerful debug functions. The user can download the code from the PC to the emulation board for verification. The main features of the system are as follows.

Can incorporate the user s text editor or word processor with Holtek s cross assembler to form an integrated development system

Supports mouse functions with its window based human interface

Performs stand-alone operation for demonstration purposes

Auto-executes self test function at every power on reset

Provides symbolic debugging capabilities

User defined mask options

RC with variable resistor

Displays and modifies registers, carry flag, timer, port output level and internal RAM

Single instruction stepping

Jumps unconditionally to any address and halts anytime during execution

Provides up to 8 breakpoint settings

Real time 255 forward step or 256 backward step trace  $% \left( {{{\mathbf{x}}_{\mathbf{x}}} \right)$

After program verification on the emulation board the customer supplies Holtek with the verified code prior to manufacturing.

## **Application Circuits**

Notes: R\*: Depends on the required system clock frequency (R=36k ~620k , at VDD=3V). \*\*: Timer clock may come from an external or internal frequency source.

## **Instruction Set Summary**

| Mnemonic                                                                                                                                         | Description                                                                                                                                                                                                                                                                                               | Byte                                                                                                    | Cycle                                                                                                   | CF |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----|

| Arithmetic                                                                                                                                       |                                                                                                                                                                                                                                                                                                           |                                                                                                         |                                                                                                         |    |

| ADD A,[R1R0]<br>ADC A,[R1R0]<br>SUB A,[R1R0]<br>SBC A,[R1R0]<br>ADD A,XH<br>SUB A,XH<br>DAA                                                      | Add data memory to ACC<br>Add data memory with carry to ACC<br>Subtract data memory from ACC<br>Subtract data memory from ACC with borrow<br>Add immediate data to ACC<br>Subtract immediate data from ACC<br>Decimal adjust ACC for addition                                                             | $     \begin{array}{c}       1 \\       1 \\       1 \\       2 \\       2 \\       1     \end{array} $ | $     \begin{array}{c}       1 \\       1 \\       1 \\       2 \\       2 \\       1     \end{array} $ |    |

| Logic Operation                                                                                                                                  |                                                                                                                                                                                                                                                                                                           |                                                                                                         |                                                                                                         |    |

| AND A,[R1R0]<br>OR A,[R1R0]<br>XOR A,[R1R0]<br>AND [R1R0],A<br>OR [R1R0],A<br>XOR [R1R0],A<br>XOR [R1R0],A<br>AND A,XH<br>OR A,XH<br>XOR A,XH    | AND data memory to ACC<br>OR data memory to ACC<br>Exclusive-OR data memory to ACC<br>AND ACC to data memory<br>OR ACC to data memory<br>Exclusive-OR ACC to data memory<br>AND immediate data to ACC<br>OR immediate data to ACC<br>Exclusive-OR immediate data to ACC                                   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                  | $ \begin{array}{c} 1\\ 1\\ 1\\ 1\\ 1\\ 2\\ 2\\ 2\\ 2 \end{array} $                                      |    |

| Increment and<br>Decrement                                                                                                                       |                                                                                                                                                                                                                                                                                                           |                                                                                                         |                                                                                                         |    |

| INC A<br>INC Rn<br>INC [R1R0]<br>INC [R3R2]<br>DEC A<br>DEC Rn<br>DEC [R1R0]<br>DEC [R3R2]                                                       | Increment ACC<br>Increment register, n=0~4<br>Increment data memory<br>Increment data memory<br>Decrement ACC<br>Decrement register, n=0~4<br>Decrement data memory<br>Decrement data memory                                                                                                              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                          | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                                    |    |

| Data Move                                                                                                                                        |                                                                                                                                                                                                                                                                                                           |                                                                                                         |                                                                                                         |    |

| MOV A,Rn<br>MOV Rn,A<br>MOV A,[R1R0]<br>MOV A,[R3R2]<br>MOV [R1R0],A<br>MOV [R3R2],A<br>MOV A,XH<br>MOV R1R0,XXH<br>MOV R3R2,XXH<br>MOV R3R2,XXH | Move register to ACC, n=0~4<br>Move ACC to register, n=0~4<br>Move data memory to ACC<br>Move data memory to ACC<br>Move ACC to data memory<br>Move ACC to data memory<br>Move immediate data to ACC<br>Move immediate data to R1 and R0<br>Move immediate data to R3 and R2<br>Move immediate data to R4 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                  | $ \begin{array}{c} 1\\ 1\\ 1\\ 1\\ 1\\ 1\\ 2\\ 2\\ 2\\ 2 \end{array} $                                  |    |

| Mnemonic         | Description                            | Byte | Cycle | CF |

|------------------|----------------------------------------|------|-------|----|

| Rotate           |                                        |      |       |    |

| RL A             | Rotate ACC left                        | 1    | 1     |    |

| RLC A            | Rotate ACC left through the carry      | 1    | 1     |    |

| RR A             | Rotate ACC right                       | 1    | 1     |    |

| RRC A            | Rotate ACC right through the carry     | 1    | 1     |    |

| Input and Output |                                        |      |       |    |

| IN A,Pi          | Input port-i to ACC, port-i=PM, PS, PP | 1    | 1     |    |

| OUT PA,A         | Output ACC to port-A                   | 1    | 1     |    |

| Branch           |                                        |      |       |    |

| JMP addr         | Jump unconditionally                   | 2    | 2     |    |

| JC addr          | Jump on carry=1                        | 2    | 2     |    |

| JNC addr         | Jump on carry=0                        | 2    | 2     |    |

| JTMR addr        | Jump on timer overflow                 | 2    | 2     |    |

| JAn addr         | Jump on ACC bit n=1                    | 2    | 2     |    |

| JZ A,addr        | Jump on ACC is zero                    | 2    | 2     |    |

| JNZ A,addr       | Jump on ACC is not zero                | 2    | 2     |    |

| JNZ Rn,addr      | Jump on register Rn not zero, n=0,1,4  | 2    | 2     |    |

| Subroutine       |                                        |      |       |    |

| CALL addr        | Subroutine call                        | 2    | 2     |    |

| RET              | Return from subroutine or interrupt    | 1    | 1     |    |

| RETI             | Return from interrupt service routine  | 1    | 1     |    |

| Flag             |                                        |      |       |    |

| CLC              | Clear carry flag                       | 1    | 1     | 0  |

| STC              | Set carry flag                         | 1    | 1     | 1  |

| EI               | Enable interrupt                       | 1    | 1     |    |

| DI               | Disable interrupt                      | 1    | 1     |    |

| NOP              | No operation                           | 1    | 1     |    |

| Timer            |                                        |      |       |    |

| TIMER XXH        | Set 8 bits immediate data to TIMER     | 2    | 2     |    |

| TIMER ON         | Set TIMER start counting               | 1    | 1     |    |

| TIMER OFF        | Set TIMER stop counting                | 1    | 1     |    |

| MOV A,TMRL       | Move low nibble of TIMER to ACC        | 1    | 1     |    |

| MOV A,TMRH       | Move high nibble of TIMER to ACC       | 1    | 1     |    |

| MOV TMRL,A       | Move ACC to low nibble of TIMER        | 1    | 1     |    |

| MOV TMRH,A       | Move ACC to hight nibble of TIMER      | 1    | 1     |    |

| Mnemonic                                                   | Description                                                                                                                                                                       | Byte                         | Cycle                        | CF |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|----|

| Table Read                                                 |                                                                                                                                                                                   |                              |                              |    |

| READ R4A<br>READ MR0A<br>READF R4A<br>READF MR0A           | Read ROM code of current page to R4 and ACC<br>Read ROM code of current page to M(R1,R0), ACC<br>Read ROM code of page F to R4 and ACC<br>Read ROM code of page F to M(R1,R0),ACC | 1<br>1<br>1<br>1             | 2<br>2<br>2<br>2             |    |

| Sound Control                                              |                                                                                                                                                                                   |                              |                              |    |

| SOUND n<br>SOUND A<br>SOUND ONE<br>SOUND LOOP<br>SOUND OFF | Activate SOUND channel n<br>Activate SOUND channel with ACC<br>Turn on SOUND one cycle<br>Turn on SOUND repeat cycle<br>Turn off SOUND                                            | $2 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1$ | $2 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1$ |    |

| Miscellaneous                                              |                                                                                                                                                                                   |                              |                              |    |

| HALT                                                       | Enter power down mode                                                                                                                                                             | 2                            | 2                            |    |

### **Instruction Definitions**

| ADC A,[R1R0] | Add data memory contents and carry to the accumulator                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Machine code | 00001000                                                                                                                              |

| Description  | The contents of the data memory addressed by the register pair "R1,R0" and the carry are added to the accumulator. Carry is affected. |

| Operation    | ACC ACC+M(R1,R0)+CF                                                                                                                   |

| ADD A,XH     | Add immediate data to the accumulator                                                                                                 |

| Machine code | 0100000 0000dddd                                                                                                                      |

| Description  | The specified data is added to the accumulator. Carry is affected.                                                                    |

| Operation    | ACC ACC+XH                                                                                                                            |

| ADD A,[R1R0] | Add data memory contents to the accumulator                                                                                           |

| Machine code | $0\ 0\ 0\ 0\ 1\ 0\ 0\ 1$                                                                                                              |

| Description  | The contents of the data memory addressed by the register pair "R1,R0" is added to the accumulator. Carry is affected.                |

| Operation    | ACC ACC+M(R1,R0)                                                                                                                      |

| AND A,XH     | Logical AND immediate data to accumulator                                                                                             |

| Machine code | 0100010 0000dddd                                                                                                                      |

| Description  | Data in the accumulator is logical AND with the immediate data speci-<br>fied by the code.                                            |

| Operation    | ACC ACC "AND" XH                                                                                                                      |

| AND A,[R1R0] | Logical AND accumulator with data memory                                                                                              |

| Machine code | 0 0 0 1 1 0 1 0                                                                                                                       |

| Description  | Data in the accumulator is logical AND with the data memory addressed<br>by the register pair "R1,R0" Operation                       |

|              | ACC ACC "AND" M(R1,R0)                                                                                                                |

| AND [R1R0],A | Logical AND data memory with accumulator                                                                                              |

| Machine code | 0 0 0 1 1 1 0 1                                                                                                                       |

| Description  | Data in the data memory addressed by the register pair "R1,R0" is logical AND with the accumulator                                    |

| Operation    | M(R1,R0) M(R1,R0) "AND" ACC                                                                                                           |

| CALL address | Subroutine call                                                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Machine code | 1111aaaa aaaaaaaa                                                                                                                             |

| Description  | The program counter bits $0\sim11$ are saved in the stack and the specified address loaded into the program counter.                          |

| Operation    | Stack PC+2<br>PC address                                                                                                                      |

| CLC          | Clear carry flag                                                                                                                              |

| Machine code | 00101010                                                                                                                                      |

| Description  | The carry flag is reset to zero.                                                                                                              |

| Operation    | CF 0                                                                                                                                          |

| DAA          | Decimal-Adjust accumulator                                                                                                                    |

| Machine code | 00110110                                                                                                                                      |

| Description  | The accumulator value is adjusted to BCD (Binary Code Decimal), if the contents of the accumulator is greater than 9 or CF (Carry flag) is 1. |

| Operation    | If ACC>9 or CF=1 then<br>ACC ACC+6, CF 1<br>else<br>ACC ACC, CF CF                                                                            |

| DEC A        | Decrement accumulator                                                                                                                         |

| Machine code | 00111111                                                                                                                                      |

| Description  | Data in the accumulator is decremented by 1. Carry flag is not affected.                                                                      |

| Operation    | ACC ACC 1                                                                                                                                     |

| DEC Rn       | Decrement register                                                                                                                            |

| Machine code | 0 0 0 1 n n n 1                                                                                                                               |

| Description  | Data in the working register "Rn" is decremented by 1. Carry flag is not affected.                                                            |

| Operation    | Rn Rn 1; Rn=R0,R1,R2,R3, R4, for n=0, 1, 2, 3, 4                                                                                              |

| DEC [R1R0]   | Decrement data memory                                                                                                                         |

| Machine code | 0 0 0 0 1 1 0 1                                                                                                                               |

| Description  | Data in the data memory specified by the register pair "R1,R0" is decre-<br>mented by 1. Carry flag is not affected.                          |

| Operation    | M(R1,R0) M(R1,R0) 1                                                                                                                           |

| DEC [R3R2]                                                                                              | Decrement data memory                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Machine code<br>Description                                                                             | 0 0 0 0 1 1 1 1<br>Data in the data memory specified by the register pair "R3,R2" is decre-                                                                                                                                                                                                                                                                    |

| Description                                                                                             | mented by 1. Carry flag is not affected.                                                                                                                                                                                                                                                                                                                       |

| Operation                                                                                               | M(R3,R2) $M(R3,R2)$ 1                                                                                                                                                                                                                                                                                                                                          |

| DI                                                                                                      | Disable interrupt                                                                                                                                                                                                                                                                                                                                              |

| Machine code                                                                                            | 00101101                                                                                                                                                                                                                                                                                                                                                       |

| Description                                                                                             | Internal time-out interrupt and external interrupt are disabled.                                                                                                                                                                                                                                                                                               |

| EI                                                                                                      | Enable interrupt                                                                                                                                                                                                                                                                                                                                               |

| Machine code                                                                                            | 0 0 1 0 1 1 0 0                                                                                                                                                                                                                                                                                                                                                |

| Description                                                                                             | Internal time-out interrupt and external interrupt are enabled.                                                                                                                                                                                                                                                                                                |

| HALT                                                                                                    | Halt system clock                                                                                                                                                                                                                                                                                                                                              |

| Machine code                                                                                            | $0 \ 0 \ 1 \ 1 \ 0 \ 1 \ 1 \ 1 \ 1 \ 0 \ 0$                                                                                                                                                                                                                                                                                                                    |

| Description                                                                                             | Turn off system clock, and enter power down mode.                                                                                                                                                                                                                                                                                                              |

| Operation                                                                                               | PC PC+2                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |

| IN A,Pi                                                                                                 | Input port to accumulator                                                                                                                                                                                                                                                                                                                                      |

| IN A,Pi<br>Machine code                                                                                 | Input port to accumulator<br>PM 00110010                                                                                                                                                                                                                                                                                                                       |

|                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                         | PM 00110010                                                                                                                                                                                                                                                                                                                                                    |

| Machine code Description                                                                                | PM       00110010         PS       00110011         PP       00110100         The data on port "Pi" is transferred to the accumulator.                                                                                                                                                                                                                         |

| Machine code                                                                                            | PM       00110010         PS       00110011         PP       00110100                                                                                                                                                                                                                                                                                          |

| Machine code Description                                                                                | PM       00110010         PS       00110011         PP       00110100         The data on port "Pi" is transferred to the accumulator.                                                                                                                                                                                                                         |

| Machine code<br>Description<br>Operation                                                                | PM00110010PS00110011PP00110100The data on port "Pi" is transferred to the accumulator.ACCPi; Pi=PM, PS or PP                                                                                                                                                                                                                                                   |

| Machine code<br>Description<br>Operation<br>INC A                                                       | PM00110010PS00110011PP00110100The data on port "Pi" is transferred to the accumulator.ACCPi; Pi=PM, PS or PPIncrement accumulator                                                                                                                                                                                                                              |

| Machine code<br>Description<br>Operation<br>INC A<br>Machine code                                       | PM00110010PS00110011PP00110100The data on port "Pi" is transferred to the accumulator.ACCPi; Pi=PM, PS or PPIncrement accumulator00110001                                                                                                                                                                                                                      |

| Machine code<br>Description<br>Operation<br>INC A<br>Machine code<br>Description                        | PM00110010PS00110011PP00110100The data on port "Pi" is transferred to the accumulator.ACCPi; Pi=PM, PS or PPIncrement accumulator00110001Data in the accumulator is incremented by 1. Carry flag is not affected.                                                                                                                                              |

| Machine code<br>Description<br>Operation<br>INC A<br>Machine code<br>Description<br>Operation           | <ul> <li>PM 00110010</li> <li>PS 00110011</li> <li>PP 00110100</li> <li>The data on port "Pi" is transferred to the accumulator.</li> <li>ACC Pi; Pi=PM, PS or PP</li> <li>Increment accumulator</li> <li>00110001</li> <li>Data in the accumulator is incremented by 1. Carry flag is not affected.</li> <li>ACC ACC+1</li> </ul>                             |

| Machine code<br>Description<br>Operation<br>INC A<br>Machine code<br>Description<br>Operation<br>INC Rn | <ul> <li>PM 00110010</li> <li>PS 00110011</li> <li>PP 00110100</li> <li>The data on port "Pi" is transferred to the accumulator.</li> <li>ACC Pi; Pi=PM, PS or PP</li> <li>Increment accumulator</li> <li>00110001</li> <li>Data in the accumulator is incremented by 1. Carry flag is not affected.</li> <li>ACC ACC+1</li> <li>Increment register</li> </ul> |

21

| INC [R1R0]   | Increment data memory                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Machine code | 00001100                                                                                                                                                                 |

| Description  | Data in the data memory specified by the register pair "R1,R0" is incre-<br>mented by 1. Carry flag is not affected.                                                     |

| Operation    | M(R1,R0) $M(R1,R0)+1$                                                                                                                                                    |

| INC [R3R2]   | Increment data memory                                                                                                                                                    |

| Machine code | 0 0 0 0 1 1 1 0                                                                                                                                                          |

| Description  | Data memory specified by the register pair "R3,R2" is incremented by 1.<br>Carry flag is not affected.                                                                   |

| Operation    | M(R3,R2) $M(R3,R2)+1$                                                                                                                                                    |

| JAn address  | Jump if accumulator bit n is set                                                                                                                                         |

| Machine code | 100nnaaa aaaaaaaa                                                                                                                                                        |

| Description  | Bits 0~10 of the program counter are replaced with the directly-specified address but bit 11 of the program counter is unaffected, if accumulator bit n is set to 1.     |

| Operation    | $ \begin{array}{ll} PC \ (bit \ 0{\sim}10) & address, \ if \ ACC \ bit \ n{=}1(n{=}0{\sim}3) \\ PC & PC{+}2, \ if \ ACC \ bit \ n{=}0 \end{array} $                      |

| JC address   | Jump if carry is set                                                                                                                                                     |

| Machine code | 11000aaa aaaaaaaa                                                                                                                                                        |

| Description  | Bits $0~10$ of the program counter are replaced with the directly-specified address but bit 11 of the program counter is unaffected, if the CF (Carry flag) is set to 1. |

| Operation    | PC (bit 0~10) address, if CF=1<br>PC PC+2, if CF=0                                                                                                                       |

| JMP address  | Direct jump                                                                                                                                                              |

| Machine code | 1110aaaa aaaaaaaa                                                                                                                                                        |

| Description  | Bits $0 \sim 11$ of the program counter are replaced with the directly-specified address.                                                                                |

| Operation    | PC address                                                                                                                                                               |

| JNC address  | Jump if carry is not set                                                                                                                                                 |

| Machine code | 11001aaa aaaaaaaa                                                                                                                                                        |

| Description  | Bits $0~10$ of the program counter are replaced with the directly-specified address and bit 11 of the program counter is unaffected, if the CF (Carry flag) is set to 0. |

| Operation    | $ \begin{array}{ll} PC \ (bit \ 0{\sim}10) & address, \ if \ CF=0 \\ PC & PC+2, \ if \ CF=1 \end{array} $                                                                |

22

| JNZ A,address  | Jump if accumulator is not 0                                                                                                                                           |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Machine code   | 10111aaa aaaaaaaa                                                                                                                                                      |

| Description    | Bits $0 \sim 10$ of the program counter are replaced with the directly-specified address but bit 11 of the program counter is unaffected, if the accumulator is not 0. |

| Operation      | PC (bit 0~10) address, if ACC 0<br>PC PC+2, if ACC=0                                                                                                                   |

| JNZ Rn,address | Jump if register is not 0                                                                                                                                              |

| Machine code   | RO 10100aaa aaaaaaaa                                                                                                                                                   |

|                | R1 10101aaa aaaaaaaa                                                                                                                                                   |

|                | R4 11011aaa aaaaaaaa                                                                                                                                                   |

| Description    | Bits 0~10 of the program counter are replaced with the directly-specified address but bit 11 of the program counter is unaffected, if the register is not 0.           |

| Operation      | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                  |

| JTMR address   | Jump if time-out                                                                                                                                                       |

| Machine code   | 11010aaa aaaaaaaa                                                                                                                                                      |

| Description    | Bits 0~10 of the program counter are replaced with the directly-specified address but bit 11 of the program counter is unaffected, if the TF (Timer flag) is set to 1. |

| Operation      | $ \begin{array}{ll} PC \ (bit \ 0 {\sim} 10) & address, \ if \ TF=1 \\ PC & PC+2, \ if \ TF=0 \end{array} $                                                            |

| JZ A,address   | Jump if accumulator is 0                                                                                                                                               |

| Machine code   | 10110aaa aaaaaaaa                                                                                                                                                      |

| Description    | Bits $0 \sim 10$ of the program counter are replaced with the directly-specified address but bit 11 of the program counter is unaffected, if the accumulator is 0.     |

| Operation      | PC (bit 0~10) address, if ACC=0<br>PC PC+2, if ACC 0                                                                                                                   |

| MOV A,Rn       | Move register to accumulator                                                                                                                                           |

| Machine code   | 0 0 1 0 n n n 1                                                                                                                                                        |

| Description    | Data in the working register "Rn" is moved to the accumulator.                                                                                                         |

| Operation      | ACC Rn; Rn=R0~R4, for n= $0~4$                                                                                                                                         |

| MOV A,TMRH<br>Machine code<br>Description<br>Operation                                                      | Move timer high nibble to accumulator<br>0 0 1 1 1 0 1 1<br>The high nibble data of the timer counter is loaded to the accumulator.<br>ACC TIMER (high nibble)                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV A,TMRL<br>Machine code<br>Description<br>Operation                                                      | Move timer low nibble to accumulator<br>0 0 1 1 1 0 1 0<br>The low nibble data of the timer counter is loaded to the accumulator.<br>ACC TIMER (low nibble)                                                                                                                                                                                                                                                            |

| MOV A,XH<br>Machine code<br>Description<br>Operation                                                        | Move immediate data to accumulator<br>0 1 1 1 d d d d<br>The 4-bit data specified by the code is loaded to the accumulator.<br>ACC XH                                                                                                                                                                                                                                                                                  |

| MOV A,[R1R0]<br>Machine code<br>Description<br>Operation                                                    | Move data memory to accumulator<br>0 0 0 0 0 1 0 0<br>Data in the data memory specified by the register pair "R1,R0" is moved<br>to the accumulator.<br>ACC M(R1,R0)                                                                                                                                                                                                                                                   |

|                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MOV A,[R3R2]<br>Machine code<br>Description                                                                 | Move data memory to accumulator<br>0 0 0 0 0 1 1 0<br>Data in the data memory specified by the register pair "R3,R2" is moved<br>to the accumulator.                                                                                                                                                                                                                                                                   |

| Machine code                                                                                                | 0 0 0 0 0 1 1 0<br>Data in the data memory specified by the register pair "R3,R2" is moved                                                                                                                                                                                                                                                                                                                             |

| Machine code<br>Description<br>Operation<br><b>MOV R1R0,XXH</b><br>Machine code                             | 0 0 0 0 0 1 1 0<br>Data in the data memory specified by the register pair "R3,R2" is moved<br>to the accumulator.<br>ACC M(R3,R2)<br>Move immediate data to R1 and R0<br>0 1 0 1 d d d 0 0 0 0 d d d d<br>The 8-bit data specified by the code is loaded to the working registers R1<br>and R0, the high nibble of the data is loaded to R1, and the low nibble to                                                     |