FUJITSU SEMICONDUCTOR

DATA SHEET

DS05-11046-1E

MEMORY cmos

# 4 × 4 M × 4 BIT SYNCHRONOUS DYNAMIC RAM

MB81F64442C-102/-103/-102L/-103L

### CMOS 4-Bank × 4,194,304-Word × 4 Bit Synchronous Dynamic Random Access Memory

### **■** DESCRIPTION

The Fujitsu MB81F64442C is a CMOS Synchronous Dynamic Random Access Memory (SDRAM) containing 67,108,864 memory cells accessible in a 4-bit format. The MB81F64442C features a fully synchronous operation referenced to a positive edge clock whereby all operations are synchronized at a clock input which enables high performance and simple user interface coexistence. The MB81F64442C SDRAM is designed to reduce the complexity of using a standard dynamic RAM (DRAM) which requires many control signal timing constraints, and may improve data bandwidth of memory as much as 5 times more than a standard DRAM.

The MB81F64442C is ideally suited for workstations, personal computers, laser printers, high resolution graphic adapters/accelerators and other applications where an extremely large memory and bandwidth are required and where a simple interface is needed.

#### **■ PRODUCT LINE & FEATURES**

| Parameter                          |           | MB81F64442C |                            |                    |  |  |  |  |  |  |

|------------------------------------|-----------|-------------|----------------------------|--------------------|--|--|--|--|--|--|

| Faranietei                         | -102      | -102L       | -103                       | -103L              |  |  |  |  |  |  |

| CL - tRCD - tRP                    | 2 - 2 - 2 | clk min.    | 3 - 2 - 2                  | 3 - 2 - 2 clk min. |  |  |  |  |  |  |

| Clock Frequency                    | 100 MI    | Hz max.     | 100 MHz max.               |                    |  |  |  |  |  |  |

| Burst Mode Cycle Time              | 10 ns     | s min.      | 10 ns                      | s min.             |  |  |  |  |  |  |

| Access Time From Clock (CL = 3)    | 6 ns      | max.        | 6 ns max.                  |                    |  |  |  |  |  |  |

| Operating Current (2 banks active) | 105 m     | A max.      | 105 m                      | A max.             |  |  |  |  |  |  |

| Power Down Mode Current (Icc2P)    | 2 mA max. | 1 mA max.   | 2 mA max. 1 mA ma          |                    |  |  |  |  |  |  |

| Self Refresh Current (Icce)        | 1 mA max. | 500 μA max. | nax. 1 mA max. 500 μA max. |                    |  |  |  |  |  |  |

- Single +3.3 V Supply ±0.3 V tolerance

- LVTTL compatible I/O

- 4 K refresh cycles every 65.6 ms

- Four bank operation

- Burst read/write operation and burst read/single write operation capability

- Standard and low power versions

- Programmable burst type, burst length, and CAS latency

- Auto-and Self-refresh (every 16 μs)

- CKE power down mode

- · Output Enable and Input Data Mask

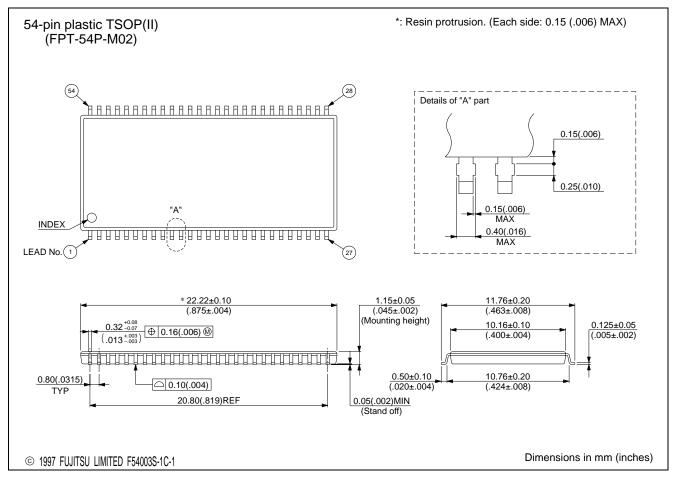

### **■ PACKAGE**

### **Package and Ordering Information**

54-pin plastic (400 mil) TSOP-II, order as MB81F64442C-xxxFN (Std power), MB81F64442C-xxxLFN (Low power), MB81F64442C-xxxEFN (Extra power)

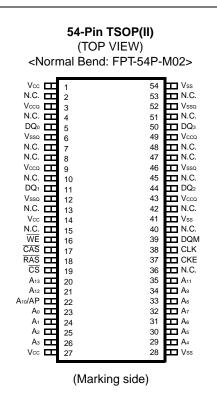

### **■ PIN ASSIGNMENTS AND DESCRIPTIONS**

| Pin Number                                                | Symbol                                                                 | Function                                                                                           |

|-----------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1, 3, 9, 14, 27, 43, 49                                   | Vcc, Vccq                                                              | Supply Voltage                                                                                     |

| 5, 11, 44, 50                                             | DQ₀ to DQ₃                                                             | Data I/O                                                                                           |

| 6, 12, 28, 41, 46, 52, 54                                 | Vss, Vssq *                                                            | Ground                                                                                             |

| 2, 4, 7, 8, 10, 13, 15, 36, 40, 42, 45, 47,<br>48, 51, 53 | N.C.                                                                   | No Connection                                                                                      |

| 16                                                        | WE                                                                     | Write Enable                                                                                       |

| 17                                                        | CAS                                                                    | Column Address Strobe                                                                              |

| 18                                                        | RAS                                                                    | Row Address Strobe                                                                                 |

| 19                                                        | <u>CS</u>                                                              | Chip Select                                                                                        |

| 20, 21                                                    | A <sub>13</sub> (BA <sub>0</sub> ), A <sub>12</sub> (BA <sub>1</sub> ) | Bank Select (Bank Address)                                                                         |

| 22                                                        | AP                                                                     | Auto Precharge Enable                                                                              |

| 22, 23, 24, 25, 26, 29, 30, 31, 32, 33, 34, 35            | A <sub>0</sub> to A <sub>11</sub>                                      | Address Input  • Row: A <sub>0</sub> to A <sub>11</sub> • Column: A <sub>0</sub> to A <sub>9</sub> |

| 37                                                        | CKE                                                                    | Clock Enable                                                                                       |

| 38                                                        | CLK                                                                    | Clock Input                                                                                        |

| 39                                                        | DQM                                                                    | Input Mask/Output Enable                                                                           |

<sup>\*:</sup> These pins are connected internally in the chip.

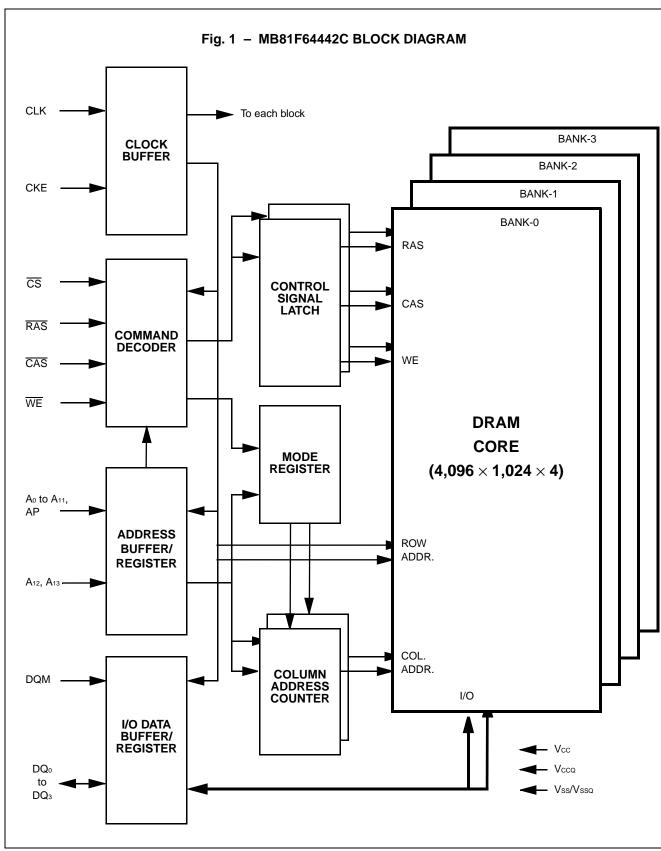

### **■ BLOCK DIAGRAM**

### **■ FUNCTIONAL TRUTH TABLE** Note 1

### COMMAND TRUTH TABLE Notes 2, 3, and 4

| Function                  | Notes | Symbol   | CI  | <b>KE</b> | CS | RAS | CAS | WE  | A <sub>13</sub> , | <b>A</b> 10 | <b>A</b> 11 | A <sub>9</sub> to |

|---------------------------|-------|----------|-----|-----------|----|-----|-----|-----|-------------------|-------------|-------------|-------------------|

| Function                  | NOIES | Syllibol | n-1 | n         | CS | KAS | CAS | VVE | (BA)              | (AP)        | <b>A</b> 11 | Ao                |

| Device Deselect           | *5    | DESL     | Н   | Х         | Н  | Х   | Х   | Х   | Х                 | Х           | Х           | Х                 |

| No Operation              | *5    | NOP      | Н   | Х         | L  | Н   | Н   | Н   | Х                 | Х           | Х           | Х                 |

| Burst Stop                |       | BST      | Н   | Х         | L  | Н   | Н   | L   | Х                 | Х           | Χ           | Х                 |

| Read                      | *6    | READ     | Н   | Х         | L  | Н   | L   | Н   | V                 | L           | Χ           | V                 |

| Read with Auto-precharge  | *6    | READA    | Н   | Х         | L  | Н   | L   | Н   | V                 | Н           | Χ           | V                 |

| Write                     | *6    | WRIT     | Н   | Х         | L  | Н   | L   | L   | V                 | L           | Χ           | V                 |

| Write with Auto-precharge | *6    | WRITA    | Н   | Х         | L  | Н   | L   | L   | V                 | Н           | Χ           | V                 |

| Bank Active (RAS)         | *7    | ACTV     | Н   | Х         | L  | L   | Н   | Н   | V                 | V           | V           | V                 |

| Precharge Single Bank     |       | PRE      | Н   | Х         | L  | L   | Н   | L   | V                 | L           | Χ           | Х                 |

| Precharge All Banks       |       | PALL     | Н   | Х         | L  | L   | Н   | L   | Х                 | Н           | Х           | Х                 |

| Mode Register Set         | *8, 9 | MRS      | Н   | Χ         | L  | L   | L   | L   | Х                 | Х           | Х           | V                 |

**Notes:** \*1. V = Valid, L = Logic Low, H = Logic High, X = either L or H.

- \*2. All commands assumes no CSUS command on previous rising edge of clock.

- \*3. All commands are assumed to be valid state transitions.

- \*4. All inputs are latched on the rising edge of clock.

- \*5. NOP and DESL commands have the same effect on the part.

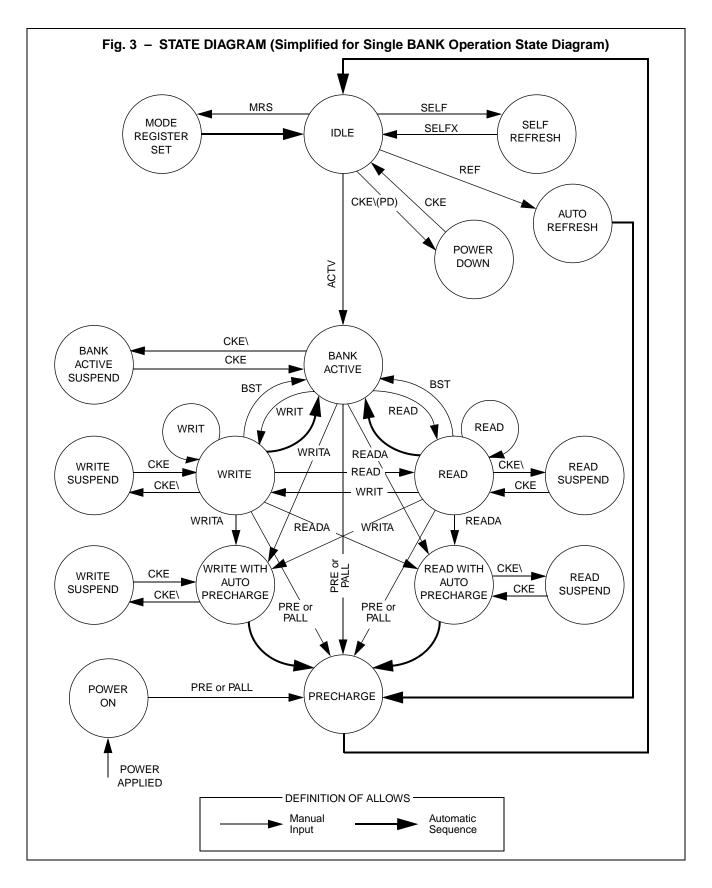

- \*6. READ, READA, WRIT and WRITA commands should only be issued after the corresponding bank has been activated (ACTV command). Refer to STATE DIAGRAM.

- \*7. ACTV command should only be issued after corresponding bank has been precharged (PRE or PALL command).

- \*8. Required after power up.

- \*9. MRS command should only be issued after all banks have been precharged (PRE or PALL command). Refer to STATE\_DIAGRAM.

### **DQM TRUTH TABLE**

| Function                 | Command | Cł  | DQM |     |

|--------------------------|---------|-----|-----|-----|

| Function                 | Command | n-1 | n   | DQW |

| Data Write/Output Enable | ENBL    | Н   | Х   | L   |

| Data Mask/Output Disable | MASK    | Н   | Х   | Н   |

### **CKE TRUTH TABLE**

| Current              | Function 1               | Notes | Symbol | CI  | <b>KE</b> | CS | RAS | CAS | WE  | A <sub>13</sub> , | <b>A</b> 10 | <b>A</b> 11, |

|----------------------|--------------------------|-------|--------|-----|-----------|----|-----|-----|-----|-------------------|-------------|--------------|

| State                | Function 1               | votes | Symbol | n-1 | n         | CS | KAS | CAS | VVE | (BA)              | (AP)        | <b>A</b> 9-0 |

| Bank Active          | Clock Suspend Mode Entry | / *1  | CSUS   | Н   | L         | Х  | Х   | Х   | Х   | Х                 | Х           | Х            |

| Any<br>(Except Idle) | Clock Suspend Continue   | *1    |        | L   | L         | Х  | Х   | Х   | Х   | Х                 | Х           | Х            |

| Clock<br>Suspend     | Clock Suspend Mode Exit  |       |        | L   | Н         | Х  | Х   | Х   | Х   | Х                 | Х           | Х            |

| Idle                 | Auto-refresh Command     | *2    | REF    | Н   | Н         | L  | L   | L   | Н   | Х                 | Х           | Х            |

| Idle                 | Self-refresh Entry       | *2, 3 | SELF   | Н   | L         | L  | L   | L   | Н   | Х                 | Х           | Х            |

| Self Refresh         | Self-refresh Exit        | *4    | SELFX  | L   | Η         | L  | Н   | Н   | Н   | Х                 | Х           | Х            |

| Sell Reliesii        | Sell-reflesh Exit        | 4     | SELFA  | L   | Н         | Н  | Х   | Х   | Х   | Х                 | Х           | Х            |

| Idla                 | Dower Down Entry         | *2    | PD     | Н   | L         | L  | Н   | Н   | Н   | Х                 | Х           | Х            |

| Idle                 | Power Down Entry         | *3    | PD     | Н   | L         | Н  | Х   | Х   | Х   | Х                 | Х           | Х            |

| Power Down           | Power Down Exit          |       |        | L   | Н         | L  | Н   | Н   | Н   | Х                 | Х           | Х            |

| Power Down           | Power Down Exit          |       |        | L   | Н         | Н  | Х   | Х   | Χ   | Х                 | Х           | Х            |

Notes: \*1. The CSUS command requires that at least one bank is active. Refer to STATE DIAGRAM.

<sup>\*2.</sup> REF and SELF commands should only be issued after all banks have been precharged (PRE or PALL command). Refer to STATE DIAGRAM.

<sup>\*3.</sup> SELF and PD commands should only be issued after the last read data have been appeared on DQ.

<sup>\*4.</sup> CKE should be held high within tRC.

### **OPERATION COMMAND TABLE (Applicable to single bank)**

| Current<br>State | CS | RAS | CAS | WE | Addr       | Command    | Function Notes                                                     |

|------------------|----|-----|-----|----|------------|------------|--------------------------------------------------------------------|

| Idle             | Н  | Х   | Х   | Х  | Х          | DESL       | NOP                                                                |

|                  | L  | Н   | Н   | Н  | Х          | NOP        | NOP                                                                |

|                  | L  | Н   | Н   | L  | Х          | BST        | NOP                                                                |

|                  | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal *2                                                         |

|                  | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal *2                                                         |

|                  | L  | L   | Н   | Н  | BA, RA     | ACTV       | Bank Active                                                        |

|                  | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | NOP (PALL may affect other banks.)                                 |

|                  | L  | L   | L   | Н  | Х          | REF/SELF   | Auto-refresh or Self-refresh *3                                    |

|                  | L  | L   | L   | L  | MODE       | MRS        | Mode Register Set *3, 7 (Idle after trsc)                          |

| Bank Active      | Н  | Х   | Х   | Χ  | Х          | DESL       | NOP                                                                |

|                  | L  | Н   | Н   | Н  | Х          | NOP        | NOP                                                                |

|                  | L  | Н   | Н   | L  | Х          | BST        | NOP                                                                |

|                  | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Begin Read; Determine AP                                           |

|                  | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Begin Write; Determine AP                                          |

|                  | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal *2                                                         |

|                  | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | Precharge; Determine Precharge Type (PALL may affect other banks.) |

|                  | L  | L   | L   | Н  | Х          | REF/SELF   | Illegal                                                            |

|                  | L  | L   | L   | L  | MODE       | MRS        | Illegal                                                            |

| Current<br>State | CS | RAS | CAS | WE | Addr       | Command    | Function Notes                                                                             |  |  |

|------------------|----|-----|-----|----|------------|------------|--------------------------------------------------------------------------------------------|--|--|

| Read             | Н  | Х   | Х   | Х  | Х          | DESL       | NOP (Continue Burst to End → Bank Active)                                                  |  |  |

|                  | L  | Н   | Н   | Н  | Х          | NOP        | NOP (Continue Burst to End → Bank Active)                                                  |  |  |

|                  | L  | Н   | Н   | L  | Х          | BST        | Burst Stop → Bank Active                                                                   |  |  |

|                  | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Terminate Burst, New Read;<br>Determine AP                                                 |  |  |

|                  | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Terminate Burst, Start Write; Determine AP  *4                                             |  |  |

|                  | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal *2                                                                                 |  |  |

|                  | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | Terminate Burst, Precharge → Idle;<br>Determine Precharge Type                             |  |  |

|                  | L  | L   | Г   | Н  | X          | REF/SELF   | Illegal                                                                                    |  |  |

|                  | L  | L   | Г   | L  | MODE       | MRS        | Illegal                                                                                    |  |  |

| Write            | Н  | Х   | Х   | Х  | Х          | DESL       | NOP (Continue Burst to End → Bank Active)                                                  |  |  |

|                  | L  | Н   | Н   | Н  | Х          | NOP        | NOP (Continue Burst to End → Bank Active)                                                  |  |  |

|                  | L  | Н   | Н   | L  | Х          | BST        | Burst Stop → Bank Active                                                                   |  |  |

|                  | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Terminate Burst, Start Read;<br>Determine AP                                               |  |  |

|                  | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Terminate Burst, New Write;<br>Determine AP                                                |  |  |

|                  | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal *2                                                                                 |  |  |

|                  | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | Terminate Burst, Precharge → Idle; Determine Precharge Type (PALL may affect other banks.) |  |  |

|                  | L  | L   | L   | Н  | X REF/SELF |            | Illegal                                                                                    |  |  |

|                  | L  | L   | L   | L  | MODE       | MRS        | Illegal                                                                                    |  |  |

| Current<br>State                 | CS | RAS | CAS | WE | Addr       | Command    | Function Notes                                                         |

|----------------------------------|----|-----|-----|----|------------|------------|------------------------------------------------------------------------|

| Read with<br>Auto-               | Н  | Х   | Х   | Х  | Х          | DESL       | NOP (Continue Burst to End $\rightarrow$ Precharge $\rightarrow$ Idle) |

| precharge                        | L  | Н   | Н   | Н  | Х          | NOP        | NOP (Continue Burst to End $\rightarrow$ Precharge $\rightarrow$ Idle) |

|                                  | L  | Н   | Н   | L  | Х          | BST        | Illegal                                                                |

|                                  | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal                                                                |

|                                  | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal                                                                |

|                                  | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal *2                                                             |

|                                  | L  | L   | Н   | L  | ВА         | PRE        | Illegal *2                                                             |

|                                  | L  | L   | Н   | L  | AP         | PALL       | Illegal                                                                |

|                                  | L  | L   | L   | Н  | Х          | REF/SELF   | Illegal                                                                |

|                                  | L  | L   | L   | L  | MODE       | MRS        | Illegal                                                                |

| Write with<br>Auto-<br>precharge | Н  | Х   | Х   | Х  | Х          | DESL       | NOP (Continue Burst to End $\rightarrow$ Precharge $\rightarrow$ Idle) |

| precharge                        | L  | Н   | Н   | Н  | Х          | NOP        | NOP (Continue Burst to End $\rightarrow$ Precharge $\rightarrow$ Idle) |

|                                  | L  | Н   | Н   | L  | Х          | BST        | Illegal                                                                |

|                                  | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal                                                                |

|                                  | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal                                                                |

|                                  | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal *2                                                             |

|                                  | L  | L   | Н   | L  | ВА         | PRE        | Illegal *2                                                             |

|                                  | L  | L   | Н   | L  | AP         | PALL       | Illegal                                                                |

|                                  | L  | L   | L   | Н  | Х          | REF/SELF   | Illegal                                                                |

|                                  | L  | L   | L   | L  | MODE       | MRS        | Illegal                                                                |

| Current<br>State   | CS | RAS | CAS | WE | Addr       | Command    | Function                         | Notes |

|--------------------|----|-----|-----|----|------------|------------|----------------------------------|-------|

| Precharge          | Н  | Х   | Х   | Х  | Х          | DESL       | NOP (Idle after trp)             |       |

|                    | L  | Н   | Н   | Н  | Х          | NOP        | NOP (Idle after trp)             |       |

|                    | L  | Н   | Н   | L  | Х          | BST        | NOP (Idle after trp)             |       |

|                    | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal                          | *2    |

|                    | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal                          | *2    |

|                    | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal                          | *2    |

|                    | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | NOP (PALL may affect other bank) | *5    |

|                    | L  | L   | L   | Н  | Х          | REF/SELF   | Illegal                          |       |

|                    | L  | L   | L   | L  | MODE       | MRS        | Illegal                          |       |

| Bank<br>Activating | Н  | Х   | Х   | X  | Х          | DESL       | NOP (Bank Active after tRCD)     |       |

| Activating         | L  | Н   | Н   | Н  | Х          | NOP        | NOP (Bank Active after tRCD)     |       |

|                    | L  | Н   | Н   | L  | Х          | BST        | NOP (Bank Active after tRCD)     |       |

|                    | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal                          | *2    |

|                    | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal                          | *2    |

|                    | L  | L   | Н   | Н  | BA, RA     | ACTV       | Illegal                          | *2, 8 |

|                    | L  | L   | Н   | L  | ВА         | PRE        | Illegal                          | *2    |

|                    | L  | L   | Н   | L  | AP         | PALL       | Illegal                          |       |

|                    | L  | L   | L   | Н  | Х          | REF/SELF   | Illegal                          |       |

|                    | L  | L   | L   | L  | MODE       | MRS        | Illegal                          |       |

### (Continued)

| Current<br>State | <u>cs</u> | RAS | CAS | WE | Addr | Command                            | Function Notes                    |

|------------------|-----------|-----|-----|----|------|------------------------------------|-----------------------------------|

| Refreshing       | Н         | Х   | Х   | Х  | Х    | DESL                               | NOP (Idle after trc)              |

|                  | L         | Н   | Н   | Х  | Х    | NOP/BST                            | NOP (Idle after t <sub>RC</sub> ) |

|                  | L         | Н   | L   | Х  | Х    | READ/READA/<br>WRIT/WRITA          | Illegal                           |

|                  | L         | L   | Н   | Х  | Х    | ACTV/<br>PRE/PALL                  | Illegal                           |

|                  | L         | L   | L   | Х  | Х    | REF/SELF/<br>MRS                   | Illegal                           |

| Mode<br>Register | Н         | Х   | Х   | Х  | Х    | DESL                               | NOP (Idle after trsc)             |

| Setting          | L         | Н   | Н   | Н  | Х    | NOP                                | NOP (Idle after trsc)             |

|                  | L         | Н   | Н   | L  | Х    | BST                                | Illegal                           |

|                  | L         | Н   | L   | Х  | Х    | READ/READA/<br>WRIT/WRITA          | Illegal                           |

|                  | L         | L   | Х   | Х  | Х    | ACTV/PRE/<br>PALL/REF/<br>SELF/MRS | Illegal                           |

### ABBREVIATIONS:

RA = Row Address

CA = Column Address

AP = Auto Precharge

### **COMMAND TRUTH TABLE FOR CKE**

| Current<br>State | CKE<br>n-1 | CKE<br>n | CS | RAS | CAS | WE | Addr | Function Notes                                                                      |

|------------------|------------|----------|----|-----|-----|----|------|-------------------------------------------------------------------------------------|

| Self-<br>refresh | Н          | Х        | Х  | Х   | Х   | Х  | Х    | Invalid                                                                             |

| Tellesii         | L          | Н        | Н  | Х   | Х   | Х  | Х    | Exit Self-refresh (Self-refresh Recovery $\rightarrow$ Idle after $t_{RC}$ )        |

|                  | L          | Н        | L  | Н   | Н   | Н  | Х    | Exit Self-refresh (Self-refresh Recovery $\rightarrow$ Idle after t <sub>RC</sub> ) |

|                  | L          | Н        | L  | Н   | Н   | L  | Х    | Illegal                                                                             |

|                  | L          | Н        | L  | Н   | L   | X  | Х    | Illegal                                                                             |

|                  | L          | Н        | L  | L   | Х   | Χ  | Х    | Illegal                                                                             |

|                  | L          | L        | Х  | Х   | Х   | Χ  | Х    | NOP (Maintain Self-refresh)                                                         |

| Self-<br>refresh | L          | Х        | Х  | Х   | Х   | Х  | Х    | Invalid                                                                             |

| Recovery         | Н          | Н        | Н  | Х   | Х   | Х  | Х    | Idle after t <sub>RC</sub>                                                          |

|                  | Н          | Н        | L  | Н   | Н   | Н  | Х    | Idle after t <sub>RC</sub>                                                          |

|                  | Н          | Н        | L  | Н   | Н   | L  | Х    | Illegal                                                                             |

|                  | Н          | Н        | L  | Н   | L   | Х  | Х    | Illegal                                                                             |

|                  | Н          | Н        | L  | L   | Х   | Х  | Х    | Illegal                                                                             |

|                  | Н          | L        | Х  | Х   | Х   | Х  | X    | Illegal                                                                             |

| Current<br>State | CKE<br>n-1 | CKE<br>n | CS | RAS | CAS | WE | Addr | Function Notes                        |

|------------------|------------|----------|----|-----|-----|----|------|---------------------------------------|

| Power<br>Down    | Н          | Х        | Х  | Х   | Х   | Х  | Х    | Invalid                               |

| Down             |            |          | Н  | Х   | Х   | Х  | Х    | Fuit Davier Davin Made Lidle          |

|                  | L          | Н        | L  | Н   | Н   | Н  | Х    | - Exit Power Down Mode → Idle         |

|                  | L          | L        | Х  | Х   | Х   | Х  | Х    | NOP (Maintain Power Down Mode)        |

|                  | L          | Н        | L  | L   | Х   | X  | Х    | Illegal                               |

|                  | L          | Н        | L  | Н   | L   | Х  | Х    | Illegal                               |

|                  | L          | Н        | L  | Н   | Н   | L  | Х    | Illegal                               |

| All<br>Banks     | Н          | Н        | Н  | Х   | Х   | Х  |      | Refer to the Operation Command Table. |

| Idle             | Н          | Н        | L  | Н   | Х   | Х  |      | Refer to the Operation Command Table. |

|                  | Н          | Н        | L  | L   | Н   | Х  |      | Refer to the Operation Command Table. |

|                  | Н          | Н        | L  | L   | L   | Н  | Х    | Auto-refresh                          |

|                  | Н          | Н        | L  | L   | L   | L  | MODE | Refer to the Operation Command Table. |

|                  | Н          | L        | Н  | Х   | Х   | Х  | Х    | Power Down *6                         |

|                  | Н          | L        | L  | Н   | Н   | Н  | Х    | Power Down *6                         |

|                  | Н          | L        | L  | Н   | Н   | L  |      | Illegal                               |

|                  | Н          | L        | L  | Н   | L   | Х  | Х    | Illegal                               |

|                  | Н          | L        | L  | L   | Н   | Х  | Х    | Illegal                               |

|                  | Н          | L        | L  | L   | L   | Н  | Х    | Self-refresh *6                       |

|                  | Н          | L        | L  | L   | L   | L  | Х    | Illegal                               |

|                  | L          | Х        | Х  | Х   | Х   | Х  | Х    | Invalid                               |

### (Continued)

| Current<br>State                      | CKE<br>n-1 | CKE<br>n | CS | RAS | CAS | WE | Addr | Function Notes                        |  |

|---------------------------------------|------------|----------|----|-----|-----|----|------|---------------------------------------|--|

| Bank Active<br>Bank                   | Н          | Н        | Х  | Х   | Х   | Х  | Х    | Refer to the Operation Command Table. |  |

| Activating Read/Write                 | Н          | L        | Х  | Х   | Х   | Х  | Х    | Begin Clock Suspend next cycle        |  |

| Read with Auto- precharge/ Write with | L          | Н        | Х  | Х   | Х   | Х  | Х    | Exit Clock Suspend next cycle         |  |

| Auto-<br>precharge                    | L          | L        | Х  | Х   | Х   | Х  | Х    | Maintain Clock Suspend                |  |

| Clock<br>Suspend                      | Н          | Х        | Х  | Х   | Х   | Х  | Х    | Invalid                               |  |

| Suspend                               | L          | Н        | Χ  | Х   | Х   | X  | Х    | Exit Clock Suspend next cycle         |  |

|                                       | L          | L        | Χ  | Х   | Х   | X  | Х    | Maintain Clock Suspend                |  |

| Any State<br>Other Than               | L          | X        | Χ  | Х   | Х   | X  | Х    | Invalid                               |  |

| Listed<br>Above                       | Н          | Н        | Χ  | Х   | Х   | X  | Х    | Refer to the Operation Command Table. |  |

| 1.3000                                | Н          | L        | Х  | Х   | Х   | Х  | Х    | Illegal                               |  |

**Notes:** \*1. All entries assume the CKE was High during the proceeding clock cycle and the current clock cycle. Illegal means don't used command. If used, power up sequence be asserted after power shut down.

- \*2. Illegal to bank in specified state; entry may be legal in the bank specified by BA, depending on the state of that bank.

- \*3. Illegal if any bank is not idle.

- \*4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- \*5. NOP to bank precharging or in idle state.

May precharge bank spesified by BA (and AP).

- \*6. SELF command should only be issued after the last read data have been appeared on DQ.

- \*7. MRS command should only be issued on condition that all DQ are in Hi-Z.

#### **■ FUNCTIONAL DESCRIPTION**

#### SDRAM BASIC FUNCTION

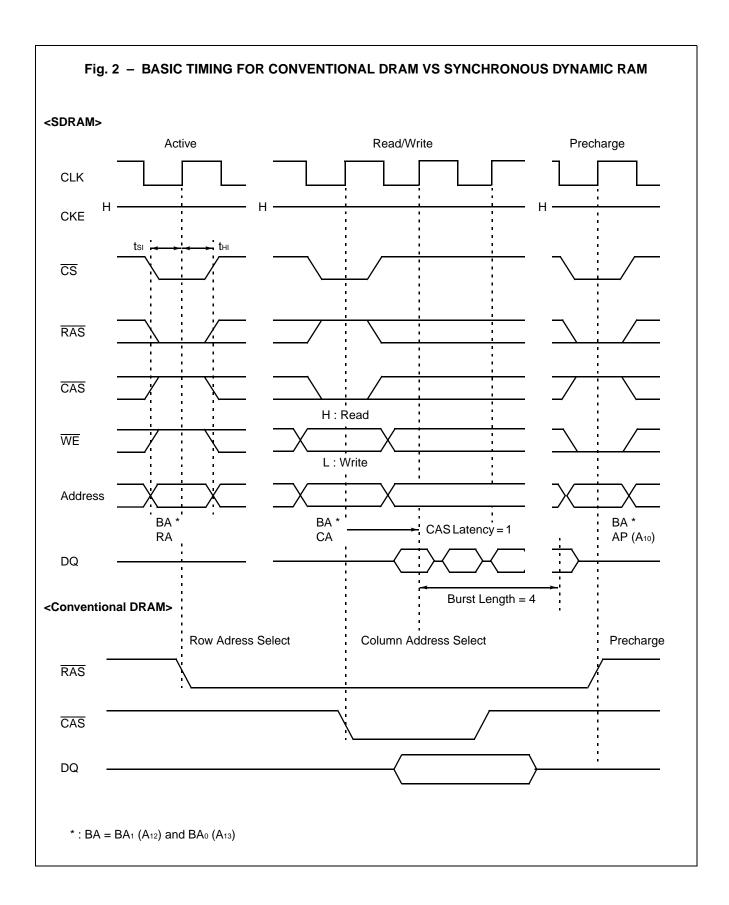

Three major differences between this SDRAM and conventional DRAMs are: synchronized operation, burst mode, and mode register.

The **synchronized operation** is the fundamental difference. An SDRAM uses a clock input for the synchronization, where the DRAM is basically asynchronous memory although it has been using two clocks, RAS and CAS. Each operation of DRAM is determined by their timing phase differences while each operation of SDRAM is determined by commands and all operations are referenced to a positive clock edge. Fig 3 shows the basic timing diagram differences between SDRAMs and DRAMs.

The **burst mode** is a very high speed access mode utilizing an internal column address generator. Once a column addresses for the first access is set, following addresses are automatically generated by the internal column address counter.

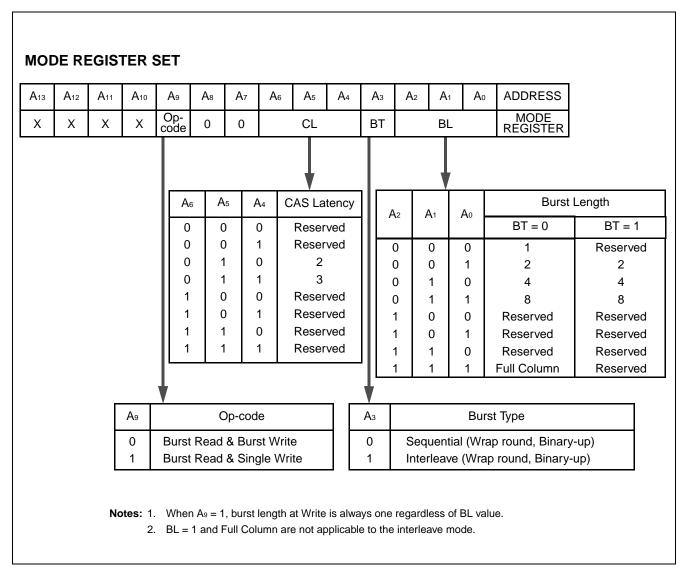

The **mode register** is to justify the SDRAM operation and function into desired system conditions. MODE REGISTER TABLE shows how SDRAM can be configured for system requirement by mode register programming.

### **CLOCK (CLK) and CLOCK ENABLE (CKE)**

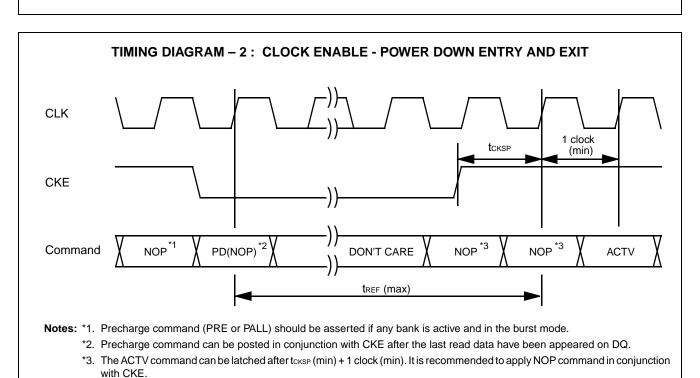

All input and output signals of SDRAM use register type buffers. A CLK is used as a trigger for the register and internal burst counter increment. All inputs are latched by a positive edge of CLK. All outputs are validated by the CLK. CKE is a high active clock enable signal. When CKE = Low is latched at a clock input during active cycle, the next clock will be internally masked. During idle state (all banks have been precharged), the Power Down mode (standby) is entered with CKE = Low and this will make extremely low standby current.

### CHIP SELECT (CS)

$\overline{\text{CS}}$  enables all commands inputs,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , and  $\overline{\text{WE}}$ , and address input. When  $\overline{\text{CS}}$  is High, command signals are negated but internal operation such as burst cycle will not be suspended. If such a control isn't needed,  $\overline{\text{CS}}$  can be tied to ground level.

### COMMAND INPUT (RAS, CAS and WE)

Unlike a conventional DRAM,  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  do not directly imply SDRAM operation, such as Row address strobe by  $\overline{RAS}$ . Instead, each combination of  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  input in conjunction with  $\overline{CS}$  input at a rising edge of the CLK determines SDRAM operation. Refer to FUNCTIONAL TRUTH TABLE in page 5.

### ADDRESS INPUT (Ao to A11)

Address input selects an arbitrary location of a total of 4,194,304 words of each memory cell matrix. A total of fourteen address input signals are required to decode such a matrix. SDRAM adopts an address multiplexer in order to reduce the pin count of the address line. At a Bank Active command (ACTV), twelve Row addresses are initially latched and the remainder of ten Column addresses are then latched by a Column address strobe command of either a Read command (READ or READA) or Write command (WRIT or WRITA).

#### BANK SELECT (A13, A12)

This SDRAM has four banks and each bank is organized as 4 M words by 4-bit.

Bank selection by A<sub>13</sub>, A<sub>12</sub> occurs at Bank Active command (ACTV) followed by read (READ or READA), write (WRIT or WRITA), and precharge command (PRE).

### DATA INPUT AND OUTPUT (DQ<sub>0</sub> to DQ<sub>3</sub>)

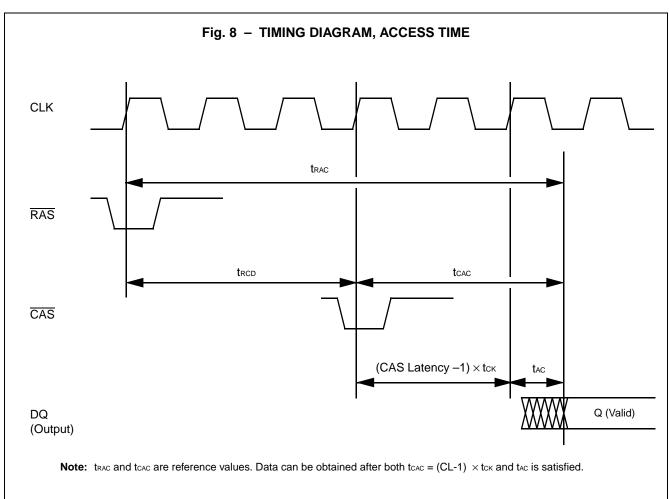

Input data is latched and written into the memory at the clock following the write command input. Data output is obtained by the following conditions followed by a read command input:

$t_{\text{RAC}}$ ; from the bank active command when  $t_{\text{RCD}}$  (min) is satisfied. (This parameter is reference only.)

tcac ; from the read command when tRCD is greater than tRCD (min). (This parameter is reference only.)

tac ; from the clock edge after trac and toac.

The polarity of the output data is identical to that of the input. Data is valid between access time (determined by the three conditions above) and the next positive clock edge (toh).

### DATA I/O MASK (DQM)

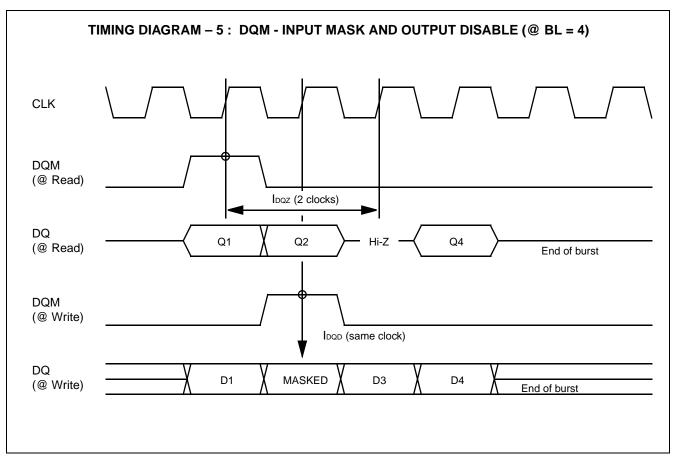

DQM is an active high enable input and has an output disable and input mask function. During burst cycle and when DQM = High is latched by a clock, input is masked at the same clock and output will be masked at the second clock later while internal burst counter will increment by one or will go to the next stage depending on burst type.

### **BURST MODE OPERATION AND BURST TYPE**

The burst mode provides faster memory access. The burst mode is implemented by keeping the same Row address and by automatic strobing column address. Access time and cycle time of Burst mode is specified as tac and tok, respectively. The internal column address counter operation is determined by a mode register which defines burst type and burst count length of 1, 2, 4 or 8 bits of boundary. In order to terminate or to move from the current burst mode to the next stage while the remaining burst count is more than 1, the following combinations will be required:

| Current Stage | Next Stage  | Method (Assert the following command) |                                        |  |  |

|---------------|-------------|---------------------------------------|----------------------------------------|--|--|

| Burst Read    | Burst Read  |                                       | Read Command                           |  |  |

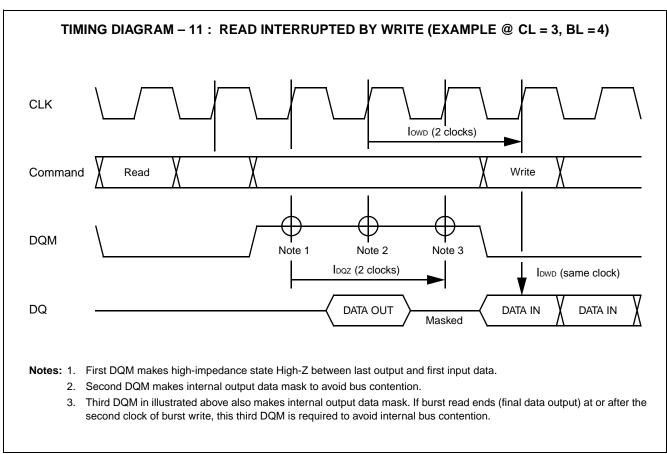

| Burst Read    | Burst Write | 1st Step                              | Mask Command (Normally 3 clock cycles) |  |  |

| Buist Read    | Burst write | 2nd Step                              | Write Command after lowd               |  |  |

| Burst Write   | Burst Write |                                       | Write Command                          |  |  |

| Burst Write   | Burst Read  |                                       | Read Command                           |  |  |

| Burst Read    | Precharge   |                                       | Precharge Command                      |  |  |

| Burst Write   | Precharge   |                                       | Precharge Command                      |  |  |

The burst type can be selected either sequential or interleave mode if burst length is 2, 4 or 8. The sequential mode is an incremental decoding scheme within a boundary address to be determined by count length, it assigns +1 to the previous (or initial) address until reaching the end of boundary address and then wraps round to least significant address (= 0). The interleave mode is a scrambled decoding scheme for  $A_0$  and  $A_2$ . If the first access of column address is even (0), the next address will be odd (1), or vice-versa.

### (Continued)

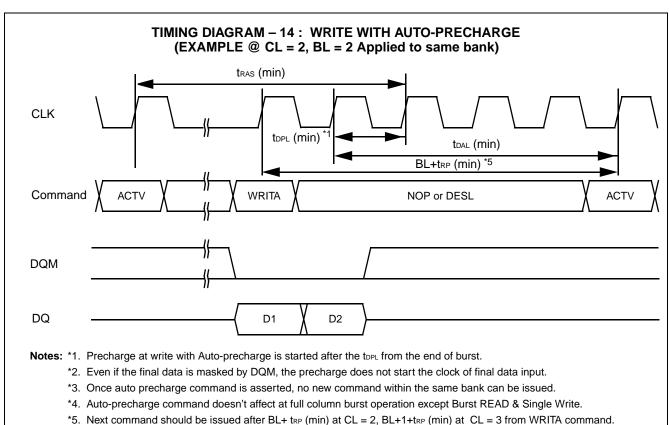

When the full burst operation is executed at single write mode, Auto-precharge command is valid only at write operation.

The burst type can be selected either sequential or interleave mode. But only the sequential mode is usable to the full column burst. The sequential mode is an incremental decoding scheme within a boundary address to be determined by burst length, it assigns +1 to the previous (or initial) address until reaching the end of boundary address and then wraps round to least significant address (= 0).

| Burst<br>Length | Starting Column<br>Address<br>A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | Sequential Mode | Interleave      |

|-----------------|----------------------------------------------------------------------------|-----------------|-----------------|

| 2               | X X 0                                                                      | 0 – 1           | 0 – 1           |

| 2               | X X 1                                                                      | 1 – 0           | 1 – 0           |

|                 | X 0 0                                                                      | 0-1-2-3         | 0-1-2-3         |

| 4               | X 0 1                                                                      | 1-2-3-0         | 1-0-3-2         |

| 4               | X 1 0                                                                      | 2-3-0-1         | 2-3-0-1         |

|                 | X 1 1                                                                      | 3-0-1-2         | 3-2-1-0         |

|                 | 0 0 0                                                                      | 0-1-2-3-4-5-6-7 | 0-1-2-3-4-5-6-7 |

|                 | 0 0 1                                                                      | 1-2-3-4-5-6-7-0 | 1-0-3-2-5-4-7-6 |

|                 | 0 1 0                                                                      | 2-3-4-5-6-7-0-1 | 2-3-0-1-6-7-4-5 |

| 8               | 0 1 1                                                                      | 3-4-5-6-7-0-1-2 | 3-2-1-0-7-6-5-4 |

|                 | 1 0 0                                                                      | 4-5-6-7-0-1-2-3 | 4-5-6-7-0-1-2-3 |

|                 | 1 0 1                                                                      | 5-6-7-0-1-2-3-4 | 5-4-7-6-1-0-3-2 |

|                 | 1 1 0                                                                      | 6-7-0-1-2-3-4-5 | 6-7-4-5-2-3-0-1 |

|                 | 1 1 1                                                                      | 7-0-1-2-3-4-5-6 | 7-6-5-4-3-2-1-0 |

### **FULL COLUMN BURST AND BURST STOP COMMAND (BST)**

The full column burst is an option of burst length and available only at sequential mode of burst type. This full column burst mode is repeatedly access to the same column. If burst mode reaches end of column address, then it wraps round to first column address (= 0) and continues to count until interrupted by the news read (READ) /write (WRIT), precharge (PRE), or burst stop (BST) command. The selection of Auto-precharge option is illegal during the full column burst operation except write command at BURST READ & SINGLE WRITE mode.

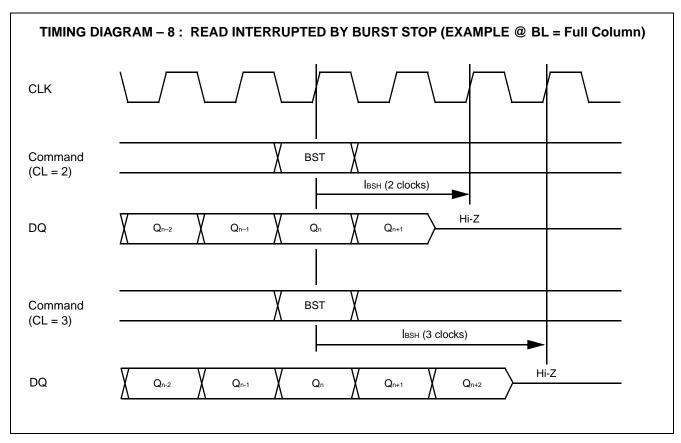

The BST command is applicable to terminate the burst operation. If the BST command is asserted during the burst mode, its operation is terminated immediately and the internal state moves to Bank Active.

When read mode is interrupted by BST command, the output will be in High-Z.

For the detail rule, please refer to Timing Diagram-8.

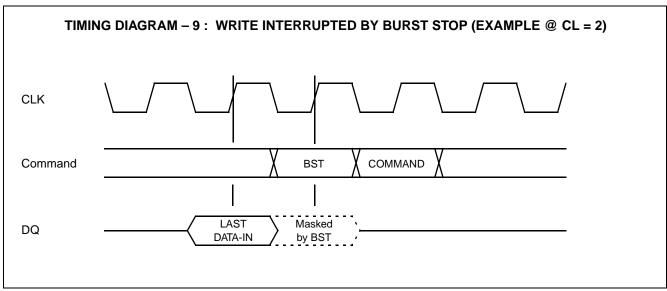

When write mode is interrupted by BST command, the data to be applied at the same time with BST command will be ignored.

#### **BURST READ & SINGLE WRITE**

The burst read and single write mode provides single word write operation regardless of its burst length. In this mode, burst read operation does not be affected by this mode.

### PRECHARGE AND PRECHARGE OPTION (PRE, PALL)

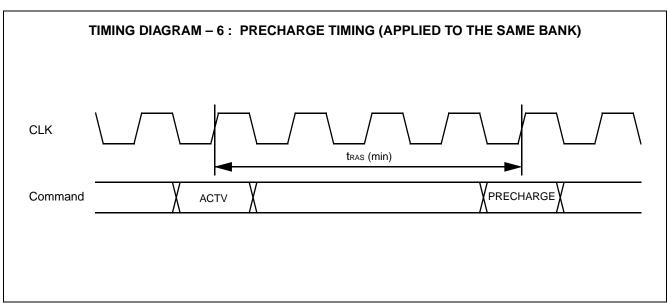

SDRAM memory core is the same as conventional DRAMs', requiring precharge and refresh operations. Precharge rewrites the bit line and to reset the internal Row address line and is executed by the Precharge command (PRE). With the Precharge command, SDRAM will automatically be in standby state after precharge time (trp).

The precharged bank is selected by combination of AP and  $A_{13}$ ,  $A_{12}$  when Precharge command is asserted. If AP = High, all banks are precharged regardless of  $A_{13}$ ,  $A_{12}$  (PALL). If AP = Low, a bank to be selected by  $A_{13}$ ,  $A_{12}$  is precharged (PRE).

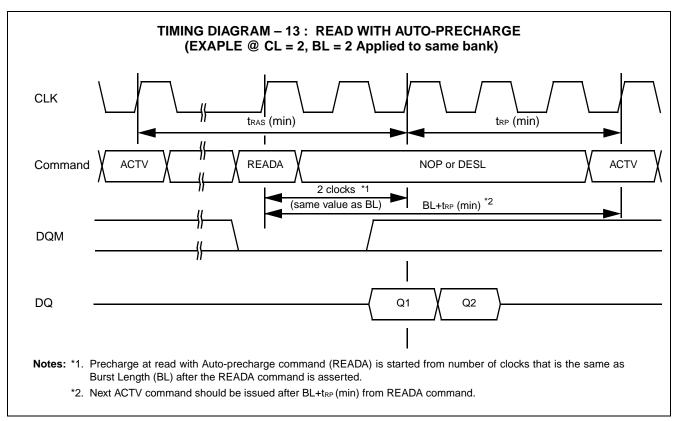

The auto-precharge enters precharge mode at the end of burst mode of read or write without Precharge command assertion.

This auto precharge is entered by AP = High when a read or write command is asserted. Refer to FUNCTIONAL TRUTH TABLE.

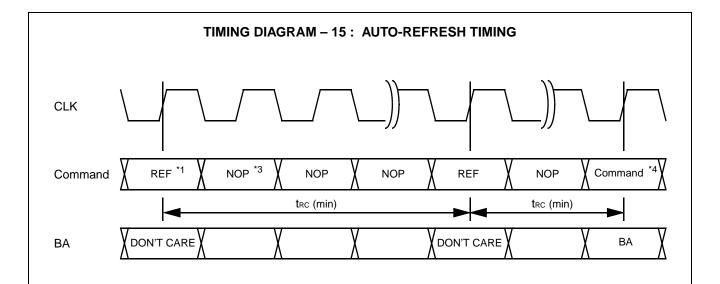

### **AUTO-REFRESH (REF)**

Auto-refresh uses the internal refresh address counter. The SDRAM Auto-refresh command (REF) generates Precharge command internally. All banks of SDRAM should be precharged prior to the Auto-refresh command. The Auto-refresh command should also be asserted every 16  $\mu$ s or a total 4096 refresh commands within a 65.6 ms period.

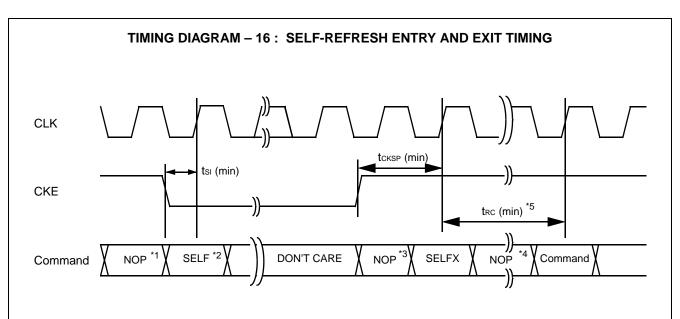

### **SELF-REFRESH ENTRY (SELF)**

Self-refresh function provides automatic refresh by an internal timer as well as Auto-refresh and will continue the refresh function until cancelled by SELFX.

The Self-refresh is entered by applying an Auto-refresh command in conjunction with CKE = Low (SELF). Once SDRAM enters the self-refresh mode, all inputs except for CKE will be "don't care" (either logic high or low level state) and outputs will be in a High-Z state. During a self-refresh mode, CKE = Low should be maintained. SELF command should only be issued after last read data has been appeared on DQ.

**Note:** When the burst refresh method is used, a total of 4096 auto-refresh commands within 4 ms must be asserted prior to the self-refresh mode entry.

#### SELF-REFRESH EXIT (SELFX)

To exit self-refresh mode, apply minimum tpde after CKE brought high, and then the NOP command (NOP) or the Deselect command (DESL) should be asserted within one troperiod. CKE should be held High within one troperiod after tpde. Refer to Timing Diagram for the detail.

It is recommended to assert an Auto-refresh command just after the tRC period to avoid the violation of refresh period.

**Note:** When the burst refresh method is used, a total of 4096 auto-refresh commands within 4 ms must be asserted after the self-refresh exit.

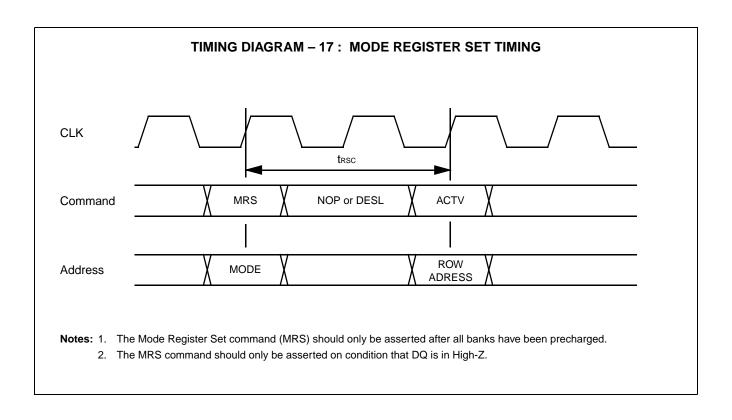

#### **MODE REGISTER SET (MRS)**

The mode register of SDRAM provides a variety of different operations. The register consists of four operation fields; Burst Length, Burst Type, CAS latency, and Operation Code. Refer to MODE REGISTER TABLE in page 33.

The mode register can be programmed by the Mode Register Set command (MRS). Each field is set by the address line. Once a mode register is programmed, the contents of the register will be held until re-programmed by another MRS command (or part loses power). MRS command should only be issued on condition that all DQ is in Hi-Z.

The condition of the mode register is undefined after the power-up stage. It is required to set each field after initialization of SDRAM. Refer to POWER-UP INITIALIZATION below.

#### **POWER-UP INITIALIZATION**

The SDRAM internal condition after power-up will be undefined. It is required to follow the following Power On Sequence to execute read or write operation.

- 1. Apply power and start clock. Attempt to maintain either NOP or DESL command at the input.

- 2. Maintain stable power, stable clock, and NOP condition for a minimum of 200  $\mu s$ .

- 3. Precharge all banks by Precharge (PRE) or Precharge All command (PALL).

- 4. Assert minimum of 8 Auto-refresh command (REF).

- 5. Program the mode register by Mode Register Set command (MRS).

In addition, it is recommended DQM and CKE to track  $V_{CC}$  to insure that output is High-Z state. The Mode Register Set command (MRS) can be set before 8 Auto-refresh command (REF).

### MINIMUM CLOCK LATENCY OR DELAY TIME FOR 1 BANK OPERATION

| Second command (same bank)  First command | MRS                     | ACTV                    | READ         | READA              | WRIT         | WRITA              | PRE          | PALL         | REF                  | SELF                    |

|-------------------------------------------|-------------------------|-------------------------|--------------|--------------------|--------------|--------------------|--------------|--------------|----------------------|-------------------------|

| MRS                                       | <b>t</b> rsc            | <b>t</b> rsc            |              |                    |              |                    | trsc         | <b>t</b> rsc | trsc                 | <b>t</b> rsc            |

| ACTV                                      |                         |                         | <b>t</b> RCD | *4<br><b>t</b> RCD | <b>t</b> RCD | *4<br><b>t</b> RCD | <b>t</b> ras | <b>t</b> ras |                      |                         |

| READ                                      |                         |                         | 1            | 1                  | *1<br>4      | *1<br><b>4</b>     | 1            | 1            |                      |                         |

| READA                                     | BL +<br>t <sub>RP</sub> | BL +<br>t <sub>RP</sub> |              |                    |              |                    |              |              | BL + t <sub>RP</sub> | BL +<br>t <sub>RP</sub> |

| WRIT                                      |                         |                         | <b>t</b> wr  | <b>t</b> wr        | 1            | 1                  | <b>t</b> dpl | <b>t</b> dpl |                      |                         |

| WRITA                                     | <b>t</b> dal            | <b>t</b> dal            |              |                    |              |                    |              |              | <b>t</b> dal         | <b>t</b> dal            |

| PRE                                       | *3<br><b>t</b> RP       | *3<br><b>t</b> RP       |              |                    |              |                    | <b>t</b> RP  | <b>t</b> RP  | *3<br><b>t</b> RP    | *3<br><b>t</b> rp       |

| PALL                                      | *3<br><b>t</b> RP       | *3<br><b>t</b> RP       |              |                    |              |                    | <b>t</b> RP  | <b>t</b> RP  | *3<br><b>t</b> RP    | *3<br><b>t</b> rp       |

| REF                                       | <b>t</b> RC             | <b>t</b> RC             |              |                    |              |                    | <b>t</b> RC  | <b>t</b> RC  | <b>t</b> RC          | <b>t</b> RC             |

| SELFX                                     | <b>t</b> rc             | <b>t</b> rc             |              |                    |              |                    |              |              | <b>t</b> rc          | trc                     |

Notes: \*1. Assume no I/O conflict.

- \*2. If  $t_{RP} \le t_{CK}$ , minimum latency is a sum of BL + CL.

- \*3. Assume output is in High-Z state.

- \*4. Assume tras is satisfied.

|  | Illegal Command |

|--|-----------------|

|--|-----------------|

### MINIMUM CLOCK LATENCY OR DELAY TIME FOR MULTI BANK OPERATION

| Second command (other bank)  First command | MRS                                | ACTV               | READ           | READA   | WRIT     | WRITA         | PRE          | PALL               | REF                                | SELF                               |

|--------------------------------------------|------------------------------------|--------------------|----------------|---------|----------|---------------|--------------|--------------------|------------------------------------|------------------------------------|

| MRS                                        | <b>t</b> RSC                       | <b>t</b> rsc       |                |         |          |               | <b>t</b> rsc | <b>t</b> rsc       | trsc                               | trsc                               |

| ACTV                                       |                                    | *1<br><b>t</b> RRD | 1              | 1       | 1        | 1             | *7<br>1      | *2<br><b>t</b> ras |                                    |                                    |

| READ                                       |                                    | *1<br>1            | 1              | 1       | *2<br>*3 | *2<br>*3<br>4 | *7<br>1      | *8<br>1            |                                    |                                    |

| READA *9                                   | *1<br>*4<br>BL+<br>t <sub>RP</sub> | *1<br><b>1</b>     | 1              | 1       | 4 *2 *3  | *2<br>*3<br>4 | 1            |                    | *1<br>*4<br>BL+<br>t <sub>RP</sub> | *1<br>*4<br>BL+<br>t <sub>RP</sub> |

| WRIT                                       |                                    | *1<br><b>1</b>     | *2<br><b>1</b> | *2<br>1 | *2<br>1  | *2<br>1       | *7<br>1      | *8<br>1            |                                    |                                    |

| WRITA *9                                   | *1<br>*4<br>BL+<br>t <sub>RP</sub> | 1                  | 1              | 1       | 1        | 1             | 1            |                    | *1<br>BL+<br>t <sub>RP</sub>       | *1<br>BL+<br>t <sub>RP</sub>       |

| PRE                                        | *1<br><b>t</b> RP                  | *1<br>1            | 1              | 1       | 1        | 1             | 1            | *2<br><b>t</b> ras | *1<br><b>t</b> RP                  | *1<br><b>t</b> RP                  |

| PALL *5                                    | <b>t</b> RP                        | <b>t</b> RP        |                |         |          |               | 1            | 1                  | *1<br>*6<br><b>t</b> RP            | *1<br>*6<br><b>t</b> RP            |

| REF                                        | <b>t</b> RC                        | <b>t</b> RC        |                |         |          |               | <b>t</b> RC  | <b>t</b> rc        | <b>t</b> RC                        | <b>t</b> RC                        |

| SELFX                                      | <b>t</b> rc                        | <b>t</b> rc        |                |         |          |               |              |                    | trc                                | <b>t</b> RC                        |

**Notes:** \*1. Assume other banks is in idle state.

- \*2. Assume other banks is in active state.

- \*3. Assume no I/O conflict.

- \*4. If  $t_{RP} \le t_{CK}$ , minimum latency is a sum of BL + CL.

- \*5. Assume PALL command dose not affect any operation on other banks.

- \*6. Assume output is in High-Z sate.

- \*7. Assume tras of other banks is satisfied.

- \*8. Assume tras (ACTV to PALL) is satisfied.

- \*9. If other banks should be interrupted, tras of own bank is satisfied.

|  |  | Illegal Command |

|--|--|-----------------|

|--|--|-----------------|

22

### ■ ABSOLUTE MAXIMUM RATINGS (See WARNING)

| Parameter                             | Symbol    | Value        | Unit |

|---------------------------------------|-----------|--------------|------|

| Voltage of Vcc Supply Relative to Vss | Vcc, Vcca | -0.5 to +4.6 | V    |

| Voltage at Any Pin Relative to Vss    | VIN, VOUT | -0.5 to +4.6 | V    |

| Short Circuit Output Current          | Іоит      | -50 to +50   | mA   |

| Power Dissipation                     | Po        | 1.0          | W    |

| Storage Temperature                   | Тѕтс      | -55 to +125  | °C   |

**WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### ■ RECOMMENDED OPERATING CONDITIONS

(Referenced to Vss)

| Parameter           | Notes | Symbol    | Min. | Тур. | Max.      | Unit |

|---------------------|-------|-----------|------|------|-----------|------|

| Supply Voltage      |       | Vcc, Vccq | 3.0  | 3.3  | 3.6       | V    |

| Supply Voltage      |       | Vss, Vssq | 0    | 0    | 0         | V    |

| Input High Voltage  | *1    | VIH       | 2.0  | _    | Vcc + 0.5 | V    |

| Input Low Voltage   | *2    | VıL       | -0.5 | _    | 0.8       | V    |

| Ambient Temperature |       | TA        | 0    | _    | 70        | °C   |

**Notes:** \*1. Overshoot limit:  $V_{H}$  (max) =  $V_{CC}$  +1.5 V with a pulsewidth  $\leq 5$  ns.

\*2. Undershoot limit:  $V_{\mathbb{L}}$  (min) = -1.5 V with a pulsewidth  $\leq 5$  ns.

**WARNING:** Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.

### **■ CAPACITANCE**

$(T_A = 25^{\circ}C, f = 1 \text{ MHz})$

| Parameter                         | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------------|------|------|------|------|

| Input Capacitance, Except for CLK | C <sub>IN1</sub> | 2.5  | _    | 5.0  | pF   |

| Input Capacitance for CLK         | C <sub>IN2</sub> | 2.5  | _    | 4.0  | pF   |

| I/O Capacitance                   | Cı/o             | 4.0  | _    | 6.5  | pF   |

### **■ DC CHARACTERISTICS**

(At recommended operating conditions unless otherwise noted.) Notes 1, 2

| Dore                                                   | Parameter                          |                                                  | Condition                                                                                                                                                                                         | Va   | lue            | Unit |

|--------------------------------------------------------|------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|

| Fara                                                   | imeter                             | Symbol                                           | Condition                                                                                                                                                                                         | Min. | Max.           | Unit |

| Output High Voltage                                    |                                    | V <sub>OH(DC)</sub>                              | Iон = −2 mA                                                                                                                                                                                       | 2.4  | _              | V    |

| Output Low Voltage                                     |                                    | Vol(DC)                                          | IoL = 2 mA                                                                                                                                                                                        | _    | 0.4            | V    |

| Input Leakage Curre                                    | ent (Any Input)                    | lu                                               | $0 \text{ V} \le V_{IN} \le V_{CC}$ ;<br>All other pins not under test = $0 \text{ V}$                                                                                                            | -10  | 10             | μА   |

| Output Leakage Cui                                     | rrent                              | ILO                                              | 0 V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> ;<br>Data out disabled                                                                                                                                    | -10  | 10             | μΑ   |

|                                                        | MB81F64442C<br>-102/102L/-103/103L | Burst: Length = 4 trc = min for BL = 4 tck = min | 105                                                                                                                                                                                               | mA   |                |      |

| Operating Current<br>(Average Power<br>Supply Current) | MB81F64442C<br>-102/102L/-103/103L | Icc1D                                            | Burst: Length = 4 (each Bank) tRC = min for BL = 4 (each Bank) tcκ = min 2 banks active Outputs open Addresses changed up to 3-times during tRC (min) 0 V ≤ VIN ≤ VCC                             | _    | Max. — 0.4  10 | mA   |

|                                                        | MB81F64442C<br>-102/103            |                                                  | CKE = V <sub>I</sub> ∟<br>All banks idle                                                                                                                                                          | _    | 2              |      |

|                                                        | MB81F64442<br>-102L/103L           | - Ісс2Р                                          | $tc\kappa = min$<br>Power down mode<br>$0 \ V \le V_{IN} \le V_{CC}$                                                                                                                              | _    |                | → mA |

|                                                        | MB81F64442C<br>-102/-103           |                                                  | CKE = V <sub>I</sub> L<br>All banks idle                                                                                                                                                          | _    | 1              | ^    |

| Precharge Standby                                      | MB81F64442C<br>-102L/103L          | - Icc2PS                                         | $ \begin{array}{l} CLK = H \ or \ L \\ Power \ down \ mode \\ 0 \ V \leq V_{IN} \leq V_{CC} \end{array} $                                                                                         | _    | 0.5            | mA   |

| Current<br>(Power Supply<br>Current)                   |                                    | Ісс2н                                            | CKE = $V_{IH}$<br>All banks idle, $t_{CK}$ = min<br>NOP commands only,<br>Input signals (except to<br>CMD) are changed one<br>time during 3 clock cycles<br>$0 \text{ V} \leq V_{IN} \leq V_{CC}$ | _    | 15             | mA   |

|                                                        |                                    | Icc2ns                                           | $\label{eq:cke} \begin{split} CKE &= V_{IH} \\ All \ banks \ idle \\ CLK &= H \ or \ L \\ Input \ signal \ are \ stable \\ 0 \ V &\leq V_{IN} \leq V_{CC} \end{split}$                            | _    | 2              | mA   |

| Parameter                                              |                           | Cumbal           | Condition                                                                                                                                                                           | Va   | lue  | Unit |

|--------------------------------------------------------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Para                                                   | meter                     | Symbol           | Condition                                                                                                                                                                           | Min. | Max. | Unit |

|                                                        | MB81F64442C<br>-102/-103  | Іссзр            | CKE = V <sub>IL</sub><br>Any bank active                                                                                                                                            | _    | 2    | mA   |

|                                                        | MB81F64442C<br>-102L/103L | ICC3P            | $ t_{CK} = min $ $ 0 \ V \le V_{IN} \le V_{CC} $                                                                                                                                    | _    | 1    | IIIA |

|                                                        | MB81F64442C<br>-102/-103  | lassa            | CKE = V <sub>IL</sub><br>Any bank active                                                                                                                                            | _    | 1    | mA   |

|                                                        | MB81F64442C<br>-102L/103L | Іссзрѕ           | CLK = H  or  L<br>$0 \text{ V} \le V_{IN} \le V_{CC}$                                                                                                                               | _    | 0.5  | IIIA |

| Active Standby<br>Current<br>(Power Supply<br>Current) |                           | Іссэн            | CKE = V <sub>IH</sub> Any bank active tck = min NOP commands only, Input signals (except to CMD) are changed one time during 3 clock cycles 0 V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | _    | 25   | mA   |

|                                                        |                           | Іссзиѕ           | CKE = V <sub>IH</sub> Any bank active CLK = H or L 0 V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                          | _    | 2    | mA   |

| Burst mode Current<br>(Average Power Sup               | ply Current)              | Icc4             | tck = min Burst Length = 4 Outputs open Multiple-banks active Gapless data 0 V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                  | _    | 85   | mA   |

| Refresh Current #1<br>(Average Power Sup               | ply Current)              | Iccs             | Auto-refresh; $t_{CK} = min$ $t_{RC} = min$ $0 \ V \le V_{IN} \le V_{CC}$                                                                                                           | _    | 240  | mA   |

| Refresh Current #2<br>(Average Power                   | MB81F64442C<br>-102/103   | Icc <sub>6</sub> | Self-refresh;<br>tck = min                                                                                                                                                          | _    | 1    | mA   |

| Supply Current)                                        | MB81F64442C<br>-102L/103L | 1000             | CKE ≤ 0.2 V<br>0 V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                                                              | _    | 0.5  | 1117 |

### **■ AC CHARACTERISTICS**

(At recommended operating conditions unless otherwise noted.) Note 2, 3, 4

| Davameter Notes                          | Maria  | Symbol           | MB81F64442C-102/-102L |      | MB81F64442C-103/-103L |      | 11:4     |

|------------------------------------------|--------|------------------|-----------------------|------|-----------------------|------|----------|

| Parameter Notes                          |        |                  | Min.                  | Max. | Min.                  | Max. | – Unit ∣ |

| Clock Period                             | CL = 2 | tck2             | 10                    | _    | 15                    |      | ns       |

|                                          | CL = 3 | <b>t</b> cкз     | 10                    |      | 10                    | _    | ns       |

| Clock High Time                          |        | <b>t</b> сн      | 3                     | _    | 3                     | _    | ns       |

| Clock Low Time                           |        | <b>t</b> cL      | 3                     | _    | 3                     | _    | ns       |

| Input Setup Time                         |        | <b>t</b> sı      | 2                     | _    | 2                     | _    | ns       |

| Input Hold Time                          |        | tнı              | 1                     | _    | 1                     | _    | ns       |

| Access Time from Clock *5, 6 (tck = min) | CL = 2 | t <sub>AC2</sub> | _                     | 6    | _                     | 8    | ns       |

|                                          | CL = 3 | <b>t</b> AC3     |                       | 6    |                       | 6    | ns       |

| Output in Low-Z *7                       |        | <b>t</b> LZ      | 0                     | _    | 0                     | _    | ns       |

| Output in High-Z *7                      | CL = 2 | <b>t</b> HZ2     | 3                     | 6    | 3                     | 8    | ns       |

|                                          | CL = 3 | <b>t</b> HZ3     |                       | 6    |                       | 6    | ns       |

| Output Hold Time *7                      |        | tон              | 3                     | _    | 3                     | _    | ns       |

| Time between Refresh                     |        | tref             | _                     | 65.6 | _                     | 65.6 | ms       |

| Transition Time                          |        | tτ               | 0.5                   | 2    | 0.5                   | 2    | ns       |

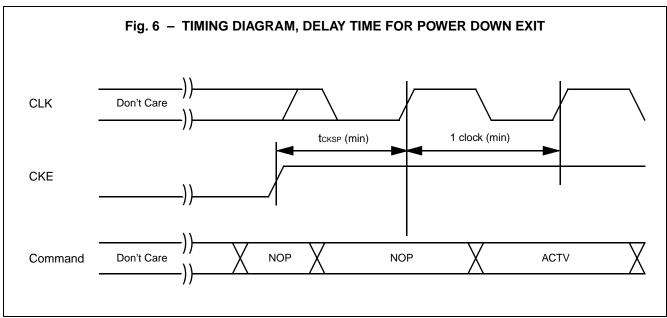

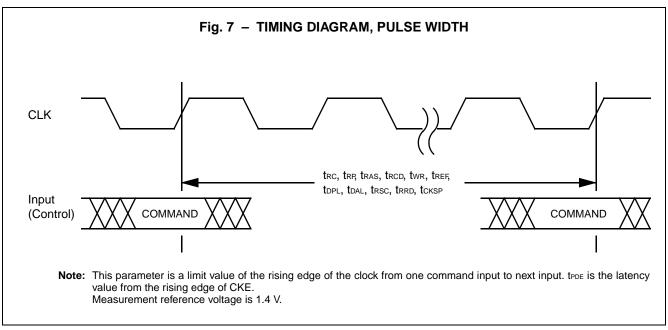

| CKE Setup Time for Power Down Exit Time  |        | <b>t</b> cksp    | 3                     | _    | 3                     | _    | ns       |

### BASE VALUES FOR CLOCK COUNT/LATENCY

| Doromotor Notes                             |      | Symbol            | MB81F64442C-102/-102L   |        | MB81F64442C-103/-103L   |        | 111:4:4 |

|---------------------------------------------|------|-------------------|-------------------------|--------|-------------------------|--------|---------|

| Parameter Notes                             |      |                   | Min.                    | Max.   | Min.                    | Max.   | Unit    |

| RAS Cycle Time *8                           |      | <b>t</b> RC       | 70                      | _      | 70                      | _      | ns      |

| RAS Precharge Time                          |      | <b>t</b> RP       | 20                      | _      | 20                      | _      | ns      |

| RAS Active Time                             |      | <b>t</b> ras      | 50                      | 110000 | 50                      | 110000 | ns      |

| RAS to CAS Delay Time *9                    |      | trcd              | 20                      | _      | 20                      | _      | ns      |

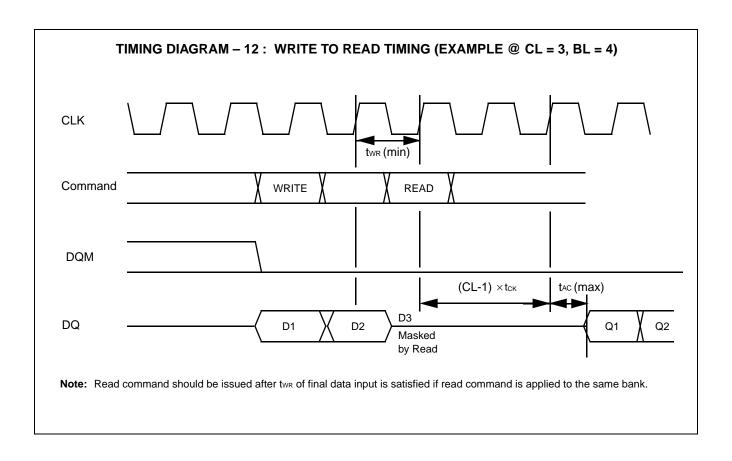

| Write Recovery Time                         |      | twr               | 10                      | _      | 10                      | _      | ns      |

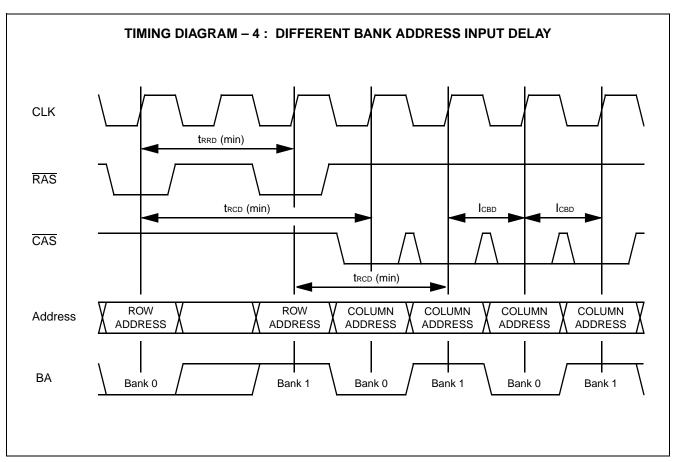

| RAS to RAS Bank Active Delay Time           |      | <b>t</b> rrd      | 20                      | _      | 20                      | _      | ns      |

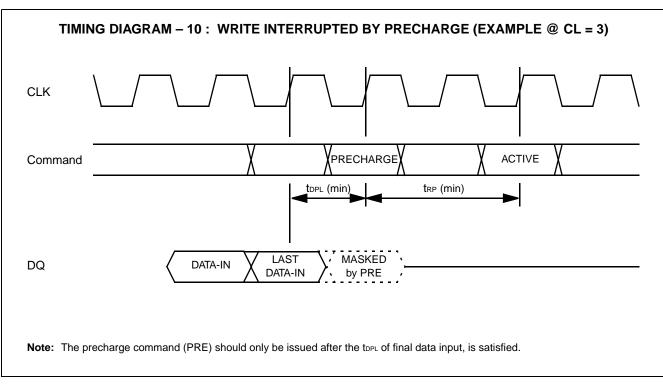

| Data-in to Precharge Lead Time              |      | <b>t</b> DPL      | 10                      | _      | 10                      | _      | ns      |

| Data-in to Active/Refresh<br>Command Period | CL=2 | t <sub>DAL2</sub> | 1 cyc + t <sub>RP</sub> | _      | 1 cyc + t <sub>RP</sub> | _      | ns      |

|                                             | CL=3 | <b>t</b> DAL3     | 2 cyc + t <sub>RP</sub> | _      | 2 cyc + t <sub>RP</sub> | _      | ns      |

| Mode Resister Set Cycle Time                |      | <b>t</b> RSC      | 20                      | _      | 20                      | _      | ns      |

### **CLOCK COUNT FORMULA** Note 13

$\label{eq:clock} \mbox{Clock} \geq \ \ \frac{\mbox{Base Value}}{\mbox{Clock Period}} \ \ \mbox{(Round off a whole number)}$

#### **LATENCY - FIXED VALUES**

(The latency values on these parameters are fixed regardless of clock period.)

| Parameter                                       | Notes  | Symbol            | MB81F64442C-102/-102L | MB81F64442C-103/-103L | Unit  |

|-------------------------------------------------|--------|-------------------|-----------------------|-----------------------|-------|

| CKE to Clock Disable                            |        | Іске              | 1                     | 1                     | cycle |

| DQM to Output in High-Z                         |        | lpqz              | 2 2                   |                       | cycle |

| DQM to Input Data Delay                         |        | IDQD              | 0                     | 0                     | cycle |

| Last Output to Write Command Delay              |        | lowd              | 2                     | 2                     | cycle |

| Write Command to Input Data<br>Delay            |        | lowd              | 0                     | 0                     | cycle |

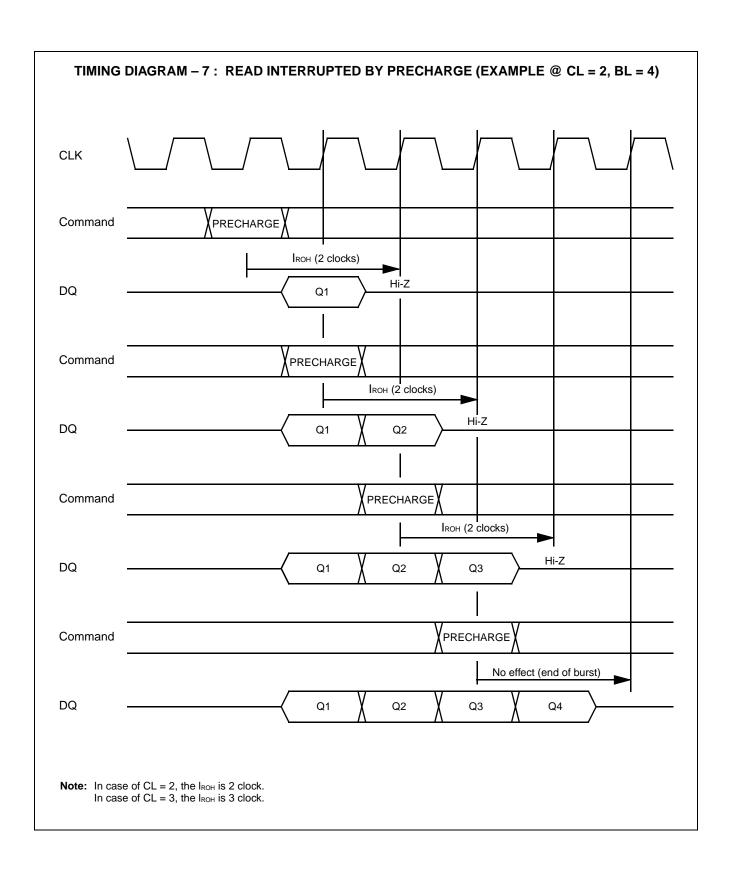

| Precharge to Output in High-Z Delay             | CL = 2 | I <sub>ROH2</sub> | 2                     | 2                     | cycle |

|                                                 | CL = 3 | Іпонз             | 3                     | 3                     | cycle |

| Burst Stop Command to<br>Output in High-Z Delay | CL = 2 | Івѕн2             | 2                     | 2                     | cycle |

|                                                 | CL = 3 | Івѕнз             | 3                     | 3                     | cycle |

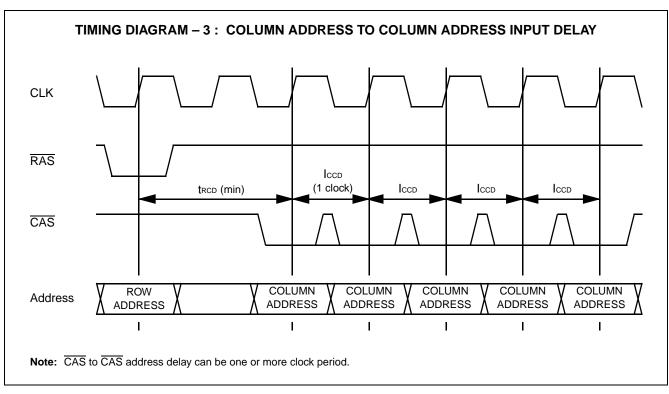

| CAS to CAS Delay (min)                          |        | Іссь              | 1                     | 1                     | cycle |

| CAS Bank Delay (min)                            |        | Ісво              | 1                     | 1                     | cycle |

# **Notes:** \*1. lcc depends on the output termination or load conditions, clock cycle rate, signal clocking rate; the specified values are obtained with the output open and no termination register.

- \*2. An initial pause (DESL or NOP) of 200 μs is required after power-up followed by a minimum of eight Auto-refresh cycles.

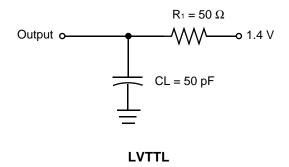

- \*3. AC characteristics assume  $t_T = 1$  ns and 50 pF of capacitive load.

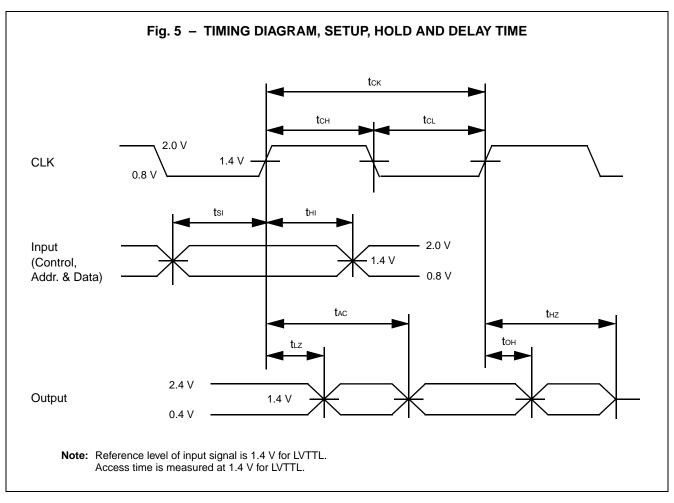

- \*4. 1.4 V is the reference level for measuring timing of input signals. Transition times are measured between V<sub>IH</sub> (min) and V<sub>IL</sub> (max). (See Fig. 5)

- \*5. Maximum value of CL = 2 depends on tck.

- \*6. tac also specifies the access time at burst mode except for first access.

- \*7. Specified where output buffer is no longer driven. toh, tlz, and thz define the times at which the output level achieves ±200 mV.

- \*8. Actual clock count of trc (Irc) will be sum of clock count of tras (Iras) and trp (Irp).

- \*9. Operation within the trcd (min) ensures that access time is detetermined by trcd (min) + trcd (max); If trcd is greater than the specified trcd (min), access time is determined by trcd.

- \*10. All base values are measured from the clock edge at the command input to the clock edge for the next command input. All clock counts are calculated by a simple formula: clock count equals base value divided by clock period (round off to a whole number).

Fig. 4 - EXAMPLE OF AC TEST LOAD CIRCUIT

Note: AC characteristics are measured in this condition. This load circuits are not applicable for VoH and VoL.

### **■ MODE REGISTER TABLE**

Notes: \*1. The latency of CKE (ICKE) is one clock.