### **Digital Deflection Controller**

**SDA 9064-5**

Preliminary Data NMOS IC

#### **Features**

- Pipeline processor structure controls deflection stages

- Raster alignment by keyboard or automatically

- Adaptable beam current compensation for picture height and width

- Protection input stops the exceeding

- For double the line frequency and 100-/120-Hz vertical frequency interlaced

| Туре       | Ordering Code | Package    |  |  |

|------------|---------------|------------|--|--|

| SDA 9064-5 | Q67100-H8382  | P-DIP-40-1 |  |  |

#### **Circuit Description**

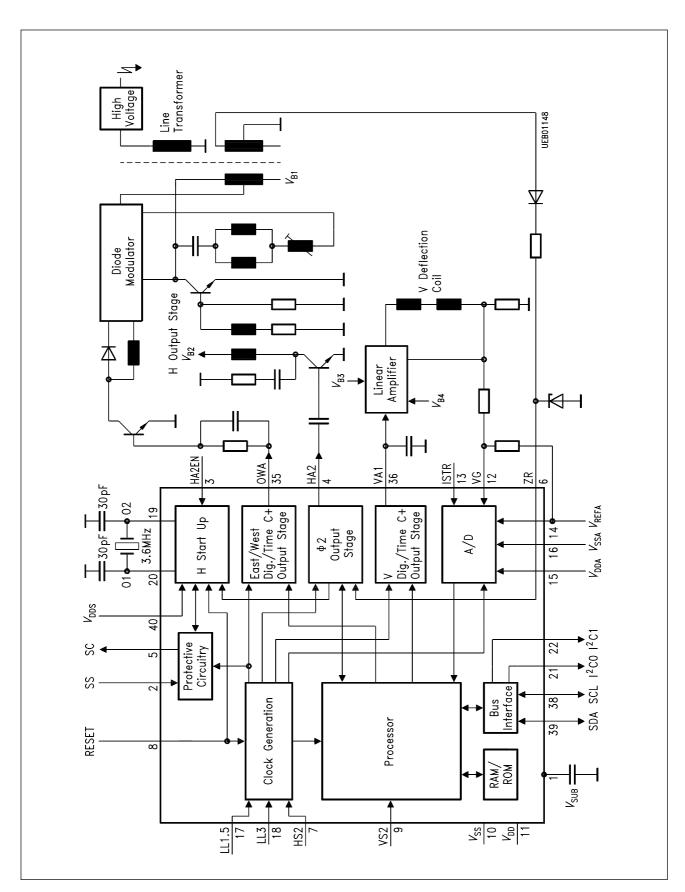

The DDC consists essentially of a processor with program ROM and RAM, ports for input and output signals and a clock rate divider that supplies the whole chip with clock signals.

The processor is specially manufactured for the arithmetic operations performed in the DDC. It operates according to the pipeline principle on account of the high requirements involved with regard to time. It has two 16-bit accumulators. The 16-bit data bus and the 7-bit address bus take care of the data traffic between the processor and the ports. The size of the static RAM is 96 x 16 bits; the program ROM can store 800 16-bit instructions.

The V port and the  $\Phi 2$  port comprise counters for coarse conversion and a chain of 32 resistors for amplitute quantization of fine conversion. The  $\Phi 2$  port further measures the position of the ZR pulses with respect to time and transfers measured data to the processor. The east/west port similarly has a counter for digital time conversion but manages without fine conversion.

The 9-bit analog-to-digital converter works on the principle of successive approximation using a capacitance field.

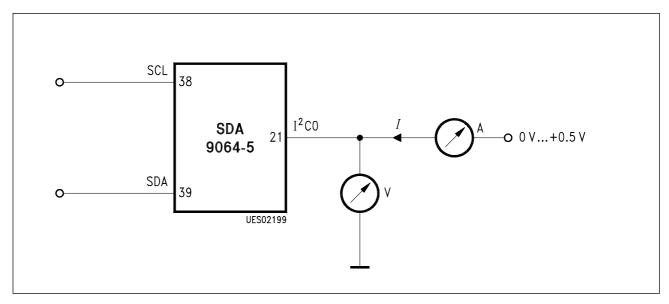

The I<sup>2</sup>C Bus interface makes it possible to read and modify deflection data in the RAM. The protective circuitry monitors inputs SS, ZR and HA2EN using comparators.

The start-up circuitry has its own power and clock pulse supply. It is therefore completely independent of the other DDC functions.

#### Description of the Signal and Data I/O of the Digital Deflection Controller

The digital deflection controller (DDC) generates horizontal-frequency, pulsewidth modulated control signals for external deflection output stages of color TV sets. The output signal for the horizontal deflection is phase-shifted, the signal for the east/west raster correction is parabolic and the signal for the vertical deflection is saw-tooth modulated. Signal computation is performed with data values from an internal memory that can be written by the I<sup>2</sup>C Bus. DDC is synchronized by means of a horizontal and a vertical input signal.

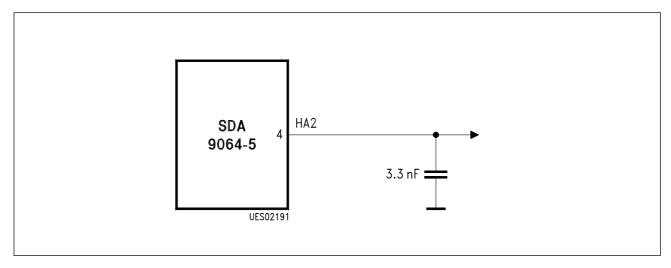

The HA2 output generates the control signals for a conventional horizontal output stage.

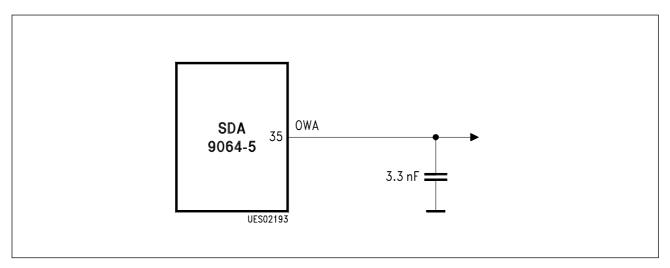

The east/west output drives the diode modulator via a switched small-signal transistor.

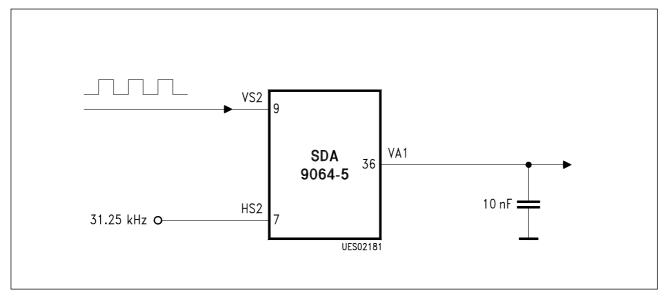

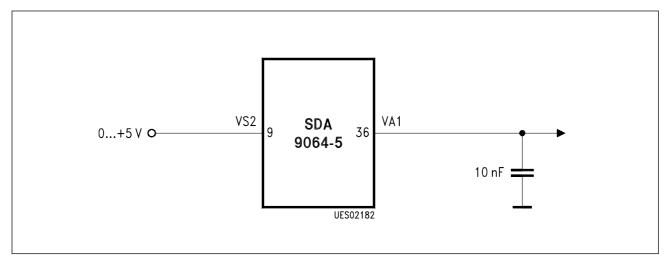

After the integration of the output signal a linear amplifier can be connected to the output VA1 to drive the V-output stage.

The above-mentioned data values which determine the raster are stored (system-specific for 45 AX picture tubes) in an integrated ROM for 50-Hz and 60-Hz vertical deflection frequencies. However, individual alignment is possible as well. The data obtained is written into a nonvolatile memory of the operating processor. During switch-on, the data is transferred via the I<sup>2</sup>C Bus to the deflection RAM in the DDC.

In addition, the variable storage time of the horizontal deflection stage transistor is compensated ( $\Phi$ 2 control loop), while the pulse duty factor of the driver-control signal remains constant. The horizontal deflection stage is switched off via a protective circuitry, when the voltage at input SS exceeds a given level.

The start-up circuitry supplies the horizontal deflection stage transistor with control signals in the standby mode, the switch-off phase, and during system clock failure.

The system includes a control loop with an analog-to-digital converter to stabilize the shape and amplitude of the vertical deflection current (V-feedback).

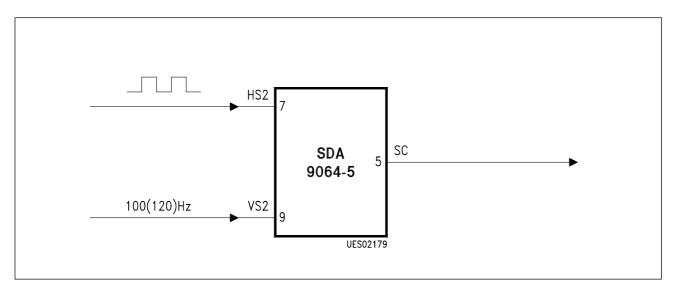

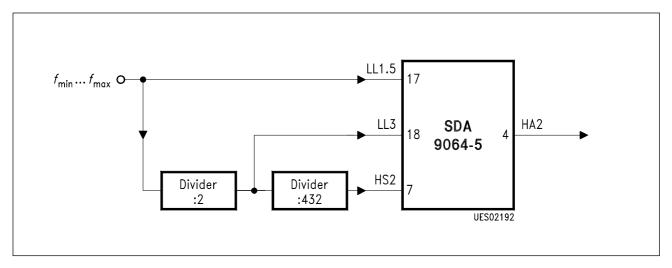

The input signals HS2 and VS2 are supplied with double the frequency from a TV-standard conversion circuitry.

The resolution enhancement filter of the VDA can be set via two outputs with the I<sup>2</sup>C Bus interface of the deflection controller.

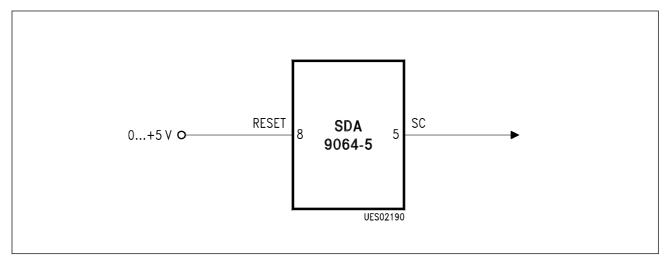

The DDC can be externally reset via a RESET input (with L level).

Deflection frequencies: 100/120-Hz field frequency, 31.25/31.5-kHz line frequency.

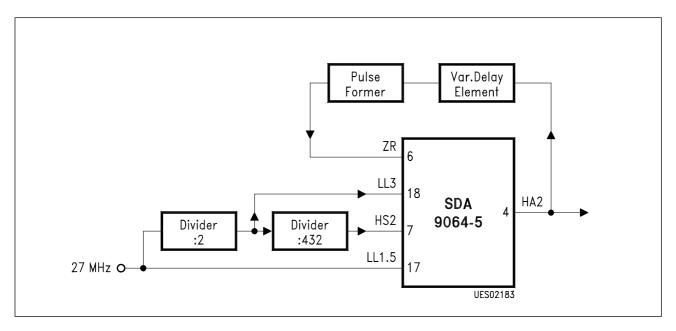

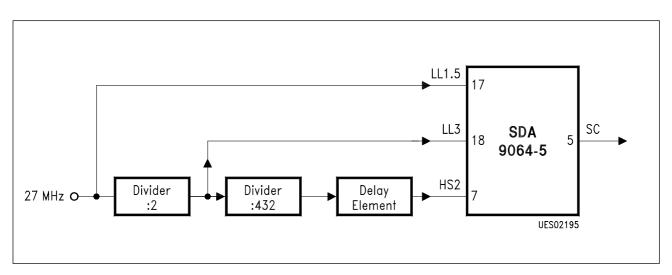

Figure 1 shows the block diagram with the interface.

#### **Description of the Start-Up Circuitry**

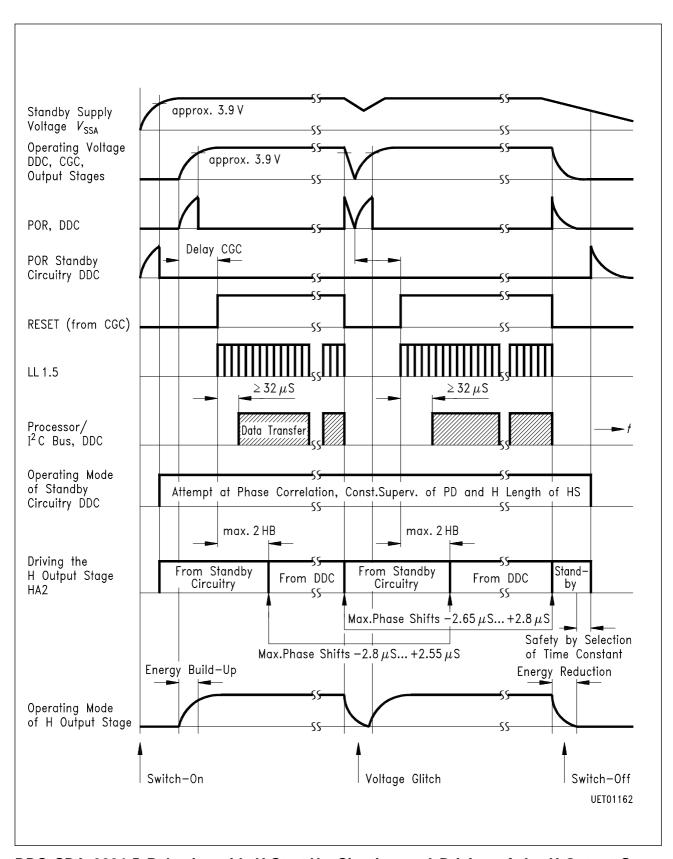

The horizontal start-up circuitry is provided with the supply voltage of the operating processor via pin  $V_{\rm DD\,S}$ . This supply voltage is already present in the standby mode of the TV set, although the supply voltage for the horizontal driver and horizontal output stages is not yet available.

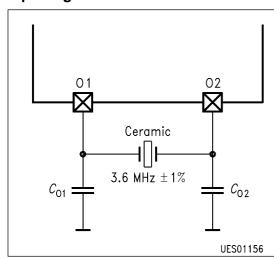

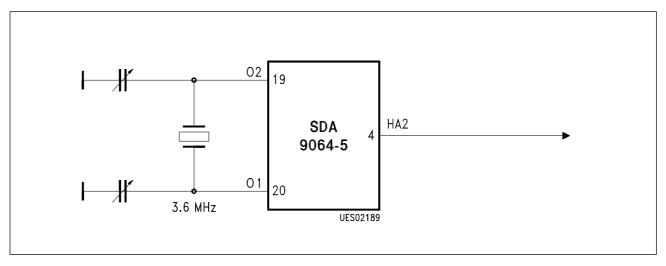

During standby mode, the HA2 output signal shape corresponds to the standard mode, however, without  $\Phi$ 2 function. The H-level duration is 14.5  $\mu$ s and the period ranges between 31.6 and 32.55  $\mu$ s, depending on the tolerance of the ceramic resonator ( $\pm$  1 %).

After the main supply voltage  $V_{\rm DD}$  has been switched on and the HA2 signals of the start-up circuitry have been correlated with the HA2 signals arriving from the DDC ( $\Phi$ 2 circuitry), the standard mode is selected within one frame period (max. shift is – 2.8 to + 2.55  $\mu$ s including all tolerances), if the following requirements are met:

- The DDC supplies the start-up circuitry with HA2 signals satisfactory with respect to the period and H-level duration

- The ZR-pulse threshold is not exceeded at pin SS

- The supply voltage at the horizontal driver exceeds the minimal value (threshold at pin HA2EN, if connected).

The standby mode is selected immediately in response to a drop in the DDC-main supply voltage and concomitant max. phase shifts of -2.65 to +2.8  $\mu$ s.

The maximum period duration of HA2 with reference to LH junctions may be 36  $\mu$ s in the event of faults (e.g. failure of LL1.5, malfunctions in the DDC with the exception of the start-up circuitry.

The switch-off time constant of  $V_{\rm DD\,S}$  should be larger than that of  $V_{\rm DD}$ , ensuring that the HA2 pulses are continuously supplied during a voltage glitch of  $V_{\rm DD}$  and exceed the duration of the horizontal output stage voltage supply during switch-off.

During all operating modes, HA2 will be high for the duration of the ZR pulse.

#### I<sup>2</sup>C Bus Protocol

The DDC includes a I<sup>2</sup>C Bus port designed for the following functions:

- Slave receiver

- Slave transmitter

Since the DDC does not include a master function, data transfers are always initiated and controlled by an external bus master. The actual data transfer is executed by the processor of the DDC serving its  $I^2C$  Bus port every 32  $\mu s$  and receiving or transferring data in accordance with the operating mode set.

A maximum of 127 memory locations is available for read/write operations via the processor of the DDC.

SDA 9064-5

## **SIEMENS**

During the slave-receiver mode, the DDC accepts data from the I<sup>2</sup>C Bus master. A bus telegram transmitted in this mode is characterized by the following:

#### Slave Receiver

During the slave-transmitter mode, data is transmitted from the DDC to the  $I^2C$  Bus master with the  $I^2C$  Bus master clock. The first data byte to be transmitted is always the status word.

A bus telegram transmitted in the slave-transmitter mode is characterized by the following:

#### **Slave Transmitter**

| STA | Slave-Addr | R | Ack | Status | Ack | Data-H | Ack | Data-L | NA | STOP |

|-----|------------|---|-----|--------|-----|--------|-----|--------|----|------|

|     |            |   |     |        |     |        |     |        |    |      |

STA = Start identification R = Read/write bit = high

Ack = Acknowledge STOP = Stop identification W = Read/write bit = low NA = No acknowledge

The slave address of the DDC is 1000110. The following information can be received by the slave receiver during this operating mode:

Sub-addresses 0A to 29: 32 bytes for raster

alignment at 100 and 120 Hz

vertical deflection

frequency

Sub-addresses 2A and 2B: 2 control words with control

bits for DDC and VDA

The following information can be queried by the DDC during the slave-transmitter mode:

- Status word whose bits identify the status of the DDC

- Fixed raster data from the ROM

- Raster alignment data from the internal RAM

**Tables 1 to 4** list the sub-addresses, name and effect of the individual data. The raster size setting (e.g. east/west pin cushion with EP) usually influences other raster characteristics (e.g. picture width). This influence can be avoided by changing other data values accordingly; refer to networking list shown in **table 5**. The table lists the useful steps of the data values to be adjusted and the necessary adaptation of the other data (per step width) for non-iterative setting.

**SDA 9064-5**

## **SIEMENS**

The adjustment program INFRARAST in conjunction with the microcontroller SDA 20160 as I<sup>2</sup>C Bus master of the TV receiver provides for user-friendly setting via remote control.

When the supply voltage  $V_{\rm DD}$  is not present, pins SCL and SDA are in high-impedance state.

When the clock LL1.5 is not present, the I<sup>2</sup>C Bus port is without function and SCL and SDA are in high-impedance state.

When the supply voltage  $V_{\rm DD}$  is switched on (after internal power ON reset), data can be transferred via the I<sup>2</sup>C Bus port after approx. 32  $\mu$ s.

Table 1 I<sup>2</sup>C Bus Data of the DDC

| Sub-      | Data   |        |        |        |        |        |        |        | Definition                                                                                |

|-----------|--------|--------|--------|--------|--------|--------|--------|--------|-------------------------------------------------------------------------------------------|

| addresses | D 7    | D 6    | D 5    | D 4    | D 3    | D 2    | D 1    | D 0    |                                                                                           |

| 0A        | HP 5   | HP 4   | HP 3   | HP 2   | HP 1   | HP 0   | Х      | Х      | Horizontal picture position                                                               |

| 0B        | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      | None                                                                                      |

| 0C        | VSC 55 | VSC 54 | VSC 53 | VSC 52 | VSC 51 | VSC 50 | Х      | Х      | Vertical S-correction during 100-Hz operating mode                                        |

| 0D        | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      | None                                                                                      |

| 0E        | VSC 65 | VSC 64 | VSC 63 | VSC 62 | VSC 61 | VSC 60 | Х      | Х      | Vertical S-correction during 120-Hz operating mode                                        |

| 0F        | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      | None                                                                                      |

| 10        | VF 63  | VF 62  | VF 61  | VF 60  | VF 511 | VF 510 | VF 509 | VF 508 | Vertical upper linearity; 120-Hz adjustment values VF 6x and                              |

| 11        | VF 507 | VF 506 | VF 505 | VF 504 | VF 503 | VF 502 | VF 501 | VF 500 | - 100-Hz absolute values VF 5xx;<br>120-Hz absolute value<br>VF 6xx = VF 5xx + 16 · VF 6x |

| 12        | VC 3   | VC 2   | VC 1   | VC 0   | VS 511 | VS 510 | VS 509 | VS 508 | Picture height compensation VC for evaluating the beam                                    |

| 13        | VS 507 | VS 506 | VS 505 | VS 504 | VS 503 | VS 502 | VS 501 | VS 500 | current information ISTR and vertical picture position VS                                 |

| 14        | HC 3   | HC 2   | HC 1   | HC 0   | PH 511 | PH 510 | PH 509 | PH 508 | Picture width compensation HC for evaluating the beam current                             |

| 15        | PH 507 | PH 506 | PH 505 | PH 504 | PH 503 | PH 502 | PH 501 | PH 500 | information ISTR and picture height PH                                                    |

| 16        | VL 515 | VL 514 | VL 513 | VL 512 | VL 511 | VL 510 | VL 509 | VL 508 | Vertical linearity during 100-Hz                                                          |

| 17        | VL 507 | VL 506 | VL 505 | VL 504 | VL 503 | VL 502 | VL 501 | VL 500 | operating mode                                                                            |

| 18        | EWC 55 | EWC 54 | EWC 53 | EWC 52 | EWC 51 | EWC 50 | PW 59  | PW 58  | East/west raster correction in the corners at 100-Hz operating                            |

| 19        | PW 57  | PW 56  | PW 55  | PW 54  | PW 53  | PW 52  | PW 51  | PW 50  | mode EWC and picture width at 100-Hz operating mode PW                                    |

Table 1 I2C Bus Data of the DDC (cont'd)

| Sub-      |        |        |        | Da     | ıta    |        |                   |                   | Definition                                                                               |  |

|-----------|--------|--------|--------|--------|--------|--------|-------------------|-------------------|------------------------------------------------------------------------------------------|--|

| addresses | D 7    | D 6    | D 5    | D 4    | D 3    | D 2    | D 1               | D 0               |                                                                                          |  |

| 1A        | EP 515 | EP 514 | EP 513 | EP 512 | EP 511 | EP 510 | EP 509            | EP 508            | East/west parabola during                                                                |  |

| 1B        | EP 507 | EP 506 | EP 505 | EP 504 | EP 503 | EP 502 | EP 501            | EP 500            | 100-Hz operating mode                                                                    |  |

| 1C        | TR 515 | TR 514 | TR 513 | TR 512 | TR 511 | TR 510 | TR 509            | TR 508            | East/west trapezoidal correction during 100-Hz                                           |  |

| 1D        | TR 507 | TR 506 | TR 505 | TR 504 | TR 503 | TR 502 | TR 501            | TR 500            | operating mode                                                                           |  |

| 1E        | Х      | Χ      | Х      | Х      | VS 611 | VS 610 | VS 609            | VS 608            | Vertical picture position during                                                         |  |

| 1F        | VS 607 | VS 606 | VS 605 | VS 604 | VS 603 | VS 602 | VS 601            | VS 600            | 120-Hz operating mode                                                                    |  |

| 20        | EHTH 3 | EHTH 2 | EHTH 1 | EHTH 0 | PH 611 | PH 610 | PH 609            | PH 608            | Dynamic picture width compensation EHTH for evaluating the beam current information ISTR |  |

| 21        | PH 607 | PH 606 | PH 605 | PH 604 | PG 603 | PH 602 | PH 601            | PH 600            | and picture height during 120-Hz operating mode PH                                       |  |

| 22        | VL 615 | VL 614 | VL 613 | VL 612 | VL 611 | VL 610 | VL 609            | VL 608            | Vertical linearity during 120-Hz                                                         |  |

| 23        | VL 607 | VL 606 | VL 605 | VL 604 | VL 603 | VL 602 | VL 601            | VL 600            | operating mode                                                                           |  |

| 24        | EWC 65 | EWC 64 | EWC 63 | EWC 62 | EWC 61 | EWC 60 | PW 69             | PW 68             | East/west raster correction in the corners during 120-Hz operating mode EWC and          |  |

| 25        | PW 67  | PW 66  | PW 65  | PW 64  | PW 63  | PW 62  | PW 61             | PW 60             | picture width during 120-Hz operating mode PW                                            |  |

| 26        | EP 615 | EP 614 | EP 613 | EP 612 | EP 611 | EP 610 | EP 609            | EP 608            | East/west parabola during                                                                |  |

| 27        | EP 607 | EP 606 | EP 605 | EP 604 | EP 603 | EP 602 | EP 601            | EP 600            | 120-Hz operating mode                                                                    |  |

| 28        | TR 615 | TR 614 | TR 613 | TR 612 | TR 611 | TR 610 | TR 609            | TR 608            | East/west trapezoidal                                                                    |  |

| 29        | TR 607 | TR 606 | TR 605 | TR 604 | TR 603 | TR 602 | TR 601            | TR 600            | correction during 100-Hz operating mode                                                  |  |

| 2A        | Х      | Х      | Х      | Х      | Х      | Х      | I <sup>2</sup> C1 | I <sup>2</sup> C0 | Control word 1, control bits for outputs I <sup>2</sup> C0 1                             |  |

| 2B        | Х      | Х      | EFS    | FS     | RAM    | Х      | Х                 | Х                 | Control word 2, refer to table 2                                                         |  |

| C4-CB     | X      | X      | X      | X      | X      | X      | X                 | X                 | These adresses are reserved for test operation and must not be used                      |  |

| CC-CD     | Х      | X      | Х      | X      | X      | Х      | Х                 | Х                 | Switch back to normal operating mode                                                     |  |

|           | PONRES | HOFF   | Х      | Х      | Х      | Х      | Х                 | FD                | Status word, refer to table 3                                                            |  |

Table 2 Control Word 2

|     | 0                          | 1                        |  |  |  |

|-----|----------------------------|--------------------------|--|--|--|

| EFS | 100/120-Hz operating mode  |                          |  |  |  |

|     | dedicted by the DDC        | determined by the FS bit |  |  |  |

| FS  | 100-Hz operating mode      | 120-Hz operating mode    |  |  |  |

| RAM | DDC uses fixed raster data |                          |  |  |  |

|     | from the internal ROM      | from the internal RAM    |  |  |  |

Table 3

Status Word 2

|        | 0                         | 1                                      |  |  |

|--------|---------------------------|----------------------------------------|--|--|

| PONRES | Status wo                 | ord is read                            |  |  |

|        | after reset of bus master | after each DDC reset                   |  |  |

| FD     | DDC recognized 100 Hz     | 120 Hz recognized                      |  |  |

| HOFF   | Standard HA2 function     | HA2 set "high" by protective circuitry |  |  |

Table 4

Effect of the Raster Alignment Data

| Sub-<br>addresses | Data Value    | Range (in decimals) | Effect                                                                                             |

|-------------------|---------------|---------------------|----------------------------------------------------------------------------------------------------|

| 0A                | HP 5 HP 0     | - 32 <b>+</b> 31    | Picture to the right to the left                                                                   |

| 0C                | VSC 55 VSC 50 | - 32 <b>+</b> 31    | S-correction max. neg max. positive                                                                |

| 0E                | VSC 65 VSC 60 | - 32 <b>+</b> 31    | S-correction max. neg max. positive                                                                |

| 10                | VF 63 VF 60   | -8 + <b>7</b>       | Line spacing small on top large on top (refer to table 1)                                          |

| 10 and 11         | VF 511 VF 500 | 2400 3600           | Line spacing small on top large on top (refer to table 1)                                          |

| 12                | VC 3 VC 0     | -8 O                | V-deflection current decreases considerably/<br>does not decrease when increasing beam<br>current  |

| 12 and 13         | VS 511 VS 500 | 2600 3400           | Picture position bottom top                                                                        |

| 14                | HC 3 HC 0     | -8 O                | H-deflection current decreasing considerably/<br>does not decrease when increasing beam<br>current |

| 14 and 15         | PH 511 PH 500 | 1450 2150           | Picture height min max.                                                                            |

| 16 and 17         | VL 515 VL 500 | - 32768<br>+ 32767  | Line spacing bottom > top top > bottom                                                             |

| 18                | EWC 55 EWC 50 | - 32 <b>+</b> 31    | Vertical lines in the corners facing max. outward max. inward                                      |

| 18 and 19         | PW 59 PW 50   | 0 1023              | Picture width max min., PW must be > 0, when HC is to be effective                                 |

| 1A and 1B         | EP 515 EP 500 | - 32768<br>+ 32767  | East-West raster max. concave max. convex                                                          |

| 1C and 1D         | TR 515 TR 500 | - 32768 0           | Picture wider narrower on bottom                                                                   |

| 1E and 1F         | VS 611 VS 600 | 2600 3400           | Picture position bottom top                                                                        |

| 20                | EHTH 3 EHTH 0 | -8 O                | Considerable no reduction in H-deflection current with white H stripe                              |

| 20 and 21         | PH 611 PH 600 | 1450 2150           | Picture height min max.                                                                            |

| 22 and 23         | VL 615 VL 600 | - 32768<br>+ 32767  | Line spacing bottom > top top > bottom                                                             |

| 24                | EWC 65 EWC 60 | - 32 <b>+</b> 31    | Vertical lines in the corners facing max. outward max. inward                                      |

| 24 and 25         | PW 69 PW 60   | 0 1023              | Picture width max min., PW must be > 0, HC is to be effective                                      |

Table 4

Effect of the Raster Alignment Data (cont'd)

| Sub-<br>addresses | Data Value    | Range (in decimals) | Effect                               |

|-------------------|---------------|---------------------|--------------------------------------|

| 26 and 27         | EP 615 EP 600 | - 32768<br>+ 32767  | East-West raster max. concave convex |

| 28 and 29         | TR 615 TR 600 | <b>– 32768</b> 0    | Picture wider narrower on bottom     |

## **Networking Lists**

Table 5.1 East/West Data 100 Hz

| Setting:                                       | Changes: | EWC 5 | EP 5 | TR 5         | PW 5 |

|------------------------------------------------|----------|-------|------|--------------|------|

| (increase) picture width                       |          | _     | _    | _            | -2   |

| Trapezoidal correction (smaller at the bottom) |          | _     | _    | 102          | - 4  |

| (Magnify) parabola                             |          | _     | 260  | - 634        | 12   |

| Corners (facing inward)                        |          | 1     | 760  | <b>- 618</b> | 6    |

Table 5.2 East/West Data 120 Hz

| Setting:                                       | Changes: | EWC 6 | EP 6 | TR 6         | VF 6 PW 6 |

|------------------------------------------------|----------|-------|------|--------------|-----------|

| (increase) picture width                       |          | _     | _    | _            | -2        |

| Trapezoidal correction (smaller at the bottom) |          | _     | _    | 125          | - 4       |

| (magnify) parabola                             |          | _     | 382  | <b>- 782</b> | 12        |

| Corners (facing inward)                        |          | 2     | 1073 | <b>- 732</b> | 6         |

Table 5.3 Vertical Data 100 Hz

| Setting:                      | Changes: | VSC 5 | VL 5  | PH 5 | VF 5 | VS 5 |

|-------------------------------|----------|-------|-------|------|------|------|

| Picture position (to the top) |          | _     | _     | _    | _    | 16   |

| (Magnify) picture height      |          | _     | _     | 8    | 12   | _    |

| Linearity (top > bottom)      |          | _     | 64    | _    | 12   | - 26 |

| (Magnify) S-correction        |          | 1     | - 283 | 19   | 11   | _    |

Table 5.4 Vertical Data 120 Hz

| Setting:                      | Changes: | VSC 6 | VL 6         | PH 6 | VF 6 PW 6 | VS 6 |

|-------------------------------|----------|-------|--------------|------|-----------|------|

| Picture position (to the top) |          | _     | _            | _    | _         | 16   |

| (Magnify) picture height      |          | _     | _            | 8    | 12/16     | _    |

| Linearity (top > bottom)      |          | _     | 93           | _    | 12/16     | - 26 |

| (Magnify) S-correction        |          | 2     | <b>– 475</b> | 19   | 11/16     | _    |

**Block Diagram**

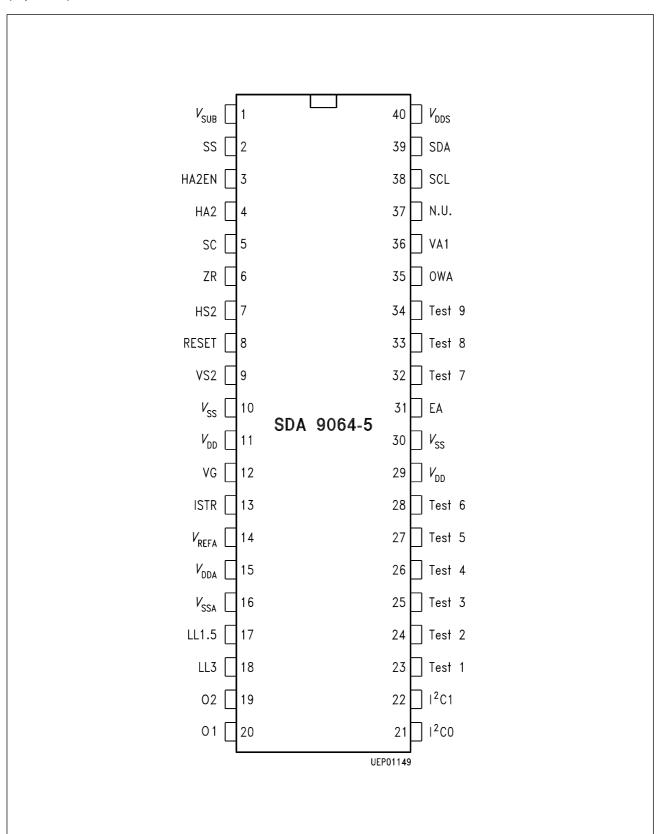

## **Pin Configuration**

(top view)

## **Pin Definitions and Functions**

| Pin | Symbol    | Function                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

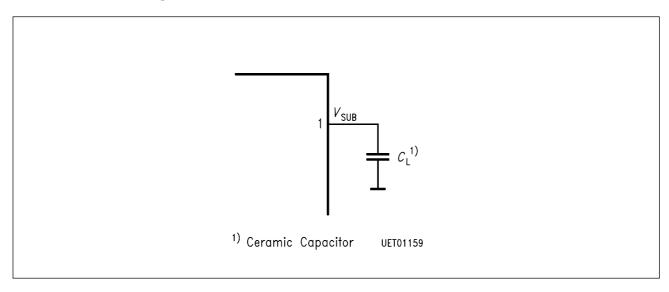

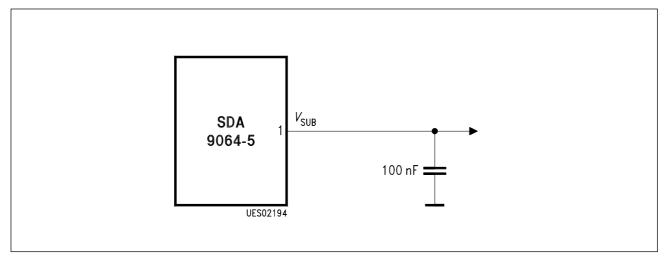

| 1   | $V_{SUB}$ | Substrate voltage            | Substrate voltage pin to connect an external smoothing capacitor for the internally generated substrate voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

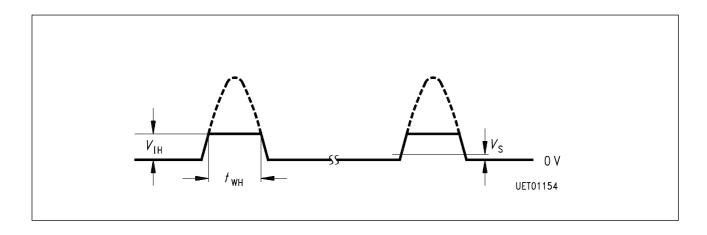

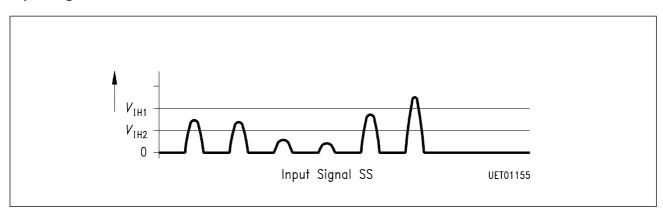

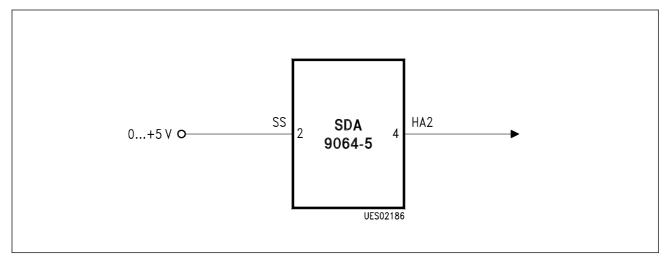

| 2   | SS        | Protective circuitry         | The protective circuitry switches off the horizontal output stage and blanks the picture tube. Usually a signal derived from the line flyback is injected at SS. If the input signal exceeds a given upper level, the blanking mode is enabled (sandcastle pulse with $V_{\rm OH 1}$ level) and the output HA2 goes to high. If the input signal falls below a given lower level at SS, only the blanking mode is enabled. After the protective circuitry responds via $V_{\rm IH 1}$ , POR should be enabled (switch ON/OFF of $V_{\rm DD S}$ ). |

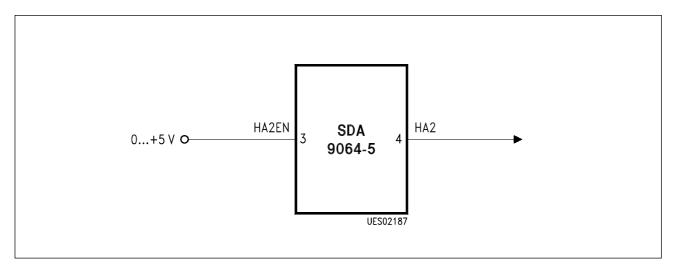

| 3   | HA2EN     |                              | Enable/disable of HA2 pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

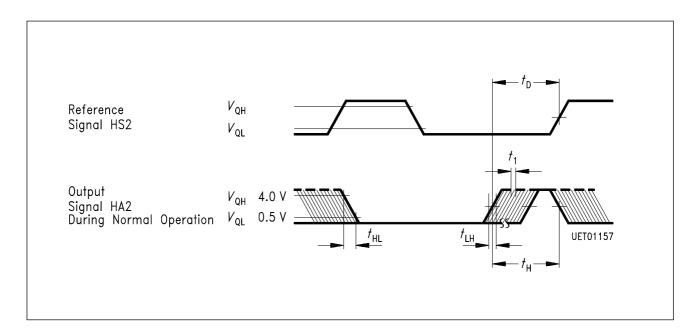

| 4   | HA2       | Output horizontal driver     | The L/H transition initiates the line retrace. The output stage transistor transfer delay is compensated $(\Phi_2)$ . The pulse duty factor is kept constant. During all operating modes, HA2 is high for the duration of the ZR signal.                                                                                                                                                                                                                                                                                                          |

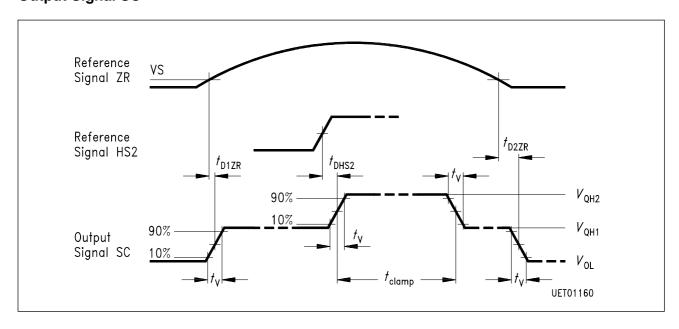

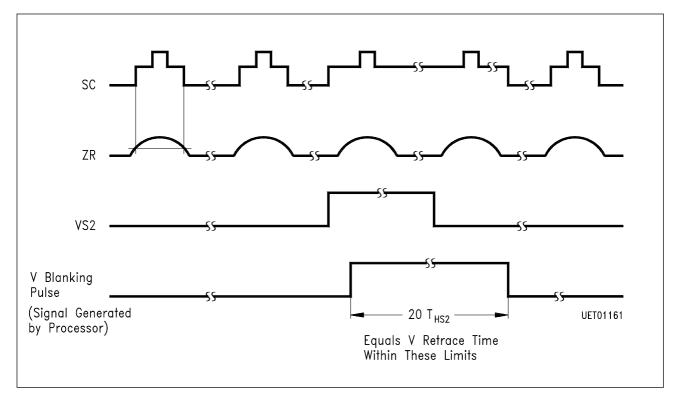

| 5   | SC        | Sandcastle                   | The combined key pulse SC is generated from the horizontal and vertical flyback and the burst. The pulse can be switched to continuous blanking with the protective circuitry. The pulse is a two-level pulse.                                                                                                                                                                                                                                                                                                                                    |

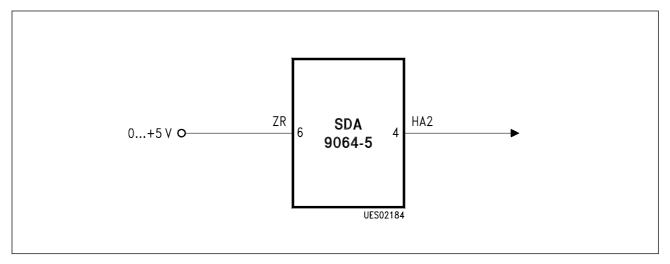

| 6   | ZR        | Line retrace input           | The signal voltage for this input is derived from the horizontal deflection stage. The behavior of the signal voltage corresponds to the voltage at the horizontal deflection coil. The control signal for the horizontal deflection stage (HA2) is controlled in such a manner that the input signal ZR arrives at a certain location in the blanking period of the CVBS signal.                                                                                                                                                                 |

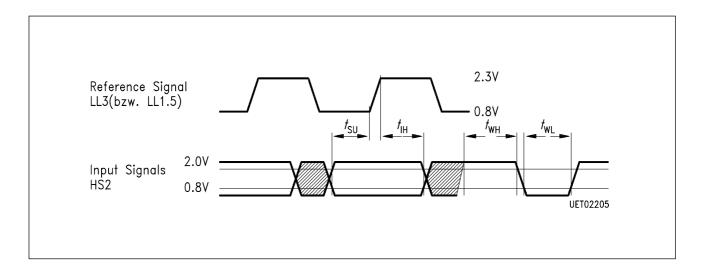

| 7   | HS2       | Horizontal synchronous pulse | The HS2 pulse is supplied by the TV-standard conversion circuitry and is used as line reference signal.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Function                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | RESET             | Input for external reset signal          | The external RESET as well as power-on reset are effective in the following sections: start-up circuitry, clock divider, processor, program ROM, $\Phi_2$ circuitry, A/D converter. The IC goes into the 100-Hz mode and into the ROM mode of the deflection data. (The ROM mode is retained until the RAM mode is selected via the bus interface). The blanking mode is enabled via output SC. The start-up circuitry goes into the standby mode when $V_{\rm DDS}$ is switched on or during external RESET. The HA2 pulses are present during an external RESET. The RAM and the OW port are not reset. The external RESET does not affect the $\rm I^2C$ Bus port, since the port is brought into a defined state each time it is addressed via the $\rm I^2C$ Bus interface. However, the POR bit is set in the status word. The REF outputs are not influenced by external RESET. |

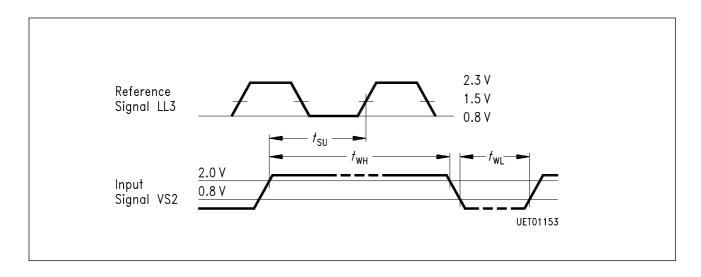

| 9   | VS2               | Vertical synchronous pulse               | The input VS2 is supplied by a pulse from the TV-standard conversion circuitry, which is used as picture reference signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10  | $V_{\mathtt{SS}}$ |                                          | Ground potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11  | $V_{DD}$          |                                          | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12  | VG                | Vertical feedback input                  | The voltage drop at the feedback resistor which is proportional to the current flowing through the vertical deflection coils is used as input signal. The vertical current is adjusted to a given nominal value with this signal. Continuous blanking will be enabled via the output SC when the vertical saw-tooth current is missing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13  | ISTR              | Input/beam<br>current of picture<br>tube | The voltage signal proportional to the beam current is used as input signal for the following purpose: By means of beam currents differing in value (change in image brightness), the high voltage is varied and thus also the deflection angle of the beam which determines the modulation of the picture width and height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

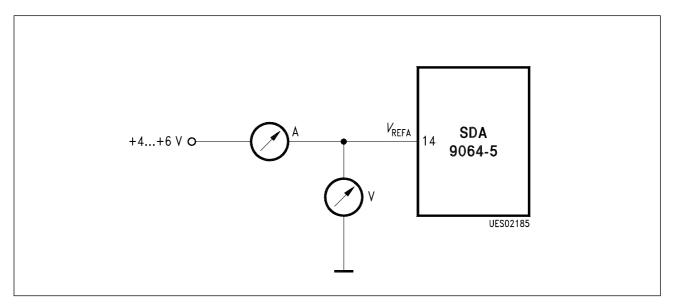

| 14  | $V_{REFA}$        |                                          | Reference voltage for A/D converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15  | $V_{DDA}$         |                                          | Supply voltage for A/D converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16  | $V_{\sf SSA}$     |                                          | Ground potential for A/D converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

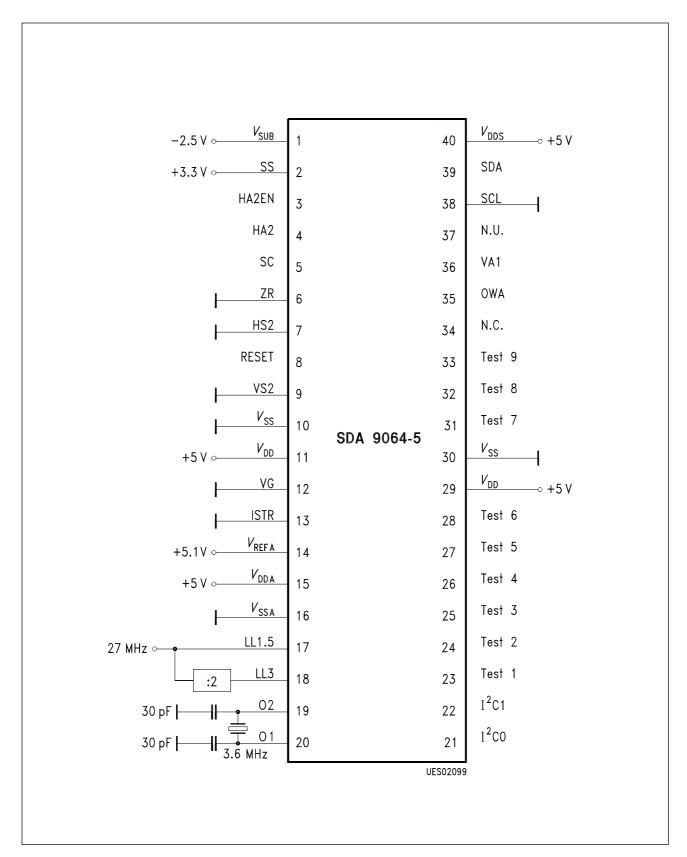

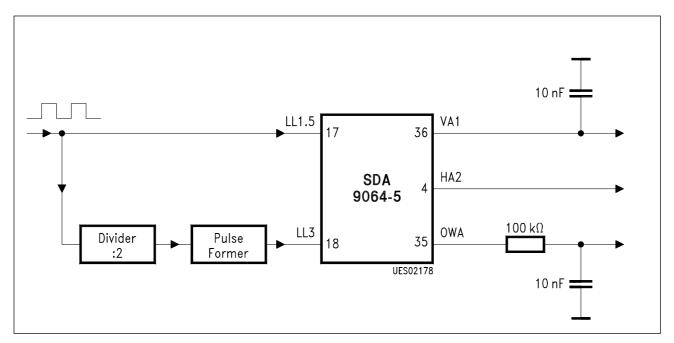

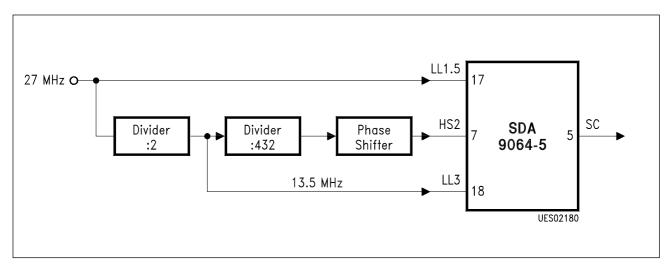

| 17  | LL1.5             |                                          | 27-MHz system clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18  | LL3               |                                          | 13.5-MHz-clock signal from CGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

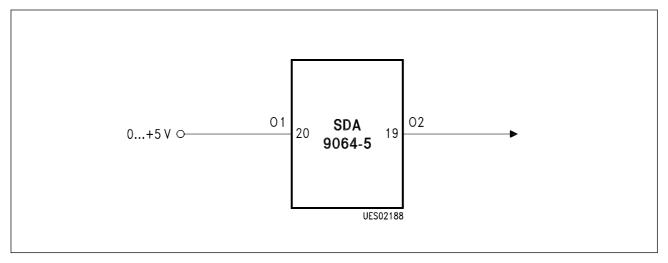

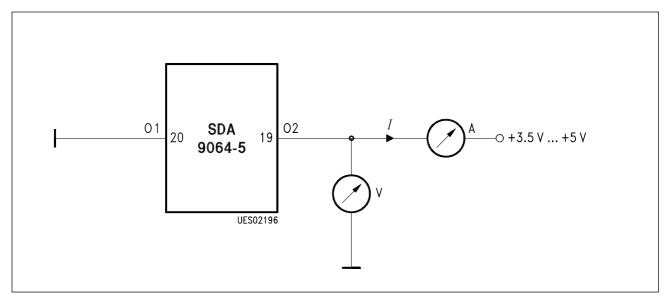

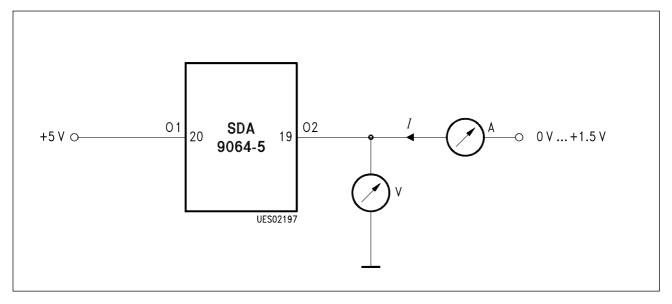

| 19  | O2                |                                          | Oscillator output for start-up circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20  | O1                |                                          | Oscillator input for start-up circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Pin Definitions and Functions (cont'd)

| Pin                              | Symbol                                    | Function                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|-------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

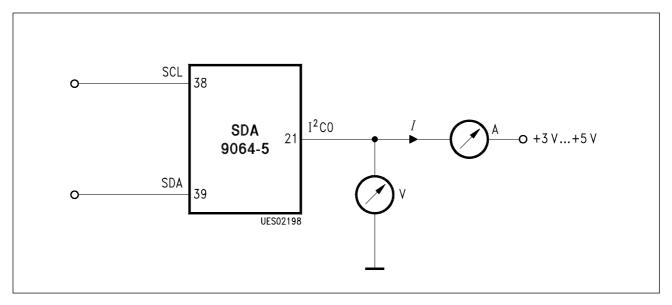

| 21<br>22                         | I <sup>2</sup> C0<br>I <sup>2</sup> C1    |                                    | General purpose output ports controlled by I <sup>2</sup> C Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23<br>24<br>25<br>26<br>27<br>28 | Test 1 Test 2 Test 3 Test 4 Test 5 Test 6 | Test                               | Do not connect pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 29                               | $V_{	extsf{DD}}$                          |                                    | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30                               | $V_{	t SS}$                               |                                    | Ground potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31<br>32<br>33                   | Test 7<br>Test 8<br>Test 9                | Test                               | } Do not connect pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 34                               | N.C.                                      |                                    | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

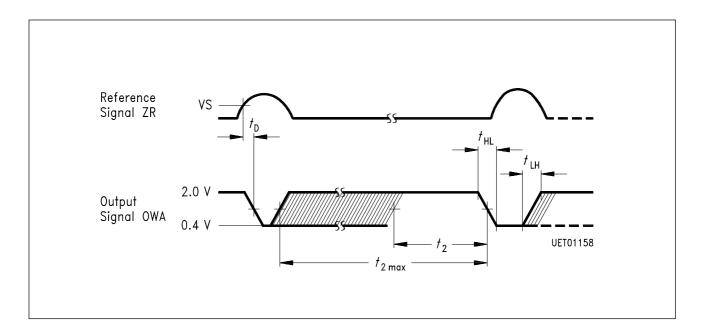

| 35                               | OWA                                       | Output east/west raster correction | The course of the pulse duration of the PDM signal over the picture period is that of a parabola. The course of the pulse duration is established primarily by the programmed deflection data.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 36                               | VA1                                       | Vertical<br>deflection 1           | The saw-tooth signal required by the analog vertical output stage is generated in a digital time converter which effects the conversion of a binary data word into a pulse duty factor. An increase of resolution by the factor of 32 is effected by amplitute quantization during the rising edge of the PDM signal within a clock period $(1/f_T)$ . By connecting an external capacitor, the saw-tooth voltage for the vertical output stage is generated.                                                                                                                                            |

| 37                               | N.U.                                      | not used                           | Do not connect pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 38<br>39                         | SCL<br>SDA                                | I²C Bus<br>∫ interface             | The data traffic between SDA 9064-5 and its environment is processed on the basis of the I <sup>2</sup> C Bus standard via a 2-wire interface. The interface of the SDA 9064-5 has been designed only for the slave function. The SDA 9064-5 can be addressed as transmitter or receiver. A message transmitted via the I <sup>2</sup> C Bus is defined by a start and a stop identification. The actual message comprises one or several telegrams which can be separated by repeating the start condition. A telegram consists of data with a 2-byte organization, an address byte, and a status byte. |

| 40                               | $V_{	extsf{DD}	extsf{S}}$                 |                                    | Standby supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol           | Lin   | Unit |     |

|-------------------------------|------------------|-------|------|-----|

|                               |                  | min.  | max. |     |

| Input voltage                 | $V_{IM}$         | - 0.5 | 6.0  | V   |

| Supply voltage                | $V_{	extsf{DD}}$ | - 0.3 | 6.0  | V   |

| Substrate voltage             | $V_{SUB}$        | - 3.2 | 0    | V   |

| Total power dissipation       | $P_{tot}$        |       | 1.7  | W   |

| Ambient temperature range     | $T_{A}$          | 0     | 70   | °C  |

| Storage temperature range     | $T_{ m stg}$     | - 55  | 125  | °C  |

| Thermal resistance system-air | $R_{th\;SA}$     |       | 36   | K/W |

#### **Characteristics**

$T_{\rm A}$  = 25 °C (all voltages are referred to  $V_{\rm SS}$ )

| Parameter                                                                                                                    | Symbol                                          | Limi                 | Limit Values      |                            |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------|-------------------|----------------------------|--|

|                                                                                                                              |                                                 | min.                 | max.              |                            |  |

| Supply voltage                                                                                                               | $V_{DD}{}^{4)}$                                 | 4.5                  | 5.5<br>300        | V<br>mA                    |  |

| Standby supply voltage for start-up circuitry                                                                                | $V_{ m DDS}^{ m 1)}$                            | 4.5                  | 5.5<br>15         | V<br>mA                    |  |

| Supply voltage for A/D converter                                                                                             | $V_{	extsf{DDA}} \ I_{	extsf{DDA}}$             | 4.5                  | 5.5<br>1.5        | V<br>mA                    |  |

| Ripple against $V_{\rm SSA}$                                                                                                 |                                                 |                      | 0.5               | mV                         |  |

| Substrate voltage at pin for connecting an external smoothing capacitor                                                      | $V_{ m SUB}^{ m 2)}$                            | - 3                  | - 2<br>100        | V<br>μA                    |  |

| Ripple against $V_{SSA}$                                                                                                     |                                                 |                      | 50                | mV                         |  |

| Ambient temperature range                                                                                                    | $T_{A}$                                         | 0                    | 70                | °C                         |  |

| Input currents Pin 3, 6, 8, 17, 20, 38, 39 Pin 7, 9, 12, 13, 18 Pin 2 Pin 6, 17, 20, 38, 39 Pin 2, 3, 8, 12, 13 Pin 7, 0, 18 | $I_{ m IH}$ $I_{ m IH}$ $I_{ m IL}$ $I_{ m IL}$ | 100<br>- 10<br>- 100 | 10<br>100<br>1000 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |  |

| Pin 7, 9, 18                                                                                                                 | $I_{IL}$                                        | - 1000               | <b>– 10</b>       | μA                         |  |

The voltage must have reached the required operating level prior to connecting the supply voltages for  $V_{\rm DD}$  and the H-output stage. In addition, the voltage must glitch-free and switched off only after the H-supply voltage has been deactivated.

<sup>2)</sup> Internally generated, however, can also be connected externally.

The  $I_{\rm DDS}$  feedback current flows across pin 10.  $V_{\rm DD}$  must be switched on and off without contact chatter.

#### Characteristics (cont'd)

$T_{\rm A}$  = 25 °C;  $V_{\rm DD}$  = 5 V (all voltages are referred to  $V_{\rm SS}$ )

| Parameter | Symbol | Limit Values |      |      | Unit | Test    |

|-----------|--------|--------------|------|------|------|---------|

|           |        | min.         | typ. | max. |      | Circuit |

## Input Signals: LL1.5 100-Hz (120-Hz) Field PAL (NTSC); TTL Input

| H-input voltage                                                   | $V_{IH}$                            | 2.3         |     | $V_{	extsf{DD}}$ | V  | * |

|-------------------------------------------------------------------|-------------------------------------|-------------|-----|------------------|----|---|

| L-input voltage                                                   | $V_{IL}$                            | $V_{	t SS}$ |     | 0.8              | V  | * |

| Input capacitance measured against $V_{\rm SS},\ V_{\rm I}$ = 0 V | $C_1$                               |             |     | 5                | pF | * |

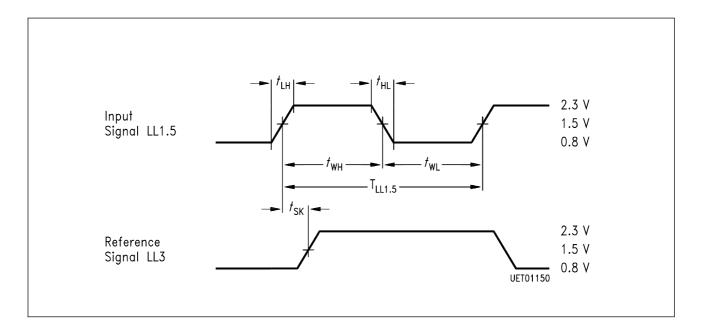

| Period                                                            | T <sub>LL1.5</sub>                  | 34.6        | 37  | 39.8             | ns | 2 |

| Pulse duty factor                                                 | t <sub>WH</sub> /T <sub>LL1.5</sub> | 0.43        | 0.5 | 0.57             |    | 2 |

| Skew for LL3                                                      | t <sub>SK</sub>                     | -5          |     | 5                | ns | * |

| Transition times                                                  | $t_{HL},t_{LH}$                     | 2           |     | 6                | ns | 2 |

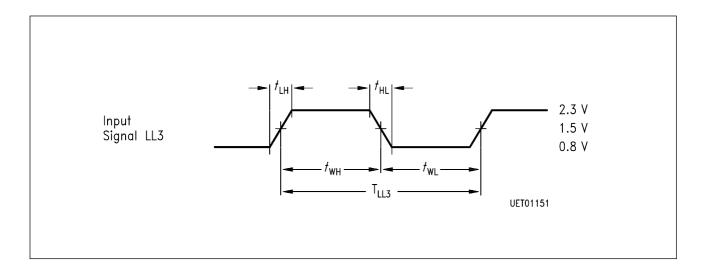

#### Input Signals: LL3 100-Hz (120-Hz) Field PAL (NTSC); TTL Input

| $V_{IH}$                   | 2.3                                                        |                                                                                            | $V_{	extsf{DD}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V                                                                                                                                    | *                                                                                                                                            |

|----------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{IL}$                   | $V_{	extsf{SS}}$                                           |                                                                                            | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V                                                                                                                                    | *                                                                                                                                            |

| $C_1$                      |                                                            |                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | pF                                                                                                                                   | *                                                                                                                                            |

| T <sub>LL3</sub>           | 69.2                                                       | 74                                                                                         | 79.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                   | 2                                                                                                                                            |

| $t_{\rm WH}/{\rm T_{LL3}}$ | 0.43                                                       | 0.5                                                                                        | 0.57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                      | 2                                                                                                                                            |