# DS21448DK 3.3V E1/T1/J1 Line Interface Design Kit Daughter Card

#### www.maxim-ic.com

# **GENERAL DESCRIPTION**

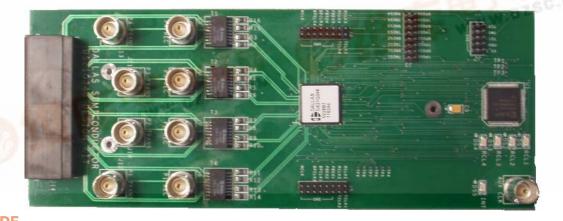

The DS21448DK is an easy-to-use evaluation board for the DS21448 quad E1/T1/J1 LIU. It is intended to be used as a daughter card with the DK101 motherboard or the DK2000 motherboard. A surface-mounted DS21448 and careful layout of the analog signal traces provide maximum signal integrity to demonstrate the transmit and receive capabilities of the DS21448. The DK101/DK2000 motherboard and Dallas' ChipView software give point-and-click access to configuration and status registers from a Windows®-based PC. On-board LEDs indicate interrupt status and receive-carrier loss for all four ports. The evaluation board provides both RJ45 and BNC connectors for the line-side transmit and receive differential pairs on all four ports.

Each DS21448DK is shipped with a free DK101 motherboard. For complex applications, the DK2000 high-performance demo kit motherboard can be purchased separately.

Windows is a registered trademark of Microsoft Corp.

#### ORDERING INFORMATION

| PART      | DESCRIPTION                                                        |

|-----------|--------------------------------------------------------------------|

| DS21448DK | DS21448 Design Kit Daughter Card (with included DK101 Motherboard) |

#### **FEATURES**

- Demonstrates Key Functions of the DS21448

Quad LIU

- Includes Transformers, BNC, and RJ45 Network Connectors and Termination Passives

- Compatible with DK101 and DK2000 Demo Kit Motherboards

- DK101/DK2000 and ChipView Software Provide Point-and-Click Access to the DS21448 Register Set

- Memory-Mapped FPGA Provides Flexible Clock and Signal Routing

- LEDs for Receive-Carrier Loss and Interrupt

- Easy-to-Read Silk-Screen Labels Identify the Signals Associated with All Connectors, Jumpers, and LEDs

#### **DESIGN KIT CONTENTS**

DS21448DK Design Kit Daughter Card DK101 Demo Kit Motherboard CD-ROM

> ChipView Software DS21448DK Data Sheet DS21448 Data Sheet DK101 Data Sheet DS21448 Errata Sheet

pdf.dzsc.com

of 17 PEV: 121803

#### **COMPONENT LIST**

| DESIGNATION                                  | QTY | DESCRIPTION                                             | SUPPLIER                | PART               |

|----------------------------------------------|-----|---------------------------------------------------------|-------------------------|--------------------|

| 1                                            | 1   | 3.3V E1/T1/J1 line interface, 0°C to +70°C, 144-pin BGA | Dallas<br>Semiconductor | DS21448            |

| C1, C2, C6, C10,<br>C12, C22, C24            | 7   | 0.47μF, 25V, 10% ceramic capacitors (1206)              | Digi-Key                | PCC1891CT-ND       |

| C3–C5, C7, C8,<br>C11, C21, C23,<br>C25, C26 | 10  | 0.1μF, 16V, 10% ceramic capacitors (0603)               | Digi-Key                | 311-1088-1-ND      |

| C9                                           | 1   | 10μF, 16V, 20% tantalum capacitor (B case)              | Digi-Key                | PCS3106CT-ND       |

| C13-C16                                      | 4   | 0.1μF, 25V, 10% ceramic capacitors (1206)               | Digi-Key                | PCC1883CT-ND       |

| C17-C20                                      | 4   | 1μF, 16V, 10% ceramic capacitors (1206)                 | Digi-Key                | PCC1882CT-ND       |

| DS1-DS5                                      | 5   | LED, red, SMD                                           | Digi-Key                | P500CT-ND          |

| J1, J6–J13                                   | 9   | Connector BNC RA, 5-pin                                 | Kruvand                 | UCBJR220           |

| J2                                           | 1   | Connector, 10-pin, dual row, vertical                   | Digi-Key                | S2012-05-ND        |

| J3–J5                                        | _   | 8-row by 2-column pin strip, 0.1" centers, 0.025" post  | NA                      | Lab Stock          |

| J14                                          | 1   | RA RJ45, 8-pin, 4-port jack                             | Molex                   | 43223-8140         |

| J15, J16                                     | 2   | Socket, SMD, 50-pin, dual row, vertical                 | Samtec                  | TFM-125-02-S-D-LC  |

| R1–R16,<br>R37–R41,<br>R54–R57               | 25  | 0Ω, 1/8W, 5% resistors (1206)                           | Digi-Key                | P0.0ETR-ND         |

| R17, R20, R21,<br>R25, R28–R36,<br>R53       | 14  | 10kΩ, 1/10W, 1% resistors (0805)                        | Digi-Key                | P10.0KCCT-ND       |

| R18, R19,<br>R22–R24, R26,<br>R27            | 7   | 51.1Ω, 1/10W, 1% resistors (0805)                       | Digi-Key                | P51.1CCT-ND        |

| R42, R43                                     | 2   | 1.0kΩ, 1/10W, 1% resistors (0805)                       | Digi-Key                | P1.00KCCT-ND       |

| R44-R51                                      | 8   | 61.9Ω, 1/8W, 1% resistors (1206)                        | Digi-Key                | P61.9FCT-ND        |

| T1–T4                                        | 4   | XFMR, dual, 16-pin SMT                                  | Pulse Engineering       | TX1099             |

| U1                                           | 1   | Xilinx CPLD 72 macrocell, 100-pin TQFP, 3.3V            | Avnet                   | XC95142XL-10TQ100C |

# **BASIC OPERATION**Hardware Configuration

# Using the DK101 Processor Board

- Connect the daughter card to the DK101 processor board.

- Supply 3.3V to the banana-plug receptacles marked GND and VCC\_3.3V. (The external 5V connector is unused. Additionally, the TIM 5V supply headers are unused.)

- All processor-board DIP switch settings should be in the ON position with the exception of the flashprogramming switch, which should be OFF.

- From the Programs menu, launch the host application named ChipView.EXE. Run the ChipView application. If

the default installation options were used, click the Start button on the Windows toolbar and select Programs →

ChipView → ChipView.

#### Using the DK2000 Processor Board

- Connect the daughter card to the DK2000 processor board.

- Connect J1 to the power supply that is delivered with the kit. Alternately, a PC power supply can be connected to connector J2.

- From the Programs menu, launch the host application named ChipView.EXE. Run the ChipView application. If

the default installation options were used, click the Start button on the Windows toolbar and select Programs →

ChipView → ChipView.

#### General

- Upon power-up, the RCL LEDs are lit, and the INT LED is off.

- After power-up, the RCL LEDs extinguish upon external loopback.

- Due to the dual winding transformer, only the  $120\Omega$  line build-out (LBO) configuration setting is needed to cover both  $75\Omega$  E1 and  $120\Omega$  E1.

#### Miscellaneous

- Clock frequencies are provided by a register-mapped CPLD, which is on the DS21448 daughter card.

- The definition file for this CPLD is named DS21448DK02A0\_CPLD.def. See the CPLD Register Map

definitions.

# **Quick Setup (Register View)**

- The PC loads the program, offering a choice between DEMO MODE, REGISTER VIEW, and TERMINAL MODE. Select Register View.

- The program requests a definition file. Select DS21448DK02A0 CPLD.DEF.

- The Register View Screen appears, showing the register names, acronyms, and values. Note the CPLD def file contains a link such that the def file for the DS21448 is also loaded. Selection among the def files is accomplished using the drop-down box on the right-hand side of the program window.

- From the drop-down box, select the DS21448 def file and configure register CCR3 of ports 1 through 4 with a 90h.

- The device begins transmitting a pseudo-random bit sequence. Upon external loopback, the RCL LED extinguishes, denoting that the device has found a carrier and has successfully decoded the pseudorandom bit sequence. For more advanced configurations, please refer to the DS21448 data sheet.

#### ADDRESS MAP

The DK101 daughter card address space begins at 0x81000000.

The DK2000 daughter card address space begins at:

0x30000000 for slot 0

0x40000000 for slot 1

0x50000000 for slot 2

0x60000000 for slot 3

All offsets in the *Daughter Card Address Map* table are relative to the beginning of the Daughter Card address space.

# **Daughter Card Address Map**

| OFFSET           | DEVICE     | FUNCTION                                                    |

|------------------|------------|-------------------------------------------------------------|

| 0X0000 to 0X0015 | CPLD       | Board ID, clock and signal routing                          |

| 0X2000 to 0X2015 | LIU Port 1 |                                                             |

| 0X3000 to 0X3015 | LIU Port 2 | Board is populated with either the DS21Q348 or the DS21448. |

| 0X4000 to 0X4015 | LIU Port 3 | Please see the factory data sheet for details.              |

| 0X5000 to 0X5015 | LIU Port 4 |                                                             |

Registers in the CPLD can be easily modified using ChipView, a host-based user-interface software with the definition file named DS21448DK02A0\_CPLD.DEF. This file is included as part of the design kit documentation download (accessed through the DS21448's quick view data sheet) or the included CD-ROM. The definition file for the LIU is named *DS21448.def*.

# **CPLD Register Map**

| OFFSET | REGISTER  | TYPE       | FUNCTION                        |

|--------|-----------|------------|---------------------------------|

| 0X0000 | BID       | Read-Only  | Board ID                        |

| 0X0001 | _         | 1          | Unused                          |

| 0X0002 | XBIDH     | Read-Only  | High Nibble Extended Board ID   |

| 0X0003 | XBIDM     | Read-Only  | Middle Nibble Extended Board ID |

| 0X0004 | XBIDL     | Read-Only  | Low Nibble Extended Board ID    |

| 0X0005 | BREV      | Read-Only  | Board FAB Revision              |

| 0X0006 | AREV      | Read-Only  | Board Assembly Revision         |

| 0X0007 | PREV      | Read-Only  | PLD Revision                    |

| 0X0011 | MCLK_SRC  | Read-Write | MCLK Source Register            |

| 0X0012 | TCLK1_SRC | Read-Write | TCLK1 Source Register           |

| 0X0013 | TCLK2_SRC | Read-Write | TCLK2 Source Register           |

| 0X0014 | TCLK3_SRC | Read-Write | TCLK3 Source Register           |

| 0X0015 | TCLK4_SRC | Read-Write | TCLK4 Source Register           |

# **ID Registers**

| OFFSET | NAME  | FUNCTION                                                                        |

|--------|-------|---------------------------------------------------------------------------------|

| 0X0000 | BID   | Board ID. BID is read-only with a value of 0xD.                                 |

| 0X0002 | XBIDH | High Nibble Extended Board ID. XBIDH is read-only with a value of 0x00.         |

| 0X0003 | XBIDM | Middle Nibble Extended Board ID. XBIDM is read-only with a value of 0x02.       |

| 0X0004 | XBIDL | Low Nibble Extended Board ID. XBIDL is read-only with a value of 0x00.          |

| 0X0005 | BREV  | Board FAB Revision. BREV is read-only and displays the current fab revision.    |

| 0X0006 | AREV  | Board Assembly Revision. AREV is read-only and displays the assembly revision.  |

| 0X0007 | PREV  | PLD Revision. PREV is read-only and displays the current PLD firmware revision. |

# **Control Registers**

The control registers are used set the clock frequency on the MCLK and TCLK pins. Options are 1.544MHz, 2.048MHz, external source (through AUX CLK BNC), and tri-state.

# MCLK\_SRC: MCLK SOURCE (OFFSET = 0x0011) INITIAL VALUE = 0x1

| (MSB) |   |   |   |      |        |         | (LSB)   |

|-------|---|---|---|------|--------|---------|---------|

| _     | _ | _ | _ | HI Z | EXTOSC | 2048MHZ | 1544MHZ |

| NAME    | POSITION   | FUNCTION                                     |

|---------|------------|----------------------------------------------|

| HI_Z    | MCLK_SRC.3 | 1 = Tri-state MCLK.                          |

| EXTOSC  | MCLK_SRC.2 | 1 = Connect MCLK to the external oscillator. |

| 2048MHZ | MCLK_SRC.1 | 1 = Connect MCLK to the 2.048MHz clock.      |

| 1544MHZ | MCLK_SRC.0 | 1 = Connect MCLK to the 1.544MHz clock.      |

# TCLK1\_SRC: TCLK SOURCE (OFFSET = 0x0012) INITIAL VALUE = 0x1

| (MSB) |   |   |   |      |        |         | (LSB)   |

|-------|---|---|---|------|--------|---------|---------|

| _     | _ | _ | _ | HI_Z | EXTOSC | 2048MHZ | 1544MHZ |

| NAME    | POSITION    | FUNCTION                                      |

|---------|-------------|-----------------------------------------------|

| HI_Z    | TCLK1_SRC.3 | 1 = Tri-state TCLK1.                          |

| EXTOSC  | TCLK1_SRC.2 | 1 = Connect TCLK1 to the external oscillator. |

| 2048MHZ | TCLK1_SRC.1 | 1 = Connect TCLK1 to the 2.048MHz clock.      |

| 1544MHZ | TCLK1_SRC.0 | 1 = Connect TCLK1 to the 1.544MHz clock.      |

# TCLK2\_SRC: TCLK SOURCE (OFFSET = 0x0013) INITIAL VALUE = 0x1

| (MSB) |   |   |      |        |         | (LSB)   |

|-------|---|---|------|--------|---------|---------|

| _     | _ | _ | HI_Z | EXTOSC | 2048MHZ | 1544MHZ |

| NAME    | POSITION    | FUNCTION                                      |

|---------|-------------|-----------------------------------------------|

| HI_Z    | TCLK2_SRC.3 | 1 = Tri-state TCLK2.                          |

| EXTOSC  | TCLK2_SRC.2 | 1 = Connect TCLK2 to the external oscillator. |

| 2048MHZ | TCLK2_SRC.1 | 1 = Connect TCLK2 to the 2.048MHz clock.      |

| 1544MHZ | TCLK2_SRC.0 | 1 = Connect TCLK2 to the 1.544MHz clock.      |

# TCLK3\_SRC: TCLK SOURCE (OFFSET = 0x0014) INITIAL VALUE = 0x1

| (MSB) |   |   |      |        |         | (LSB)   |

|-------|---|---|------|--------|---------|---------|

|       | _ | _ | HI_Z | EXTOSC | 2048MHZ | 1544MHZ |

| NAME    | POSITION    | FUNCTION                                      |

|---------|-------------|-----------------------------------------------|

| HI_Z    | TCLK3_SRC.3 | 1 = Tri-state TCLK3.                          |

| EXTOSC  | TCLK3_SRC.2 | 1 = Connect TCLK3 to the external oscillator. |

| 2048MHZ | TCLK3_SRC.1 | 1 = Connect TCLK3 to the 2.048MHz clock.      |

| 1544MHZ | TCLK3_SRC.0 | 1 = Connect TCLK3 to the 1.544MHz clock.      |

# TCLK4\_SRC: TCLK SOURCE (OFFSET = 0x0015) INITIAL VALUE = 0x1

| (MSB) |   |   |   |      |        |         | (LSB)   |

|-------|---|---|---|------|--------|---------|---------|

| _     | _ | _ | _ | HI Z | EXTOSC | 2048MHZ | 1544MHZ |

| NAME    | POSITION    | FUNCTION                                      |

|---------|-------------|-----------------------------------------------|

| HI_Z    | TCLK4_SRC.3 | 1 = Tri-state TCLK4.                          |

| EXTOSC  | TCLK4_SRC.2 | 1 = Connect TCLK4 to the external oscillator. |

| 2048MHZ | TCLK4_SRC.1 | 1 = Connect TCLK4 to the 2.048MHz clock.      |

| 1544MHZ | TCLK4_SRC.0 | 1 = Connect TCLK4 to the 1.544MHz clock.      |

# **DS21448 INFORMATION**

For more information about the DS21448, please consult the DS21448 data sheet available on our website, www.maxim-ic.com/telecom.

# **TECHNICAL SUPPORT**

For additional technical support, please email your questions to telecom.support@dalsemi.com.

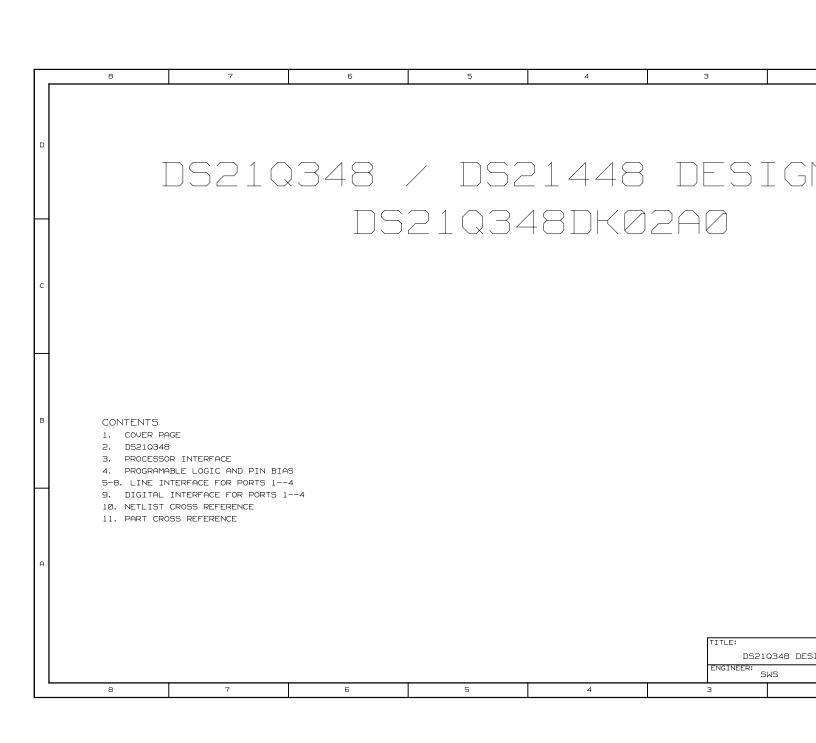

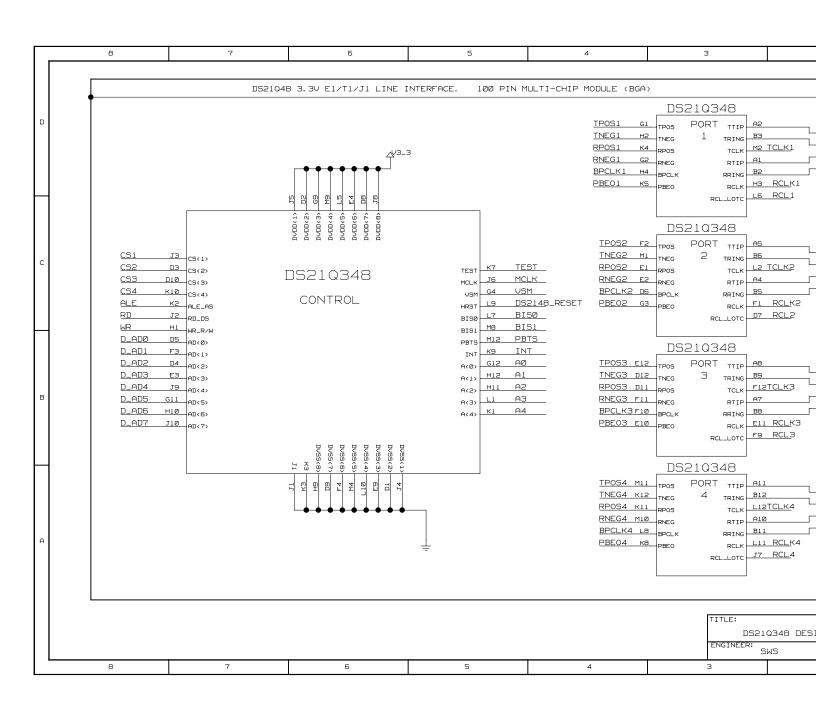

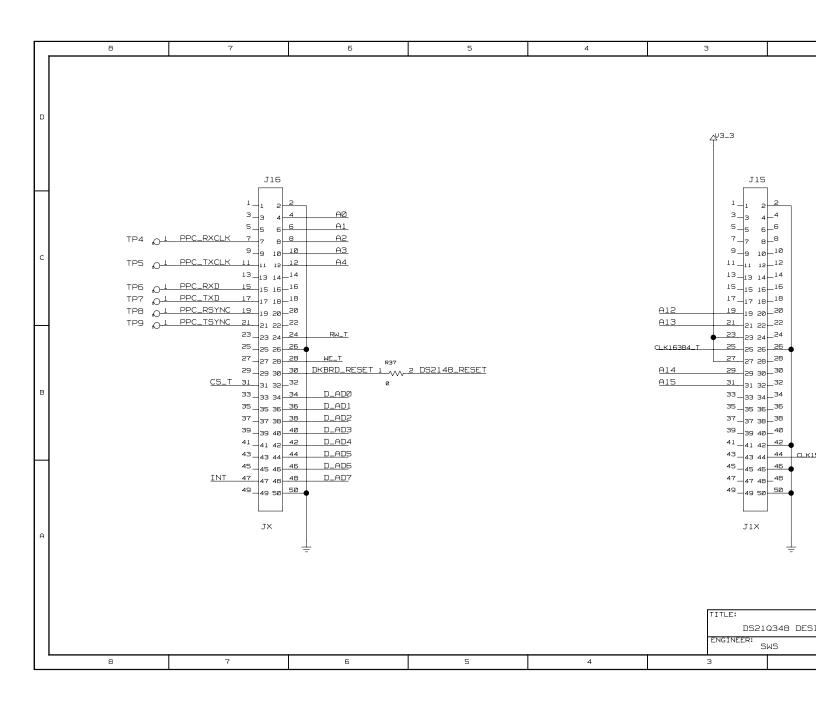

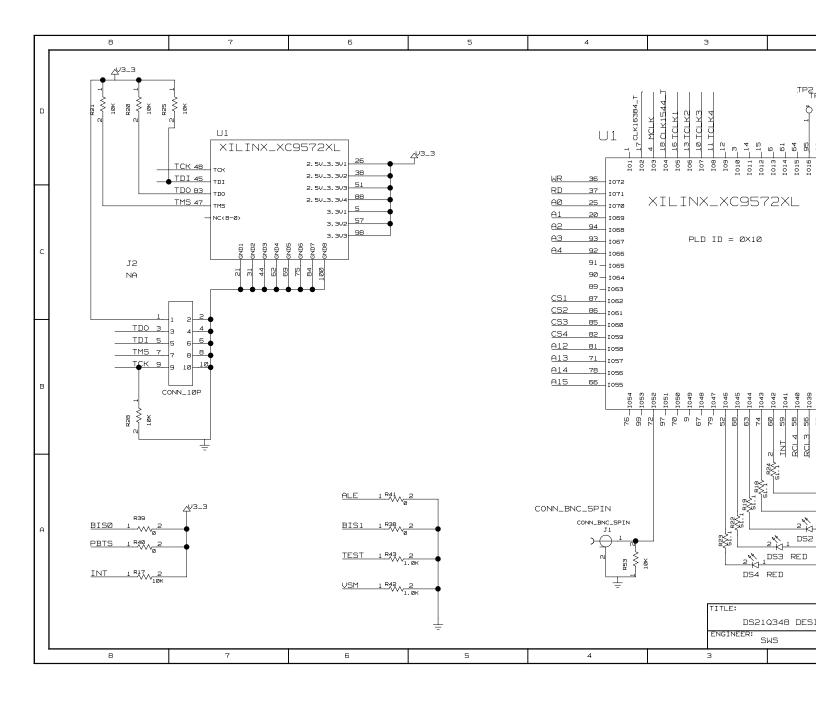

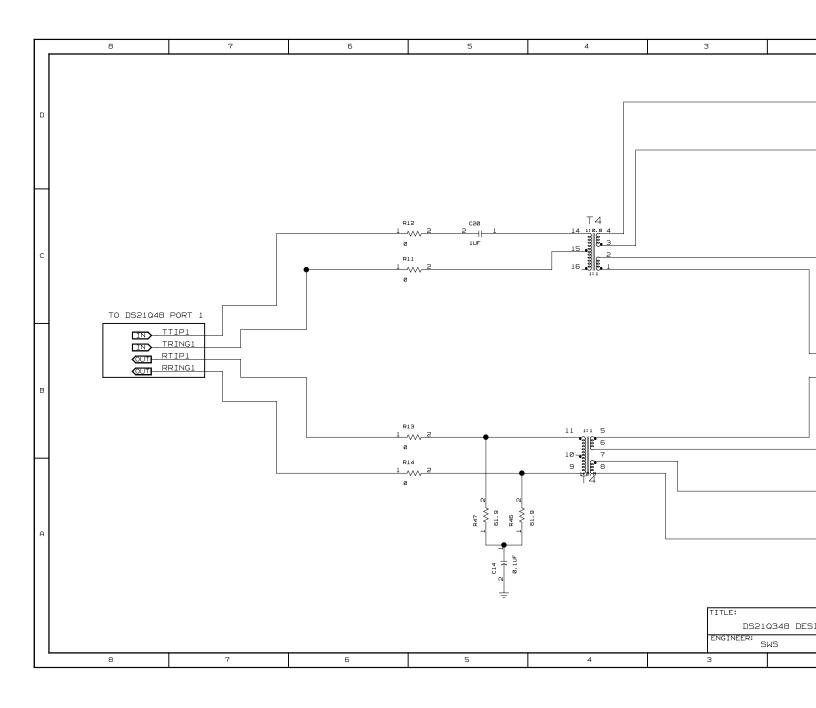

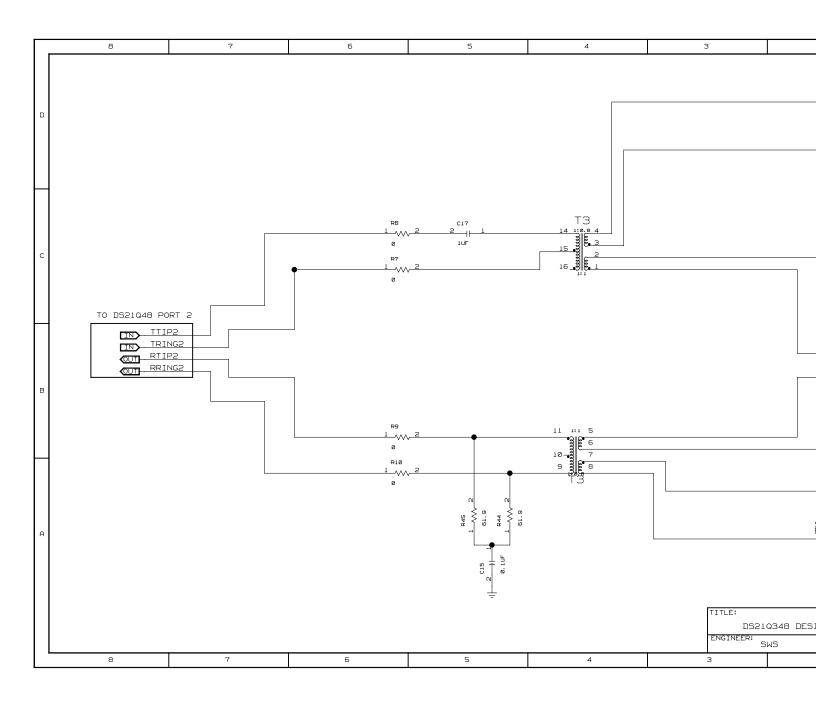

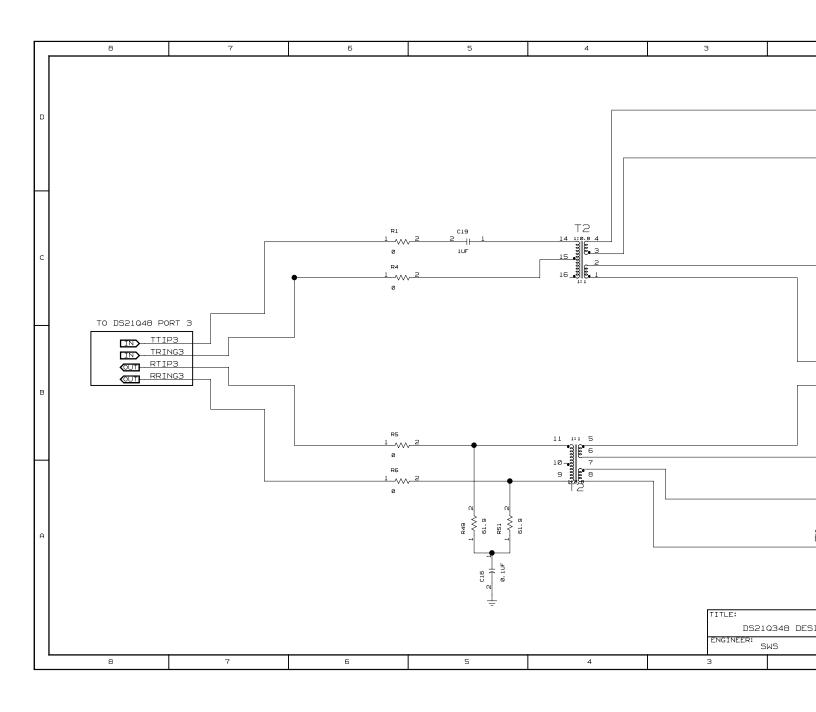

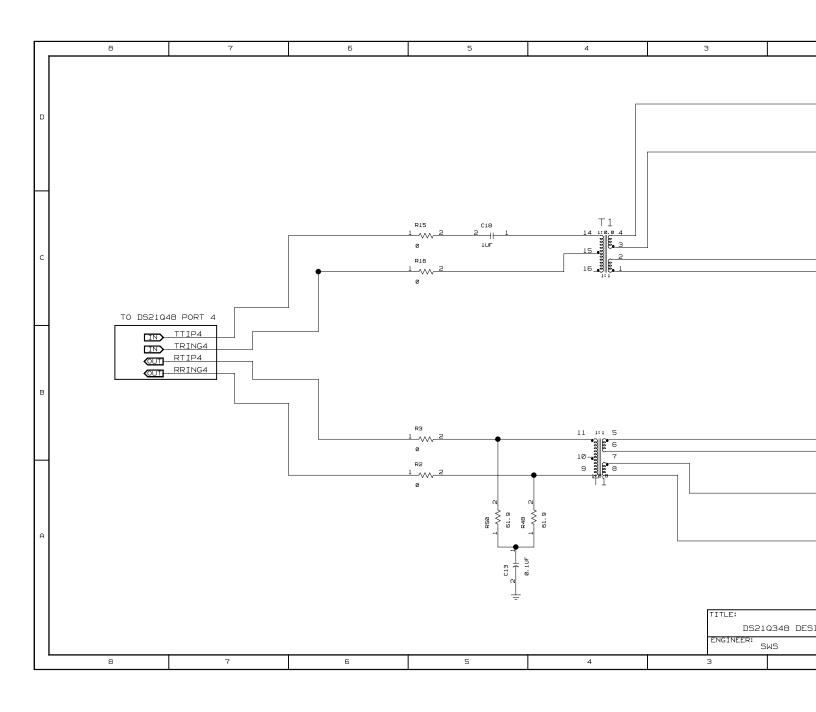

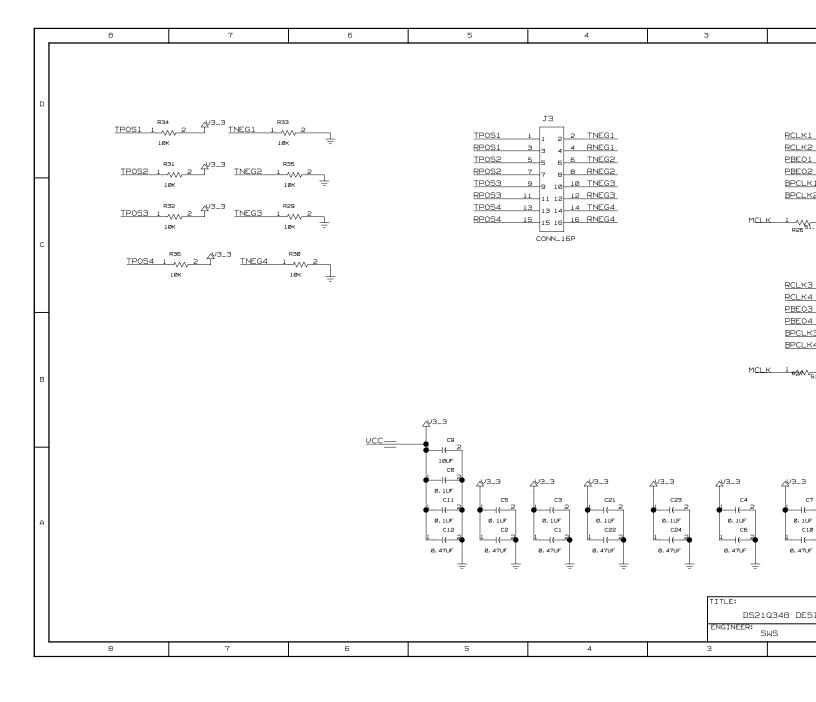

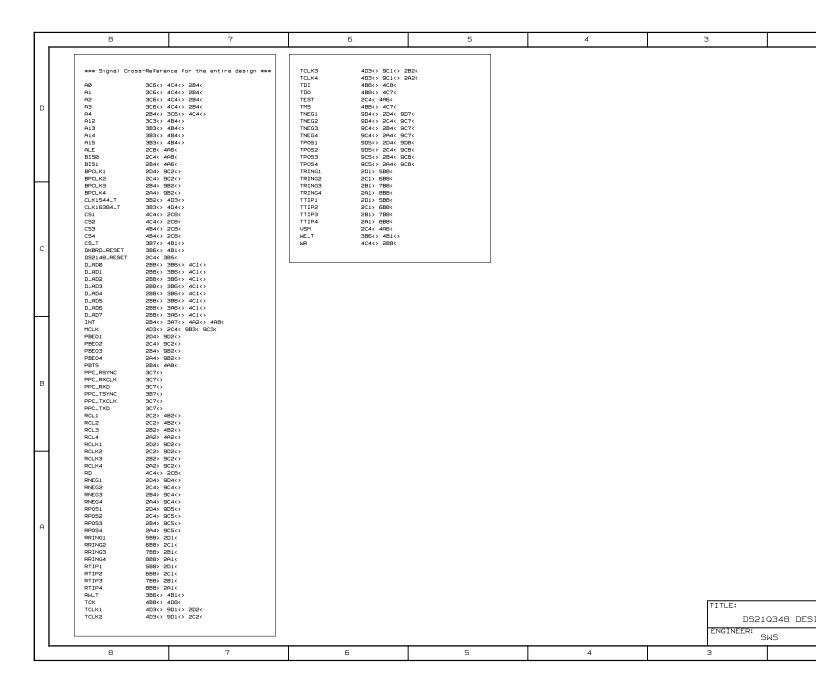

# **SCHEMATICS**

The D21448DK schematics are featured in the following pages.

| Γ |   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7     | 6                                                                                                                                                                                                                                                                         | 5 | 4 | 3 |           |

|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-----------|

|   | ם | ### Part Cross-Reference for  1 DS21034B 2A3 2B8 2B6  C1 CAP 9A4  C2 CAP 9A5  C3 CAP 9A6  C5 CAP 9A5  C5 CAP 9A5  C6 CAP 9A6  C7 CAP 9A2  C8 CAP 9A5  C9 CAP 9A5  C10 CAP 9A5  C11 CAP 9A5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | R2B RES 4BB R29 RES 9C7 R30 RES 9C8 R31 RES 9D8 R32 RES 9D8 R33 RES 9D7 R34 RES 9D7 R35 RES 9D7 R36 RES 9D7 R36 RES 9D7 R36 RES 9C7 R37 RES 3B6 R38 RES 4A6 R40 RES 4A8                                                                                                   |   |   |   |           |

|   | C | C13 CAP BAS C14 CAP SAS C15 CAP BAS C15 CAP BAS C17 CAP BCS C18 CAP BCS C19 CAP TCS C20 CAP TCS C21 CAP BCS C21 CAP BA4 C22 CAP BA4 C22 CAP BA4 C23 CAP BA3 C24 CAP BA3 C25 CAP BA2 C25 CA |       | R43 RES 4A6  A44 RES 6A5  A45 RES 6A5  A47 RES 5A5  R47 RES 5A5  R48 RES 5A5  R49 RES 7A5  R50 RES 8A5  R51 RES 7A5  R53 RES 4A4  R54 RES 5A1  R55 RES 6A2  R57 RES 6A2  R57 RES 6A2  R57 RES 6A1  T1 XFMR_2IN_4OUT 6A4 6C4  T4 XFMR_2IN_4OUT 6A4 5C4  T91 TSTENT_SNG 4D2 |   |   |   |           |

|   | В | J2 CONN_16P 4C8 J3 CONN_16P 9C4 J4 CONN_16P 9C2 J5 CONN_16P 9C2 J5 CONN_16P 9C2 J6 CONN_BNC_SPIN 762 J7 CONN_BNC_SPIN 561 J9 CONN_BNC_SPIN 501 J10 CONN_BNC_SPIN 501 J11 CONN_BNC_SPIN 501 J12 CONN_BNC_SPIN 501 J12 CONN_BNC_SPIN 501 J13 CONN_BNC_SPIN 501 J14 CONN_BNC_SPIN 501 J15 CONN_BNC_SPIN 501 J16 CONN_BNC_SPIN 501 J17 CONN_BNC_SPIN 501 J18 CONN_BNC_SPIN 501 J19 CONN_BNC_SPIN 501 J10 CONN_BN | 2 8C2 | TP3 TSTPNT_SNG 4D2 TP4 TSTPNT_SNG 3C6 TP5 TSTPNT_SNG 3C6 TP6 TSTPNT_SNG 3C6 TP7 TSTPNT_SNG 3C6 TP8 TSTPNT_SNG 3C6 TP8 TSTPNT_SNG 3C6 US TSTPNT_SNG 3C6 US TSTPNT_SNG 3B6 US XILINX_XC9572XL 4D4 4D7                                                                       |   |   |   |           |

|   | D | R4 RES 7CB RES RES 7BB RES 7BB RES 7BB RES 6CB RB RB RES 6CB RB RB RES 8CB 8CB RB RB RES 8CB RB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                                                                                                                                                                                                                           |   |   |   | Q348 DES] |

|   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                                                                                                                                                                                                                                                           |   |   |   | MS        |

| L |   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7     | Б                                                                                                                                                                                                                                                                         | 5 | 4 | 3 |           |