#### 查询ONET4211LD供应商

ONET4211LD

SLLS688-NOVEMBER 2005

# 155 Mbps to 4.25 Gbps LASER DRIVER

### **FEATURES**

- Multirate Operation From 155 Mbps up to 4.25 Gbps

- Bias Current Programmable From 1 mA to 100 mA

- Modulation Current Programmable From 5 mA to 85 mA

- APC and Fault Detection

- Fault Mode Selection

- Bias and Photodiode Current Monitors

- CML Data Inputs

- Temperature Compensation of Modulation

Current

- Single 3.3-V Supply

- Surface-Mount, Small-Footprint, 4 mm × 4 mm 24-Lead QFN Package

### **APPLICATIONS**

- SONET/SDH Transmission Systems

- Fibre Channel Optical Modules

- Fiber Optic Data Links

- Digital Cross-Connects

- Optical Transmitters

### DESCRIPTION

The ONET4211LD is a laser driver for multiple fiber optic applications up to 4.25 Gbps. The device accepts CML input data and provides bias and modulation currents for driving a laser diode. Also provided are automatic power control (APC), temperature compensation of modulation current, fault detection, and current monitor features.

The device is available in a small-footprint, 4 mm  $\times$  4 mm 24-pin QFN package. The circuit requires a single 3.3-V supply.

This power-efficient laser driver is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### SLLS688-NOVEMBER 2005

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **DETAILED DESCRIPTION**

#### **BLOCK DIAGRAM**

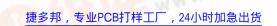

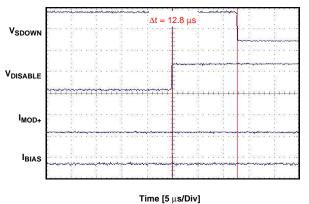

A simplified block diagram of the ONET4211LD is shown in Figure 1.

This compact, low-power, 4.25-Gbps laser driver circuit consists of a high-speed data path and a bias-and-control block.

The function of the data path is to buffer the input data and then modulate the laser diode current according to the input data stream.

The bias-and-control block generates the laser diode bias current, contains automatic power control (APC) to maintain constant optical output power, generates a modulation current that can be temperature compensated, and controls power on during start-up and shutdown after failure detection. The circuit design is optimized for high-speed and low-voltage operation (3.3 V).

The main circuit blocks are described in detail in the following paragraphs.

Figure 1. Simplified Block Diagram of the ONET4211LD

3

(4)

**DETAILED DESCRIPTION (continued)**

### HIGH-SPEED DATA PATH

The high-speed data path consists of an input buffer stage and a current modulator.

The input buffer stage takes CML-compatible differential signals. It provides on-chip,  $50-\Omega$  termination to VCC. AC-coupling may be used at the DIN+ and DIN- inputs.

The laser diode current modulator consists mainly of two common-emitter output transistors and the required driver circuitry. According to the input data stream, the modulation current is sunk at the MOD+ or the MOD- pin.

Modulation current setting is performed by means of the modulation current generator block, which is supervised by the control circuit block.

The laser diode can be either ac- or dc-coupled. In either case, the maximum modulation current is 85 mA. The modulation output is optimized for driving a 20- $\Omega$  load.

For optimum power efficiency, the laser driver does not provide any on-chip back-termination.

### **BIAS AND CONTROL**

The bias-and-control circuitry consists of the bandgap voltage and bias generation block, the bias current generator, the automatic power control block, and the supervising control circuitry.

### BANDGAP VOLTAGE AND BIAS GENERATION

The bandgap voltage reference provides the process- and temperature-independent reference voltages needed to set bias current, modulation current, and photodiode reference current. Additionally, this block provides the biasing for all internal circuits.

### **AUTOMATIC POWER CONTROL**

The ONET4211LD laser driver incorporates an APC loop to compensate for the changes in laser threshold current over temperature and lifetime. The internal APC is enabled when resistors are connected to the IBMAX and APCSET pins. A back-facet photodiode mounted in the laser package is used to detect the average laser output power. The photodiode current  $I_{PD}$  that is proportional to the average laser power can be calculated by using the laser-to-monitor transfer ratio,  $\rho_{MON}$  and the average power,  $P_{AVG}$ :

$$I_{\text{PD}}[A] = P_{\text{AVG}}[W] \times \rho_{\text{MON}}[A/W]$$

<sup>(1)</sup>

In closed-loop operation, the APC modifies the laser diode bias current by comparing  $I_{PD}$  with a reference current  $I_{APCSET}$  and generates a bias compensation current.  $I_{PD}$  can be programmed by selecting the external resistor  $R_{APCSET}$  according to:

$$\mathsf{R}_{\mathsf{APCSET}}[\Omega] = \frac{4.69 \,\mathsf{V}}{\mathsf{I}_{\mathsf{PD}}[\mathsf{A}]} = \frac{4.69 \,\mathsf{V}}{\mathsf{P}_{\mathsf{AVG}}[\mathsf{W}] \times \rho_{\mathsf{MON}}[\mathsf{A}/\mathsf{W}]} \tag{2}$$

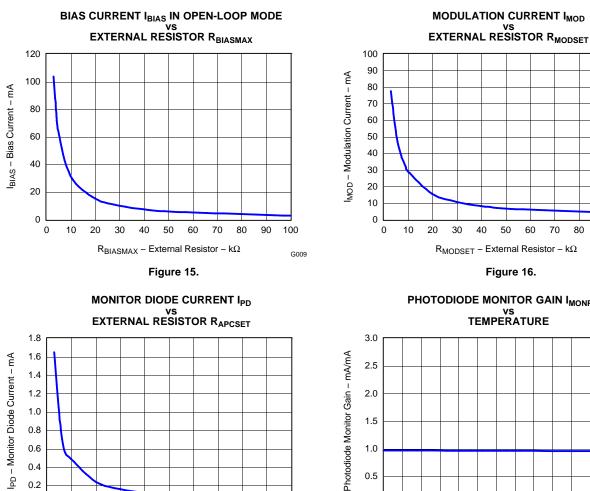

The bias compensation current subtracts from the maximum bias current to maintain the monitor photodiode current. The maximum bias current is programmed by the resistor connected to IBMAX:

$$I_{\text{BIASMAX}}[A] = \frac{343 \text{ V}}{\text{R}_{\text{BIASMAX}}[\Omega]}$$

(3)

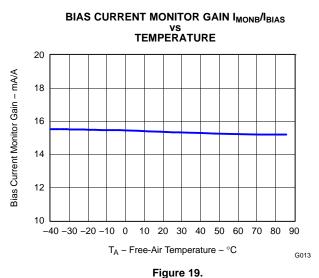

An external pin, MONB, is provided as a bias current monitor output. A fraction of the bias current (1/68) is mirrored and develops a voltage drop across an external resistor to ground,  $R_{MONB}$ . The voltage at MONB is given as:

$V_{MONB}[V] = \frac{R_{MONB}[\Omega] \times I_{BIAS}[A]}{68}$ If the voltage at MONB is greater than the programmed threshold, a fault mode occurs.

MONP is also provided as a photocurrent monitor output. The photodiode current,  $I_{PD}$ , is mirrored and develops a voltage across an external resistor to ground,  $R_{MONP}$ . The voltage at MONP is given as:

### DETAILED DESCRIPTION (continued)

$$V_{\text{MONP}}[V] = R_{\text{MONP}}[\Omega] \times I_{\text{PD}}[A]$$

If the voltage at MONP is greater than the programmed threshold, a fault mode occurs.

As with any negative-feedback system design, care must be taken to ensure stability of the loop. The loop bandwidth must not be too high, in order to minimize pattern-dependent jitter. The dominant pole is determined by the capacitor C<sub>APC</sub>. The recommended value for C<sub>APC</sub> is 200 nF. The capacitance of the monitor photodiode C<sub>PD</sub> adds another pole to the system, and thus it must be small enough to maintain stability. The recommended value for this capacitance is  $C_{PD} \leq 50$  pF.

The internal APC loop can be disabled by connecting a 100-kΩ resistor from APCSET to VCC and leaving PD open. In open-loop operation, the laser diode current is set by IBIASMAX and IMODSET.

### MODULATION CURRENT GENERATOR

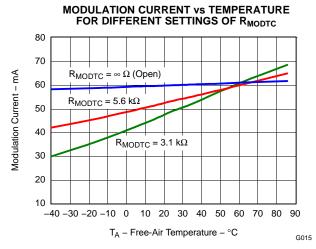

The modulation current generator defines the tail current of the modulator, which is sunk from either MOD+ or MOD-, depending on the data pattern. The modulation current consists of a current I<sub>MOD0</sub> at a reference temperature  $T_0 = 60^{\circ}C$  (set by the resistor  $R_{MODSET}$ ) and a temperature-dependent modulation current defined by the resistor R<sub>MODTC</sub>. The modulation current can be estimated as follows:

$$I_{\text{MOD}}[A] = \frac{265 \text{ V}}{\mathsf{R}_{\text{MODSET}}[\Omega]} \times \left[ 1 + \left( \frac{24 \Omega}{\mathsf{R}_{\text{MODTC}}[\Omega]} + 630 \text{ ppm} \right) \times \left( \mathsf{T}[^{\circ}\mathsf{C}] - \mathsf{T}_{0}[^{\circ}\mathsf{C}] \right) \right]$$

(6)

Note that the reference temperature,  $T_0$ , and the temperature compensation set by  $R_{MODTC}$  vary from part to part. To reduce the variation, I<sub>MOD</sub> can be calibrated over temperature and set with a microcontroller DAC or digital potentiometer.

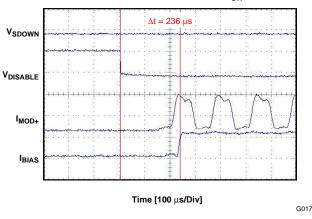

### CONTROL

The function of this block is to control the start-up sequence, detect faults, detect tracking failure of the APC loop, and provide disable control. The laser driver has a controlled start-up sequence which helps prevent transient glitches from being applied to the laser during power on. At start-up, the laser diode is off, SDOWN is low, and the APC loop is open. Once V<sub>CC</sub> reaches ~2.8 V, the laser diode bias generator and modulation current generator circuitry are activated (if DISABLE is low). The slow-start circuitry gradually brings up the current delivered to the laser diode. From the time when V<sub>CC</sub> reaches ~2.8 V until the modulation current and bias current reach 95% of their steady state value, is considered the initialization time. If DISABLE is asserted during power on, the slow-start circuitry does not activate until DISABLE is negated.

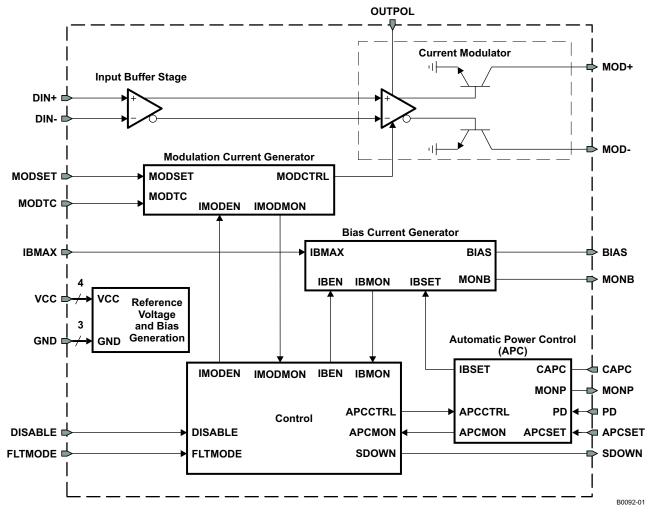

### **FAULT DETECTION**

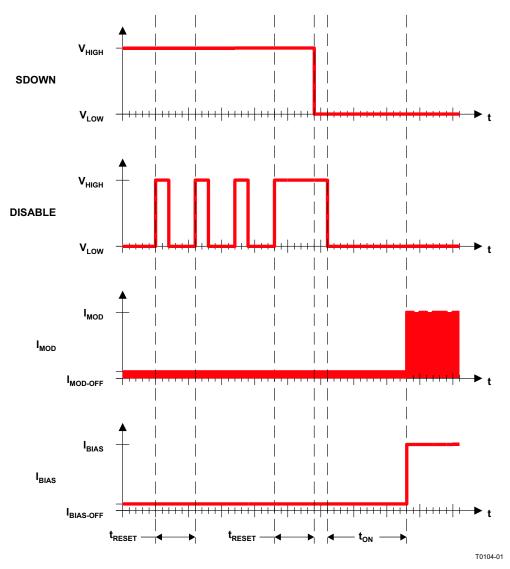

The fault detection circuitry monitors the operation of the ONET4211LD. If FLTMODE is set to a low level, (hard-fault mode) this circuitry disables the bias and modulation circuits and latches the SDOWN output on detection of a fault. The fault mode is reset by toggling DISABLE (for a minimum time of T<sub>RES</sub>) or by toggling VCC.

Once DISABLE is toggled, SDOWN is set low and the circuit is re-initialized.

If FLTMODE is set to a high level (soft-fault mode), a fault is indicated at the SDOWN output; however, the bias and modulation circuits are not disabled. The SDOWN output is reset once the fault-causing condition disappears. Toggling DISABLE or VCC is not required.

A functional representation of the fault-detection circuitry is shown in Figure 2.

(5)

### **DETAILED DESCRIPTION (continued)**

A fault mode is produced if the laser cathode is grounded and the photocurrent causes MONP to exceed its programmed threshold. Another fault mode can be produced if the laser diode end-of-life condition causes excessive bias current and photocurrent that results in monitor voltages (MONP, MONB) being greater than their programmed threshold. Other fault modes can occur if there are any I/O pin single-point failures (short to VCC or GND) and the monitor voltages exceed their programmed threshold (see Table 1).

### **DETAILED DESCRIPTION (continued)**

### Table 1. Response to I/O-Pin Shorts to VCC or GND

| DIN     | FLTMODE                                                             | = LOW                                                               | FLTMODE = HIGH                                                      |                                                                     |  |  |

|---------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| PIN     | Response to Short to GND                                            | Response to Short to $V_{CC}$                                       | Response to Short to GND                                            | Response to Short to $V_{CC}$                                       |  |  |

| APCSET  | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | No fault, I <sub>MOD</sub> unaffected                               | SDOWN high, ${\rm I}_{\rm BIAS}$ and ${\rm I}_{\rm MOD}$ unaffected | No fault                                                            |  |  |

| BIAS    | SDOWN latched high, I <sub>MOD</sub> disabled                       | No fault, $I_{BIAS}$ goes to zero                                   | SDOWN high, I <sub>MOD</sub><br>unaffected                          | No fault, I <sub>MOD</sub> unaffected                               |  |  |

| CAPC    | No fault                                                            | No fault, I <sub>BIAS</sub> goes to zero                            | No fault, I <sub>MOD</sub> unaffected                               | No fault, I <sub>BIAS</sub> goes to zero                            |  |  |

| DIN+    | No fault, I <sub>MOD</sub> disabled                                 | No fault                                                            | No fault, I <sub>MOD</sub> disabled                                 | No fault                                                            |  |  |

| DIN-    | No fault, I <sub>MOD</sub> disabled                                 | No fault                                                            | No fault, I <sub>MOD</sub> disabled                                 | No fault                                                            |  |  |

| DISABLE | Normal circuit operation                                            | Normal circuit operation                                            | Normal circuit operation                                            | Normal circuit operation                                            |  |  |

| IBMAX   | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | SDOWN latched high, $I_{BIAS}$ and $I_{MOD}$ disabled               | SDOWN high, I <sub>MOD</sub><br>unaffected                          | SDOWN high, $I_{MOD}$ unaffected                                    |  |  |

| MOD+    | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | No fault                                                            | SDOWN high, I <sub>BIAS</sub> unaffected                            | No fault                                                            |  |  |

| MOD-    | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | No fault                                                            | SDOWN high, I <sub>BIAS</sub> unaffected                            | No fault                                                            |  |  |

| MODSET  | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | No fault, I <sub>MOD</sub> disabled                                 | SDOWN high, I <sub>BIAS</sub> unaffected                            | No fault, I <sub>MOD</sub> disabled                                 |  |  |

| MODTC   | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | No fault                                                            | SDOWN high, ${\rm I}_{\rm BIAS}$ and ${\rm I}_{\rm MOD}$ unaffected | No fault                                                            |  |  |

| MONB    | No fault                                                            | SDOWN latched high, $I_{BIAS}$ and $I_{MOD}$ disabled               | No fault                                                            | SDOWN high, ${\rm I}_{\rm BIAS}$ and ${\rm I}_{\rm MOD}$ unaffected |  |  |

| MONP    | No fault                                                            | SDOWN latched high, $I_{\text{BIAS}}$ and $I_{\text{MOD}}$ disabled | No fault                                                            | SDOWN high, ${\rm I}_{\rm BIAS}$ and ${\rm I}_{\rm MOD}$ unaffected |  |  |

| OUTPOL  | No fault, polarity reverses                                         | No fault                                                            | No fault, polarity reverses                                         | No fault                                                            |  |  |

| PD      | No fault, I <sub>MOD</sub> unaffected                               | No fault, I <sub>BIAS</sub> goes to zero                            | No fault, I <sub>MOD</sub> unaffected                               | No fault, I <sub>BIAS</sub> goes to zero                            |  |  |

| SDOWN   | No fault                                                            | No fault                                                            | No fault                                                            | No fault                                                            |  |  |

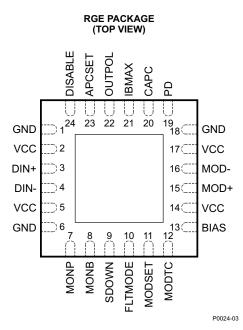

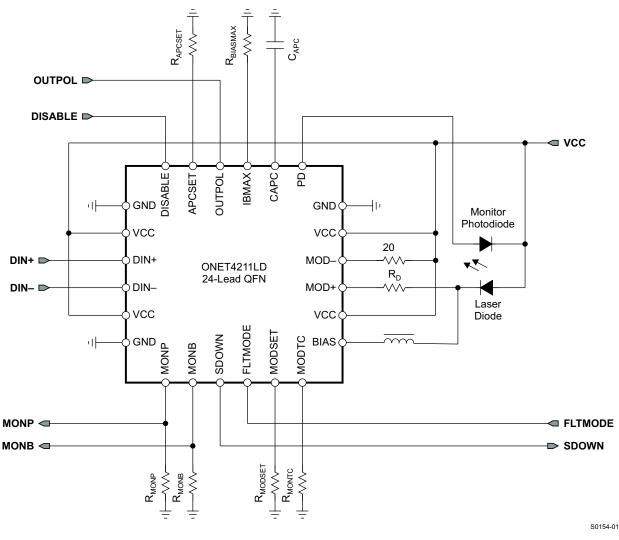

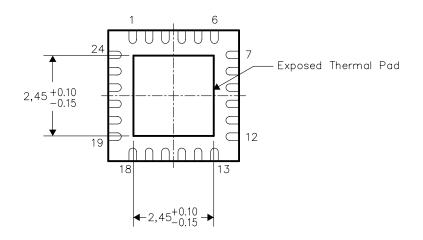

### PACKAGE

For the ONET4211LD, a small-footprint, 4-mm  $\times$  4-mm, 24-lead QFN package is used, with a lead pitch of 0,5 mm. The pinout is shown in Figure 3.

To achieve the required low thermal resistance of about 38 K/W, which keeps the maximum junction temperature below 115°C, a good thermal connection of the exposed die pad is mandatory.

Figure 3. Pinout of the ONET4211LD in a 4-mm × 4-mm, 24-Lead QFN Package (Top View)

#### **TERMINAL FUNCTIONS**

| TERMINAL |              | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.          | TIPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                      |

| APCSET   | 23           | Analog-in  | Set photodiode reference current with resistor to GND.                                                                                                                                                                                                                                                                                                                                                                           |

| BIAS     | 13           | Analog-out | Laser-diode bias-current sink. Connect to laser cathode.                                                                                                                                                                                                                                                                                                                                                                         |

| CAPC     | 20           | Analog     | APC loop capacitor                                                                                                                                                                                                                                                                                                                                                                                                               |

| DIN+     | 3            | CML-in     | Non-inverted data input. On-chip, 50- $\Omega$ terminated to VCC.                                                                                                                                                                                                                                                                                                                                                                |

| DIN-     | 4            | CML-in     | Inverted data input. On-chip, 50- $\Omega$ terminated to VCC.                                                                                                                                                                                                                                                                                                                                                                    |

| DISABLE  | 24           | LVTTL-in   | Disable modulation and bias-current outputs.                                                                                                                                                                                                                                                                                                                                                                                     |

| FLTMODE  | 10           | CMOS-in    | Fault mode selection input. If a low level is applied to this pin, any fault event is latched and the bias and modulation currents are disabled in a fault condition. Toggling of DISABLE or VCC resets the fault condition. If pin is set to a high level, fault events are flagged at the SDOWN output but not latched. The bias and modulation currents are not disabled. SDOWN is reset once the fault condition disappears. |

| GND      | 1, 6, 18, EP | Supply     | Circuit ground. The exposed die pad (EP) must be grounded.                                                                                                                                                                                                                                                                                                                                                                       |

| IBMAX    | 21           | Analog-in  | Set maximum laser diode current with resistor to GND.                                                                                                                                                                                                                                                                                                                                                                            |

| MOD+     | 15           | Analog-out | Laser modulation current output. Connect to laser cathode. Avoid usage of vias on board.                                                                                                                                                                                                                                                                                                                                         |

| MOD-     | 16           | Analog-out | Complementary laser modulation current output. Connect to VCC adjacent to anode of laser diode. Avoid usage of vias on board.                                                                                                                                                                                                                                                                                                    |

| MODSET   | 11           | Analog-in  | Set temperature-independent modulation current with resistor to GND.                                                                                                                                                                                                                                                                                                                                                             |

| MODTC    | 12           | Analog-in  | Set modulation-current temperature compensation with resistor to GND.                                                                                                                                                                                                                                                                                                                                                            |

| MONB     | 8            | Analog-out | Bias current monitor. Sources 1/68 of the bias current.                                                                                                                                                                                                                                                                                                                                                                          |

| MONP     | 7            | Analog-out | Photodiode current monitor. Sources a current identical to the photodiode current.                                                                                                                                                                                                                                                                                                                                               |

| OUTPOL   | 22           | LVTTL-in   | Alters modulation current output polarity. Open or high: normal polarity; low: inverted polarity. OUTPOL is pulled up internally. Normal polarity: when DIN+ is high, current is sunk into MOD+.                                                                                                                                                                                                                                 |

| PD       | 19           | Analog-in  | Monitor photodiode input. Connect to photodiode anode for APC. Sinks the photodiode current to GND.                                                                                                                                                                                                                                                                                                                              |

| SDOWN    | 9            | LVTTL-out  | Fault detection flag                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCC      | 2, 5, 14, 17 | Supply     | 3.3-V, ±10% supply voltage                                                                                                                                                                                                                                                                                                                                                                                                       |

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| V <sub>CC</sub>                                                                                                                                     | Supply voltage <sup>(2)</sup>                                             | –0.3 V to 4 V        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------|

| I <sub>IBIAS</sub>                                                                                                                                  | Current into BIAS                                                         | -20 mA to 120 mA     |

| I <sub>IMOD+</sub> , I <sub>IMOD-</sub>                                                                                                             | Current into MOD+, MOD-                                                   | - 20 mA to 120 mA    |

| I <sub>PD</sub>                                                                                                                                     | Current into PD                                                           | -5 mA to 5 mA        |

| V <sub>DIN+</sub> , V <sub>DIN-</sub> , V <sub>DISABLE</sub> , V <sub>MONB</sub> ,<br>V <sub>MONP</sub> , V <sub>FLTMODE</sub> , V <sub>SDOWN</sub> | Voltage at DIN+, DIN-, DISABLE, MONB, MONP, FLTMODE, SDOWN <sup>(2)</sup> | -0.3 V to 4V         |

| V <sub>CAPC</sub> , V <sub>IBMAX</sub> , V <sub>MODSET</sub> ,<br>V <sub>APCSET</sub> , V <sub>MODTC</sub>                                          | Voltage at CAPC, IBMAX, MODSET, APCSET, MODTC <sup>(2)</sup>              | –0.3 V to 3 V        |

| V <sub>MOD+</sub> , V <sub>MOD-</sub>                                                                                                               | Voltage at MOD+, MOD- <sup>(2)</sup>                                      | 0.6 V to VCC + 1.5 V |

| V <sub>BIAS</sub>                                                                                                                                   | Voltage at BIAS <sup>(2)</sup>                                            | 1 V to 3.5 V         |

| ESD                                                                                                                                                 | ESD rating at all pins except MOD+, MOD-                                  | 2 kV (HBM)           |

| ESD                                                                                                                                                 | ESD rating at MOD+, MOD-                                                  | 1 kV (HBM)           |

| T <sub>J,max</sub>                                                                                                                                  | Maximum junction temperature                                              | 150°C                |

| T <sub>STG</sub>                                                                                                                                    | Storage temperature range                                                 | –65°C to 150°C       |

| T <sub>A</sub>                                                                                                                                      | Characterized free-air operating temperature range                        | -40°C to 85°C        |

| T <sub>LEAD</sub>                                                                                                                                   | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds              | 260°C                |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                 |                                | MIN | NOM | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | Supply voltage                 | 3   | 3.3 | 3.6 | V    |

| T <sub>A</sub>  | Operating free-air temperature | -40 |     | 85  | °C   |

### DC ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                        | TEST CONDITIONS                                                                                                              | MIN  | TYP  | MAX  | UNIT   |

|-----------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| V <sub>CC</sub>       | Supply voltage                                   |                                                                                                                              | 3    | 3.3  | 3.6  | V      |

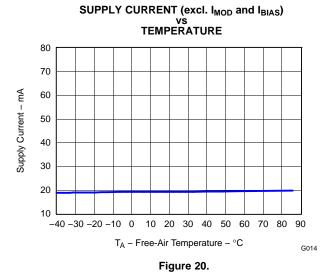

| L                     | Supply current                                   | $I_{MOD}$ = 30 mA, $I_{BIAS}$ = 20 mA (excluding $I_{MOD},$ $I_{BIAS})$                                                      |      | 22   |      | mA     |

| Ivcc                  | Supply current                                   | $I_{MOD}$ = 60 mA, $I_{BIAS}$ = 100 mA (excluding $I_{MOD},$ $I_{BIAS})$                                                     |      |      | 45   | mA     |

| I <sub>BIAS</sub>     | Bias current range                               |                                                                                                                              |      |      | 100  | mA     |

| I <sub>BIAS-OFF</sub> | Bias off-current                                 | DISABLE = high or hard-fault mode; $V_{BIAS} \le 3.5 \text{ V}$                                                              |      |      | 25   | μΑ     |

|                       | Bias overshoot                                   | During module hot plugging. V <sub>CC</sub> turnon time must be $\leq 0.8~\text{s}$                                          |      |      | 10%  |        |

|                       | Bias current temperature stability APC open loop |                                                                                                                              |      |      | 480  | ppm/°C |

|                       | Bias current absolute accuracy <sup>(1)</sup>    | $I_{BIAS} \ge 1 \text{ mA}$                                                                                                  | -15% |      | 15%  |        |

|                       |                                                  | $I_{BIAS} = 1 \text{ mA}, T_A = 25^{\circ}C$                                                                                 |      | ±15% |      |        |

|                       | Bias current monitor gain, IBIAS/IMONB           |                                                                                                                              |      | 68   |      | mA/ mA |

|                       | MONB and MONP threshold range                    | A fault is never detected for V <sub>MONB/P</sub> $\leq$ 1 V and a fault always occurs for V <sub>MONB/P</sub> $\geq$ 1.35 V | 1    | 1.25 | 1.35 | V      |

|                       | PD current monitor gain, IPD/IMONP               |                                                                                                                              |      | 1    |      | mA/mA  |

| VID                   | Differential input signal                        |                                                                                                                              | 200  |      | 1600 | mVp-p  |

|                       | SDOWN output high voltage                        | $I_{OH} = 100 \ \mu A \ sourcing$                                                                                            | 2.4  |      |      | V      |

|                       | SDOWN output low voltage                         | I <sub>OL</sub> = 1 mA sinking                                                                                               |      |      | 0.4  | V      |

|                       | DISABLE input impedance                          |                                                                                                                              | 4.7  | 7.4  | 10   | kΩ     |

|                       | DISABLE input high voltage                       |                                                                                                                              | 2    |      |      | V      |

|                       | DISABLE input low voltage                        |                                                                                                                              |      |      | 0.8  | V      |

| V <sub>PD</sub>       | Monitor diode voltage                            |                                                                                                                              |      |      | 1.6  | V      |

|                       | Monitor diode dc current range                   |                                                                                                                              | 18   |      | 1500 | μΑ     |

(1) Absolute accuracy refers to part-to-part variation.

### AC ELECTRICAL CHARACTERISTICS

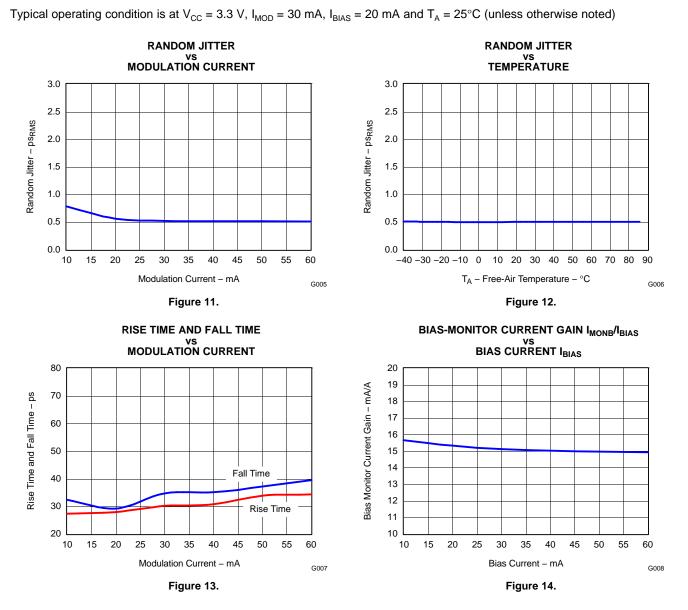

Typical operating condition is at V<sub>CC</sub> = 3.3 V,  $I_{MOD}$  = 30 mA,  $I_{BIAS}$  = 20 mA and  $T_A$  = 25°C. over recommended operating conditions (unless otherwise noted)

| PARAMETER                   |                              | TEST CONDITIONS                                               | MIN  | TYP  | MAX | UNIT   |

|-----------------------------|------------------------------|---------------------------------------------------------------|------|------|-----|--------|

|                             | Data rate                    |                                                               | 4.25 |      |     | Gbps   |

| I <sub>MOD</sub>            | Modulation current range     | Current into MOD+/MOD- pin;<br>$V_{MOD+}, V_{MOD-} \ge 0.6 V$ | 5    |      | 85  | mA     |

| I <sub>MOD-OFF</sub>        | Modulation off-current       | DISABLE = high or hard-fault occurred                         |      |      | 25  | μΑ     |

|                             | Modulation current stability |                                                               | -600 |      | 600 | ppm/°C |

| Modulation current absolute |                              | I <sub>MOD</sub> = 10 mA                                      |      | ±40% |     |        |

|                             | accuracy <sup>(1)</sup>      | I <sub>MOD</sub> = 80 mA                                      |      | ±25% |     |        |

SLLS688-NOVEMBER 2005

### AC ELECTRICAL CHARACTERISTICS (continued)

Typical operating condition is at V<sub>CC</sub> = 3.3 V, I<sub>MOD</sub> = 30 mA, I<sub>BIAS</sub> = 20 mA and T<sub>A</sub> = 25°C. over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                               | TEST CONDITIONS                                                                                                                        | MIN  | TYP  | MAX | UNIT              |

|--------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------------------|

|                    | Modulation current                      | $R_{MODTC} = 3.125 \text{ k}\Omega$                                                                                                    |      | 8300 |     | nnm/°C            |

|                    | temperature compensation <sup>(2)</sup> | R <sub>MODTC</sub> open                                                                                                                |      | 630  |     | ppm/°C            |

| t <sub>r</sub>     | Output rise time (20% to 80%)           | $V_{MOD+} \ge 1 \text{ V}, V_{MOD-} \ge 1 \text{ V}, I_{MOD} = 30 \text{ mA}$                                                          |      | 35   | 55  | ps                |

| t <sub>f</sub>     | Output fall time (80% to 20%)           | $V_{MOD+} \ge 1 \text{ V}, V_{MOD-} \ge 1 \text{ V}, I_{MOD} = 30 \text{ mA}$                                                          |      | 35   | 55  | ps                |

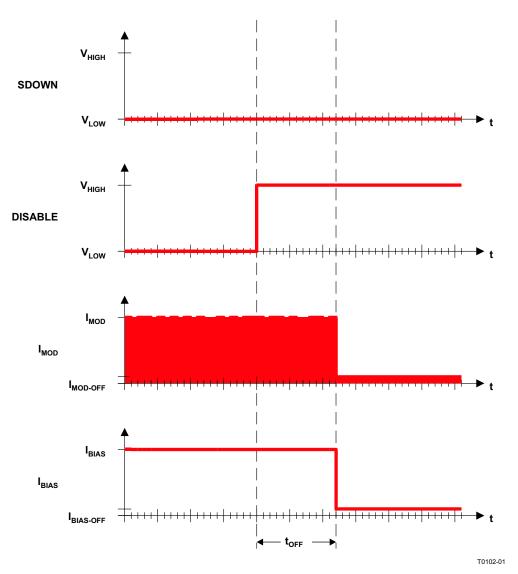

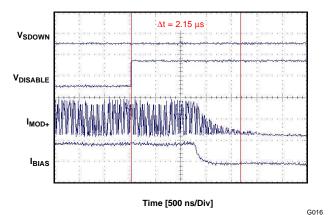

| t <sub>OFF</sub>   | Disable assert time (see Figure 4)      | Time from rising edge of DISABLE until output currents fall below the maximum limits of I <sub>MOD-OFF</sub> and I <sub>BIAS-OFF</sub> |      | 0.06 | 5   | μs                |

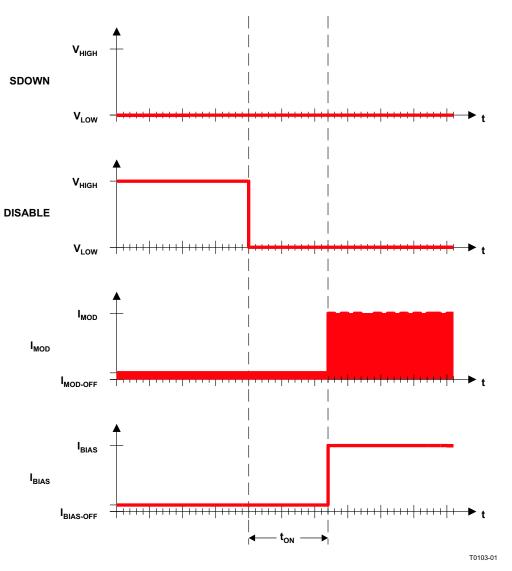

| t <sub>ON</sub>    | Disable negate time (see Figure 5)      | Time from falling edge of DISABLE until output is 90% of nominal                                                                       |      | 200  |     | μs                |

| t <sub>INIT</sub>  | Time to initialize                      | From power on or negation of SDOWN using DISABLE                                                                                       |      | 200  |     | μs                |

| t <sub>FAULT</sub> | Fault assert time                       | Time from fault to SDOWN rising edge                                                                                                   |      | 3.3  | 50  | μs                |

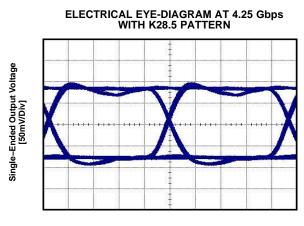

| t <sub>RESET</sub> | DISABLE reset (see Figure 6)            | Maximum spike pulse duration at DISABLE being ignored                                                                                  |      |      | 10  | μs                |

|                    |                                         | DISABLE high time required to reset SDOWN                                                                                              | 20   |      |     | μs                |

|                    | Output overshoot/undershoot             |                                                                                                                                        | -29% |      | 29% |                   |

|                    | Random jitter                           | I <sub>MOD</sub> = 60 mA                                                                                                               |      | 0.6  | 0.9 | ps <sub>RMS</sub> |

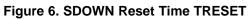

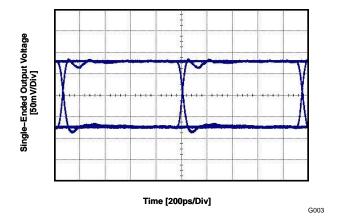

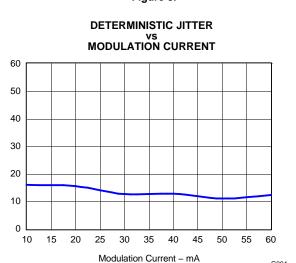

|                    |                                         | 10 mA $\leq$ I <sub>MOD</sub> $\leq$ 60 mA, with K28.5 pattern at 4.25 Gbps                                                            |      | 15   | 30  | ps <sub>p-p</sub> |

| DJ                 | Deterministic jitter <sup>(3)</sup>     | 10 mA $\leq$ $I_{MOD}$ $\leq$ 60 mA, with 2^{23} –1 PRBS or equivalent pattern at 2.67 Gbps                                            |      | 13   | 32  | ps <sub>p-p</sub> |

|                    | ·                                       | K28.5 pattern at 1.06 Gbps                                                                                                             |      | 5    |     | ps <sub>p-p</sub> |

|                    |                                         | 2 <sup>23</sup> – 1 PRBS or equivalent pattern at 155<br>Mbps                                                                          |      | 10   |     | ps <sub>p-p</sub> |

(2) For a given external resistor connected to the MODTC pin, the modulation-current temperature compensation varies due to part-to-part variations.

(3) Jitter measured at positive edge and negative edge crossing of eye diagram.

SLLS688-NOVEMBER 2005

Figure 4. DISABLE Assert Time TOFF

SLLS688-NOVEMBER 2005

Figure 5. DISABLE Negate Time TON

SLLS688-NOVEMBER 2005

G002

G004

SLLS688-NOVEMBER 2005

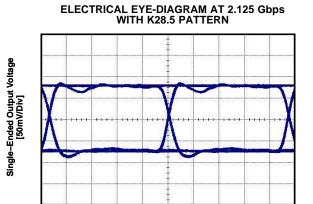

### **TYPICAL CHARACTERISTICS**

Typical operating condition is at V<sub>CC</sub> = 3.3 V,  $I_{MOD}$  = 30 mA,  $I_{BIAS}$  = 20 mA and  $T_A$  = 25°C (unless otherwise noted)

G001

Deterministic Jitter Including PWD - psp-p

Time [50ps/Div]

Figure 7.

ELECTRICAL EYE-DIAGRAM AT 1.0625 Gbps WITH K28.5 PATTERN

Figure 9.

Time [100ps/Div]

Figure 8.

Figure 10.

14

SLLS688-NOVEMBER 2005

15

SLLS688-NOVEMBER 2005

G010

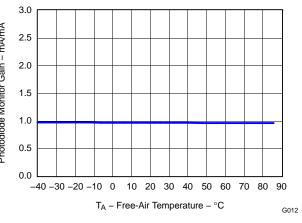

### **TYPICAL CHARACTERISTICS (continued)**

Typical operating condition is at V<sub>CC</sub> = 3.3 V,  $I_{MOD}$  = 30 mA,  $I_{BIAS}$  = 20 mA and  $T_A$  = 25°C (unless otherwise noted)

G011

10 20 30 40 50 60 70 80 90 100  $R_{APCSET}$  – External Resistor –  $k\Omega$

Figure 17.

PHOTODIODE MONITOR GAIN IMONP/IPD vs TEMPERATURE

60 70 80 90 100

Figure 18.

0.2 0.0

0

SLLS688-NOVEMBER 2005

### **TYPICAL CHARACTERISTICS (continued)**

Typical operating condition is at  $V_{CC}$  = 3.3 V,  $I_{MOD}$  = 30 mA,  $I_{BIAS}$  = 20 mA and  $T_A$  = 25°C (unless otherwise noted)

rigato tor

Figure 21.

DISABLE ASSERT TIME TOFF

Figure 22.

. . . . .

G018

Figure 24.

### **APPLICATION INFORMATION**

Figure 25 shows the ONET4211LD connected with a dc-coupled interface to the laser diode; alternatively, the ONET4211LD laser driver can be ac-coupled.

Figure 25. Basic Application Circuit With DC-Coupled Interface Between the ONET4211LD and the Laser Diode

APC loop instability can occur with large inductive loading on the BIAS pin. To ensure loop stability in this case, it is recommended to connect a 1-nF capacitor to ground at the BIAS pin.

(7)

SLLS688-NOVEMBER 2005

# APPLICATION INFORMATION (continued) SELECT A LASER

In the design example according to Figure 25, the ONET4211LD is dc-coupled to a typical communication-grade laser diode capable of operating at 4.25 Gb/s with the following specifications shown in Table 2.

|                  | PARAMETER                    | VALUE | UNITS |

|------------------|------------------------------|-------|-------|

| λ                | Wavelength                   | 1310  | nm    |

| $P_{AVG}$        | Average Optical Output Power | 5     | mW    |

| I <sub>TH</sub>  | Threshold current            | 10    | mA    |

| ρ <sub>ΜΟΝ</sub> | Laser-to-monitor transfer    | 0.05  | mA/mW |

| η                | Laser slope efficiency       | 0.2   | mW/mA |

#### **Table 2. Laser Diode Specifications**

#### SELECT APCSET RESISTOR

When the APC loop is activated, the desired average optical output power  $P_{AVG}$  is defined by characteristics of the monitor diode and by the APCSET resistor  $R_{APCSET}$ . The relation between the monitor photodiode current  $I_{PD}$  and the average optical output power  $P_{AVG}$  is given by Equation 7:

$$I_{PD}[A] = P_{AVG}[W] \times \rho_{MON}[A/W]$$

The R<sub>APCSET</sub> resistor is calculated by Equation 8:

$$\mathsf{R}_{\mathsf{APCSET}}[\Omega] = \frac{4.69 \,\mathsf{V}}{\mathsf{I}_{\mathsf{PD}}[\mathsf{A}]} = \frac{4.69 \,\mathsf{V}}{\mathsf{P}_{\mathsf{AVG}}[\mathsf{W}] \times \rho_{\mathsf{MON}}[\mathsf{A}/\mathsf{W}]} \tag{8}$$

For the laser diode specified in Table 2 and the desired average optical output power of 5 mW, R<sub>APCSET</sub> is calculated as in Equation 9:

$$\mathsf{R}_{\mathsf{APCSET}}[\Omega] = \frac{4.69 \text{ V}}{\mathsf{P}_{\mathsf{AVG}}[\mathsf{W}] \times \rho_{\mathsf{MON}}[\mathsf{A}/\mathsf{W}]} = \frac{4.69 \text{ V}}{5 \text{ mW} \times 0.05 \text{ mA/mW}} = 18.75 \text{ k}\Omega$$

(9)

Note that the monitor photodiode current I<sub>PD</sub> must not exceed 1.5 mA, corresponding to a minimum APCSET resistor  $R_{APCSET.MIN} = 3.1 \text{ k}\Omega$ .

#### SELECT MODSET RESISTOR

Modulation current  $I_{MOD}$  is dependent on the required optical output peak-to-peak power  $P_{p-p}$  or the average optical power  $P_{AVG}$ .  $I_{MOD}$  can be calculated using the laser slope efficiency  $\eta$  and the desired extinction ratio  $r_e$ :

$$I_{MOD}[A] = \frac{P_{p-p}[W]}{\eta[W/A]} = \frac{2 \times P_{AVG}[W] \times \frac{r_{e}^{-1}}{r_{e}^{+1}}}{\eta[W/A]}$$

(10)

Using the laser diode parameters from Table 2 and assuming an extinction ratio  $r_e = 8 \text{ dB}$  ( $\approx 6.3$ ) for an average optical power  $P_{AVG} = 5 \text{ mW}$ , the required modulation current results as:

$$I_{MOD} = \frac{2 \times 5 \text{ mW} \times \frac{6.3 - 1}{6.3 + 1}}{0.2 \text{ mW/mA}} = 36.3 \text{ mA}$$

(11)

The modulation current is adjustable, with a selectable temperature coefficient TC according to the relation:

$$I_{MOD}[A] = I_{MOD0}[A] \times \left(1 + TC \times \left(T[^{\circ}C] - T_{0}[^{\circ}C]\right)\right)$$

(12)

where T is the ambient temperature in °C and T<sub>0</sub> is the reference temperature (T<sub>0</sub> = 60°C).

The temperature coefficient TC of the modulation current is typically adjustable between 630 ppm/°C and 8300 ppm/°C.

For calculation of the required external resistor R<sub>MODSET</sub> for a given modulation current and a given temperature, the formula can be modified as follows:

SLLS688-NOVEMBER 2005

$$\mathsf{R}_{\mathsf{MODSET}}[\Omega] = \frac{265 \text{ V}}{\mathsf{I}_{\mathsf{MOD}}[\mathsf{A}]} \times \left(1 + \mathsf{TC} \times \left(\mathsf{T}[^{\circ}\mathsf{C}] - \mathsf{T}_{\mathsf{0}}[^{\circ}\mathsf{C}]\right)\right)$$

(13)

TEXAS TRUMENTS www.ti.com

If 4000 ppm/°C is the desired temperature coefficient and the modulation current from the preceding example, 36.3 mA, is required at a temperature of 25°C, the MODSET resistor  $R_{MODSET}$  is given by Equation 14.

$$\mathsf{R}_{\mathsf{MODSET}}[\Omega] = \frac{265 \,\mathsf{V}}{36.3 \,\mathsf{mA}} \times \left(1 + \frac{4000 \,\mathsf{ppm}}{^{\circ}\mathsf{C}} \times (25^{\circ}\mathsf{C} - 60^{\circ}\mathsf{C})\right) = 6.3 \,\mathsf{k}\Omega \tag{14}$$

Note that the modulation current  $I_{MOD}$  must not exceed 85 mA over the complete temperature range, corresponding to a minimum MODSET resistor  $R_{MODSET,MIN} = 3.1 \text{ k}\Omega$ .

#### SELECT MODTC RESISTOR

The R<sub>MODTC</sub> resistor is used to program a modulation temperature coefficient that can be used to compensate for the decreased slope efficiency of the laser at a higher temperature. The temperature coefficient  $TC_{LD}$  of the laser can be calculated using the slope efficiency  $\eta_1$  at temperature  $T_1$  and  $\eta_2$  at temperature  $T_2$  as shown in Equation 15:

$$TC_{LD}\left[\frac{1}{^{\circ}C}\right] = \frac{\eta_{2}[W/A] - \eta_{1}[W/A]}{\eta_{1}[W/A] \times (T_{2}[^{\circ}C] - T_{1}[^{\circ}C])} \times 10^{6}$$

(15)

As an example, for the laser in Table 2, the slope efficiency at temperature  $T_1 = 25^{\circ}C$  is  $\eta_1 = 0.2$  mW/mA. At temperature  $T_2 = 85^{\circ}C$ , the slope efficiency is  $\eta_2 = 0.15$  mW/mA. The corresponding temperature coefficient TC<sub>LD</sub> of the laser can be calculated:

$$TC_{LD} = \frac{0.15 \text{ mW/mA} - 0.2 \text{ mW/mA}}{0.2 \text{ mW/mA} \times (85^{\circ}\text{C} - 25^{\circ}\text{C})} \times 10^{6} = -4167 \frac{1}{^{\circ}\text{C}}$$

(16)

The MODTC resistor  $R_{MODTC}$  can be used to compensate the laser temperature coefficient  $TC_{LD}$  in order to maintain the same optical output swing within a range of 630 ppm up to 8300 ppm. For this,  $R_{MODTC}$  may be programmed as follows:

$$\mathsf{R}_{\mathsf{MODTC}} = \frac{24 \,\Omega}{(\mathsf{TC} - 630 \,\mathsf{ppm}) \times \left[\frac{1}{\circ \mathsf{C}}\right] \times \circ \mathsf{C}}$$

(17)

To compensate for the decreased slope efficiency of the laser in Table 2, TC must be 4167 ppm/°C.

This leads to the following MODTC resistor R<sub>MODTC</sub>:

$$\mathsf{R}_{\mathsf{MODTC}} = \frac{24 \,\Omega}{\frac{4167 \,\mathsf{ppm} - 630 \,\mathsf{ppm}}{^{\circ}\mathsf{C}}} = 6.8 \,\mathsf{k}\Omega \tag{18}$$

#### SELECT BIASMAX RESISTOR

The BIASMAX resistor R<sub>BIASMAX</sub> is used to limit the bias current applied to the laser diode.

To calculate R<sub>BIASMAX</sub>, the maximum threshold current at 85°C and end of life must be determined. The maximum bias current for the dc-coupled interface can be approximated by Equation 19.

$$I_{\text{BIASMAX}}[A] = I_{\text{THMAX}}[A]$$

<sup>(19)</sup>

R<sub>BIASMAX</sub> can be set by Equation 20.

$$\mathsf{R}_{\mathsf{BIASMAX}}[\Omega] = \frac{343 \,\mathsf{V}}{\mathsf{I}_{\mathsf{BIASMAX}}[\mathsf{A}]} = \frac{343 \,\mathsf{V}}{\mathsf{I}_{\mathsf{THMAX}}[\mathsf{A}]} \tag{20}$$

For the example laser diode, the maximum threshold current is 40 mA at 85°C. Therefore, R<sub>BIASMAX</sub> can be approximated by Equation 21.

SLLS688-NOVEMBER 2005

$\mathsf{R}_{\mathsf{BIASMAX}} = \frac{343 \text{ V}}{40 \text{ mA}} = 8.6 \text{ k}\Omega$

### SELECT $V_{\text{MONB}}$ AND $V_{\text{MONP}}$ RANGE

Monitoring the bias current is achieved by taking the fractional (1/68) bias current and developing a voltage across an external resistor to ground. Equation 22 provides the value for  $V_{MONB}$  for a resistor value equal to 768  $\Omega$ .

$$V_{\text{MONB}}[V] = \frac{\mathsf{R}_{\text{MONB}}[\Omega] \times \mathsf{I}_{\text{BIAS}}[A]}{68} = \frac{768 \ \Omega \times \mathsf{I}_{\text{BIAS}}[A]}{68} = 11.29 \ \Omega \times \mathsf{I}_{\text{BIAS}}[A] \tag{22}$$

Monitoring of the photo current is achieved by taking a mirror of  $I_{PD}$  and developing a voltage across an external resistor to ground. Equation 23 provides the value for  $V_{MONP}$  for a resistor equal to 200  $\Omega$ .

$$V_{\text{MONP}}[V] = R_{\text{MONP}}[\Omega] \times I_{\text{PD}}[A] = 200 \ \Omega \times I_{\text{PD}}[A]$$

<sup>(23)</sup>

### LASER DIODE INTERFACE

The output stage of the ONET4211LD is optimized for driving a  $20 \cdot \Omega$  load. The combination of a damping resistor, R<sub>D</sub>, along with the resistance of the laser diode, must be  $20 \cdot \Omega$  for impedance matching. The suggested typical value for R<sub>D</sub> is 6  $\Omega$  to 15  $\Omega$ . A bypass capacitor of 10 nF placed close to the laser anode also helps to optimize performance.

# PACKAGE OPTION ADDENDUM

16-Dec-2005

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup>  | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| ONET4211LDRGER   | ACTIVE                | QFN             | RGE                | 24   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| ONET4211LDRGERG4 | ACTIVE                | QFN             | RGE                | 24   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| ONET4211LDRGET   | ACTIVE                | QFN             | RGE                | 24   | 250            | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| ONET4211LDRGETG4 | ACTIVE                | QFN             | RGE                | 24   | 250            | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### **MECHANICAL DATA**

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-Leads (QFN) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. Falls within JEDEC MO-220.

#### TEXAS INSTRUMENTS www.ti.com

# THERMAL PAD MECHANICAL DATA RGE (S-PQFP-N24)

THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB), the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to a ground plane or special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, Quad Flatpack No-Lead Logic Packages, Texas Instruments Literature No. SCBA017. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

#### Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265