### 捷多邦,专业PCB打样工厂,24小时加急出货

February 2006

### National Semiconductor

### DS90C3202 3.3V 8 MHz to 135 MHz Dual FPD-Link Receiver

### **General Description**

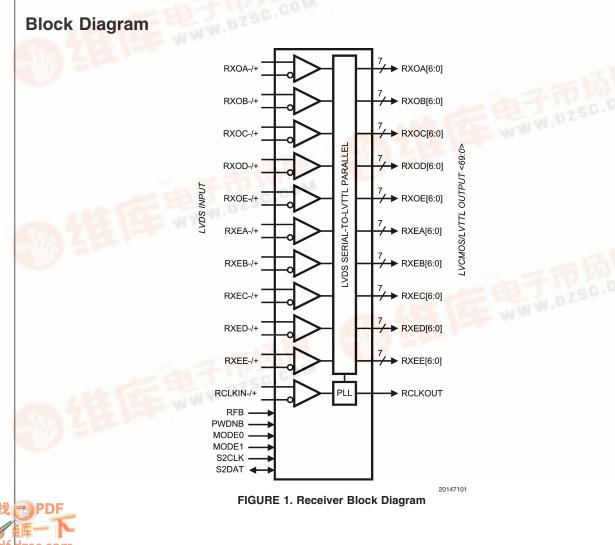

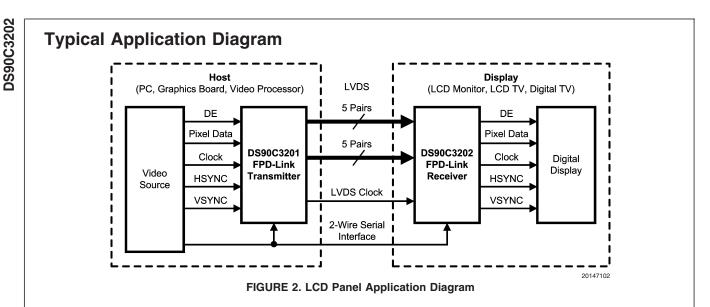

The DS90C3202 is a 3.3V single/dual FPD-Link 10-bit color receiver is designed to be used in Liquid Crystal Display TVs, LCD Monitors, Digital TVs, and Plasma Display Panel TVs. The DS90C3202 is designed to interface between the digital video processor and the display device using the low-power, low-EMI LVDS (Low Voltage Differential Signaling) interface. The DS90C3202 converts up to ten LVDS data streams back into 70 bits of parallel LVCMOS/LVTTL data. The receiver can be programmed with rising edge or falling edge clock. Optional wo-wire serial programming allows fine tuning in development and production environments. With an input clock at 135 MHz, the maximum transmission rate of each LVDS line is 945 Mbps, for an aggregate throughput rate of 9.45 Gbps (945 Mbytes/s). This allows the dual 10-bit LVDS Receiver to support resolutions up to HDTV.

### Features

- Up to 9.45 Gbit/s data throughput

- 8 MHz to 135 MHz input clock support

- Supports up to QXGA panel resolutions

- Supports HDTV panel resolutions and frame rates up to 1920 x 1080p

- LVDS 30-bit, 24-bit or 18-bit color data inputs

- Supports single pixel and dual pixel interfaces

- Supports spread spectrum clocking

- Two-wire serial communication interface

- Programmable clock edge and control strobe select

- Power down mode

- +3.3V supply voltage

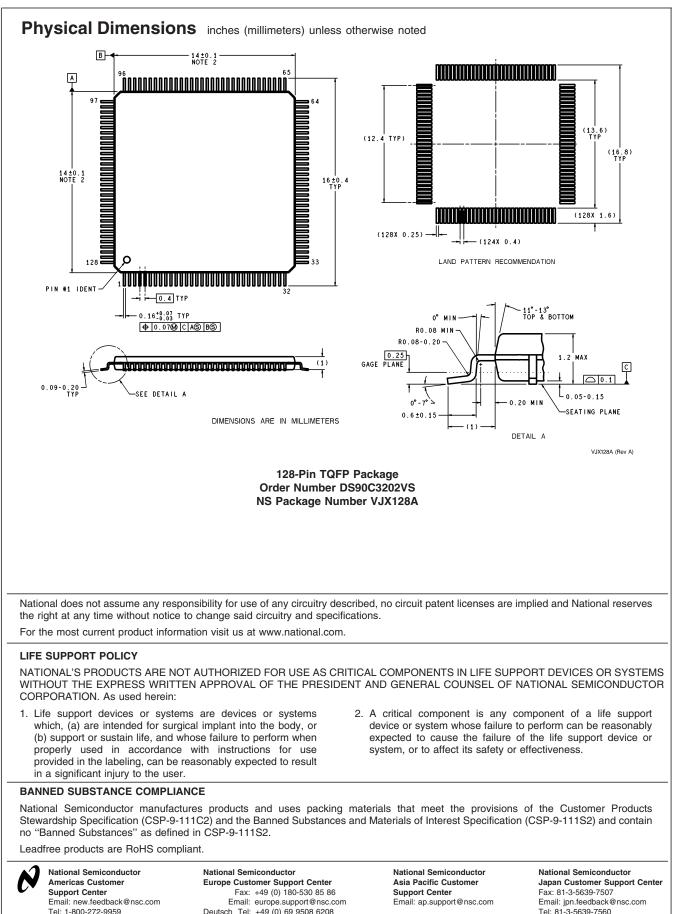

- 128-pin TQFP Package

- Compliant to TIA/EIA-644-A-2001 LVDS Standard

# DS90C3202 3.3V 8 MHz 6 135 **MHz Dual FPD-Link Receiver**

© 2006 National Semiconductor Corporation DS201471

### **Functional Description**

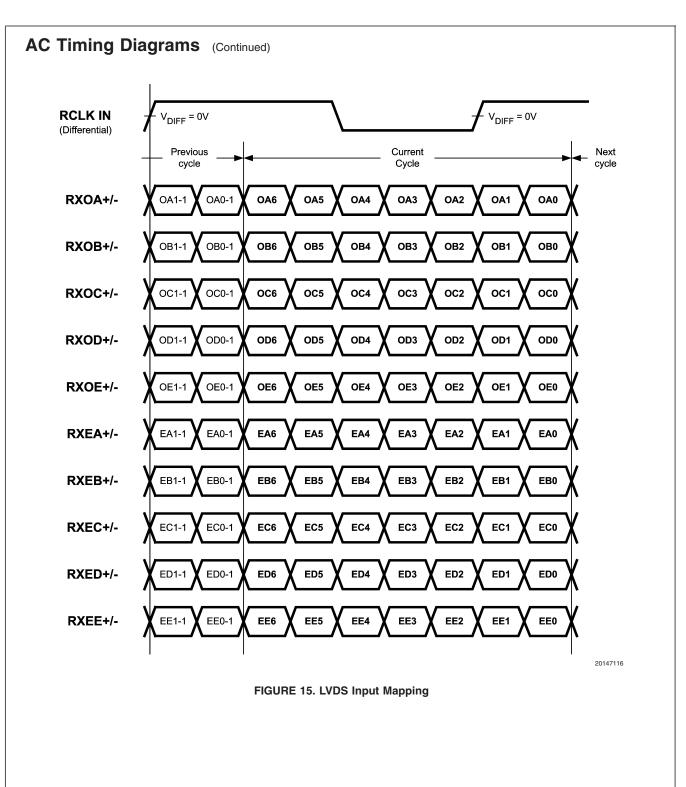

The DS90C3201 and DS90C3202 are a dual 10-bit color Transmitter and Receiver FPD-Link chipset designed to transmit data at clocks speeds from 8 to 135 MHz. DS90C3201 and DS90C3202 are designed to interface between the digital video processor and the display using a LVDS interface. The DS90C3201 transmitter serializes 2 channels of video data (10-bit each for RGB for each channel, totaling 60 bits) and control signals (HSYNC, VSYNC, DE and two user-defined signals) along with clock signal to 10 channels of LVDS signals and transmits them. The DS90C3202 receiver converts 10 channels of LVDS signals into parallel signals and outputs 2 channels of video data (10-bit each for RGB for each channel, totaling 60 bits) and control signals (HSYNC, VSYNC, DE and two user-defined signals) along with clock signal. The dual high speed LVDS channels supports single pixel in-single pixel out and dual pixel in-dual pixel out transmission modes. The FPD-Link chipset is suitable for a variety of display applications including LCD Monitors, LCD TV, Digital TV, and DLP TV, and Plasma Display Panels.

Using a true 10-bit color depth system, the 30-bit RGB color produces over 1.07 billion colors to represent High Definition (HD) displays in their most natural color, surpassing the maximum 16.7 million colors achieved by 6/8-bit color conventionally used for large-scale LCD televisions and LCD monitors.

#### LVDS RECEIVER

The LVDS Receiver receives input RGB video data and control signal timing.

### SELECTABLE OUTPUT DATA STROBE

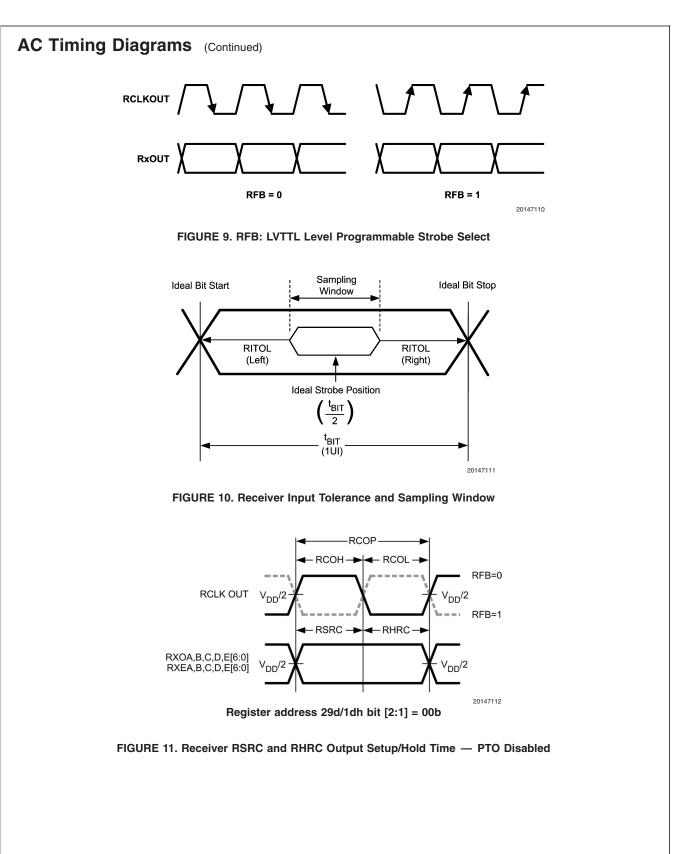

The Receiver output data edge strobe can be latched on the rising or falling edges of clock signal. The dedicated RFB pin is used to program output strobe select on the rising edge of RCLK or the falling edge of RCLK.

#### 2-WIRE SERIAL COMMUNICATION INTERFACE

Optional Two-Wire serial interface programming allows fine tuning in development and production environments. The Two-Wire serial interface provides several capabilities to reduce EMI and to customize output timing. These capabilities are selectable/programmable via Two-Wire serial interface: Programmable Skew Rates, Progress Turn On Function, Input/Output Channel Control.

#### **PROGRAMMABLE SKEW RATES**

Programmable edge rates allow the LVCMOS/LVTTL Data and Clock outputs to be adjusted for better impedance matching for noise and EMI reduction. The individual output drive control registers for Rx data out and Rx clock out are programmable via Two-Wire serial interface.

#### **PROGRESS TURN ON FUNCTION**

Progress Turn On (PTO) function aligns the two output channels of LVCMOS/LVTLL in either a non-skew data format (simultaneous switching) or a skewed data format (staggered). The skewed format delays the selected channel data and staggers the outputs. This reduces the number of outputs switching simultaneously, which lowers EMI radiation and minimizes ground bounce. Feature is controlled via Two-Wire serial interface.

#### **INPUT/OUTPUT CHANNEL CONTROL**

Full independent control for input/output channels can be disabled to minimize power supply line noise and overall power dissipation. Feature is configured via Two-Wire serial interface

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>DD</sub> ) | -0.3V to +4V                      |

|-----------------------------------|-----------------------------------|

| LVCMOS/LVTTL Input                |                                   |

| Voltage                           | –0.3V to (V <sub>DD</sub> + 0.3V) |

| LVCMOS/LVTTL Output               |                                   |

| Voltage                           | –0.3V to (V <sub>DD</sub> + 0.3V) |

| LVDS Receiver Input Voltage       | –0.3V to (V <sub>DD</sub> + 0.3V) |

| Junction Temperature              | +150°C                            |

| Storage Temperature               | –65°C to +150°C                   |

| Lead Temperature                  |                                   |

| (Soldering, 10 sec.)              | +260°C                            |

| Maximum Package Power Dis         | sipation Capacity @ 25°C          |

| 128 TQFP Package:                 | 1.4W                              |

| Package Derating:   | 25.6mW/°C above +25°C |

|---------------------|-----------------------|

| ESD Rating:         |                       |

| (HBM, 1.5kΩ, 100pF) | > 2 kV                |

| (EIAJ, 0Ω, 200pF)   | > 200 V               |

### Recommended Operating Conditions

|                                    | Min  | Nom | Мах      | Units      |

|------------------------------------|------|-----|----------|------------|

| Supply Voltage (V <sub>DD</sub> )  | 3.15 | 3.3 | 3.6      | V          |

| Operating Free Air                 |      |     |          |            |

| Temperature (T <sub>A</sub> )      | 0    | +25 | +70      | °C         |

| Supply Noise Voltage ( $V_{P-P}$ ) |      |     | ±100     | $mV_{p-p}$ |

| Receiver Input Range               | 0    |     | $V_{DD}$ | V          |

| Input Clock Frequency (f)          | 8    |     | 135      | MHz        |

|                                    |      |     |          |            |

### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol             | Parameter                             | Conditions                |                         | Min   | Тур  | Max                  | Units |

|--------------------|---------------------------------------|---------------------------|-------------------------|-------|------|----------------------|-------|

| CMOS/TTL           | DC SPECIFICATIONS (Rx outpu           | ts, control input         | s and outputs)          | •     |      |                      |       |

| V <sub>IH</sub>    | High Level Input Voltage              |                           |                         | 2.0   |      | V <sub>DD</sub>      | V     |

| V <sub>IL</sub>    | Low Level Input Voltage               |                           |                         | 0     |      | 0.8                  | V     |

| V <sub>OH</sub>    | High Level Output Voltage             | Rx clock out              | I <sub>OH</sub> = -4 mA | 2.4   |      |                      | V     |

|                    |                                       | Rx data out               | I <sub>он</sub> = –2 mA |       |      |                      |       |

| V <sub>OL</sub>    | Low Level Output Voltage              | Rx clock out              | I <sub>OL</sub> = +4 mA |       |      | 0.4                  | V     |

|                    |                                       | Rx data out               | I <sub>OL</sub> = +2 mA |       |      |                      |       |

| V <sub>CL</sub>    | Input Clamp Voltage                   | $I_{CL} = -18 \text{ mA}$ |                         |       | -0.8 | -1.5                 | V     |

| I <sub>IN</sub>    | I <sub>IN</sub> Input Current         | $V_{IN} = V_{DD}$         |                         |       |      | +10                  | μA    |

|                    |                                       | $V_{IN} = 0V$             |                         | -10   |      |                      | μA    |

| l <sub>os</sub>    | Output Short Circuit Current          | V <sub>OUT</sub> = 0V     |                         |       |      | -120                 | mA    |

| LVDS REC           | EIVER DC SPECIFICATIONS               |                           |                         |       |      |                      |       |

| V <sub>TH</sub>    | Differential Input High Threshold     | $V_{CM} = +1.2V$          |                         |       |      | +100                 | mV    |

| V <sub>TL</sub>    | Differential Input Low Threshold      |                           |                         | -100  |      |                      | mV    |

| V <sub>IN</sub>    | Input Voltage Range<br>(Single-ended) |                           |                         | 0     |      | V <sub>DD</sub>      | V     |

| IV <sub>ID</sub> I | Differential Input Voltage            |                           |                         | 0.200 |      | 0.600                | V     |

| V <sub>CM</sub>    | Differential Common Mode<br>Voltage   |                           |                         | 0.2   | 1.2  | V <sub>DD</sub> -0.1 | V     |

| I <sub>IN</sub>    | Input Current                         | $V_{IN} = +2.4V, V_{D}$   | <sub>D</sub> = 3.6V     |       |      | ±10                  | μA    |

|                    |                                       | $V_{IN} = 0V, V_{DD} =$   | 3.6V                    |       |      | ±10                  | μA    |

### Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol                  | Parameter                                                                            | Conditions                                                                |             | Min       | Тур | Max | Units |    |  |  |

|-------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|-----------|-----|-----|-------|----|--|--|

| RECEIVER SUPPLY CURRENT |                                                                                      |                                                                           |             |           |     |     |       |    |  |  |

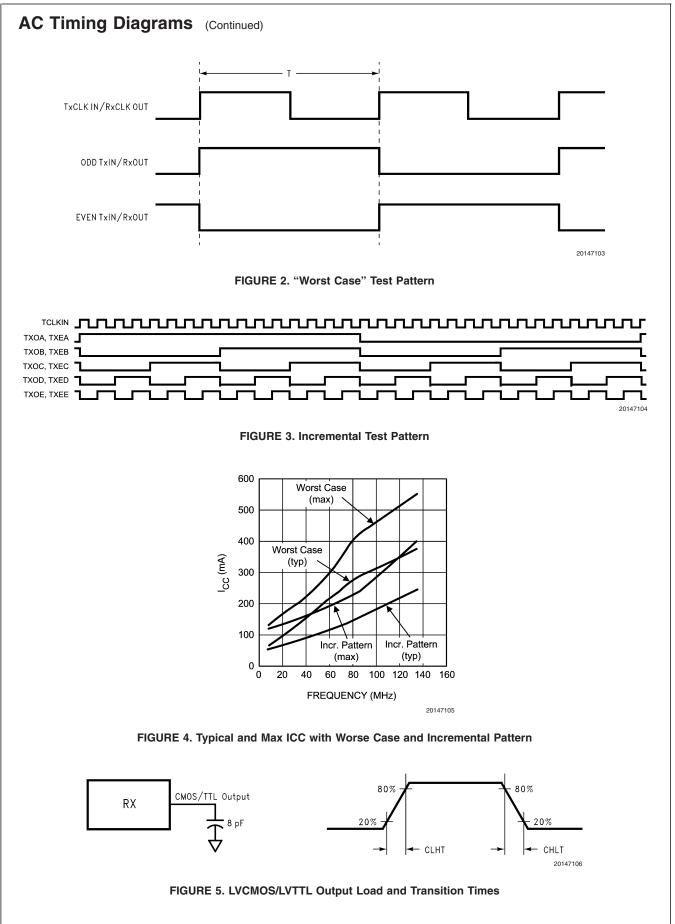

| ICCRW                   | Worst Case                                                                           | C <sub>L</sub> = 8 pF,<br>Worst Case                                      | f = 8 MHz   |           | 65  | 130 | mA    |    |  |  |

|                         | (Figures 2, 4)                                                                       | Pattern<br>Default Register<br>Settings                                   | f = 135 MHz |           | 375 | 550 | mA    |    |  |  |

| ICCRG                   | ICCRG Receiver Supply Current<br>Incremental Test Pattern<br>( <i>Figures 3, 4</i> ) | Incremental Test Pattern Worst Case                                       |             | f = 8 MHz |     | 55  | 120   | mA |  |  |

|                         |                                                                                      | ( <i>Figures 3, 4</i> ) Pattern<br>Default Register<br>Settings           | f = 135 MHz |           | 245 | 400 | mA    |    |  |  |

| ICCRZ                   | Receiver Supply Current<br>Power Down                                                | PDWNB = Low<br>Receiver Outputs<br>during Powerdown<br>Default Register S | n mode.     |           |     | 2   | mA    |    |  |  |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Typical values are given for  $V_{DD}$  = 3.3V and T  $_A$  = +25  $^\circ\text{C}.$

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified.

| Symbol       | Parameter                                                                                         | Condition/               | Min  | Тур    | Max    | Units |

|--------------|---------------------------------------------------------------------------------------------------|--------------------------|------|--------|--------|-------|

|              |                                                                                                   | Reference                |      |        |        |       |

| CLHT         | LVCMOS/LVTTL Low-to-High Transition                                                               | Rx clock out             |      | 1.45   | 2.10   | ns    |

|              | Time, $C_L = 8pF$ , ( <i>Figure 5</i> ) (Note 4)                                                  |                          |      |        |        |       |

|              | Register addr 28d/1ch,                                                                            | -                        |      |        |        |       |

|              | bit [2] (RCLK)=0b (Default),                                                                      | Rx data out              |      | 2.40   | 3.50   | ns    |

|              | bit [1] (RXE) =0b (Default),<br>bit [0] (DXO) $=$ 0b (Default)                                    |                          |      |        |        |       |

| CHLT         | bit [0] (RXO) =0b (Default)                                                                       | Dy clock out             |      | 1.05   | 0.00   |       |

| CHLI         | LVCMOS/LVTTL High-to-Low Transition<br>Time, $C_L = 8pF$ , ( <i>Figure 5</i> ) (Note 4)           | Rx clock out             |      | 1.35   | 2.20   | ns    |

|              | Register addr 28d/1ch,                                                                            |                          |      |        |        |       |

|              | bit [2] (RCLK)=0b (Default),                                                                      | Rx data out              |      | 2.40   | 3.60   | ns    |

|              | bit [1] (RXE) =0b (Default),                                                                      |                          |      | 2.40   | 0.00   | 115   |

|              | bit [0] (RXO) =0b (Default)                                                                       |                          |      |        |        |       |

| CLHT         | LVCMOS/LVTTL Low-to-High Transition                                                               | Rx clock out             |      | 2.45   |        | ns    |

| Programmable | Time, $C_1 = 8pF$ , ( <i>Figure 5</i> ) (Note 4)                                                  |                          |      |        |        |       |

| adjustment   | Register addr 28d/1ch,                                                                            |                          |      |        |        |       |

| -            | bit [2] (RCLK)=1b (Default),                                                                      | Rx data out              |      | 3.40   |        | ns    |

|              | bit [1] (RXE) =1b (Default),                                                                      |                          |      |        |        |       |

|              | bit [0] (RXO) =1b (Default)                                                                       |                          |      |        |        |       |

| CHLT         | LVCMOS/LVTTL High-to-Low Transition                                                               | Rx clock out             |      | 2.35   |        | ns    |

| Programmable | Time, $C_L = 8pF$ , ( <i>Figure 5</i> ) (Note 4)                                                  |                          |      |        |        |       |

| adjustment   | Register addr 28d/1ch,                                                                            |                          |      |        |        |       |

|              | bit [2] (RCLK)=0b (Default),                                                                      | Rx data out              |      | 3.40   |        | ns    |

|              | bit [1] (RXE) =0b (Default),                                                                      |                          |      |        |        |       |

|              | bit [0] (RXO) =0b (Default)                                                                       |                          |      |        |        |       |

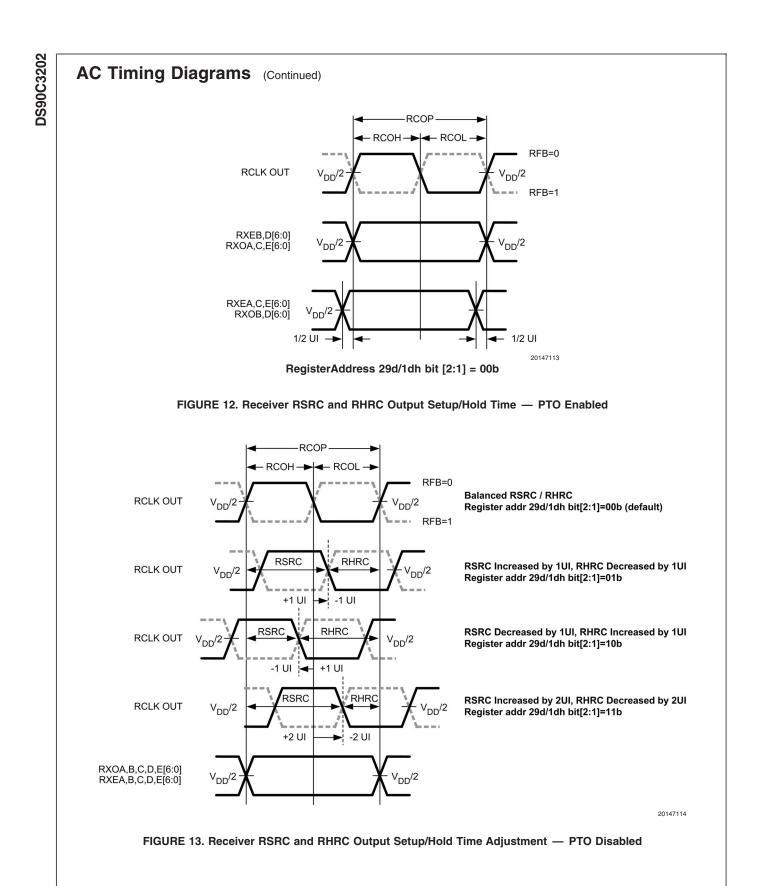

| RCOP         | RCLK OUT Period ( <i>Figures 11, 12</i> ) (Note 4)                                                | 8–135 MHz                | 7.4  | Т      | 125    | ns    |

| RCOH         | RCLK OUT High Time ( <i>Figures 11, 12</i> )                                                      | Rx clock out             | 0.4T | 0.5T   | 0.6T   | ns    |

| RCOL         | RCLK OUT Low Time ( <i>Figures 11, 12</i> )                                                       | Rx clock out             | 0.4T | 0.5T   | 0.6T   | ns    |

| RSRC         | RxOUT Setup to RCLK OUT ( <i>Figures 11, 12</i> )                                                 | (Note 5)                 |      | 0.5T   |        | ns    |

|              | Register addr 29d/1dh [2:1]= 00b (Default)                                                        |                          |      | 0.57   |        |       |

| RHRC         | RxOUT Hold to RCLK OUT ( <i>Figures 11, 12</i> ) (I<br>Register addr 29d/1dh [2:1]= 00b (Default) | NOLE 5)                  |      | 0.5T   |        | ns    |

| RSRC/RHRC    | Register addr 29d/1dh [2:1] = 01b, ( <i>Figures 13</i>                                            | 2 14) (Noto 6)           |      | +1UI / |        | ne    |

| Programmable | RSRC increased from default by 1UI                                                                | (14) (1000 0)            |      | -1UI   |        | ns    |

| Adjustment   | RHRC decreased from default by 1UI                                                                |                          |      |        |        |       |

| Agustinont   | Register addr 29d/1dh [2:1] = 10b, ( <i>Figures 13</i>                                            | 3 14) (Note 6)           |      | -1UI / |        | ns    |

|              | RSRC decreased from default by 1UI                                                                | , 14) (1000 0)           |      | +1UI   |        | 110   |

|              | RHRC increased from default by 1UI                                                                |                          |      |        |        |       |

|              | Register addr 29d/1dh [2:1] = 11b, ( <i>Figures 13</i>                                            | 3. 14) (Note 6)          |      | +2UI / |        | ns    |

|              | RSRC increased from default by 2UI                                                                |                          | -2UI |        |        |       |

|              | RHRC decreased from default by 2UI                                                                |                          |      | _      |        |       |

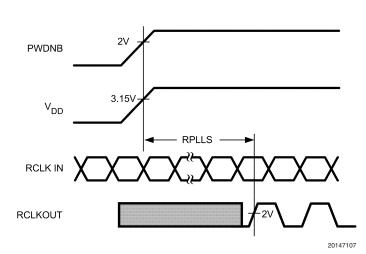

| RPLLS        | Receiver Phase Lock Loop Set (Figure 6)                                                           |                          |      |        | 10     | ms    |

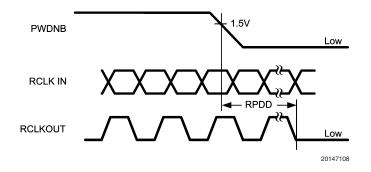

| RPDD         | Receiver Powerdown Delay (Figure 7)                                                               |                          |      |        | 100    | ns    |

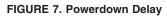

| RPDL         | Receiver Propagation Delay — Latency (Figu                                                        | re 8)                    |      |        | 4*RCLK | ns    |

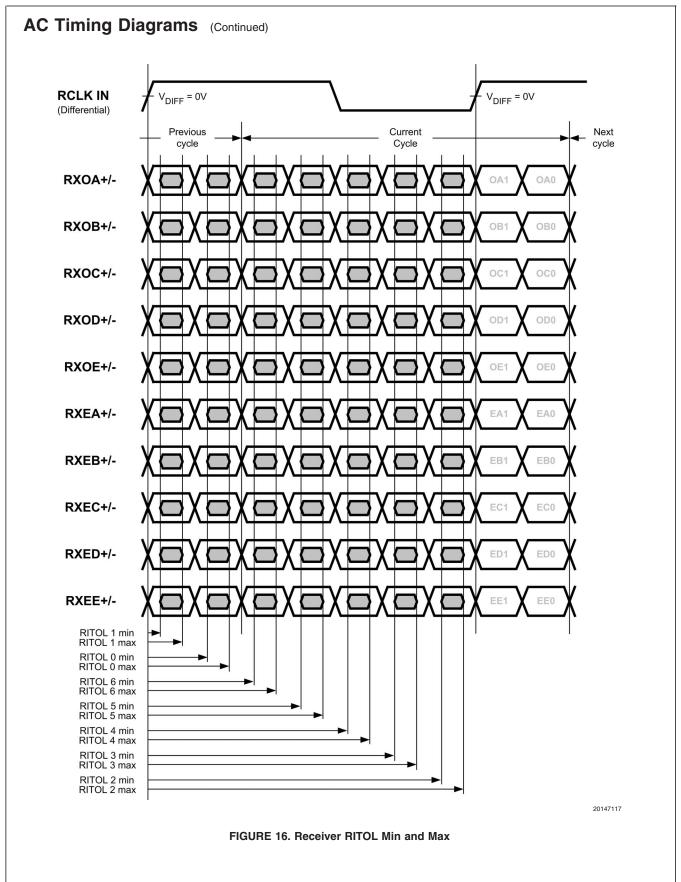

| RITOL        | Receiver Skew Margin                                                                              | V <sub>CM</sub> = 1.25V, |      |        | 0.25   | UI    |

|              | ( <i>Figures 10, 16</i> ) (Note 6)                                                                | $V_{ID} = 350 \text{mV}$ |      |        | -      | -     |

Note 4: Specification is guaranteed by characterization.

Note 5: A Clock Unit Symbol (T) is defined as 1/ (Line rate of RCLK). E.g. For Line rate of RCLK at 85MHz, 1 T = 11.76ns

Note 6: A Unit Interval (UI) is defined as 1/7th of an ideal clock period (RCLK/7). E.g. For an 11.76ns clock period (85MHz), 1 UI = 1.68ns

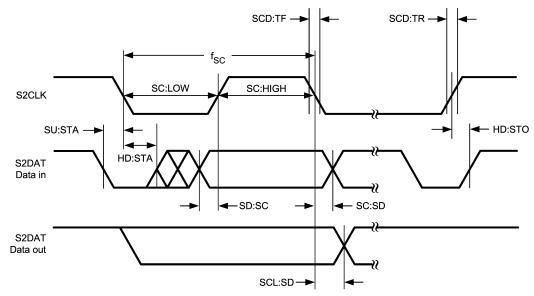

### **Two-Wire Serial Communication Interface**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                  | Conditions                           | Min | Тур | Max | Units |

|-----------------|----------------------------|--------------------------------------|-----|-----|-----|-------|

| f <sub>SC</sub> | S2CLK Clock Frequency      |                                      |     |     | 400 | kHz   |

| SC:LOW          | Clock Low Period           | $R_P = 4.7 K\Omega, C_L = 50 pF$     | 1.5 |     |     | us    |

| SC:HIGH         | Clock High Period          | $R_P = 4.7 K\Omega, C_L = 50 pF$     | 0.6 |     |     | us    |

| SCD:TR          | S2CLK and S2DAT Rise Time  | $R_P = 4.7 K\Omega, C_L = 50 pF$     |     |     | 0.3 | us    |

| SCD:TF          | S2CLK and S2DAT Fall Time  | $R_P = 4.7 K\Omega, C_L = 50 pF$     |     |     | 0.3 | us    |

| SU:STA          | Start Condition Setup Time | $R_P = 4.7 K\Omega, C_L = 50 pF$     | 0.6 |     |     | us    |

| HD:STA          | Start Condition Hold Time  | $R_{P} = 4.7 K\Omega, C_{L} = 50 pF$ | 0.6 |     |     | us    |

| HD:STO          | Stop Condition Hold Time   | $R_{P} = 4.7 K\Omega, C_{L} = 50 pF$ | 0.6 |     |     | us    |

| SC:SD           | Clock Falling Edge to Data | $R_{P} = 4.7 K\Omega, C_{L} = 50 pF$ | 0   |     |     | us    |

| SD:SC           | Data to Clock Rising Edge  | $R_{P} = 4.7 K\Omega, C_{L} = 50 pF$ | 0.1 |     |     | us    |

| SCL:SD          | S2CLK Low to S2DAT Data    | $R_{P} = 4.7 K\Omega, C_{L} = 50 pF$ | 0.1 |     | 0.9 | us    |

|                 | Valid                      |                                      |     |     |     |       |

| BUF             | Bus Free Time              | $R_P = 4.7 K\Omega, C_L = 50 pF$     | 13  |     |     | us    |

### **AC Timing Diagrams**

20147122

### AC Timing Diagrams (Continued)

FIGURE 6. Receiver Phase Lock Loop Wake-up Time

Note 7: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/LVTTL I/O.

Note 8: The incremental test pattern tests device power consumption for a "typical" LCD display pattern.

Note 9: *Figures 2, 3* show a falling edge data strobe (RCLK OUT).

Note 10: *Figure 8* show a rising edge data strobe (RCLK OUT).

FIGURE 8. Receiver Propagation Delay

FIGURE 14. Receiver RSRC and RHRC Output Setup/Hold Time Adjustment — PTO Enabled

#### **Pin Diagram** DS90C3202 Receiver RXOC2 **RXOA6 RXOA5** RXOA4 **RXOA0** VDDR2 **RXOB6** RX0B5 RXOB0 **RXOC6** RXOC5 RXOC4 **RXOC3** RXOCO **RXOD6 RXOD3** RXOD2 RXOD1 VDD4 **RXOA3 RXOA2** RXOB4 **RXOB3 RXOB2** RXOB1 RXOC1 RXOD5 RXOD4 RXOA1 VSSR2 VDD5 VSS5 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 96 RESRVD 97 64 VSS4 MODE1 -98 63 - RXOD0 VSSL 99 62 - RXOE6 VDDL -100 61 RXOE5 RXOA-101 60 - RXOE4 RXOA+ -102 59 - RXOE3 103 58 - RXOE2 RXOB- -RXOB+ -104 57 - RXOE1 RXOC-105 56 - RXOE0 RXOC+ -106 - VDD3 55 107 54 - VSS3 RXOD- -108 - RXEA6 RXOD+ -53 - RXEA5 RXOE-109 52 RXOE+ -110 51 - RXEA4 VSSL -111 50 • RXEA3 VSSL -112 DS90C3202 • RXEA2 49 VDDL -113 48 - RXEA1 VDDL -114 47 - RXEA0 RCLKIN- 115 - VDD2 46 RCLKIN+ - 116 45 - VSS2 RXEA- - 117 44 - RCLKOUT RXEA+ - 118 43 - VDDR1 RXEB- - 119 42 - VSSR1 RXEB+ -120 41 - RXEB6 RXEC- -121 40 - RXEB5 RXEC+ -122 39 - RXEB4 RXED-123 38 - RXEB3 - RXEB2 RXED+ -124 37 125 36 - RXEB1 RXEE-RXEE+ -126 35 - RXEB0 MODE0 - 127 34 - RXEC6 RFB — 128 33 - VDD1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 S2DAT -S2CLK -VDDP1 -VSSP1 -VSSP0 -RXEE0 - RXEE1 - RXEE2 - RXEE2 - RXEE2 - RXEE3 - RXEE3 - RXEE5 - RXEE6 - RXEE7 - RXE77 - RX777 RXED0 H RXED1 H RXED2 H RXED2 H RXED2 H RXED5 H RXED7 H RXE07 VDDP0 -PWDNB -Т Т Т Τ Т Т Т - USSV RXEC1 -RXEC2 -RXEC3 -RXEC4 -RXEC5 -VSS1 20147118

| DS900   | 3202 Pin Des | scription | S                    |                                                                         |

|---------|--------------|-----------|----------------------|-------------------------------------------------------------------------|

| Pin No. | Pin Name     | I/O       | Pin Type             | Description                                                             |

| 1       | S2DAT        | I/OP      | Digital              | Two-wire Serial Interface – Data                                        |

| 2       | S2CLK        | I/P       | Digital              | Two-wire Serial Interface – Clock                                       |

| 3       | VDDP1        | VDD       | PLL                  | Power supply for PLL circuitry                                          |

| 4       | VSSP1        | GND       | PLL                  | Ground pin for PLL circuitry                                            |

| 5       | VSSP0        | GND       | PLL                  | Ground pin for PLL circuitry                                            |

| 6       | VDDP0        | VDD       | PLL                  | Power supply for PLL circuitry                                          |

| 7       | PWDNB        | I/P       | LVTTL I/P (pulldown) | Powerdown Bar (Active LOW)<br>0 = DEVICE DISABLED<br>1 = DEVICE ENABLED |

| 8       | RXEE0        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 9       | RXEE1        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 10      | RXEE2        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 11      | RXEE3        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 12      | RXEE4        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 13      | RXEE5        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 14      | RXEE6        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 15      | VSS0         | GND       | LVTTL O/P PWR        | Ground pin for LVTTL outputs and digital circuitry                      |

| 16      | VDD0         | VDD       | LVTTL O/P PWR        | Power supply pin for LVTTL outputs and digital circuitry                |

| 17      | RXED0        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 18      | RXED1        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 19      | RXED2        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 20      | RXED3        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 21      | RXED4        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 22      | RXED5        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 23      | RXED6        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 24      | VSSR0        | GND       | RX LOGIC             | Ground pin for logic                                                    |

| 25      | VDDR0        | VDD       | RX LOGIC             | Power supply for logic                                                  |

| 26      | RXEC0        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 27      | RXEC1        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 28      | RXEC2        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 29      | RXEC3        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 30      | RXEC4        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 31      | RXEC5        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 32      | VSS1         | GND       | LVTTL O/P PWR        | Ground pin for LVTTL outputs and digital circuitry                      |

| 33      | VDD1         | VDD       | LVTTL O/P PWR        | Power supply pin for LVTTL outputs and digital circuitry                |

| 34      | RXEC6        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 35      | RXEB0        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 36      | RXEB1        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

| 37      | RXEB2        | O/P       | LVTTL O/P            | LVTTL level data output                                                 |

|         | 1            |           |                      | · · · · · · · · · · · · · · · · · · ·                                   |

LVTTL level data output

LVTTL level data output

LVTTL level data output

LVTTL level data output

Ground pin for logic

Power supply for logic

LVTTL level clock output

Ground pin for LVTTL outputs and digital circuitry

38

39

40

41

42

43

44

45

RXEB3

RXEB4

RXEB5

RXEB6

VSSR1

VDDR1

RCLKOUT

VSS2

O/P

O/P

O/P

O/P

GND

VDD

O/P

GND

LVTTL O/P

LVTTL O/P

LVTTL O/P

LVTTL O/P

**RX LOGIC**

RX LOGIC

LVTTL O/P

LVTTL O/P PWR

#### DS90C3202 Pin Descriptions (Continued) **Pin Name** I/O Pin Type Pin No. Description VDD2 VDD LVTTL O/P PWR 46 Power supply pin for LVTTL outputs and digital circuitry 47 RXEA0 O/P LVTTL O/P LVTTL level data output 48 RXEA1 O/P LVTTL O/P LVTTL level data output RXEA2 O/P LVTTL O/P LVTTL level data output 49 50 RXEA3 O/P LVTTL O/P LVTTL level data output 51 RXEA4 O/P LVTTL O/P LVTTL level data output 52 RXEA5 O/P LVTTL O/P LVTTL level data output O/P 53 RXEA6 LVTTL O/P LVTTL level data output LVTTL O/P PWR 54 VSS3 GND Ground pin for LVTTL outputs and digital circuitry 55 VDD3 VDD LVTTL O/P PWR Power supply pin for LVTTL outputs and digital circuitry O/P LVTTL level data output 56 RXOE0 LVTTL O/P 57 RXOE1 O/P LVTTL O/P LVTTL level data output 58 RXOE2 O/P LVTTL O/P LVTTL level data output O/P 59 RXOE3 LVTTL O/P LVTTL level data output 60 O/P LVTTL O/P LVTTL level data output RXOE4 RXOE5 O/P 61 LVTTL O/P LVTTL level data output O/P 62 RXOE6 LVTTL O/P LVTTL level data output O/P LVTTL level data output 63 RXOD0 LVTTL O/P VSS4 GND LVTTL O/P PWR Ground pin for LVTTL outputs and digital circuitry 64 65 VDD4 VDD LVTTL O/P PWR Power supply pin for LVTTL outputs and digital circuitry RXOD1 O/P 66 LVTTL O/P LVTTL level data output 67 RXOD2 O/P LVTTL O/P LVTTL level data output RXOD3 O/P 68 LVTTL O/P LVTTL level data output RXOD4 O/P LVTTL level data output 69 LVTTL O/P RXOD5 O/P LVTTL level data output 70 LVTTL O/P RXOD6 O/P LVTTL O/P LVTTL level data output 71 72 RXOC0 O/P LVTTL O/P LVTTL level data output RXOC1 O/P 73 LVTTL O/P LVTTL level data output 74 O/P RXOC2 LVTTL O/P LVTTL level data output RXOC3 O/P LVTTL O/P LVTTL level data output 75 RXOC4 O/P LVTTL level data output 76 LVTTL O/P 77 RXOC5 O/P LVTTL O/P LVTTL level data output 78 RXOC6 O/P LVTTL O/P LVTTL level data output 79 RXOB0 O/P LVTTL O/P LVTTL level data output 80 RXOB1 O/P LVTTL O/P LVTTL level data output RXOB2 O/P LVTTL O/P LVTTL level data output 81 82 RXOB3 O/P LVTTL O/P LVTTL level data output 83 RXOB4 O/P LVTTL O/P LVTTL level data output 84 RXOB5 O/P LVTTL O/P LVTTL level data output 85 RXOB6 O/P LVTTL O/P LVTTL level data output 86 VDDR2 VDD **RX LOGIC** Power supply for logic 87 VSSR2 GND **RX LOGIC** Ground pin for logic 88 RXOA0 O/P LVTTL O/P LVTTL level data output RXOA1 O/P LVTTL O/P LVTTL level data output 89 90 RXOA2 O/P LVTTL O/P LVTTL level data output O/P LVTTL O/P 91 RXOA3 LVTTL level data output

| Pin No. | Pin Name | I/O | Pin Type             | Description                                                                                           |

|---------|----------|-----|----------------------|-------------------------------------------------------------------------------------------------------|

| 92      | RXOA4    | O/P | LVTTL O/P            | LVTTL level data output                                                                               |

| 93      | RXOA5    | O/P | LVTTL O/P            | LVTTL level data output                                                                               |

| 94      | RXOA6    | O/P | LVTTL O/P            | LVTTL level data output                                                                               |

| 95      | VDD5     | VDD | LVTTL O/P PWR        | Power supply pin for LVTTL outputs and digital circuitry                                              |

| 96      | VSS5     | GND | LVTTL O/P PWR        | Ground pin for LVTTL outputs and digital circui                                                       |

| 97      | RESRVD   | I/P | LVTTL I/P (pulldown) | Tie to VSS for correct functionality                                                                  |

| 98      | MODE1    | I/P | Digital (pulldown)   | "ODD" Bank Enable<br>0 = LVTTL ODD OUTPUTS DISABLED<br>1 = LVTTL ODD OUTPUTS ENABLED                  |

| 99      | VSSL     | GND | LVDS PWR             | Power supply pin for LVDS                                                                             |

| 100     | VDDL     | VDD | LVDS PWR             | Ground pin for LVDS                                                                                   |

| 101     | RXOA-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 102     | RXOA+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 103     | RXOB-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 104     | RXOB+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 105     | RXOC-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 106     | RXOC+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 107     | RXOD-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 108     | RXOD+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 109     | RXOE-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 110     | RXOE+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 111     | VSSL     | GND | LVDS PWR             | Ground pin for LVDS                                                                                   |

| 112     | VSSL     | GND | LVDS PWR             | Ground pin for LVDS                                                                                   |

| 113     | VDDL     | VDD | LVDS PWR             | Power supply pin for LVDS                                                                             |

| 114     | VDDL     | VDD | LVDS PWR             | Power supply pin for LVDS                                                                             |

| 115     | RCLKIN-  | I/P | LVDS I/P             | Negative LVDS differential clock input                                                                |

| 116     | RCLKIN+  | I/P | LVDS I/P             | Positive LVDS differential clock input                                                                |

| 117     | RXEA-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 118     | RXEA+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 119     | RXEB-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 120     | RXEB+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 121     | RXEC-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 122     | RXEC+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 123     | RXED-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 124     | RXED+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 125     | RXEE-    | I/P | LVDS I/P             | Negative LVDS differential data input                                                                 |

| 126     | RXEE+    | I/P | LVDS I/P             | Positive LVDS differential data input                                                                 |

| 127     | MODE0    | I/P | Digital (pulldown)   | "EVEN" Bank Enable<br>0 = LVTTL EVEN OUTPUTS DISABLED<br>1 = LVTTL EVEN OUTPUTS ENABLED               |

| 128     | RFB      | I/P | Digital (pulldown)   | Rising Falling Bar ( <i>Figure 9</i> )<br>0 = FALLING EDGE DATA STROBE<br>1 = RISING EDGE DATA STROBE |

### Two-Wire Serial Communication Interface Description

The DS90C3202 operates as a slave on the Serial Bus, so the S2CLK line is an input (no clock is generated by the DS90C3202) and the S2DAT line is bi-directional. DS90C3202 has a fixed 7bit slave address. The address is not user configurable in anyway.

A zero in front of the register address is required. For example, to access register 0x0Fh, "0F" is the correct way of accessing the register.

### COMMUNICATING WITH THE DS90C3202 CONTROL REGISTERS

There are 32 data registers (one byte each) in the DS90C3202, and can be accessed through 32 addresses. All registers are predefined as read only or read and write. The DS90C3202 slave state machine does not require an internal clock and it supports only byte read and write. Page mode is not supported. The 7bit binary address is 0111110 All seven bits are hardwired internally.

Reading the DS90C3202 can take place either of three ways:

- 1. If the location latched in the data register addresses is correct, then the read can simply consist of a slave address byte, followed by retrieving the data byte.

- 2. If the data register address needs to be set, then a slave address byte, data register address will be sent first, then the master will repeat start, send the slave address byte and data byte to accomplish a read.

- When performing continuous read operations, another write (or read) instruction in between reads needs to be completed in order for the two-wire serial interface module to read repeatedly.

The data byte has the most significant bit first. At the end of a read, the DS90C3202 can accept either Acknowledge or No Acknowledge from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte).

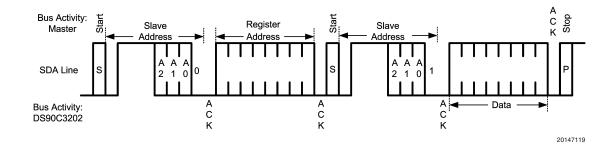

The master must generate a Start by sending the 7-bit slave address plus a 0 first, and wait for acknowledge from DS90C3202. When DS90C3202 acknowledges (the 1st ACK) that the master is calling, the master then sends the data register address byte and waits for acknowledge from the slave. When the slave acknowledges (the 2nd ACK), the master repeats the "Start" by sending the 7-bit slave address plus a 1 (indicating that READ operation is in progress) and waits for acknowledge from DS90C3202. After the slave responds (the 3rd ACK), the slave sends the data to the bus and waits for acknowledge from the master. When the master acknowledges (the 4th ACK), it generates a "Stop". This completes the "READ".

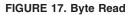

A **Write** to the DS90C3202 will always include the slave address, data register address byte, and a data byte.

| Address  | R/W   | RESET | Bit # | Description                                             | Default Valu |

|----------|-------|-------|-------|---------------------------------------------------------|--------------|

| 0d/0h    | R     | PWDN  | [7:0] | Vender ID low byte[7:0] = 05h                           | 0000_0101    |

| 1d/1h    | R     | PWDN  | [7:0] | Vender ID high byte[15:8] =13h                          | 0001_0011    |

| 2d/2h    | R     | PWDN  | [7:0] | Device ID low byte[7:0] = 28h                           | 0010_1000    |

| 3d/3h    | R     | PWDN  | [7:0] | Device ID high byte 15:8] = 67h                         | 0110_0111    |

| 4d/4h    | R     | PWDN  | [7:0] | Device revision [7:0] = 00h to begin with               | 0000_0000    |

| 5d/5h    | R     | PWDN  | [7:0] | Low frequency limit, 8Mhz = 8h                          | 0000_1000    |

| 6d/6h    | R     | PWDN  | [7:0] | High frequency limit 135Mhz = 87h = 0000_0000_1000_0111 | 1000_0111    |

| 7d/7h    | R     | PWDN  | [7:0] | Reserved                                                | 0000_0000    |

| 8d/8h    | R     | PWDN  | [7:0] | Reserved                                                | 0000_0000    |

| 9d/9h    | R     | PWDN  | [7:0] | Reserved                                                | 0000_0000    |

| 10d/ah   | R     | PWDN  | [7:0] | Reserved                                                | 0000_0000    |

| 11d/bh   | R     | PWDN  | [7:0] | Reserved                                                | 0000_0000    |

| 20d/14h  | R/W   | None  | [7:0] | Reserved                                                | 0000_0000    |

| 21d/15h  | R/W   | None  | [7:0] | Reserved                                                | 0000_0000    |

| 22d/16h  | R/W   |       |       | Reserved                                                | 0000_0000    |

| 220/1011 | Π/ ٧٧ | None  | [7:3] | LVDS input skew control for CLK channel,                | 0000_0000    |

|          |       |       | [2:0] | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Tsetup improvement    |              |

| 23d/17h  | R/W   | None  | [7]   | Reserved                                                | 0000_0000    |

| 200/1711 | 11/ 1 | None  | [6:4] | LVDS input skew control for RXO channel B,              | 0000_0000    |

|          |       |       | [0.4] | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Thold improvements    |              |

|          |       |       | [3]   | Reserved                                                |              |

|          |       |       | [2:0] | LVDS input skew control for RXO channel C,              |              |

|          |       |       | [2.0] | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Thold improvements    |              |

| 24d/18h  | R/W   | None  | [7]   | Reserved                                                | 0000_0000    |

|          |       |       | [6:4] | LVDS input skew control for RXO channel D,              |              |

|          |       |       | [0.1] | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Thold improvements    |              |

|          |       |       | [3]   | Reserved                                                |              |

|          |       |       | [2:0] | LVDS input skew control for RXO channel E,              |              |

|          |       |       |       | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Thold improvements    |              |

| 25d/19h  | R/W   | None  | [7]   | Reserved                                                | 0000_0000    |

|          |       |       | [6:4] | LVDS input skew control for RXO channel A,              |              |

|          |       |       |       | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Thold improvements    |              |

|          |       |       | [3]   | Reserved                                                |              |

|          |       |       | [2:0] | LVDS input skew control for RXE channel A,              |              |

|          |       |       |       | 000 (default) applies to no delay added, ONE buffer     |              |

|          |       |       |       | delay per step adjustment towards Thold improvements    |              |

### DS90C3202 Two-Wire Serial Interface Register Table (Continued)

| Address  | R/W          | RESET | Bit # | Description                                                                                                     | Default Valu |

|----------|--------------|-------|-------|-----------------------------------------------------------------------------------------------------------------|--------------|

| 26d/1ah  | R/W          | None  | [7]   | Reserved                                                                                                        | 0000_0000    |

|          |              |       | [6:4] | LVDS input skew control for RXE channel B,                                                                      |              |

|          |              |       |       | 000 (default) applies to no delay added, ONE buffer                                                             |              |

|          |              |       |       | delay per step adjustment towards Thold improvements                                                            |              |

|          |              |       | [3]   | Reserved                                                                                                        |              |

|          |              | -     | [2:0] | LVDS input skew control for RXE channel C,                                                                      |              |

|          |              |       |       | 000 (default) applies to no delay added, ONE buffer                                                             |              |

|          |              |       |       | delay per step adjustment towards Thold improvements                                                            |              |

| 27d/1bh  | R/W          | None  | [7]   | Reserved                                                                                                        | 0000_0000    |

|          |              | -     | [6:4] | LVDS input skew control for RXE channel D,                                                                      |              |

|          |              |       |       | 000 (default) applies to no delay added, ONE buffer                                                             |              |

|          |              |       |       | delay per step adjustment                                                                                       |              |

|          |              | -     | [3]   | Reserved                                                                                                        |              |

|          |              |       | [2:0] | LVDS input skew control for RXE channel E,                                                                      |              |

|          |              |       | [=:0] | 000 (default) applies to no delay added, ONE buffer                                                             |              |

|          |              |       |       | delay per step adjustment towards Thold improvements                                                            |              |

| 28d/1ch  | R/W          | None  | [7:3] | Reserved                                                                                                        | 0000_0000    |

| 200/1011 | 1 1/ • •     |       | [2]   | LVTTL output transition time control for CLK                                                                    | 0000_0000    |

|          |              |       | [2]   | 0: $Tr/Tf = 1.0ns$ (default)                                                                                    |              |

|          |              |       |       | 1: $Tr/Tf = 1.5ns$                                                                                              |              |

|          |              |       | [1]   | LVTTL output transition time control for RXE                                                                    |              |

|          |              |       | [']   | 0: $Tr/Tf = 1.5ns$ (default)                                                                                    |              |

|          |              |       |       | 1: $Tr/Tf = 2.5ns$                                                                                              |              |

|          |              |       | [0]   |                                                                                                                 |              |

|          |              |       | [0]   | LVTTL output transition time control for RXO                                                                    |              |

|          |              |       |       | 0: $Tr/Tf = 1.5ns$ (default)<br>1: $Tr/Tf = 2.5ns$                                                              |              |

| 29d/1dh  | R/W          | None  | [7:0] |                                                                                                                 | 0000 0000    |

| 290/1011 | <b>m/ vv</b> | None  | [7:3] | Reserved                                                                                                        | 0000_0000    |

|          |              |       | [2:1] | LVTTL output setup and hold time control                                                                        |              |

|          |              |       |       | 00: balanced setup and hold time (default)                                                                      |              |

|          |              |       |       | 01: setup time is increased from default position by 1UI<br>& hold time is reduced from default position by 1UI |              |

|          |              |       |       | 10: setup time is decreased from default position by 1UI                                                        |              |

|          |              |       |       | & hold time is reduced from default position by 1UI                                                             |              |

|          |              |       |       | 11: setup time is increased from default position by 2UI                                                        |              |

|          |              |       |       | & hold time is increased from default position by 201                                                           |              |

|          |              |       | [0]   | LVTTL output PTO control                                                                                        |              |

|          |              |       | [U]   | 1: PTO disabled, all outputs setup time are only                                                                |              |

|          |              |       |       | controlled by contents of [2:1]                                                                                 |              |

|          |              |       |       | 0: PTO enabled (default)                                                                                        |              |

|          |              |       |       | Group1: CLK to latch Data is re-assigned earlier by                                                             |              |

|          |              |       |       | 0.5UI respect to the normal centered position if only                                                           |              |

|          |              |       |       | PTO option enabled; but PTO option and (Tsetup or                                                               |              |

|          |              |       |       | Thold) adjustment can co-exist                                                                                  |              |

|          |              |       |       | Group2: CLK to latch Data stays as the normal                                                                   |              |

|          |              |       |       | centered position if only PTO option enabled; but PTO                                                           |              |

|          |              |       |       | option and (Tsetup or Thold) adjustment can co-exist                                                            |              |

| Address     | R/W | RESET | Bit # | Description                                               | Default Value |

|-------------|-----|-------|-------|-----------------------------------------------------------|---------------|

| 30d/1eh     | R/W | None  | [7:5] | Reserved                                                  | 0000_0000     |

|             |     |       | [4]   | I/O disable control for RXE channel A,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [3]   | I/O disable control for RXE channel B,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [2]   | I/O disable control for RXE channel C,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [1]   | I/O disable control for RXE channel D,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [0]   | I/O disable control for RXE channel E,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

| 31d/1fh R/W | R/W | None  | [7:6] | 11; LVTTL Outputs available as long as "NO CLK" is at     | 0000_0000     |

|             |     |       |       | HIGH regardless PLL lock or not                           |               |

|             |     |       |       | 10; LVTTL Outputs available after 1K of CLK cycles        |               |

|             |     |       |       | detected & PLL generated strobes are within 0.5UI         |               |

|             |     |       |       | respect to REFCLK                                         |               |

|             |     |       |       | 01; LVTLL Outputs available after 2K of CLK cycles        |               |

|             |     |       |       | detected                                                  |               |

|             |     |       |       | 00: default ; LVTTL Outputs available after 1K of CLK     |               |

|             |     |       |       | cycles detected                                           |               |

|             |     |       | [5]   | 0: default; to select the size of wait counter between 1K |               |

|             |     |       |       | or 2K, default is 1K                                      |               |

|             |     |       | [4]   | I/O disable control for RXO channel A,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [3]   | I/O disable control for RXO channel B,                    |               |

|             |     |       |       | 1 disable, 0: enable (default)                            |               |

|             |     |       | [2]   | I/O disable control for RXO channel C,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [1]   | I/O disable control for RXO channel D,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

|             |     |       | [0]   | I/O disable control for RXO channel E,                    |               |

|             |     |       |       | 1: disable, 0: enable (default)                           |               |

Note 11: Registers with RESET designated with "None" requires device to be power cycled to reset register values to their default state.

www.national.com

Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

Tel: 81-3-5639-7560