Data Sheet

September 2003

专业PCB打样工厂

24小时加急出**作**SL6580

# Integrated Power Stage

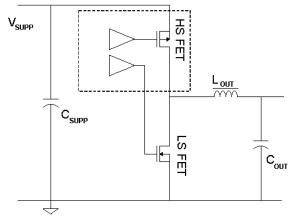

Processors that operate above 1GHz require fast, intelligent power systems. The ISL6580 Integrated Power Stage is a High Side FET/driver combination that provides high current capability per converter phase at high switching frequency. The chip incorporates intelligence to provide fast transient response and digital communication to the ISL6590 Digital Controller. The ISL6580 integrates key power stage components for fast power delivery, effective thermal design and increased noise immunity. It incorporates an integrated P-channel high side MOSFET, high side MOSFET driver and a driver for external synchronous rectifier, low side MOSFETs. The ISL6580 also features a window comparator for fast transient response as well as on-board voltage and current A/D converters for intelligent digital communication and control by the ISL6590 Controller.

Furthermore, through the communication bus, configuration and fault monitoring via the ISL6590 are available.

For more information, see the ISL6590 datasheet.

# **Ordering Information**

| PART NUMBER     | TEMP. RANGE<br>( <sup>o</sup> C) | PACKAGE       | PKG.<br>DWG. # |  |  |

|-----------------|----------------------------------|---------------|----------------|--|--|

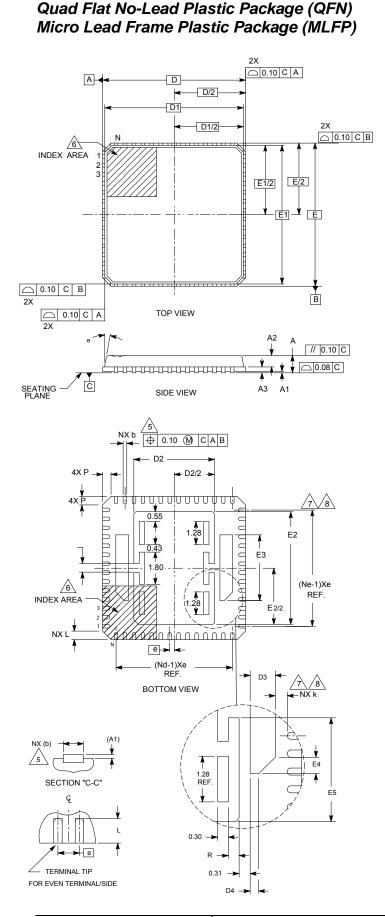

| ISL6580CR       | 0 to 70                          | 56 Ld 8x8 QFN | L56.8x8C       |  |  |

| ISL6580CR-T     | 56 Ld QFN Tape                   | & Reel        |                |  |  |

| ISL6580/90EVAL1 | Evaluation Board                 |               |                |  |  |

| ISL6580/90EVAL2 | Evaluation Board                 |               |                |  |  |

| ISL6580/90EVAL3 | Evaluation Board                 |               | 12/101         |  |  |

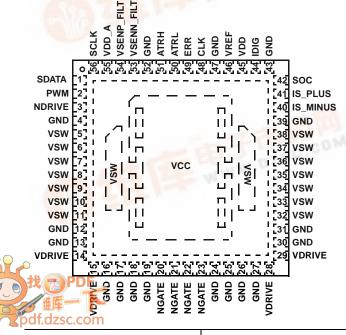

Pinout

### Features

- Optimized for Intel VR10 applications

- V<sub>IN</sub> = 12V

- Phase switching frequencies of 250kHz to 1MHz

- Phase current capability up to 25A

- High Side P-channel MOSFET

- Low Side MOSFET drivers

- Accurate, lossless, Current Sense

- Programmable MOSFET non-overlap timing (through the ISL6590 Digital Controller)

- Active Transient Response (ATR) minimizes voltage droop/overshoot during large load current transients.

- Serial control interface for system monitoring and configuration (with ISL6590 Controller)

- Input Under Voltage Protection

- Output Under/Over Voltage Protection

- Peak Current Limit

- Thermal Shutdown

- ATR Limits

- Provides an optimal power solution when combined with the ISL6590 Digital Controller

- Output voltage regulation range of 0.3VDC to 1.85VDC

- VRM-9 and VRM-10 VID Codes

- Digital interface for high noise immunity and point-of-load placement

- On board analog-to-digital converters

- 10 Msample/sec voltage A/D

- 1 Msample/sec current A/D

# Related Literature

- ISL6590 Datasheet

- Technical Brief TB363 "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

- Technical Brief TB379 "Thermal Characterization of Packaged Semiconductor Devices"

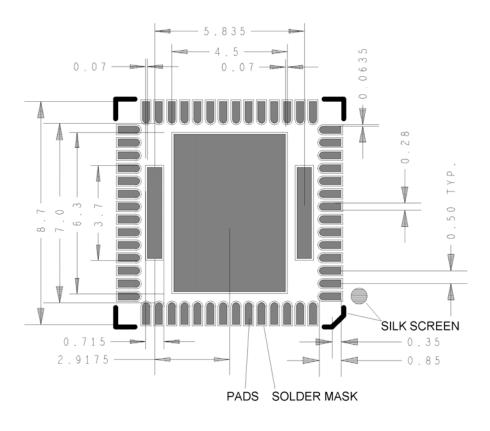

- Technical Brief TB389 "PCB Land Pattern Design and Surface Mount Guidelines for QFN (MLFP) Packages"

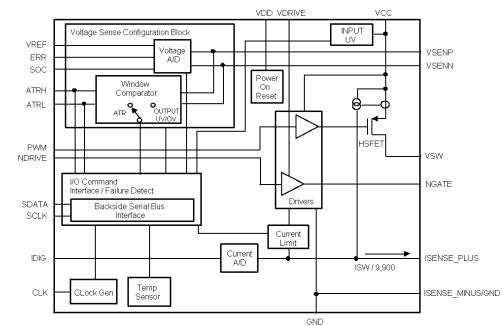

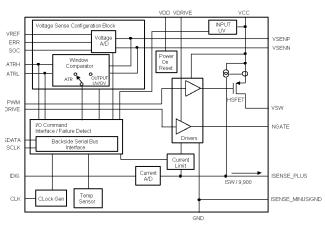

# ISL6580

# Block Diagram

## ISL6580

# Functional Pin Description

| PIN # | NAME   | I/O | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SDATA  | I/O | 3.3V CMOS | Digital I/O; serial data line that carries configuration and monitoring information to and from the Intersil ISL6590 digital controller via the shared controller interface bus. Information transmitted via SDATA includes: PVID information, input UVLO fault, output under/over voltage fault, thermal shutdown fault, peak current limit setpoint, ATRH and ATRL trip levels |

| 2     | PWM    | Ι   | 3.3V CMOS | Digital input; pulse width modulation input to the high side driver.                                                                                                                                                                                                                                                                                                             |

| 3     | NDRIVE | Ι   | 3.3V CMOS | Digital input; multifunction pin used for assigning device ID at startup. During operation, provides pulse width modulation for the low side driver                                                                                                                                                                                                                              |

| 4     | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 5     | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 6     | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 7     | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 8     | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 9     | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 10    | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 11    | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

| 12    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 13    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 14    | VDRIVE | I   | VDRIVE    | Power input typically connected to a 5V supply. Provides the supply voltage for driving the gate of the Low side NFET                                                                                                                                                                                                                                                            |

| 15    | VDRIVE | Ι   | VDRIVE    | Power input typically connected to a 5V supply. Provides the supply voltage for driving the gate of the Low side NFET                                                                                                                                                                                                                                                            |

| 16    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 17    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 18    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 19    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 20    | NGATE  | 0   | HV ANALOG | High voltage analog output used to drive the low side NFET. When NDRIVE is high, NGATE is switched to VDRIVE. When NDRIVE is low, NGATE is switched to ground.                                                                                                                                                                                                                   |

| 21    | NGATE  | 0   | HV ANALOG | High voltage analog output used to drive the low side NFET. When NDRIVE is high, NGATE is switched to VDRIVE. When NDRIVE is low, NGATE is switched to ground.                                                                                                                                                                                                                   |

| 22    | NGATE  | 0   | HV ANALOG | High voltage analog output used to drive the low side NFET. When NDRIVE is high, NGATE is switched to VDRIVE. When NDRIVE is low, NGATE is switched to ground.                                                                                                                                                                                                                   |

| 23    | NGATE  | 0   | HV ANALOG | High voltage analog output used to drive the low side NFET. When NDRIVE is high, NGATE is switched to VDRIVE. When NDRIVE is low, NGATE is switched to ground.                                                                                                                                                                                                                   |

| 24    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 25    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 26    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 27    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 28    | VDRIVE | Ι   | VDRIVE    | Power input typically connected to a 5V supply. Provides the supply voltage for driving the gate of the low side NFET                                                                                                                                                                                                                                                            |

| 29    | VDRIVE | Ι   | VDRIVE    | Power input typically connected to a 5V supply. Provides the supply voltage for driving the gate of the low side NFET                                                                                                                                                                                                                                                            |

| 30    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 31    | GND    | Ι   | GND       | IC ground                                                                                                                                                                                                                                                                                                                                                                        |

| 32    | VSW    | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                                                                                                                                                              |

# Functional Pin Description (Continued)

| <i>i</i> unouc |                         |     | scription | (continued)                                                                                                                                                                                                                                |

|----------------|-------------------------|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN #          | NAME                    | I/O | TYPE      | DESCRIPTION                                                                                                                                                                                                                                |

| 33             | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                        |

| 34             | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                        |

| 35             | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                        |

| 36             | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                        |

| 37             | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                        |

| 38             | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high and no fault condition, VCC is switched to VSW                                                                                                                                        |

| 39             | GND                     | I   | GND       | IC ground                                                                                                                                                                                                                                  |

| 40             | ISENSE<br>MINUS/<br>GND | Ι   | GND       | Ground pin for current sense resistor                                                                                                                                                                                                      |

| 41             | ISENSE<br>PLUS          | I/O | ANALOG    | Low voltage analog output; current representing 1/9900 of the high side PFET current                                                                                                                                                       |

| 42             | SOC                     | 0   | 3.3V CMOS | Digital outupt; start of conversion signal (SOC). This signal frames the error word generated by the voltage A/D when configured in regulation mode.                                                                                       |

| 43             | GND                     | Ι   | GND       | IC ground                                                                                                                                                                                                                                  |

| 44             | IDIG                    | 0   | 3.3V CMOS | Digital output; 7 bit serial word transmitted typically at 66.67MHz. The first bit is a start bit (start=1). This signal represents the sampled peak current in the high side PFET, MSB first                                              |

| 45             | VDD                     | Ι   | VDD       | Power supply for the logic typically set at 3.3V                                                                                                                                                                                           |

| 46             | VREF                    | I   | VREF      | Low voltage analog input; 2.5V reference signal used by the A/D converter and the thermal shutdown circuits                                                                                                                                |

| 47             | GND                     | I   | GND       | IC ground                                                                                                                                                                                                                                  |

| 48             | CLK                     | Ι   | 3.3V CMOS | Digital input; typically a 133MHz clock supplied to the Intersil ISL6590                                                                                                                                                                   |

| 49             | ERR                     | 0   | 3.3V CMOS | Digital output; Voltage A/D output word indicating the error from the desired output voltage and VSENP-VSENN measured voltage (Output voltage-VID). The error signal is a 6 bit serial word (MSB first) transmitted typically at 66.67MHz. |

| 50             | ATRL                    | 0   | 3.3V CMOS | Digital output; Active Transient Response Low (ATRL). ATRL indicates the regulated output voltage has"spiked" above the programmed level.                                                                                                  |

| 51             | ATRH                    | 0   | 3.3V CMOS | Digital output; Active Transient Response High (ATRH). ATRH indicates the regulated output voltage has"drooped" below the programmed level.                                                                                                |

| 52             | GND                     | Ι   | GND       | IC ground                                                                                                                                                                                                                                  |

| 53             | VSENN                   | I   | LV ANALOG | Low voltage analog input; negative input for the remote sense used to differentially sense the regulated output voltage. The IC is configurable for thre modes of operation: Regulation mode, ATR mode, and output OV/UV mode              |

| 54             | VSENP                   | I   | LV ANALOG | Low voltage analog input; positive input for the remote sense used to differentially sense the regulated output voltage. The IC is configurable for thre modes of operation: Regulation mode, ATR mode, and output OV/UV mode              |

| 55             | VDD                     | Ι   | VDD       | Power supply for the logic typically set at 3.3V                                                                                                                                                                                           |

| 56             | SCLK                    | I   | 3.3V CMOS | Digital input; typically 16.67MHz clock supplied by the Intersil ISL6590 digital controller for the controller interface bus Paddle                                                                                                        |

| PADDLE         | VCC                     | Ι   | VCC       | Power supply input typically set at 12V. Provides gate drive and source connection for the integrated high side PFET                                                                                                                       |

| Side Bar<br>1  | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high, VCC is switched to VSW                                                                                                                                                               |

| Side Bar<br>2  | VSW                     | 0   | HV ANALOG | Drain of high side PFET. When the PWM signal is high, VCC is switched to VSW                                                                                                                                                               |

### **Absolute Maximum Ratings**

| V <sub>CC</sub> 0.3V to 18V                            |

|--------------------------------------------------------|

| V <sub>DD</sub>                                        |

| V <sub>REF</sub> (see Note 1)                          |

| V <sub>DRIVE</sub> (see Note 1)0.3V to V <sub>CC</sub> |

| V <sub>CC</sub> -V <sub>SW</sub> (PChannel VBRSS)20V   |

| ISW peak                                               |

| ICC average 3.5A                                       |

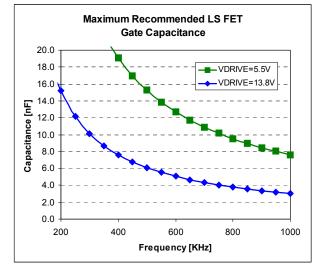

| MOSFET Gate Capacitance See Max Gate Drive section     |

| All Logic                                              |

| VSENN, VSENP                                           |

| ESD Rating                                             |

| Human Body Model (Per JEDEC JESD22-A114)1.5KV          |

## **Operating Conditions**

| Temperature Range              |

|--------------------------------|

| V <sub>CC</sub> (Typical)      |

| V <sub>DD</sub> (Typical)      |

| V <sub>DRIVE</sub> (Typical)5V |

| V <sub>REF</sub> (Typical)     |

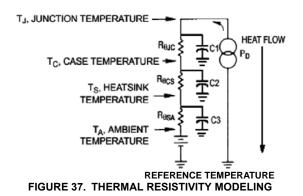

# **Thermal Information**

| Thermal Resistance        | θ <sub>JA(</sub> <sup>o</sup> C/W) | θ <sub>JB(</sub> <sup>o</sup> C/W) | θ <sub>JC(</sub> oC/W) |

|---------------------------|------------------------------------|------------------------------------|------------------------|

| Junction to bottom of ca  | ise N/A                            | N/A                                | 3                      |

| Junction to top of case . | N/A                                | N/A                                | 12.0                   |

| Junction to board (Note   | 2) N/A                             | 9                                  | N/A                    |

| Still air (Note 2)        | 26.0                               | N/A                                | N/A                    |

| 100LFM (Note 2)           | 23.5                               | N/A                                | N/A                    |

| 200LFM (Note 2)           | 22.3                               | N/A                                | N/A                    |

| 400LFM (Note 2)           | 21.2                               | N/A                                | N/A                    |

| Maximum Junction Tempe    | erature                            |                                    | 150 <sup>0</sup> C     |

| Maximum Storage Tempe     | rature Range                       |                                    | 5°C to 175°C           |

| Maximum Lead Temperate    | ure (Soldering 1                   | 0s)                                | 300 <sup>0</sup> C     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

1. See "Bias Supply Power On Sequence" section.

θ<sub>JA</sub> is measured with the component mounted on a "High Effective" Thermal Conductivity Board with "Direct Attach" Features. See Technical Brief TB379 "Thermal Characterization of Packaged Semiconductor Devices".

| Electrical Specifications | V <sub>DD</sub> = 3.3VDC, V <sub>CC</sub> = 12VDC, V <sub>DRIVE</sub> = 5VDC, V <sub>REF</sub> = 2.5V, SYSCLK = 133.33MHz, SCLK = 16.67MHz, |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                           | T <sub>A</sub> = 25°C Unless Otherwise Specified                                                                                            |

| PARAMETER                    | TEST CONDITIONS                                                                                                                        | MIN    | TYP | MAX | UNITS |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-------|

|                              | POWER STAGE                                                                                                                            |        | 1   |     | 1     |

| SWITCHING FREQUE             | ENCY                                                                                                                                   |        |     |     |       |

| Switching Frequency          | Switching Frequency Range                                                                                                              | 0.25   |     | 1   | MHz   |

|                              | POWER STAGE: NGATE                                                                                                                     |        |     |     |       |

| NGATE SIGNAL PAR             | AMETERS; V <sub>DRIVE</sub> = 5VDC                                                                                                     |        |     |     |       |

| NGATE Voltage                | Voltage Swing for Driving External NFET (I <sub>DRIVE</sub> = 2A)                                                                      |        | 5   |     | V     |

| NGATE Pullup<br>Resistance   | Pullup Resistance of ISL6580 for Biasing gate of External, Synchronous Rectifier, N Channel MOSFETs                                    |        | 1.3 |     | Ω     |

| NGATE Pulldown<br>Resistance | Pulldown Resistance of ISL6580 for Biasing gate of External, Synchronous Rectifier, N Channel MOSFETs                                  |        | 0.4 |     | Ω     |

| Gate Rise Time               | Gate Rise Time of External NFET, Transition from 0.5 to 4.5V; into 3nF                                                                 |        | 8   |     | ns    |

| Gate Fall Time               | Gate Fall Time of External NFET Transition from 4.5 to 0.5V; into 3nF                                                                  |        | 4   |     | ns    |

| Turn on Delay Time           | C <sub>LOAD</sub> = 3nF                                                                                                                |        | 25  |     | ns    |

|                              | POWER STAGE: INTERNAL P CHANNEL, HIGH SIDE SWITCH PARAM                                                                                | IETERS | I   |     | 1     |

| P Channel<br>RDS(on)         | Static Drain-to-Source ON resistance of Internal P Channel FET, ID =10 amps; Measured between V <sub>CC</sub> and V <sub>SW</sub> pins |        | 20  |     | mΩ    |

| P Channel V <sub>BRSS</sub>  | Switch breakdown voltage of internal P Channel FET. ID = 1.5 mA                                                                        |        | 20  |     | V     |

# $\label{eq:constraint} \begin{array}{l} \textbf{Electrical Specifications} \\ \textbf{V}_{DD} = 3.3 \text{VDC}, \ \textbf{V}_{CC} = 12 \text{VDC}, \ \textbf{V}_{DRIVE} = 5 \text{VDC}, \ \textbf{V}_{REF} = 2.5 \text{V}, \ \textbf{SYSCLK} = 133.33 \text{MHz}, \ \textbf{SCLK} = 16.67 \text{MHz}, \\ \textbf{T}_{A} = 25^{\circ} \text{C} \ \textbf{Unless Otherwise Specified (Continued)} \end{array}$

| PARAMETER                                                                                                  | TEST CONDITIONS                                                                                                                                                                                                                  | MIN       | TYP   | MAX      | UNITS            |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|----------|------------------|

|                                                                                                            | LOGIC SIGNALS                                                                                                                                                                                                                    | 1         | 1     | <u> </u> |                  |

| LOGIC SIGNAL EXF                                                                                           | ECTED RANGES (PWM, SCLK, SDATA, SOC, CLK, NDRIVE)                                                                                                                                                                                |           |       |          |                  |

| HIGH voltage                                                                                               | Logic Level HIGH Voltage Range                                                                                                                                                                                                   | 2.0       |       |          | V                |

| LOW voltage                                                                                                | Logic Level LOW Voltage Range                                                                                                                                                                                                    |           |       | 0.8      | V                |

| HIGH current                                                                                               | Output source current HIGH                                                                                                                                                                                                       | -5.0      | -20   |          | mA               |

| LOW current                                                                                                | Output sink Current LOW                                                                                                                                                                                                          | 5.0       | 20    |          | mA               |

| INPUT LOGIC CURF                                                                                           | EENT REQUIREMENTS (CLK, SCLK, NDRIVE)                                                                                                                                                                                            |           |       |          |                  |

| IIH                                                                                                        | Input High Current                                                                                                                                                                                                               | 1.7       |       | 2.7      | mA               |

| IIL                                                                                                        | Input Low Current                                                                                                                                                                                                                | 1.7       |       | 2.7      | mA               |

| MASTER CLOCK (C                                                                                            | LK)                                                                                                                                                                                                                              | I         |       | L 1      |                  |

| Frequency                                                                                                  | Master clock frequency                                                                                                                                                                                                           |           | 133   |          | MHz              |

| R                                                                                                          | Input pull up and pull down resistance                                                                                                                                                                                           | 1335      | 1907  | 2480     | Ω                |

|                                                                                                            | Note: DC accuracy of Voltage A/D is by reference<br>(Output = ERR = 6 bit, serial data word, MSB first, 66MHz clock freque                                                                                                       | ency)     |       |          |                  |

| INPUT SENSE SIGN                                                                                           | ALS                                                                                                                                                                                                                              | [         | 1     | TT       |                  |

| VSENP                                                                                                      | Positive Core Voltage of the Processor (filtered); RL = $10k\Omega$ , -400µA current draw                                                                                                                                        | 0.3       |       | Vdd      | V                |

| VSENN                                                                                                      | Return Core Voltage of the Processor (filtered);<br>RL = $10k\Omega$ , -400µA current draw                                                                                                                                       | -0.3      |       | 0.3      | V                |

| VSENP-VSENN                                                                                                | Differential Return Core Voltage of the Processor (filtered); RL = $10k\Omega$ , -400µA current draw                                                                                                                             | .3        |       | 1.8875   | V                |

| I VSENP                                                                                                    | Current into the VSENP pin                                                                                                                                                                                                       | -240      |       | 240      | uA               |

| I VSENN                                                                                                    | Current into the VSENNP pin                                                                                                                                                                                                      | -10       |       | 10       | ۸                |

|                                                                                                            |                                                                                                                                                                                                                                  |           |       |          | uA               |

| REGULATION ERRO                                                                                            | DR STEPS                                                                                                                                                                                                                         |           |       |          | UA               |

| REGULATION ERR                                                                                             | OR STEPS           Voltage increment step per LSB<br>(Over regulation range of 0.3 to 1.85VDC)                                                                                                                                   |           | 4.167 |          | mV               |

|                                                                                                            | Voltage increment step per LSB                                                                                                                                                                                                   | -133      | 4.167 | +128.83  |                  |

| ERR regulation step                                                                                        | Voltage increment step per LSB<br>(Over regulation range of 0.3 to 1.85VDC)                                                                                                                                                      | -133      | 4.167 | +128.83  | mV               |

| ERR regulation step ERR window DC ACCURACY                                                                 | Voltage increment step per LSB<br>(Over regulation range of 0.3 to 1.85VDC)                                                                                                                                                      | -133<br>6 | 4.167 | +128.83  | mV               |

| ERR regulation step                                                                                        | Voltage increment step per LSB<br>(Over regulation range of 0.3 to 1.85VDC)<br>Voltage window of ERR signal.                                                                                                                     |           | 4.167 | +128.83  | mV<br>mV         |

| ERR regulation step<br>ERR window<br>DC ACCURACY<br>Resolution<br>Differential                             | Voltage increment step per LSB<br>(Over regulation range of 0.3 to 1.85VDC)         Voltage window of ERR signal.         Any Channel; Minimum Resolution for which No Missing Codes are Guaranteed                              |           |       | +128.83  | mV<br>mV<br>Bits |

| ERR regulation step<br>ERR window<br>DC ACCURACY<br>Resolution<br>Differential<br>Nonlinearity<br>Integral | Voltage increment step per LSB<br>(Over regulation range of 0.3 to 1.85VDC)         Voltage window of ERR signal.         Any Channel; Minimum Resolution for which No Missing Codes are Guaranteed         Any Channel; LSB max |           | ± 1   | +128.83  | mV<br>mV<br>Bits |

$\label{eq:constraint} \begin{array}{l} \textbf{Electrical Specifications} \\ \textbf{V}_{DD} = 3.3 \text{VDC}, \ \textbf{V}_{CC} = 12 \text{VDC}, \ \textbf{V}_{DRIVE} = 5 \text{VDC}, \ \textbf{V}_{REF} = 2.5 \text{V}, \ \textbf{SYSCLK} = 133.33 \text{MHz}, \ \textbf{SCLK} = 16.67 \text{MHz}, \\ \textbf{T}_{A} = 25^{\circ} \text{C} \ \textbf{Unless Otherwise Specified (Continued)} \end{array}$

|                              | T <sub>A</sub> = 25°C Unless Otherwise Specified <b>(Continued)</b>                                                                                                               |            |            |             |         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-------------|---------|

| PARAMETER                    | TEST CONDITIONS                                                                                                                                                                   | MIN        | TYP        | MAX         | UNITS   |

| (Outpu                       | <b>CURRENT A/D CONVERTER</b><br>t = I <sub>DIG</sub> = 7-bit serial signal, first bit = START bit, 6 bit current word length (MSB first)                                          | , 66MHz c  | ock freque | ncy)        |         |

| CURRENT INFORM               | ATION STEP                                                                                                                                                                        |            |            |             |         |

| ISENSE step                  | Incremental step per LSB of voltage at I <sub>SENSE</sub> pin (I <sub>SENSE</sub> * R <sub>SENSE</sub> )                                                                          |            | 19.5       |             | mV      |

| ISENSE range                 | Voltage on the I <sub>SENSE</sub> pin that produces full scale output from the I <sub>SENSE</sub> A/D                                                                             |            |            | 1.25        | V       |

| DC ACCURACY                  |                                                                                                                                                                                   |            |            |             |         |

| Resolution                   | Any Channel; Minimum Resolution for which No Missing Codes are Guaranteed                                                                                                         | 6          |            |             | Bits    |

| Differential<br>Nonlinearity | Any Channel; LSB max                                                                                                                                                              |            | ± 1        |             | Bits    |

| Integral<br>Nonlinearity     | Any Channel; LSB max                                                                                                                                                              |            | ± 1        |             | Bits    |

| Gain Error                   | Any Channel; LSB max                                                                                                                                                              |            | ± 1        |             | Bits    |

| Offset Error                 | Any Channel; LSB max                                                                                                                                                              |            | ± 1        |             | Bits    |

| P CHANNEL DRAIN              | CURRENT SENSE (I <sub>SENSE</sub> )                                                                                                                                               |            |            |             |         |

| I <sub>SENSE</sub> ratio     | Ratio of V <sub>SW</sub> current to I <sub>SENSE</sub> current                                                                                                                    |            | 9900       |             |         |

|                              | WINDOW COMPARATOR                                                                                                                                                                 |            |            |             |         |

| ACTIVE TRANSIEN              | T RESPONSE (ATR) CONFIGURATION VALUES (sensed at the processor load)                                                                                                              |            |            |             |         |

| <sup>t</sup> ATR             | ATRL and ATRH signal delay                                                                                                                                                        |            | 10         |             | ns      |

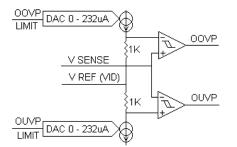

| OUTPUT UNDER VO              | DLTAGE/ OVER VOLTAGE RANGE OF CONFIGURATION VALUES                                                                                                                                |            |            |             |         |

| Over Voltage                 | Range of adjustment of the Over Voltage threshhold                                                                                                                                | 0          | +150       | 232         | mV      |

| Under Voltage                | Range of adjustment of the Under Voltage threshhold                                                                                                                               | -232       | -150       | 0           | mV      |

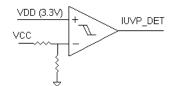

| When VCC is below            | TAGE PROTECTION VALUES<br>the threshold a comparator (with hysteresis) sets a bit in the fault register. The digital<br>VE to ground if IUVP is enabled and the fault bit is set. | controller | reads the  | fault regis | ter and |

| Vtlh                         | $V_{\mbox{\scriptsize CC}}$ Threshold, low to high (sweep Vcc from 6V to 10V).                                                                                                    | 8.6        | 9.1        | 9.6         | V       |

| VthI                         | V <sub>CC</sub> Threshold, high to low (sweep Vcc from 10V to 6V).                                                                                                                | 7.0        | 7.6        | 8.2         | V       |

| Vtlh-Vthl                    | $V_{CC}$ Threshold hysteresis, low to high to low (sweep $V_{CC}$ 6V to 10V to 6V).                                                                                               | 1.35       | 1.5        | 1.65        | V       |

| ldd                          | $V_{DD}$ current ( $V_{DD}$ = 3.3V)                                                                                                                                               |            | 8.5        |             | mA      |

| Iref                         | $V_{REF}$ current ( $V_{REF}$ = 2.5V)                                                                                                                                             |            | 1.3        |             | mA      |

|                              | PROGRAMMABLE FUNCTIONS                                                                                                                                                            |            |            |             |         |

| CURRENT LIMIT (V             | OLTAGE ON THE I <sub>SENSE</sub> PIN THAT TRIP THE PULSE BY PULSE CURRENT LIN                                                                                                     | IIT)       |            |             |         |

| Step                         | adjustment step size                                                                                                                                                              |            | 0.2        |             | V       |

| Range                        | Range of adjustment                                                                                                                                                               | .8         |            | 1.4         | V       |

| Default                      | Current Limit Default                                                                                                                                                             |            | 1.0        |             | V       |

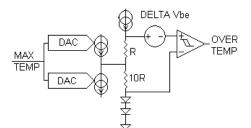

| TEMPERATURE SE               | NSE (JUNCTION TEMPERATURE THAT SETS THE OVER TEMPERATURE REG                                                                                                                      | ISTER)     |            |             |         |

| Step                         | Temperature Sense Step                                                                                                                                                            |            | 10         |             | °C      |

| Range                        | Over Temperature adjustment Range                                                                                                                                                 | 85         |            | 145         | °C      |

| Default                      | Over Temperature Default                                                                                                                                                          |            | 145        |             | °C      |

# Electrical Specifications $V_{DD} = 3.3$ VDC, $V_{CC} = 12$ VDC, $V_{DRIVE} = 5$ VDC, $V_{REF} = 2.5$ V, SYSCLK = 133.33MHz, SCLK = 16.67MHz, T<sub>A</sub> = 25°C Unless Otherwise Specified (Continued)

| PARAMETER        | TEST CONDITIONS          | MIN   | ТҮР   | MAX | UNITS |

|------------------|--------------------------|-------|-------|-----|-------|

| ATRH (ACTIVE TRA | NSIENT RESPONSE HIGH)    |       | 1     |     |       |

| Step             | ATRH Step                |       | -7.5  |     | mV    |

| Range            | ATRH adjustment Range    | -233  |       | 0   | mV    |

| Default          | Address Register Default |       | -67.5 |     | mV    |

| ATRL (ACTIVE TRA | NSIENT RESPONSE LOW)     | I     | Ľ     | I   |       |

| Step             | ATRL Step                |       | 7.5   |     | mV    |

| Range            | ATRL adjustment Range    | 0     |       | 233 | mV    |

| Default          | ATRL Default             |       | 75    |     | mV    |

| VID STEP         |                          | I     | I     | I   |       |

| Step             | VID Step                 |       | 12.5  |     | mV    |

| Range            | VID Range                | .8325 |       | 1.6 | V     |

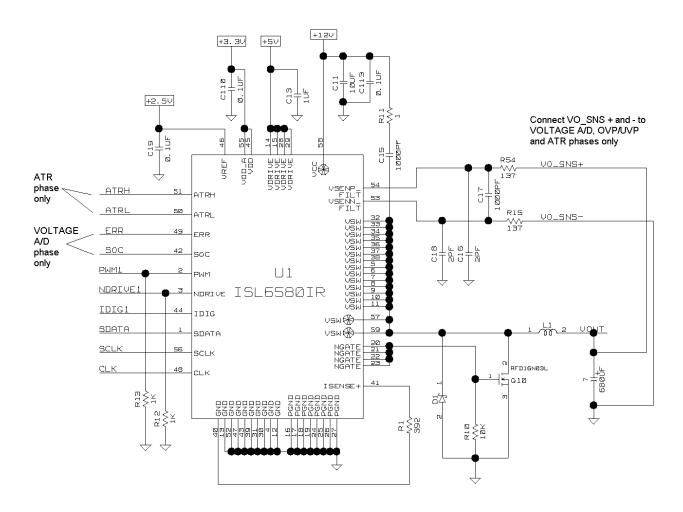

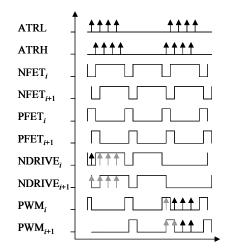

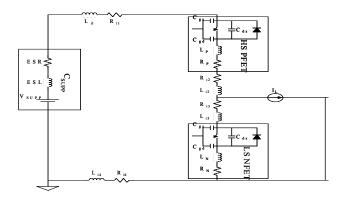

## Multi-Phase Power Conversion

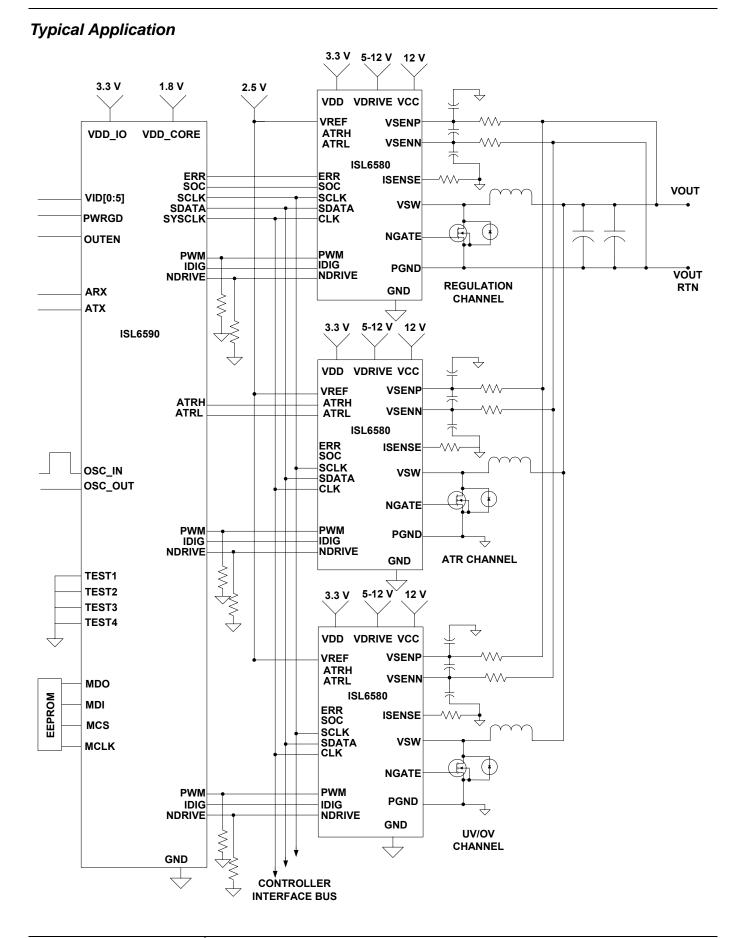

Microprocessor load current profiles have changed to the point where the multi-phase power conversion advantage is pronounced. The technical challenges associated with producing a single-phase converter which is both cost-effective and thermally viable have forced a change to the cost-saving approach of multi-phase. The ISL6590 controller and ISL6580 Power Stages help reduce the complexity of implementation by integrating vital functions and requiring minimal output components. The *Typical Application Drawing* provides a top level view of multi-phase power conversion using the ISL6590 and ISL6580. The *Typical Application Drawing* and the waveforms below describe a 3 phase converter. The ISL6590 can control up to 6 interleaved phases.

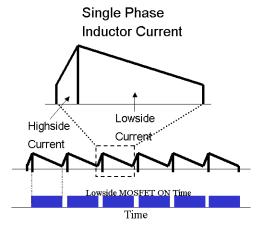

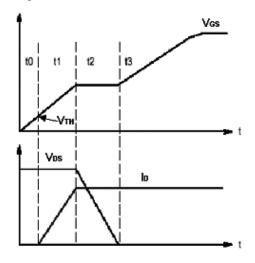

### Interleaving

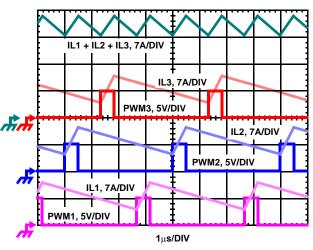

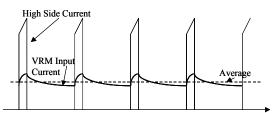

The switching of each channel in a multi-phase converter is timed to be symmetrically out of phase with each of the other channels. In a 3-phase converter, each channel switches 1/3 cycle after the previous channel and 1/3 cycle before the following channel. As a result, the three-phase converter has a combined ripple frequency three times greater than the ripple frequency of any one phase. In addition, the peak-topeak amplitude of the combined inductor currents is reduced in proportion to the number of phases (Equations 1 and 2). Increased ripple frequency and lower ripple amplitude mean that the designer can use less per-channel inductance and lower total output capacitance for any performance specification.

FIGURE 1. PWM AND INDUCTOR-CURRENT WAVEFORMS FOR 3-PHASE CONVERTER

Figure 1 illustrates the multiplicative effect on output ripple frequency. The three channel currents (IL1, IL2, and IL3), combine to form the AC ripple current and the DC load current. The ripple component has three times the ripple frequency of each individual channel current. The peak-to-peak current waveforms for each phase is about 7A, and the dc components of the inductor currents combine to feed the load.

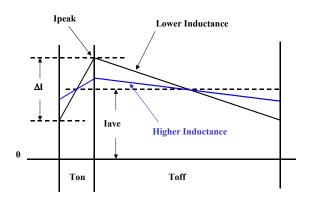

To understand the reduction of ripple current amplitude in the multi-phase circuit, examine the equation representing an individual channel's peak-to-peak inductor current.

$$I_{PP} = \frac{(V_{IN} - V_{OUT})V_{OUT}}{Lf_S V_{IN}}$$

(EQ. 1)

In Equation 1,  $V_{IN}$  and  $V_{OUT}$  are the input and output voltages respectively, L is the single-channel inductor value, and  $f_S$  is the switching frequency.

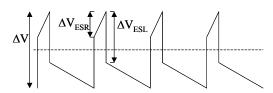

The output capacitors conduct the ripple component of the inductor current. In the case of multi-phase converters, the capacitor current is the sum of the ripple currents from each of the individual channels. Compare Equation 1 to the expression for the peak-to-peak current after the summation of N symmetrically phase-shifted inductor currents in Equation 2. Peak-to-peak ripple current decreases by an amount proportional to the number of channels. Output-voltage ripple is a function of capacitance, capacitor equivalent series resistance (ESR), and inductor ripple current. Reducing the inductor ripple current allows the designer to use fewer or less costly output capacitors.

$$I_{C, PP} = \frac{(V_{IN} - N V_{OUT}) V_{OUT}}{L f_S V_{IN}}$$

(EQ. 2)

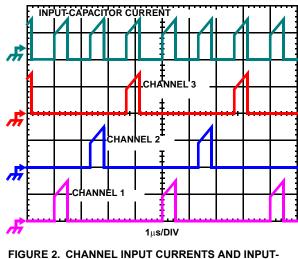

Another benefit of interleaving is to reduce input ripple current. Input capacitance is determined in part by the maximum input ripple current. Multi-phase topologies can improve overall system cost and size by lowering input ripple current and allowing the designer to reduce the cost of input capacitance. The example in Figure 2 illustrates input currents from a three-phase converter combining to reduce the total input ripple current.

FIGURE 2. CHANNEL INPUT CURRENTS AND INPUT-CAPACITOR RMS CURRENT FOR 3-PHASE CONVERTER

The converter depicted in Figure 2 delivers 36A to a 1.5V load from a 12V input. The RMS input capacitor current is

5.9A. Compare this to a single-phase converter also stepping down 12V to 1.5V at 36A. The single-phase converter has 11.9A RMS input capacitor current. The single-phase converter must use an input capacitor bank with twice the RMS current capacity as the equivalent three-phase converter.

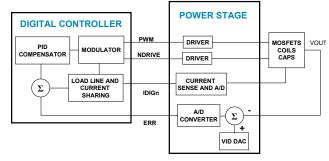

### Voltage Control Loop

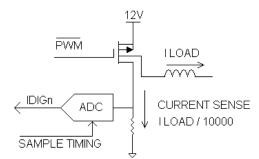

One of the ISL6580 power stages in a multiphase converter is used for voltage feed back. Output voltage is fed back to this power stage which subtracts the reference voltage (based on VID, see the VID table below) and converts the error voltage to a binary number. The digital error number is sent to the controller on the ERR line. The controller adds offset proportional to the load current for the load line (see next section on AVP) and passes the error number to the digital Proportional, Integral, Derivative (PID) compensator. The PID compensator is described in detail in a later section. Output from the PID compensator drives the 6 phase digital Pulse Width Modulator which produces the 6 PWM and DRIVE signals that control switching of the power MOSFETs.

FIGURE 3. VOLTAGE CONTROL LOOP BLOCK DIAGRAM

# Voltage Identification Codes (VID)

|                      | VID4 | VID3 | VID2 | VID1 | VID0 | VID5 |  |

|----------------------|------|------|------|------|------|------|--|

| V <sub>OUT</sub> (V) |      |      |      |      |      |      |  |

| 0.8375               | 0    | 1    | 0    | 1    | 0    | 0    |  |

| 0.8500               | 0    | 1    | 0    | 0    | 1    | 1    |  |

| 0.8625               | 0    | 1    | 0    | 0    | 1    | 0    |  |

| 0.8750               | 0    | 1    | 0    | 0    | 0    | 1    |  |

| 0.8875               | 0    | 1    | 0    | 0    | 0    | 0    |  |

| 0.9000               | 0    | 0    | 1    | 1    | 1    | 1    |  |

| 0.9125               | 0    | 0    | 1    | 1    | 1    | 0    |  |

| 0.9250               | 0    | 0    | 1    | 1    | 0    | 1    |  |

| 0.9375               | 0    | 0    | 1    | 1    | 0    | 0    |  |

| 0.9500               | 0    | 0    | 1    | 0    | 1    | 1    |  |

| 0.9625               | 0    | 0    | 1    | 0    | 1    | 0    |  |

| 0.9750               | 0    | 0    | 1    | 0    | 0    | 1    |  |

| 0.9875               | 0    | 0    | 1    | 0    | 0    | 0    |  |

| 1.0000               | 0    | 0    | 0    | 1    | 1    | 1    |  |

| 1.0125               | 0    | 0    | 0    | 1    | 1    | 0    |  |

| 1.0250               | 0    | 0    | 0    | 1    | 0    | 1    |  |

| 1.0375               | 0    | 0    | 0    | 1    | 0    | 0    |  |

| 1.0500               | 0    | 0    | 0    | 0    | 1    | 1    |  |

| 1.0625               | 0    | 0    | 0    | 0    | 1    | 0    |  |

| 1.0750               | 0    | 0    | 0    | 0    | 0    | 1    |  |

| 1.0875               | 0    | 0    | 0    | 0    | 0    | 0    |  |

| OFF                  | 1    | 1    | 1    | 1    | 1    | 1    |  |

| OFF                  | 1    | 1    | 1    | 1    | 1    | 0    |  |

| 1.1000               | 1    | 1    | 1    | 1    | 0    | 1    |  |

| 1.1125               | 1    | 1    | 1    | 1    | 0    | 0    |  |

| 1.1250               | 1    | 1    | 1    | 0    | 1    | 1    |  |

| 1.1375               | 1    | 1    | 1    | 0    | 1    | 0    |  |

| 1.1500               | 1    | 1    | 1    | 0    | 0    | 1    |  |

| 1.1625               | 1    | 1    | 1    | 0    | 0    | 0    |  |

| 1.1750               | 1    | 1    | 0    | 1    | 1    | 1    |  |

| 1.1875               | 1    | 1    | 0    | 1    | 1    | 0    |  |

| 1.2000               | 1    | 1    | 0    | 1    | 0    | 1    |  |

| 1.2125               | 1    | 1    | 0    | 1    | 0    | 0    |  |

| 1.2250               | 1    | 1    | 0    | 0    | 1    | 1    |  |

| 1.2375               | 1    | 1    | 0    | 0    | 1    | 0    |  |

| 1.2500               | 1    | 1    | 0    | 0    | 0    | 1    |  |

| 1.2625               | 1    | 1    | 1    | 0    | 0    | 0    |  |

| 1.2750               | 1    | 0    | 1    | 1    | 1    | 1    |  |

| 1.2750               | 1    | 0    | 1    | 1    | 1    | 0    |  |

| 1.3000               | 1    |      | 1    | 1    |      | 1    |  |

|                      |      | 0    |      |      | 0    |      |  |

| 1.3125               | 1    | 0    | 1    | 1    | 0    | 0    |  |

| 1.3250               | 1    | 0    | 1    | 0    | 1    | 1    |  |

| 1.3375               | 1    | 0    | 1    | 0    | 1    | 0    |  |

| 1.3500               | 1    | 0    | 1    | 0    | 0    | 1    |  |

| 1.3625               | 1    | 0    | 0    | 0    | 0    | 0    |  |

| V <sub>OUT</sub> (V) | VID4 | VID3 | VID2 | VID1 | VID0 | VID5 |

|----------------------|------|------|------|------|------|------|

| 1.3750               | 1    | 0    | 0    | 1    | 1    | 1    |

| 1.3875               | 1    | 0    | 0    | 1    | 1    | 0    |

| 1.4000               | 1    | 0    | 0    | 1    | 0    | 1    |

| 1.4125               | 1    | 0    | 0    | 1    | 0    | 0    |

| 1.4250               | 1    | 0    | 0    | 0    | 1    | 1    |

| 1.4375               | 1    | 0    | 0    | 0    | 1    | 0    |

| 1.4500               | 1    | 0    | 0    | 0    | 0    | 1    |

| 1.4625               | 1    | 0    | 1    | 0    | 0    | 0    |

| 1.4750               | 0    | 1    | 1    | 1    | 1    | 1    |

| 1.4875               | 0    | 1    | 1    | 1    | 1    | 0    |

| 1.5000               | 0    | 1    | 1    | 1    | 0    | 1    |

| 1.5125               | 0    | 1    | 1    | 1    | 0    | 0    |

| 1.5250               | 0    | 1    | 1    | 0    | 1    | 1    |

| 1.5375               | 0    | 1    | 1    | 0    | 1    | 0    |

| 1.5500               | 0    | 1    | 1    | 0    | 0    | 1    |

| 1.5625               | 0    | 1    | 0    | 0    | 0    | 0    |

| 1.5750               | 0    | 1    | 0    | 1    | 1    | 1    |

| 1.5875               | 0    | 1    | 0    | 1    | 1    | 0    |

| 1.6000               | 0    | 1    | 0    | 1    | 0    | 1    |

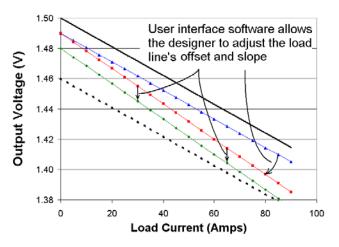

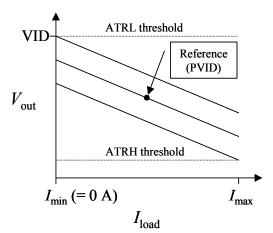

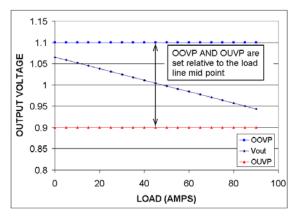

# AVP (Adaptive Voltage Positioning)

# Load Line Specifications

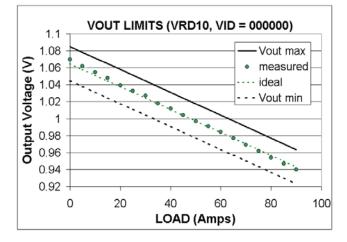

Recent Voltage Regulator specs require the regulated output voltage to decrease as load current increases as it would with a small output resistance (~0.5 to  $1.5m\Omega$ ). A typical (VRD10) specification for output voltage is:

$Vout_max = V_{VID} - Iload^*.00135$

Vout\_min =  $V_{VID}$  -0.04V-Iload\*0.00135

$V_{VID}$  is the maximum output voltage at 0 load. It is set by a 5 or 6 bit binary input to the voltage regulator called VID (Voltage ID). For VRD10, VID = 100011 indicates  $V_{OUT}$  max = 1.000V. The slope of the load line is different for other applications. For VRM 9, Vout\_max =  $V_{VID}$  – Iload\*.00095. The slope and offset from  $V_{VID}$  is adjustable in the ISL6580 / ISL6590 using the user interface software. See the User Interface Software section.

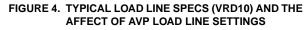

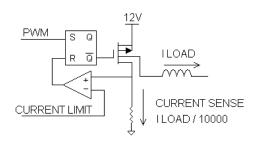

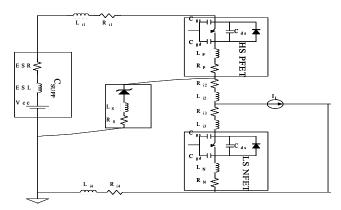

The ISL6580 / ISL6590 realize this behavior in a programmable, lossless way. Load current is measured in each ISL6580 output stage. A fraction (1/9900) of the current in the upper MOSFET is mirrored and sent through an external resistor. The voltage on the current sense resistor is sampled near the end of the upper FET's ON time, converted to a digital number and sent to the ISL6590 controller on the IDIGn line (see Figure 5). Current sensing is described in more detail in the next section.

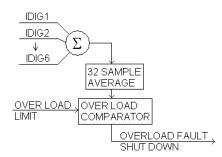

#### FIGURE 5. CURRENT SENSE BLOCK DIAGRAM

The sum of all power device currents is multiplied by a gain factor, passed through a digital low pass filter and added to the error voltage (see Figure 6).

# FIGURE 6. AVP LOAD LINE CONTROL IS ADDED TO THE ERROR SIGNAL

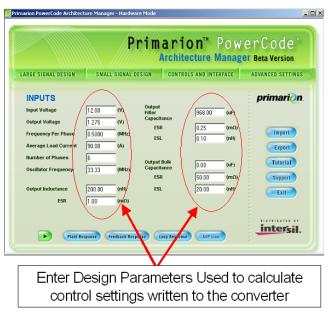

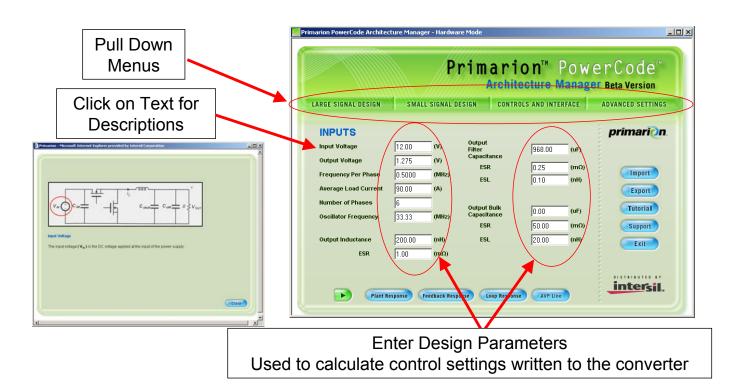

The gain factor controls how much the output voltage 'droops' and is set by the system designer using the user interface software. The user interface software calculates a number of internal register values based on data in the Large Signal Design, Inputs window. All values on the Inputs window must be entered correctly for the AVP loadline to be programmed correctly to the controller.

The user interface software will generate a plot of the loadline. It is viewed by clicking on the AVP line button at the bottom of all of the user interface software windows.

FIGURE 7. USER INTERFACE LOAD LINE ADJUSTMENTS

AVP offset moves the load line relative to the voltage required by the input VID. It can be adjusted from 0 to 50mV in steps of 3.125mV. AVP LoadLine controls the slope of the load line. This gives the designer complete flexibility within the specified "max" and "min" limits.

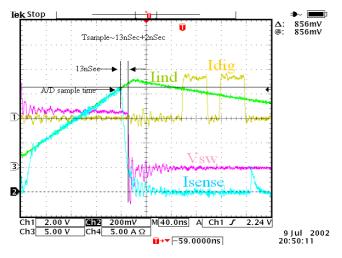

### **Current Sensing**

Current sensing is a key feature in the Intersil Digital Architecture. Precision current sensing is required to maintain accurate load lines, good current sense balancing between phases, thermal balancing, overload current, and peak current limit protection.

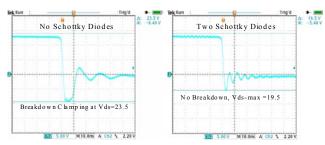

By integrating the high side MOSFET in the power stage of the Intersil Digital Architecture (see Figure 8), very accurate current sensing can be achieved across temperature. This method of current sense through integration is called current mirroring. A current mirror simply designates a certain ratio of transistors on the silicon of FET to have a separate source output but a common drain node. As a result, a small current sample from the FET can be drawn external to the power stage and through a sense resistor. Voltage across the sense resistor represents the total current through the High Side FET. Since the mirror is using the same silicon as the main current path, variations in Rdson and switching characteristics mirror that of the main FET channel. The internal structure of the sampling circuitry is seen in Figure 8.

FIGURE 8. INTERNAL STRUCTURE OF THE ISL6580 POWER STAGE

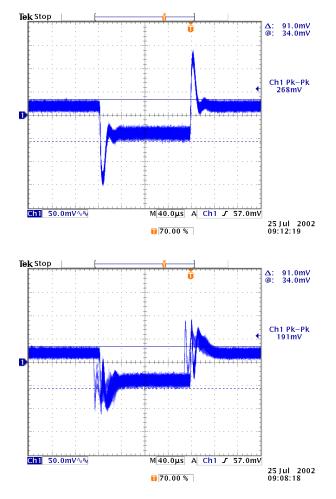

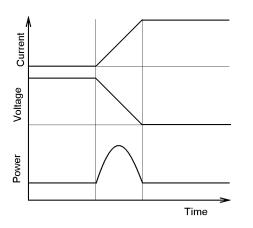

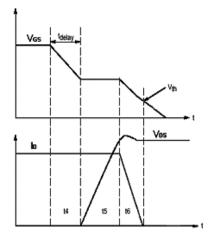

A sample of the peak current through the MOSFET is taken each clock cycle, converted to a digital signal, and sent to the controller. The master oscillator frequency inside the Intersil Digital Architecture is 133.33MHz. Figure 9 shows the voltage drop across the sense resistor, the voltage at the switch node, the inductor current, and the digital voltage signal. The inductor current signal is delayed slightly due to the probe parasitics. As can be seen from the figure, 13nS prior to the turn off of the high side MOSFET a sample of the voltage across the sense resistor is taken (I<sub>SENSE</sub>). This is done to avoid voltage spiking during the switching of the node. After sampling, I<sub>SENSE</sub> is converted to a digital signal (I<sub>DIG</sub>). The controller receives the digital signal from the I<sub>DIG</sub> pin.

FIGURE 9. VOLTAGE DROP ACROSS THE SENSE RESISTOR, VOLTAGE AT SWITCH NODE, INDUCTOR CURRENT, AND DIGITAL VOLTAGE SIGNAL

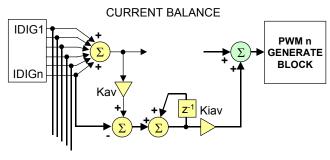

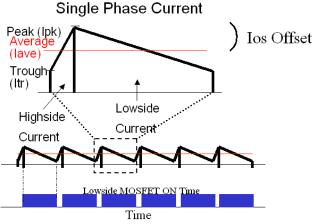

#### Current Sharing

Each ISL6580 senses current in it's upper MOSFET as described above and converts it to a serial digital signal on the IDIGn lines. The sampled, digitized current, IDIG<sub>n</sub>, from each active channel is used to gauge both overall load current and the relative channel current carried in each leg of the converter. The individual sample currents are summed and divided by the number of active channels. The resulting average current,  $I_{AVG}$ , provides a measure of the total load current demand on the converter and the appropriate level of channel current. The average current is then subtracted from the individual channel sample currents. The resulting error current,  $I_{ER}$ , is then filtered before it adjusts  $V_{COMP}$  The modified  $V_{COMP}$  signal is compared to a sawtooth ramp signal and produces a pulse width which corrects for any unbalance and drives the error current toward zero.

FIGURE 10. CURRENT BALANCE

### Loop Compensation

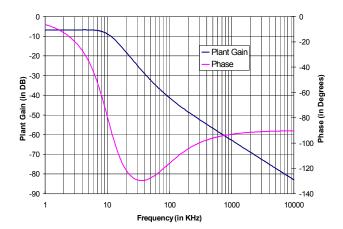

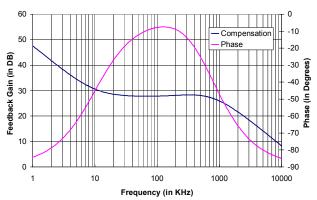

Any closed loop system must be designed to insure stability (prevent oscillation) and provide correct response to external events such as load transients. The output of a buck regulator has an inherent, low pass filter formed by the output inductor(s), output capacitance and their ESRs (Equivalent Series Resistance). Figure 1 shows a typical gain and phase plot of output inductors, capacitors and ESR.

FIGURE 11. FREQUENCY RESPONSE OF THE OUTPUT INDUCTORS AND CAPACITORS

Above the resonant frequency of the output LC filter (10kHz in this case) the gain falls at a rate of 40dB/decade and the phase shift approaches –180 degrees. At a frequency above the F =  $1/(2\delta C^*ESR) = 500$ kHz in this case) the gain slope changes to –20dB/decade and the phase shift approaches – 90 degrees.

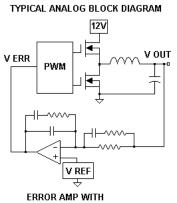

In a closed loop control system, the output is subtracted from a reference voltage to produce an error voltage. The error voltage is amplified and fed to the output stage. In a buck regulator the output stage consists of a Pulse Width Modulator (PWM), switching transistors (typically MOSFETs), series inductor(s) and output capacitors. High gain feedback reduces variation in the output due to changes in input voltage, load current and component values. However, high gain at high frequencies can cause excessive over shoot in response to transients ( if phase shift > 120 degrees and gain > 0dB ) or oscillation ( if phase shift > 180 degrees and gain > 0dB ). The trade off in designing the loop compensation is to achieve fast response to transients without excessive overshoot or oscillation.

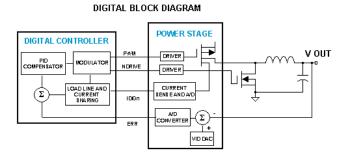

FREQUENCY COMPENSATION

FIGURE 13. DIGITAL CONTROL LOOP BLOCK DIAGRAM

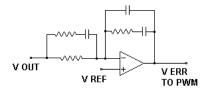

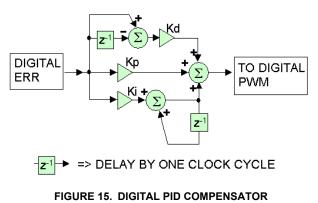

The ISL6580 subtracts a reference from the output voltage to produce an error voltage. It converts the error voltage to a 6 bit digital number and sends it to the ISL6590 controller. The controller processes the error number numerically to provide gain (<u>Proportional</u>), phase lag (<u>Integration</u>) and phase lead (<u>Derivative</u>) functions. This forms the digital PID control.

FIGURE 14. TYPICAL ANALOG ERROR AMPLIFIER AND COMPENSATION

# Adjusting The Digital PID

Frequency response of the digital PID compensator is determined by the Kp, Ki, Kd factors. These factors are stored in nonvolatile memory and are loaded in the controller at power on reset. The system designer sets the PID compensators frequency response using user interface software. The designer enters the frequencies of the desired poles and zeros and user interface software calculates the Kp, Ki and Kd factors. the software will calculate and display the frequency response of the feedback and the closed loop system.

FIGURE 16. DESIGN PARAMETER INPUT WINDOW

| 1                                                         | Frequencies Here                                             | 2                  |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------|--------------------|--|--|

|                                                           | Primarion <sup>®</sup> Pow<br>Architecture Manag             | erCode             |  |  |

| LARGE SIGNAL DESIGN SMALL                                 | SIGNAL DESIGN CONTROLS AND INTERFACE                         | ADVANCED SETTINGS  |  |  |

| Loop Response                                             | Rp2 Cp2 Time Constant 7958 (n5)                              | primari@n.         |  |  |

| F21 9.00 (KHz)<br>F22 [270.00 (KHz)<br>Fp1 [2308.00 (KHz) | Q 0.00 Input Voltage 12.00 (V)                               | Export<br>Tutorial |  |  |

| Fp2 2000.00 (KHz)                                         | Output Voltage 1,3000 (V)<br>Average Load Current 100.00 (A) | Support            |  |  |

| Pres Loop<br>Response                                     | diack Response Closed Loop AIP Livid Live                    | intersil.          |  |  |

|                                                           |                                                              |                    |  |  |

| Click Here to see a Calculation<br>of Frequency Response  |                                                              |                    |  |  |

| FIGURE 17. S                                              | SMALL SIGNAL DESIGN                                          | WINDOW             |  |  |

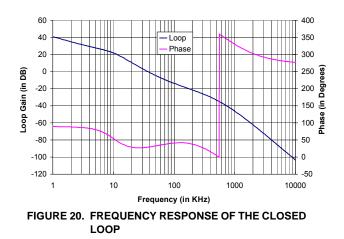

The software will calculate the frequency response of the PID controller and the closed loop system as in figures 19 and 20 below.

# ISL6580

### **Compensation Methodology**

Due to the user interface software interface, it is very easy to change the frequency compensation and see the resulting performance on a scope or network analyzer. Transient response is viewed by applying a transient load and monitoring the output voltage with a scope. Frequency response is viewed by placing a small resistor between the output and the feed back network, applying a small sine wave at the input to the feed back network and measuring the amplitude and phase shift of the resulting sine wave on the output. Sweeping the frequency produces plots similar to those above.

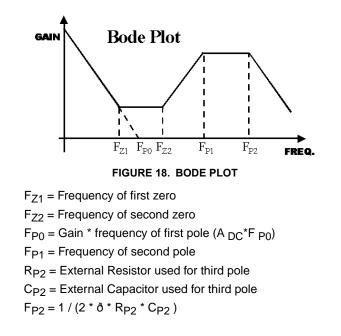

### Frequency Domain

It is recommended to place the first zero (F<sub>Z1</sub>) at the resonant frequency of the output inductors and capacitors (F =  $1/(2\delta + LC) = 10$  kHz in this case). Then increase F<sub>72</sub> and FP0 to maximize DC gain and the frequency at which gain drops below 0dB while keeping the phase margin above 60 degrees. Phase Margin is the difference between 180 degrees and the phase shift of the loop at the frequency where the gain drops below 0dB (cross over frequency). If the loops phase shift reaches 180 degrees and has gain equal to or greater than 0dB, it acts as positive feed back and the loop will oscillate. Even if the loops phase shift is slightly below 180 degrees at the cross over frequency, the loop will respond to transients with overshoot and ringing. Loop phase shift between 90 and 120 degrees at the cross over frequency (Phase margin = 60 to 90 degrees) results in little or no over shoot and ringing. Large phase margins (>90 degrees) result in slower transient response.

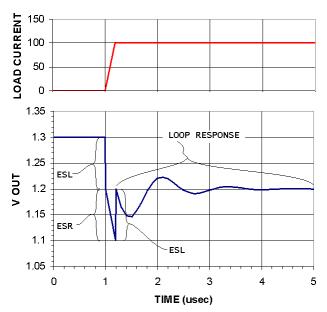

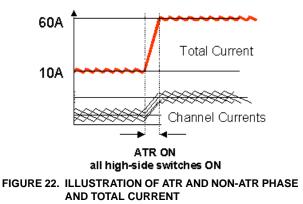

#### Time Domain