查询ADI\$16201供应商

### 捷多邦,专业PCB打样工厂,24小时加急出货

# **ANALOG DEVICES**

### **Preliminary Technical Data**

#### FEATURES

Dual-axis inclinometer/accelerometer measurements 12/14-bit digital inclination/acceleration sensor outputs ±1.7 g accelerometer measurement range +90° inclinometer measurement range 12-bit digital temperature sensor output Digitally controlled sensitivity and bias calibration **Digitally controlled sample rate Digitally controlled frequency response** Dual alarm settings with rate/threshold limits Auxiliary digital I/O **Digitally activated self-test** Digitally activated low power mode SPI® compatible serial interface Auxiliary 12 bit ADC input and DAC output DZSC.COM Single-supply operation – 3.0 to 3.6V 3500 g powered shock survivability

#### **APPLICATIONS**

Pla<mark>tform s</mark>tabilization and leveling Tilt Sensing, Inclinometers Motion / Position measurement Monitor/Alarm Devices (Security, Medical, Safety)

### **GENERAL DESCRIPTION**

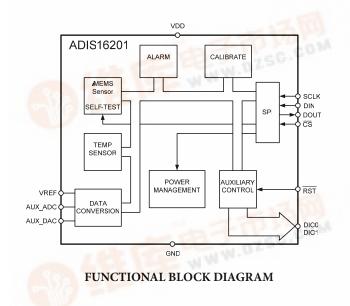

The ADIS16201 is a complete, dual-axis acceleration and inclination angle measurement system available in a single compact package enabled by ADI's *i*Sensor<sup>™</sup> integration. By enhancing ADI's *i*MEMS\* sensor technology with an embedded signal processing solution, the ADIS16201 provides factory calibrated and tunable digital sensor data in a convenient format that can be accessed using a simple SPI serial interface. The SPI interface provides access to measurements of the following parameters: dual-axis linear acceleration, dual-axis linear inclination angle, temperature, power supply and one auxiliary analog input. Easy access to calibrated digital sensor data provides developers with a system-ready device, reducing development time, cost and program risk.

**Programmable Dual-Axis**

**ADIS16201**

Inclinometer/Accelerometer

Unique characteristics of the end system can be easily accommodated via several built-in features, including an autozero recalibration via a single register command, as well as configurable sample rate and frequency response.

The ADIS16201 also offers a comprehensive set of features which can be used to further reduce the hardware complexity of system designs. These integrated features include a configurable alarm function, auxiliary 12-bit ADC, auxiliary 12-bit DAC, configurable digital I/O port, and a digital self test function. The ADIS16201 offers two different power management features that can be enabled via the SPI port: a programmable duty cycle sleep mode for systems that do not require continuous operation and a low power mode for systems that can trade reduced sample rates for more efficient power operation.

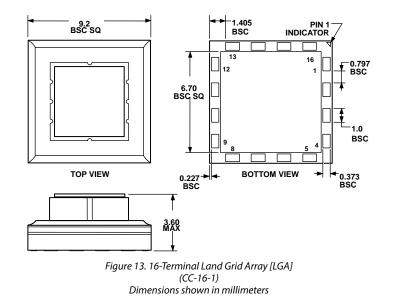

The ADIS16201 is available in a 9.2mm x 9.2mm x 4mm laminate based Land Grid Array (LGA) package with a temperature range of -40°C to +125°C.

# Preliminary Technical Data

#### TABLE OF CONTENTS

| Specifications                              | 3          |

|---------------------------------------------|------------|

| Timing Specifications                       | 5          |

| Absolute Maximum Ratings                    | 6          |

| ESD Caution                                 | 6          |

| Pin Configuration and Function Descriptions | 7          |

| Theory of Operation                         | <u>8</u>   |

| Basic Operation                             | <u>10</u>  |

| Programming and Control                     | 1 <u>2</u> |

| Calibration Registers                       | 15         |

| Alarm Functions                             | 17         |

| Auxiliary ADC Function                      | 26         |

| Temperature Sensor                          | 8          |

| Auxiliary DAC Function                      | 26         |

| Miscellaneous Control Register              | 25         |

| General Purpose I/O Control                 | 27         |

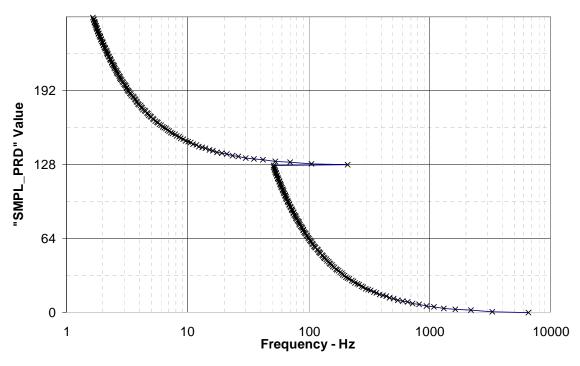

| Sample Period Control 2                   | 0 |

|-------------------------------------------|---|

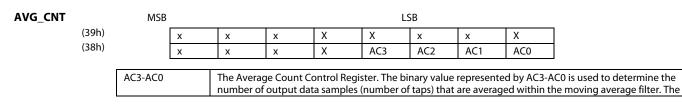

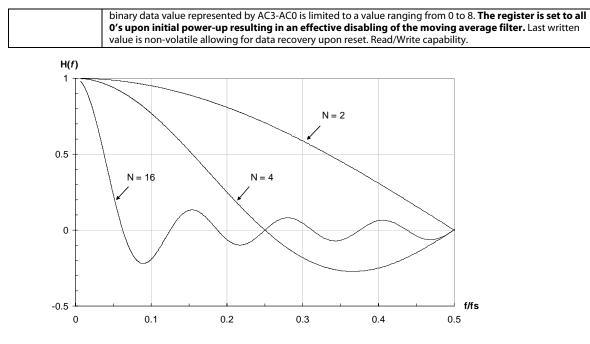

| Filtering Control                         | 1 |

| Power-Down Control 2                      | 3 |

| Status Feedback 2                         | 3 |

| Command Control 2                         | 4 |

| Applications2                             | 8 |

| Serial Peripheral Interface2              | 8 |

| Hardware Considerations 2                 | 9 |

| Grounding And Board Layout Recomendations | 9 |

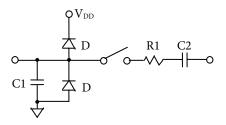

| Bandgap Reference 2                       | 9 |

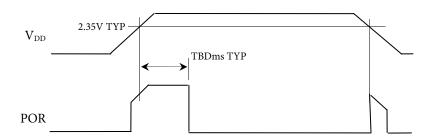

| Power-On Reset Operation2                 | 9 |

| Outline Dimensions2                       | 9 |

| Ordering Guide                            |   |

#### **REVISION HISTORY**

5/05—Revision PrA

10/05 — Revision PrB

# **Preliminary Technical Data**

### **SPECIFICATIONS**

$T_{\rm A}$  = –40°C to 125°C,  $V_{\rm DD}$  = 3.3 V, tilt = 0°, unless otherwise noted.

#### Table 1

| Parameter                                  | Conditions                                              | Min  | Тур    | Max  | Unit        |

|--------------------------------------------|---------------------------------------------------------|------|--------|------|-------------|

| INCLINOMETER                               | Each axis                                               |      |        |      |             |

| Input Range                                | Operable to $\sim \pm 90$ degree                        |      | ±70    |      | degree      |

| Accuracy                                   | 0° to +30° , 25°C, max filter                           |      | ±0.25  |      | degree      |

|                                            | $\pm 30^{\circ}$ to $\pm 60^{\circ}$ , 25°C, max filter |      | ±0.50  |      | degree      |

| Initial Sensitivity                        | @ 25°C                                                  | TBD  | 10     | TBD  | LSB/degree  |

| Sensitivity Over Temperature               |                                                         |      | 40     |      | ppm/°C      |

| Initial Bias                               | @ 25°C                                                  | TBD  | 2048   | TBD  | LSB         |

| Bias Over Temperature                      |                                                         |      | 40     |      | ppm/°C      |

| ACCELEROMETER                              | Each axis                                               |      |        |      |             |

| Input Range <sup>1</sup>                   | @25°C                                                   | ±1.7 |        |      | g           |

| Nonlinearity <sup>1</sup>                  | % of full scale                                         |      | ±0.5   | ±2.5 | %           |

| Alignment Error                            | X sensor to Y sensor                                    |      | ±0.1   |      | degree      |

| Cross Axis Sensitivity <sup>1</sup>        |                                                         |      | ±2     | ±5   | %           |

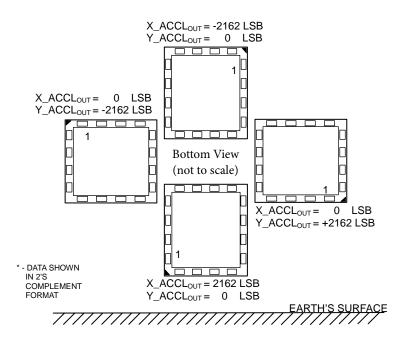

| Initial Sensitivity                        | @25°C                                                   | TBD  | 2.16   | TBD  | LSB/mg      |

| Sensitivity Over Temperature               |                                                         |      | 40     |      | ppm/°C      |

| Initial Bias                               | @25°C                                                   | TBD  | 8192   | TBD  | LSB         |

| Bias Over Temperature                      |                                                         |      | 50     |      | ppm/°C      |

| ACCELEROMETER NOISE PERFORMANCE            |                                                         |      |        |      |             |

| Output Noise                               | @25°C, no averaging                                     |      | 21.5   |      | LSB rms     |

| Noise Density                              | @25°C, no averaging                                     |      | 0.36   |      | LSB/√Hz rms |

| ACCELEROMETER FREQUENCY RESPONSE           |                                                         |      |        |      |             |

| Sensor Bandwidth                           |                                                         |      | 2250   |      | Hz          |

| Sensor Resonant Frequency                  |                                                         |      | 5.5    |      | kHz         |

| ACCELEROMETER SELF-TEST STATE <sup>2</sup> |                                                         |      |        |      |             |

| Output Change When Active                  |                                                         | 372  | 708    | 1040 | LSB         |

| TEMPERATURE SENSOR                         |                                                         |      |        |      |             |

| Output at 25°C                             |                                                         |      | 1278   |      | LSB         |

| Scale Factor                               |                                                         |      | -2.129 |      | LSB/°C      |

| ADC Input                                  |                                                         |      |        |      |             |

| Resolution                                 |                                                         |      | 12     |      | Bits        |

| Integral Non-Linearity                     |                                                         |      | ±0.5   |      | LSB         |

| Differential Non-Linearity                 |                                                         |      | ±0.5   |      | LSB         |

| Offset Error                               |                                                         |      | ±1     |      | LSB         |

| Gain Error                                 |                                                         |      | ±1     |      | LSB         |

| Input Range                                |                                                         | 0    |        | 2.5  | Volts       |

| Input Capacitance                          | During acquisition                                      |      | 20     |      | pF          |

# Preliminary Technical Data

| Parameter                              | Conditions                        | Min       | Тур      | Max | Unit   |

|----------------------------------------|-----------------------------------|-----------|----------|-----|--------|

| DAC OUTPUT                             | 5 kΩ//100 pF to GND               |           |          |     |        |

| Resolution                             |                                   |           | 12       |     | Bit    |

| Relative Accuracy                      | For Codes 101 to 3994             |           | 2        |     | LSB    |

| Differential Nonlinearity              |                                   |           | 1        |     | LSB    |

| Offset Error                           |                                   |           | 5        |     | mV     |

| Gain Error                             |                                   |           | 0.5      |     | %      |

| Output Range                           |                                   |           | 0 to 2.5 |     | V      |

| Output Impedance                       |                                   |           | 10       |     | Ω      |

| Output Settling Time                   |                                   |           | 10       |     | μs     |

| LOGIC INPUTS                           |                                   |           |          |     |        |

| Input High Voltage, V <sub>INH</sub>   |                                   | 2.0       |          |     | V      |

| Input Low Voltage, V <sub>INL</sub>    |                                   |           |          | 0.4 | V      |

| Input Current, I <sub>IN</sub>         |                                   |           | 1        | 10  | μΑ     |

| Input Capacitance, C <sub>IN</sub>     |                                   |           | 10       |     | pF     |

|                                        |                                   |           |          |     |        |

| DIGITAL OUTPUTS                        |                                   |           |          |     |        |

| Output High Voltage (V <sub>он</sub> ) | I <sub>SOURCE</sub> = 1.6 mA      | VDD - 0.4 |          |     | V      |

| Output Low Voltage (V <sub>OL</sub> )  | $I_{SINK} = 1.6 \text{ mA}$       |           |          | 0.4 | V      |

| Sleep TIMER                            |                                   |           |          |     |        |

| Timeout Period <sup>3</sup>            |                                   | 0.5       |          | 128 | sec    |

| FLASH MEMORY                           |                                   |           |          |     |        |

| Endurance <sup>4</sup>                 |                                   | 20,000    |          |     | Cycles |

| Data Retention <sup>5</sup>            | T <sub>J</sub> = 55°C             | 20        |          |     | Years  |

| CONVERSION RATE                        |                                   |           |          |     |        |

| Minimum Conversion Time                |                                   |           | 153      |     | us     |

| Maximum Conversion Time                |                                   |           | 605      |     | ms     |

| MaximumThroughput Rate                 |                                   |           | 6554     |     | SPS    |

| Minimum Throughput Rate                |                                   |           | 1.65     |     | SPS    |

| POWER SUPPLY                           |                                   |           |          |     |        |

| Operating Voltage Range VDD            |                                   | 3.0       | 3.3      | 3.6 | V      |

| Power Supply Current                   |                                   |           | 10       | TOO |        |

| Normal Operation                       | Conversion time <u>&gt;</u> 1.0ms |           | 12       | TBD | mA     |

| Power Supply Current                   |                                   |           | 20       | TOO |        |

| High Performance Mode                  | Conversion time <1.0ms            |           | 38       | TBD | mA     |

| Power Supply Current                   |                                   |           | 500      | TOO |        |

| Sleep Mode                             |                                   |           | 500      | TBD | μΑ     |

| Turn-On Time                           |                                   |           | 275      |     | ms     |

|                                        |                                   |           | 215      |     | 1115   |

<sup>1</sup> Guaranteed by *i*MEMs packaged part testing.

<sup>2</sup> Self-test response changes as the square of VDD.

<sup>3</sup> Guaranteed by Design.

<sup>4</sup> Endurance is qualified as per JEDEC Std. 22 Method A117 and measured at -40°C, +25°C, +85°C and +125°C.

<sup>5</sup> Retention lifetime equivalent at junction temperature (Tj) 55°C as per JEDEC Std. 22 Method A117. Retention lifetime will derate with junction temperature.

### **Preliminary Technical Data**

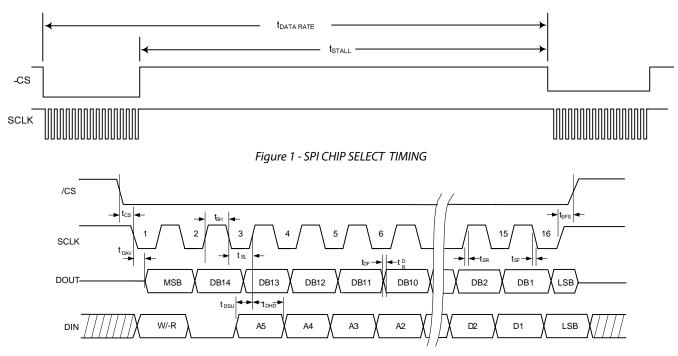

### **TIMING SPECIFICATIONS**

$T_A = -40^{\circ}$ C to 125°C,  $V_{DD} = 3.3$  V, tilt = 0°, unless otherwise noted.

#### Table 2

|                       |                                               |                  |     | Max  |        |

|-----------------------|-----------------------------------------------|------------------|-----|------|--------|

| Parameter             | Description                                   | $\mathbf{Min}^1$ | Тур |      | Unit   |

| fsclk                 |                                               | 0.01             |     | 3.48 | MHz    |

| t <sub>datarate</sub> | Chip Select Period, Higher Performance Mode   | 60               |     |      | μs     |

| t <sub>datarate</sub> | Chip Select Period, Power Efficient Mode      | 100              |     |      | μs     |

| t <sub>cs</sub>       | Chip Select to Clock Edge                     | 48.8             |     |      | ns     |

| tsl                   | SCLK Low Pulse Width                          |                  | TBD |      | ns     |

| tsh                   | SCLK High Pulse Width                         |                  | TBD |      | ns     |

| $t_{\rm DAV}$         | Data Output Valid after SCLK Edge             |                  |     | 25   | ns     |

| $t_{\rm DSU}$         | Data Input Setup Time Before SCLK Rising Edge | 24.4             |     |      | ns     |

| t <sub>DHD</sub>      | Data Input Hold Time After SCLK Rising Edge   | 48.8             |     |      | ns     |

| t <sub>DF</sub>       | Data Output Fall Time                         |                  | 5   | 12.5 | ns min |

| t <sub>DR</sub>       | Data Output Rise Time                         |                  | 5   | 12.5 | ns min |

| t <sub>SR</sub>       | SCLK Rise Time                                |                  | 5   | 12.5 | ns min |

| t <sub>SF</sub>       | SCLK Fall Time                                |                  | 5   | 12.5 | ns max |

| tsfs                  | /CS High after SCLK Edge                      | 0                |     |      | us typ |

<sup>1</sup> Guaranteed by design. Typical specifications are not tested or guaranteed.

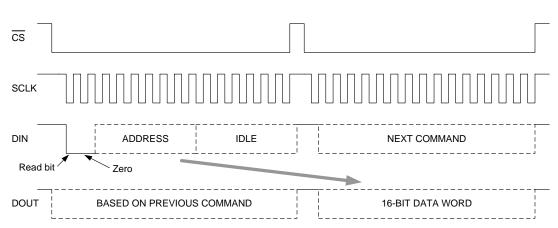

Figure 2 - SPI TIMING

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                           | Rating              |

|-------------------------------------|---------------------|

| Acceleration (Any Axis, Unpowered)  | 3500 g              |

| Acceleration (Any Axis, Powered)    | 3500 g              |

| VDD to COM                          | –0.3 V to +7.0 V    |

| Digital Input/Output Voltage to COM | –0.3 V to +5.5 V    |

| Analog Inputs to COM                | –0.3 to VDD + 0.3 V |

| Analog Inputs to COM                | –0.3 to VDD + 0.3 V |

| Operating Temperature Range         | -40°C to +125°C     |

| Storage Temperature                 | –65°C to +150°C     |

Stresses above those listed under the Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

(electrostatic ESD discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

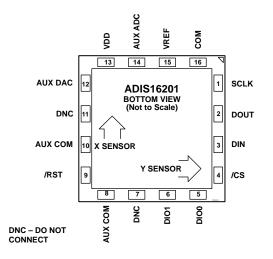

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

| Table 4. Pin | Function | Descriptions |

|--------------|----------|--------------|

|--------------|----------|--------------|

| Pin No. | Mnemonic  | Туре | Description                                                                                                                          |

|---------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 13      | VDD       | S    | +3.3 V Power Supply.                                                                                                                 |

| 16      | СОМ       | S    | Common. Reference point for all circuitry in the ADIS16201.                                                                          |

| 12      | AUX DAC   | 0    | Auxiliary DAC Analog Voltage Output.                                                                                                 |

| 14      | AUX ADC   | I.   | Auxiliary ADC Analog Input Voltage.                                                                                                  |

| 15      | VREF      | 0    | Precision Reference Output.                                                                                                          |

| 1       | SCLK      | I    | Serial Clock. SCLK provides the serial clock for accessing data from the part and writing serial data to the control registers.      |

| 3       | DIN       | I    | Data In. Data to be written to the control registers is provided on this input and is clocked in on the rising edge of the SCLK.     |

| 2       | DOUT      | 0    | Data Out. The data on this pin represents data being read from the control registers and is clocked on the falling edge of the SCLK. |

| 4       | CS        | I    | Chip Select. Active low. This input frames the serial data transfer.                                                                 |

| 9       | RST       | I    | Reset. Active low. This input resets the embedded microcontroller to a known state.                                                  |

| 5, 6    | DIO0-DIO1 | I/O  | Multifunction Digital I/O pin.                                                                                                       |

| 7, 11   | DNC       | NA   | Do Not Connect.                                                                                                                      |

| 8, 10   | AUX COM   | S    | Auxiliary Grounds. Connected to GND for proper operation.                                                                            |

### THEORY OF OPERATION

The ADIS16201 is a complete dual-axis digital inclinometer/accelerometer that uses Analog Devices' surfacemicromachining process and embedded signal processing to make a functionally complete and low cost dual axis sensor.

The ADIS16201 is based upon a dual–axis micro-machined sensor element that develops independent analog signals representative of the acceleration levels applied to the part. The acceleration signals, along with the power supply voltage, an internal temperature signal and the auxiliary analog input signal are all sampled sequentially by an on-board precision ADC. These five signals are then processed and latched into output registers accessible to the user via the SPI.

In addition, the acceleration signals are further processed to produce inclination angle data for both axes. The inclination angle data represents the tilt away from the "ideal" plane that is normal to the earth's gravitational force. This calculation assumes that no force outside of the earth's gravitational force is acting on the device.

#### ACCELEROMETER OPERATION

The acceleration sensor used in the ADIS16201 is a surfacemachined, polysilicon structure built on top of a silicon wafer. Polysilicon springs suspend the structure over the surface of the wafer and provide a resistance against acceleration forces. Deflection of the structure is measured using a differential capacitor that consists of independent fixed plates and plates attached to the moving mass. The fixed plates are driven by a set of square waves that are 180° out-of-phase from one another. Acceleration will deflect the beam and unbalance the differential capacitor, resulting in an output square wave whose amplitude is proportional to acceleration. Phase sensitive demodulation techniques are then used to rectify the signal and determine the direction of the acceleration. The output of the demodulator is amplified, digitized, and further processed within the digital domain to remove any process variations and sensitivities to supply variations.

#### **INCLINOMETER OPERATION**

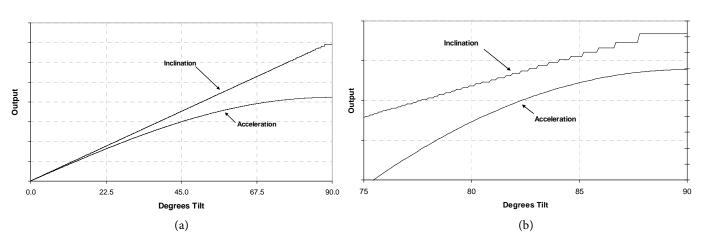

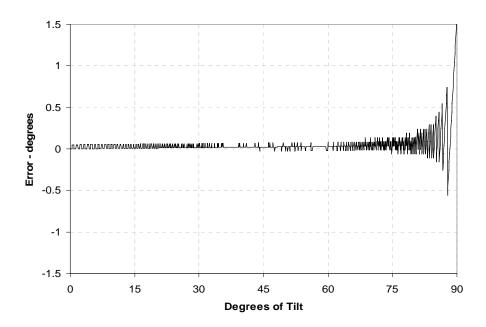

The ADIS16201 inclination angle output data is linear with respect to degrees of inclination. As the tilt angle increases, the accelerometer sensitivity reduces and eventually hits zero at the boundary condition of 90° inclination angle. In fact, this behavior can be described by using a simple sinusoidal function. This can be seen in Figure 4(a) where both the ideal inclination and acceleration output data are plotted over a span of 0° to +90° inclination. A closer examination of the plots within Figure 4(b) reveals an increase in quantization error as the inclination approaches +90°.

Since the inclination output is developed using a linear approximation of the acceleration data, the quantization error observed within the inclination output will grow as the inclination angle approaches 90°. It is suggested that the user limit the usable full scale range of the inclination outputs based upon the resolution required of the end target. Figure 5 provides a convenient guideline for use in determining the appropriate dynamic range vs. accuracy trade-off in each system design. The quantization error behavior described is symmetrical about the 0° point and should be applied equally to both positive and negative inclination angles

#### **TEMPERATURE SENSOR**

The TEMP\_OUT control register allows the end user to monitor the internal temperature of the ADIS16201 to an accuracy of +/- 3°C. The output data is presented in a straight binary format with a nominal 25°C die temperature correlating to 1278 LSB read through the TEMP\_OUT output data register. The sensitivity of -2.13LSB/°C allows for a resolution of less than 0.5°C in the temperature reading within the output data register.

Figure 4 – Acceleration and Inclination Angle Behavior versus Tilt Angle

Figure 5 – Inclination Quantization Error

### **BASIC OPERATION**

The ADIS16201 was designed for simple integration into industrial system designs, requiring only two things for acquisition of calibrated sensor data: a +3.3V power supply and a 4-wire, industry standard serial peripheral interface (SPI). All of the input/output functions on the ADIS16201 are facilitated by registers which can be accessed using the SPI interface. Each of these registers have been assigned a unique address and data format that has been tailored for their specific function. The SPI port operates in a full duplex mode; data is clocked out of the DOUT pin at the same time command/address data is being clocked in through the DIN pin. For more information on basic SPI port operation, see the Applications Section.

#### DATA OUTPUT REGISTER ACCESS

For the most basic operation of the ADIS16201, output data registers require only read commands for accessing calibrated sensor data, along with the temperature, power supply and auxiliary analog input channel data. Each read command requires two full 16-bit cycles. The first cycle is for transmitting the register address, and the second cycle is for reading of the data.

### **Preliminary Technical Data**

Table 5 displays these two cycles and their appropriate bit maps. The appropriate sequencing for each SPI signal (CS, SLCK, DIN and DOUT) during a read command can be found in Figure 6.

The data output register configuration is broken down into three different functions: new data ready bit (ND), alarm indicator (EA) and data bits (D0-D13). The ND bit is used to determine if a particular register has been updated since the last read command. As each register is updated, the data ready bit, referred to as ND in Table 5, is set to a "1" logic level. When a register is read, this bit is set to a "0" logic level. The alarm function provides users with a simple method for checking conditions and can be used to simplify system-level processing requirements.

The two acceleration output data registers are 14-bits in length and are formatted as two's complement binary numbers. The rest of the data output registers are 12 bits in length, leaving D12 and D13 as "don't care" bits. The output format for each of these registers, along with their addresses, can be found in Table 6. Each register function has two different addresses. The first address is for the upper byte, which contains the most significant bits (D8-D13), ND and EA data. The second address is for the lower byte, which contains the 8 least significant bits (D0-D7).

Figure 6 – Data Output Register Read Command Sequence

| Table 5 - Data Output Register Read Command Bit Map |            |    |     |     |     |     |    |    |    |    |    |      |        |    |    |    |

|-----------------------------------------------------|------------|----|-----|-----|-----|-----|----|----|----|----|----|------|--------|----|----|----|

| DIN                                                 | W/R        | 0  | A5  | A4  | A3  | A2  | A1 | A0 | х  | x  | x  | x    | x      | х  | x  | x  |

|                                                     |            |    |     |     |     |     |    |    |    |    |    |      |        |    |    |    |

| DOUT                                                | ND         | EA | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4   | D3     | D2 | D1 | D0 |

|                                                     | Upper Byte |    |     |     |     |     |    |    |    |    |    | Lowe | r Byte |    |    |    |

# Preliminary Technical Data

# ADIS16201

| Name       | Function                | Addresses | Resolution<br>(bits) | Data<br>Format | Scale Factor<br>(per LSB) | Output Code Examples                        |  |  |

|------------|-------------------------|-----------|----------------------|----------------|---------------------------|---------------------------------------------|--|--|

| SUPPLY_OUT | Power Supply Data       | 03h, 02h  | 12                   | Binary         | 1.22mV                    | 3.3V = 2703 LSB                             |  |  |

|            |                         |           |                      |                |                           | 0V = 0 LSB                                  |  |  |

| XACCL_OUT  | X-Axis Acceleration     | 05h, 04h  | 14                   | 2's            | 0.462mg                   | $\pm 1g = 8192 \pm 2162 \text{ LSB}$        |  |  |

|            | Data                    |           |                      | Compliment     |                           | 0g = 8192 LSB                               |  |  |

| YACCL_OUT  | Y-Axis Acceleration     | 07h, 06h  | 14                   | 2's            | 0.462mg                   | $\pm 1g = 8192 \pm 2162 \text{ LSB}$        |  |  |

|            | Data                    |           |                      | Compliment     |                           | 0g = 8192 LSB                               |  |  |

| AUX_ADC    | Auxiliary Analog Input  | 09h, 08h  | 12                   | Binary         | 0.61mV                    | 2.5V = 4095 LSB                             |  |  |

|            | Data                    |           |                      |                |                           | 0V = 0 LSB                                  |  |  |

| TEMP_OUT   | Sensor Temperature      | 0Bh, 0Ah  | 12                   | Binary         | -0.47°C                   | 0°C = 1331 LSB                              |  |  |

|            | Data                    |           |                      |                |                           | 25°C = 1278 LSB                             |  |  |

| XINCL_OUT  | X-Axis Inclination Data | 0Dh, 0Ch  | 12                   | 2's            | 0.1°                      | $\pm 90^{\circ} = 2048 \pm 900 \text{ LSB}$ |  |  |

|            |                         |           |                      | Compliment     |                           | 0° = 2048 LSB                               |  |  |

| YINCL_OUT  | Y-Axis Inclination Data | 0Fh, 0Eh  | 12                   | 2's            | 0.1°                      | $\pm 90^{\circ} = 2048 \pm 900 \text{ LSB}$ |  |  |

|            |                         |           |                      | Compliment     |                           | 0° = 2048 LSB                               |  |  |

#### Table 6 - Data Output Register Information

### **PROGRAMMING AND CONTROL**

#### **CONTROL REGISTER OVERVIEW**

The previous section described the most basic operation of the ADIS16201. For added system flexibility and programmability, the following sections describe additional Control of the ADIS16201 sensor, as provided for through the use of twenty eight digital control registers accessible via the SPI interface. A high level listing of these registers is given within Table 7. The functionality of each of these control registers is expanded upon in the following sections, providing for the full clarification of each of the control registers behavior. Available control modes for the device include selectable sample rates for the reading of the seven output vectors, selectable data averaging at the output registers, alarm settings, control of the on-board 12 bit auxiliary DAC, handling of the two general purpose I/O lines, facilitating of the sleep mode, enabling the self-test mode, as well as other miscellaneous control functions.

The conversion process is continually repeated, providing for the continuous update of the seven output registers. DATA READY flag bits common to all seven output registers allow the completion of the conversion process to be tracked via the SPI. As an alternative, the digital I/O lines can be configured through software control to create a DATA READY hardware function which in turn can signal the completion of the conversion process.

Dual alarms function are provided for within the ADIS16201 sensor with either of the alarms being able to monitor any one of the seven output registers independent of the other alarm. The alarms can be configured to monitor for excursions above or below fixed thresholds or for rates of change beyond predefined limits. The alarm conditions can be actively monitored through the SPI. In addition, the user can configure the digital I/O lines through software control to create an ALARM function that allows for monitoring of the alarm conditions through hardware.

The seven output signals noted above are all independently calibrated at the factory providing for a high degree of accuracy. In addition, the user has access to independent OFFSET and SCALE factors for each the two acceleration output vectors and the two inclination output vectors. This allows independent modification of any one or all of these four registers on an automatic basis prior to the values being read via the SPI. In turn, field level calibrations can be implemented within the sensor itself through the use of these OFFSET and SCALE variables. System level commands provided for within the sensor include the automatic zeroing of the four outputs through the use of a single NULL command via the SPI. In addition, the original factory calibration settings can be recovered at any point through the use of a simple factory reset command.

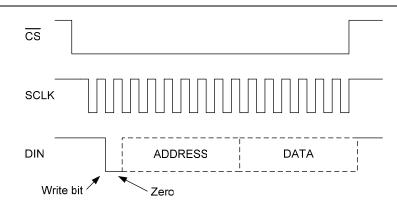

#### **CONTROL REGISTER ACCESS**

The control registers within the ADIS16201 are based upon a 16 bit / 2 byte format, and are accessed via the SPI. The SPI operates in full duplex mode with the data clocked out of the Data Out pin at the same time data is being clocked in through the Data In pin. All commands written to the ASIS16201 can be categorized as either Write commands or Read commands. All Write commands are self contained and take place within a single cycle; each Read command requires two cycles to complete. The first cycle is for transmitting the register address, and the second cycle is for reading of the data. During this second cycle, within which the Data Out line becomes active, the Data In line can be used to receive the next sequential command. This allows for the 'overlapping' of the commands. For more information on basic SPI port operation, see the Applications Section.

The READ and WRITE commands are identifiable through the Most Significant Bit (MSB), B15, of the received data. A "1" written to B15 indicates a Write command while a "0" indicates a Read command. Bits B13 through B8 contain the address of the control register that is being written to or read from. The remaining 8 bits of the Write command contain the data that is being written into the part whereas the remaining 8 bits of the Read command contain 'don't care' levels. Given that the data within the Write command is 8 bits in length, the 8 bit data format is the default byte size. A Write command operates on a single cycle as defined by the chip select, and shown in Figure 7. The Read command operates on a 2 chip select cycle basis as seen in the previous section, Figure 6. The 6 bit address range allows for the addressing of the full 64 byte address space on a byte-wise basis as detailed in Table 5, 6, 7 and 8. Data written into the device is performed on a byte-wise basis with the address of each byte being explicitly called out in the write command. Conversely, data being read from the device consists of two back-to-back 8 byte variables being sent out with the first byte out corresponding to the upper address (odd number address) and the second byte relating to the next lower address space (even number address). For example, a data read of address 03h would result in the data from address 03h being fed out followed by data from address 02h. Likewise, a data read of address 02h will result in the same data stream being output from the device

The ADIS16201 is a FLASH based device with the non-volatile functional registers implemented as FLASH registers. The

### **Preliminary Technical Data**

## ADIS16201

endurance limitation of 20,000 writes should be taken into account when considering the implementation of the device into the end target. The "Non-Volatile" column called out within Table 7 is helpful in discerning which control register writes must be counted against the Endurance limit, along with the expected update rate. When writing to a non-volatile register, the user needs to assure that the power supply remains within limits for a minimum of 200 msec after the write is initiated. This will assure a successful write of the non-volatile data.

Table 7. Control Regsiter Mapping

| Register Name | Туре | Non-<br>Volatile | Address | Bytes | Function                                                 |

|---------------|------|------------------|---------|-------|----------------------------------------------------------|

|               |      |                  | 00h-01h | 2     | Reserved                                                 |

| SUPPLY_OUT    | R    |                  | 02h     | 2     | Power Supply output data.                                |

| XACCL_OUT     | R    |                  | 04h     | 2     | X-Axis Acceleration output data.                         |

| YACCL_OUT     | R    |                  | 06h     | 2     | Y-Axis Acceleration output data.                         |

| AUX_ADC       | R    |                  | 08h     | 2     | Auxiliary ADC Data                                       |

| TEMP_OUT      | R    |                  | 0Ah     | 2     | Temperature output data                                  |

| XINCL_OUT     | R    |                  | 0Ch     | 2     | X-Axis Inclination output data.                          |

| YINCL_OUT     | R    |                  | 0Eh     | 2     | Y-Axis Inclination output data.                          |

| XACCL_OFF     | R/W  | Х                | 10h     | 2     | X-Axis Acceleration Null Factor.                         |

| YACCL_OFF     | R/W  | Х                | 12h     | 2     | Y-Axis Acceleration Null Factor.                         |

| XACCL_SCALE   | R/W  | Х                | 14h     | 2     | X-Axis Acceleration Scale Factor.                        |

| YACCL_SCALE   | R/W  | Х                | 16h     | 2     | Y-Axis Acceleration Scale Factor.                        |

| XINCL_OFF     | R/W  | Х                | 18h     | 2     | X-Axis Inclination Null Factor.                          |

| YINCL_OFF     | R/W  | Х                | 1Ah     | 2     | Y-Axis Inclination Null Factor.                          |

| XINCL_SCALE   | R/W  | Х                | 1Ch     | 2     | X-Axis Inclination Scale Factor.                         |

| YINCL_SCALE   | R/W  | Х                | 1Eh     | 2     | Y-Axis Inclination Scale Factor.                         |

| ALM_MAG1      | R/W  | Х                | 20h     | 2     | Alarm 1 Amplitude Threshold.                             |

| ALM_MAG2      | R/W  | Х                | 22h     | 2     | Alarm 2 Amplitude Threshold.                             |

| ALM_SMPL1     | R/W  | Х                | 24h     | 2     | Alarm 1 Sample Period.                                   |

| ALM_SMPL2     | R/W  | Х                | 26h     | 2     | Alarm 2 Sample Period.                                   |

| ALM_CTRL      | R/W  | Х                | 28h     | 2     | Alarm Source Control Register                            |

|               |      |                  | 2Ah-2Fh | 6     | Reserved                                                 |

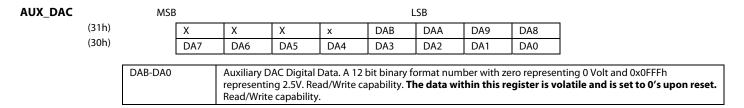

| AUX_DAC       | R/W  |                  | 30h     | 2     | Auxiliary DAC Data.                                      |

| GPIO_CTRL     | R/W  |                  | 32h     | 2     | Auxiliary Digital I/O Control Register.                  |

| MSC_CTRL      | R/W  |                  | 34h     | 2     | Miscellaneous Control Register.                          |

| SMPL_PRD      | R/W  | Х                | 36h     | 2     | ADC Sample Period Control.                               |

| AVG_CNT       | R/W  | х                | 38h     | 2     | Defines number of samples used by moving average filter. |

| PWR_MDE       | R/W  |                  | 3Ah     | 2     | Counter used to determine length of Power-Down mode.     |

| STATUS        | R    |                  | 3Ch     | 2     | System Status Register.                                  |

| COMMAND       | W    |                  | 3Eh     | 2     | System Command Register.                                 |

#### Figure 7 – Control Register Write Command Sequence of SPI Signals

#### Table 8 - Data Output Register Write Command Bit Map

| DIN | W/R | 0 | A5 | A4   | A3     | A2 | A1 | A0 | D7 | D6 | D5 | D4   | D3     | D2 | D1 | D0 |

|-----|-----|---|----|------|--------|----|----|----|----|----|----|------|--------|----|----|----|

|     |     |   |    | Uppe | r Byte |    |    |    |    |    |    | Lowe | r Byte |    |    |    |

### **CONTROL REGISTER DETAILS**

#### CALIBRATION

The ADIS16201 outputs are pre-calibrated at the factory, providing a high degree of accuracy and simpler system implementation. In addition, for system or field updates, the device has eight control registers associated with calibration updates of the acceleration and inclination output data, as defined in Table 9 below. Each of the registers has a read/write capability and is 16 bits/2bytes in length. All calibration registers contain 12 bit data with the exception of the Inclination Offset registers which contain 9 bit data. All data values are aligned to the LSB. The OFFSET registers all utilize the 2's complement format allowing for both positive and negative offsets. All SCALE registers utilize the straight binary format.

The data within these eight calibration registers is utilized in offsetting and scaling of the output data registers according to:

$$Output = A * (x + C)$$

where *x* represents the raw data prior to calibration, C is the offset, A is the scalar, and *Output* represents the Output Data register where the resultant data is stored. Each of the X and Y axis acceleration output data registers as well as the X and Y axis inclination output data registers is associated with an independent OFFSET and SCALE register for a total of four OFFSET registers and a total of four SCALE registers.

One of the primary functions of the various OFFSET and SCALE registers is to allow for the field level calibration of the ADIS16201 sensor. In particular, the OFFSET control registers allow the end user to reset to 0deg / 0mg reference point for the device. This is particularly important when considering the stack up of the tolerances in mounting the ADIS16201 to a Printed Circuit Board (PCB), the PCB to an enclosure, the enclosure mounted to the chassis of a piece of equipment, etc.... The end result is that the ADIS16201 mechanical reference may be offset several degrees from that of the end equipment mechanical reference resulting in serious offsets in the inclination and acceleration data output registers. Loading of the OFFSET registers with correction data can eliminate such errors.

A global command has been implemented within the ADIS16201 to simplify the loading of the OFFSETs. Once the end piece of equipment is leveled to its desired reference point a NULL command can be sent to the ADIS16201 via the COMMAND control register which will zero the two acceleration and the two inclination output data registers through the automatic loading of the four OFFSET registers with the inverse of the data presently located within the corresponding four output data registers (within range limits). Consequently, on the next reading of the seven output data registers the two acceleration and two inclination output data registers should be reset to mid-scale (neglecting noise and repeatability limitations). It is suggested that when the NULL command is to be implemented that the AVG\_CNT control register be set to 08h in order to maximize the filtering and reduce the effects of noise in determining the values to be loaded into the OFFSET control registers. Then again, the user may prefer to manually load each of the eight calibration registers via the SPI in order to calibrate the end system. This could be applicable when it is planned to adjust the SCALE factors thus requiring an external stimulus to excite the ADIS16201.

| XACCL_OFF | MSB        |      |                                            |                                              |                                          | l                                 | SB                                                 |                          |                            |                                                                                                                                             |

|-----------|------------|------|--------------------------------------------|----------------------------------------------|------------------------------------------|-----------------------------------|----------------------------------------------------|--------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| (11h)     |            | Х    | Х                                          | х                                            | х                                        | XANB                              | XANA                                               | XAN9                     | XAN8                       | ]                                                                                                                                           |

| (10h)     |            | XAN7 | XAN6                                       | XAN5                                         | XAN4                                     | XAN3                              | XAN2                                               | XAN1                     | XAN0                       | 1                                                                                                                                           |

|           | XANB-XA    | NO   | prior to Sc<br>zero offset<br>offset of +, | ale Factor r<br>t. Offset fac<br>/-0.945g as | nultiplicati<br>tor can be<br>suming the | on. <b>The reg</b><br>varied from | <b>jister is set</b><br>-2048 to +2<br>ominal SCAI | to 0 upon<br>2047. Resol | initial pow<br>ution equal | nat number added directly to data<br>ver-up resulting in an effective<br>Is 0.462mg/LSB for a maximum<br>value is non-volatile allowing for |

| YACCL_OFF | MSB<br>3h) | x    | X                                          | x                                            | x                                        | YANB                              | LSB<br>YANA                                        | YAN9                     | YAN8                       | 1                                                                                                                                           |

| (1        | 2h)        | YAN7 | YAN6                                       | YAN5                                         | YAN4                                     | YAN3                              | YAN2                                               | YAN1                     | YAN0                       | ]                                                                                                                                           |

#### **Table 9. Calibration Register Definitions**

| ADIS16201                    |                  |           |                                                                 |                                                             |                                                              |                                                                    |                                                                   | P                                                         | Prelimi                                            | nary Technical Dat                                                                                                                                                                |

|------------------------------|------------------|-----------|-----------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | YANB-YAN         | N0o       | prior to Sc<br>zero offset<br>offset of +                       | ale Factor r<br>t. Offset fac                               | nultiplication<br>tor can be w<br>suming the                 | on. <b>The reg</b><br>varied from<br>use of a no                   | <b>gister is se</b> t<br>-2048 to +<br>ominal SCA                 | <b>t to 0 upon</b><br>2047. Reso                          | <b>initial pov</b><br>lution equa                  | nat number added directly to dat<br><b>ver-up</b> resulting in an effective<br>Is 0.462mg/LSB for a maximum<br>value is non-volatile allowing for                                 |

| ACCL_SCALE                   | MS               | В         |                                                                 |                                                             |                                                              |                                                                    | LSB                                                               |                                                           |                                                    |                                                                                                                                                                                   |

|                              | 15h)             | х         | х                                                               | х                                                           | x                                                            | XASB                                                               | XASA                                                              | XAS9                                                      | XAS8                                               |                                                                                                                                                                                   |

| (                            | 14h)             | XAS7      | XAS6                                                            | XAS5                                                        | XAS4                                                         | XAS3                                                               | XAS2                                                              | XAS1                                                      | XAS0                                               | ]                                                                                                                                                                                 |

|                              | XASB-XAS         | 60        | <b>resulting</b><br>with 0.05%                                  | <b>in a unity g</b><br>6 resolutior                         | <b>gain scalar</b><br>n. Last writt                          | . Can be va<br>en value is                                         | ried from 0<br>non-volatil                                        | to 4095 co                                                | rrelating to<br>for data rec                       | 8 upon initial power-up<br>scale factor of 0 to 2 respectivel<br>covery upon reset. The full scale                                                                                |

| ACCL_SCALE                   | MS               | В         |                                                                 |                                                             |                                                              | l                                                                  | LSB                                                               |                                                           |                                                    |                                                                                                                                                                                   |

| (17h)                        |                  | х         | x                                                               | x                                                           | x                                                            | YASB                                                               | YASA                                                              | YAS9                                                      | YAS8                                               |                                                                                                                                                                                   |

| (16h)                        |                  | YAS7      | YAS6                                                            | YAS5                                                        | YAS4                                                         | YAS3                                                               | YAS2                                                              | YAS1                                                      | YAS0                                               |                                                                                                                                                                                   |

|                              | YASB-YAS         | 0         | <b>in a unity</b><br>resolution                                 | gain scala                                                  | r. Can be va<br>en value is r                                | aried from (<br>non-volatile                                       | 0 to 4095 co<br>e allowing f                                      | orrelating to<br>for data rec                             | o scale facto                                      | <b>8 upon initial power-up result</b><br>or of 0 to 2 respectively with 0.0<br>reset. The full scale range limits                                                                 |

| INCL_OFF                     | MSB              |           |                                                                 |                                                             |                                                              | l                                                                  | LSB                                                               |                                                           |                                                    |                                                                                                                                                                                   |

| (19h)                        |                  | х         | х                                                               | х                                                           | х                                                            | х                                                                  | Х                                                                 | Х                                                         | XIN8                                               |                                                                                                                                                                                   |

| (18h)                        |                  | XIN7      | XIN6                                                            | XIN5                                                        | XIN4                                                         | XIN3                                                               | XIN2                                                              | XIN1                                                      | XIN0                                               |                                                                                                                                                                                   |

|                              |                  |           | zero offset<br>of +/-25.50<br>recovery u                        | t. Offset fac<br>deg assumi                                 | tor can be v<br>ng the use<br>The full sca                   | varied from<br>of a nomin<br>le range lin                          | -256 to +2<br>al SCALE fa<br>nits of +/- 9                        | 55. Resolut                                               | ion equals (<br>ritten value                       | <b>ver-up</b> resulting in an effective<br>0.1deg/LSB for a maximum offse<br>e is non-volatile allowing for data<br>data register will be shifted                                 |

| INCL_OFF                     | MSB              |           |                                                                 |                                                             |                                                              |                                                                    | LSB                                                               |                                                           |                                                    |                                                                                                                                                                                   |

| (1Bh)                        |                  | х         | х                                                               | х                                                           | х                                                            | х                                                                  | Х                                                                 | Х                                                         | YIN8                                               |                                                                                                                                                                                   |

| (1Ah)                        |                  | YIN7      | YIN6                                                            | YIN5                                                        | YIN4                                                         | YIN3                                                               | YIN2                                                              | YIN1                                                      | YIN0                                               |                                                                                                                                                                                   |

|                              | YIN8- YIN0       | D         | prior to Sc<br>zero offset<br>of +/-25.50<br>recovery u         | ale Factor r<br>t. Offset fac<br>deg assumi                 | nultiplication<br>tor can be wing the use<br>The full sca    | on. <b>The reg</b><br>/aried from<br>of a nomin<br>le range lin    | <b>gister is se</b><br>-256 to +2<br>al SCALE fa<br>nits of +/- 9 | <b>t to 0 upon</b><br>55. Resolut<br>ictor. Last w        | i <b>nitial pov</b><br>ion equals<br>vritten value | number added directly to data<br><b>ver-up</b> resulting in an effective<br>0.1deg/LSB for a maximum offse<br>e is non-volatile allowing for dat<br>data register will be shifted |

|                              | MSE              | 3         |                                                                 |                                                             |                                                              |                                                                    | LSB                                                               |                                                           |                                                    |                                                                                                                                                                                   |

| INCL SCALE                   |                  |           | x                                                               | x                                                           | x                                                            | XISB                                                               | XISA                                                              | XIS9                                                      | XIS8                                               |                                                                                                                                                                                   |

| INCL_SCALE<br>(1Dh)          |                  | х         |                                                                 |                                                             |                                                              | 1                                                                  | 1                                                                 |                                                           |                                                    | 1                                                                                                                                                                                 |

|                              |                  | x<br>XIS7 | XIS6                                                            | XIS5                                                        | XIS4                                                         | XIS3                                                               | XIS2                                                              | XIS1                                                      | XIS0                                               |                                                                                                                                                                                   |

| (1Dh)                        | XISB-XIS0        | XIS7      | XIS6<br>Scale factor<br>in a unity<br>resolution                | or for X-Axis<br><b>gain scala</b>                          | Inclination<br>r. Can be va<br>en value is r                 | n Output. <b>T</b><br>aried from (<br>non-volatile                 | <b>he 12 bit r</b><br>0 to 4095 co<br>e allowing f                | <b>egister is s</b><br>orrelating to<br>for data rec      | et to 2048<br>o scale facto                        | or of 0 to 2 respectively with 0.0                                                                                                                                                |

| (1Dh)<br>(1Ch)               |                  | XIS7      | XIS6<br>Scale factor<br>in a unity<br>resolution                | or for X-Axis<br><b>gain scala</b><br>. Last writte         | Inclination<br>r. Can be va<br>en value is r                 | n Output. <b>T</b><br>aried from (<br>non-volatile<br>actor. Read  | <b>he 12 bit r</b><br>0 to 4095 co<br>e allowing f<br>I/Write cap | <b>egister is s</b><br>orrelating to<br>for data rec      | et to 2048<br>o scale facto                        | or of 0 to 2 respectively with 0.0                                                                                                                                                |

| (1Dh)<br>(1Ch)               | XISB-XISO<br>MSE | XIS7      | XIS6<br>Scale factor<br>in a unity<br>resolution                | or for X-Axis<br><b>gain scala</b><br>. Last writte         | Inclination<br>r. Can be va<br>en value is r                 | n Output. <b>T</b><br>aried from (<br>non-volatile<br>actor. Read  | <b>he 12 bit r</b><br>0 to 4095 co<br>e allowing f                | <b>egister is s</b><br>orrelating to<br>for data rec      | et to 2048<br>o scale facto                        | or of 0 to 2 respectively with 0.05                                                                                                                                               |

| (1Dh)<br>(1Ch)<br>INCL_SCALE |                  | XIS7      | XIS6<br>Scale factor<br>in a unity<br>resolution<br>will vary a | or for X-Axis<br>gain scala<br>. Last writte<br>ccording to | Inclination<br>r. Can be va<br>en value is r<br>this scale f | n Output. <b>T</b><br>aried from (<br>non-volatile<br>factor. Read | <b>he 12 bit r</b><br>0 to 4095 co<br>e allowing f<br>I/Write cap | egister is s<br>orrelating to<br>for data rec<br>ability. | et to 2048<br>o scale facto<br>overy upon          | upon initial power-up resultin<br>or of 0 to 2 respectively with 0.0!<br>reset. The full scale range limits                                                                       |

### **Preliminary Technical Data**

will vary according to this scale factor. Read/Write capability.

#### **ALARM PROGRAMMING**

The ADIS16201 contains two independent alarm functions which are referred to as Alarm1 and Alarm 2. The control registers relating to these two alarm functions are defined in Table 10 below. The Alarm 1 function is managed by the ALM\_MAG1 and ALM\_SMPL1 control registers, and the Alarm 2 function is managed by the ALM\_MAG2 and ALM\_SMPL2 control registers. Both the Alarm 1 and Alarm 2 functions share the ALM\_CNTRL register. The discussion that follows references the Alarm 1 functionality only, for simplicity.

The 16 bit ALM\_CNTRL register serves three distinct roles in controlling the Alarm 1 function. First it is used to enable the overall Alarm 1 function and select the output data variable that is to be monitored for the alarm condition. Second it is used to select whether the Alarm 1 function is to based upon a predefined Threshold (THR) level or a predefined Rate-Of-Change (ROC) slope. Last the ALM\_CNTRL register can be used in setting up one of the two General Purpose Input/Output lines (GPIO) to serve as a hardware output that indicates when an alarm condition has occurred. The enabling of the alarm hardware function as well as the control of the actual I/O line to place the alarm function on as well as the polarity of the active alarm signal is controlled through this register. Note the hardware output indicator when enabled serves both the Alarm 1 and Alarm 2 functions and cannot be used to differentiate between one alarm condition or the other. It is simply used to indicate that an alarm is active and that the user should poll the device via the SPI to discern which alarm is the source of the alarm condition (see STATUS control register definition).

With the ALM\_CTRL, MSC\_CTRL and GPIO\_CTRL control registers all being able to influence the same GPIO pins a priority level must be established for conflicting assignments of the two GPIO pins. This priority level is defined as: MSC\_CTRL has precedence over ALM\_CTRL which has precedence over GPIO\_CTRL.

The ALM\_MAG1 control register used in controlling the Alarm 1 function has two roles. The first is to store the value with which the output data variable will be compared against to discern if an alarm condition exists or not. The second is to identify whether the alarm should be active for excursions above or below the alarm limit. For a "1" in the GT1 bit of the ALM\_MAG1 control register the alarm will be active for excursions extending above a given limit. For a "0" in the GT1 bit the alarm will be active for excursions dropping below the given limit. The comparison value contained within the ALM\_MAG1 control register is located within the lower 14 bits. The format utilized for this 14 bit value should match that of the output data register that is being monitored for the alarm condition. For instance, if the YINCL\_OUT output data register is being monitored by Alarm 1 then the 14 bit value within the ALM\_MAG1 control register will take on a 2's complement format with each LSB equating to nominal 0.1deg (assumes unity SCALE and zero OFFSET factors). The ALM\_MAG value is compared against the instantaneous value of the parameter being monitored and not the filtered output data.

When the THR function is enabled the output data variable is compared against the ALM\_MAG1 level in a one for one manner. When the ROC function is enabled the comparison of the output data variable is against the ALM\_MAG1 level averaged over the number of samples as identified in the ALM\_SMPL1 control register. This acts to create a comparison of ( $\Delta$  units /  $\Delta$  time) or the derivative of the output data variable against a predefined slope.

The versatility built into the alarm function is intended to allow for an end user to adapt to any one of a number of different applications. For example, in the case of monitoring a 2's complement variable the 'GT1' bit within the ALM\_MAG1 control register can allow for the detection of negative excursions below a fixed level. In addition, the Alarm 1 and the Alarm 2 functions can be set to monitor the same variable which allows for the end user to discern if an output variable remains within a predefined window. Other options include the ROC function which can be used in the monitoring of high frequency shock levels in the acceleration outputs or slowly changing outputs in the inclination level over a period of a minute or more. With the addition of the alarm hardware functionality the ADIS16201 can be left to run independently of the main processor and only interrupt the system when an alarm condition occurs. Conversely, the alarm condition can be monitored through the routine polling of any one of the seven data output registers

### **Preliminary Technical Data**

#### Table 10. ALARM Register Definitions

#### ALM\_MAG1 MSB LSB (21h) GT1 M1D M1C M1B M1A M19 M18 Х (20h) M17 M16 M15 M14 M13 M12 M11 M10 Alarm Magnitude 1 register is non-volatile. Reset to 0 @ initial power-up. Read/Write capability. BIT DESCRIPTION GT1 "Greater Than" active alarm bit; 1 – Alarm active for output 'Greater Than' Alarm Magnitude 1 register setting. 0 - Alarm active for output 'Less Than' Alarm Magnitude 1 register setting. M1D - M10 Alarm 1 Magnitude Threshold, 14 Bits are provided for the setting of the threshold. The number can be either straight binary or 2's complement depending upon the format of the output variable that the alarm threshold is being compared against. ALM\_MAG2 MSB LSB (23h) GT2 M2D M2C M2B M2A M29 M28 х (22h) M27 M26 M25 M24 M23 M22 M21 M20 Alarm Magnitude 2 register is non-volatile. Reset to 0 @ initial power-up. Read/Write capability. DESCRIPTION BIT GT2 "Greater Than" active alarm bit; 1 – Alarm active for output 'Greater Than' Alarm Magnitude 2register setting. 0 - Alarm active for output 'Less Than' Alarm Magnitude 2 register setting. Alarm 2 Magnitude Threshold. 14 Bits are provided for the setting of the threshold. The number can be either M2D - M20 straight binary or 2's complement depending upon the format of the output variable that the alarm threshold is being compared against. ALM\_SMPL1 MSB LSB (25h) Х х Х х х Х х Х (24h) T17 T16 T15 T14 T13 T12 T11 T10 T17- T10 Alarm 1 Sample Period. This binary value represents the number of samples that an Output Variable is monitored over when performing Rate-of-Change alarm monitoring. The Rate-of-Change alarm function averages the change in the output variable over the specified number of samples and compares this change directly to the values specified in the Alarm Magnitude 1 register. Last written value is stored in non-volatile memory allowing for data recovery upon reset. Reset to 0 @ initial power-up. Read/Write capability. ALM\_SMPL2 MSB LSB (27h) Х Х Х х х х х х (26h) T26 T25 T27 T24 T23 T22 T21 T20 T27- T20 Alarm 2 Sample Period. This binary value represents the number of samples that an Output Variable is monitored over when performing Rate-of-Change alarm monitoring. The Rate-of-Change alarm function averages the change in the output variable over the specified number of samples and compares this change directly to the values specified in the Alarm Magnitude 2 register. Last written value is stored in non-volatile memory allowing for data recovery upon reset. Reset to 0's @ initial power-up. Read/Write capability.

# Preliminary Technical Data

# ADIS16201

| ALM_CTRL |       | MSB                 |                                                                                                                                                                   |                |             |               | L            | SB                     |            |            |  |  |

|----------|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|---------------|--------------|------------------------|------------|------------|--|--|

|          | (29h) |                     | ROC2                                                                                                                                                              | A2S_2          | A2S_1       | A2S_0         | ROC1         | A1S_2                  | A1S_1      | A1S_0      |  |  |

|          | (28h) |                     | х                                                                                                                                                                 | Х              | х           | х             | Х            | AOE                    | AOP        | AOL        |  |  |

|          |       | Alarm Mac           | nitude 1                                                                                                                                                          | register is no | on-volatile | Reset to 0    | @ initial r  | ower-up                | Read/Write | canability |  |  |

|          |       | BIT                 | larm Magnitude 1 register is non-volatile. <b>Reset to 0</b> @ initial power-up. Read/Write capability. IT DESCRIPTION                                            |                |             |               |              |                        |            |            |  |  |

|          |       | ROC1, ROC           |                                                                                                                                                                   |                |             |               |              |                        |            |            |  |  |

|          |       | A1S_2, A1<br>A1S_0, | IS_2, A1S_1, Alarm 1 and Alarm 2 Source Selects. Represents a 3 digit binary address enabling and selecting the output variable which is the source of the Alarm. |                |             |               |              |                        |            |            |  |  |