#### 捷多邦,专业PCB打样工厂,24小时加急出货

## 查询LTC4260IUH供应商 LINGAR TECHNOLOGY

### LTC4261

Negative Voltage Hot Swap Controller with ADC and I<sup>2</sup>C Monitoring

### DESCRIPTION

The LTC<sup>®</sup>4261 negative voltage Hot Swap<sup>™</sup> controller allows a board to be safely inserted and removed from a live backplane. Using an external N-channel pass transistor, the board supply voltage can be ramped at an adjustable rate. The device features independently adjustable inrush current and overcurrent limits to minimize stresses on the pass transistor during start-up, input step and output short conditions.

An I<sup>2</sup>C interface and onboard 10-bit ADC allow monitoring of board current, voltage and fault status. A single-wire broadcast mode is available to simplify the interface by eliminating two optoisolators.

The controller has additional features to interrupt the host when a fault has occurred, notify when output power is good, detect insertion of a board and turn off the pass transistor if an external supply monitor fails to indicate power good within a timeout period.

LTC and LT are registered trademarks of Linear Technology Corporation. Hot Swap is a trademark of Linear Technology Corporation. Patents pending. All other trademarks are the property of their respective owners.

#### -48V/200W Hot Swap Controller with I<sup>2</sup>C and ADC -48V RTN 4× 1k IN SERIES **Start-Up Behavior ≹**453k 1/4W FACH GATE VIN UV = 38.5V UVL PGI 10V/DIV UV RELEASE UVH **≯**16.9k AL FR AT 43V 1% ADIN2 **SDAO** 0V = 72.3V ٥V SDAI 1TC4261CGN 330µF V<sub>OUT</sub> 50V/DIV VIN OV RELEASE **INTV<sub>CC</sub>** SCI 100V AT 71V ON ADIN LOAD PGIO PG ŌŇ TMR EN VEF GATE DRAIN RAMP **\$**11.8k SS SENSE SENSE VIN **≦**1k **€**1M 1A/DIV 47nF 100 220nF 1ul 10nF PG 0.1µF 47nF 100V 0.0080 5% 50V/DIV 1% Vout 4261 TA01b 20ms/DIV Q1 IRF1310NS

### FEATURES

- Allows Safe Insertion into Live –48V Backplanes

- 10-Bit ADC Monitors Current and Voltages

- I<sup>2</sup>C/SMBus Interface or Single-Wire Broadcast Mode

- Wide Operating Voltage Range: -12V to -100V

- Independently Adjustable Inrush and Overcurrent Limits

- Controlled Soft-Start Inrush

- Adjustable UV/OV Thresholds and Hysteresis

- Sequenced Power Good Outputs with Delays

- Adjustable Power Good Input Timeout

- Programmable Latchoff or Auto-Retry After Faults

- Alerts Host After Faults

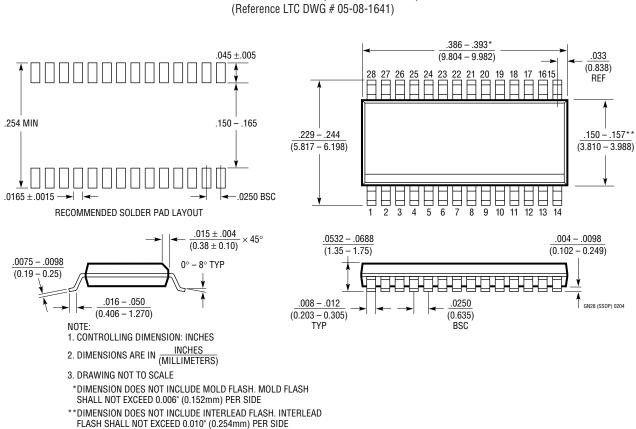

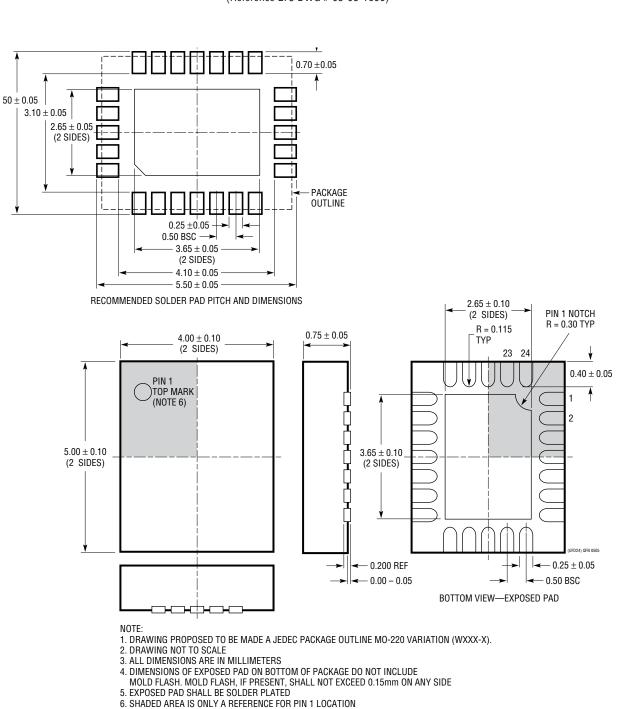

- Available in 28-Lead Narrow SSOP and 24-Lead (4mm × 5mm) QFN Packages

### APPLICATIONS

- AdvancedTCA Systems

- Telecom Infrastructure

- –48V Distributed Power Systems

- Power Monitors

dzsc.com

## TYPICAL APPLICATION

### ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| V <sub>IN</sub> (Note 3)             | -0.3V to 10.65V                |

|--------------------------------------|--------------------------------|

| Drain (Note 4)                       | 0.3V to 3.5V                   |

| PGI, ON, ALERT, SDAO, SDAI, SCL, AD  | IN, ADIN2,                     |

| OV, SENSE, ADR1, ADR0, FLTIN, TMR,   |                                |

| SS, RAMP Voltages0.3V                | to INTV <sub>CC</sub> + 0.3V   |

| UVL, UVH, EN                         | –0.3V to 10V                   |

| GATE Voltage –C                      | ).3V to V <sub>IN</sub> + 0.3V |

| PG, PGIO Voltages                    | 0.3V to 100V                   |

| Supply Voltage (INTV <sub>CC</sub> ) | 0.3V to 5.5V                   |

| Operating Temperature Range          |                |

|--------------------------------------|----------------|

| LTC4261C                             | 0°C to 70°C    |

| LTC42611                             | –40°C to 85°C  |

| Storage Temperature Range            |                |

| SSOP                                 | –65°C to 150°C |

| QFN                                  | –65°C to 125°C |

| Lead Temperature (Soldering, 10 sec) |                |

| SSOP Only                            | 300°C          |

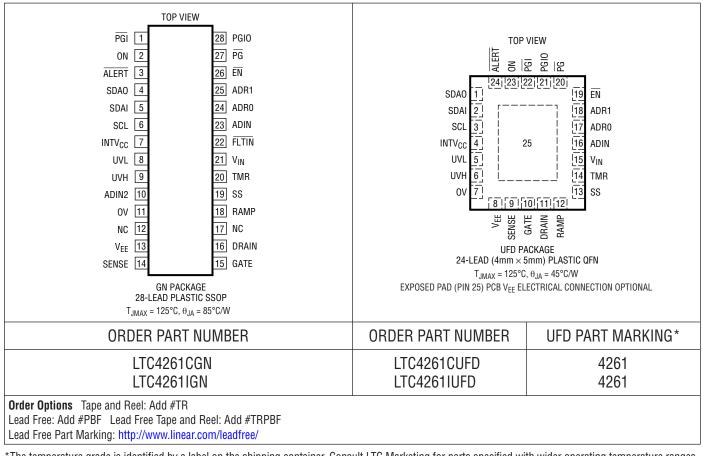

### PACKAGE/ORDER INFORMATION

\*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at I<sub>IN</sub> = 5mA, T<sub>A</sub> = 25°C. (Note 2)

| SYMBOL                   | PARAMETER                                                | CONDITIONS                                     |                                                       |      | MIN            | ТҮР            | MAX            | UNITS |

|--------------------------|----------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|------|----------------|----------------|----------------|-------|

| General                  | 1                                                        | I.                                             |                                                       |      | 1              |                |                | L     |

| VZ                       | Shunt Regulator Voltage at V <sub>IN</sub>               | I <sub>IN</sub> = 5mA                          |                                                       |      | 10.65          | 11.2           | 11.8           | V     |

| ΔVZ                      | Shunt Regulator Load Regulation                          | I <sub>IN</sub> = 5mA to 25mA                  |                                                       | •    |                | 370            | 600            | mV    |

| I <sub>IN</sub>          | V <sub>IN</sub> Supply Current                           | $V_{IN} = V_Z - 0.3V$                          |                                                       | •    |                | 2              | 5              | mA    |

| V <sub>IN(UVLO)</sub>    | V <sub>IN</sub> Undervoltage Lockout Threshold           | V <sub>IN</sub> Rising                         |                                                       | •    | 8.5            | 9              | 9.5            | V     |

| $\Delta V_{IN(UVLO)}$    | V <sub>IN</sub> Undervoltage Lockout Hysteresis          |                                                |                                                       | ٠    | 0.3            | 0.7            | 1              | V     |

| INTV <sub>CC</sub>       | Internal Regulator Voltage                               | I <sub>LOAD</sub> = 1mA to 20n                 | nA, I <sub>IN</sub> = 25mA                            | •    | 4.75           | 5              | 5.25           | V     |

| Gate Drive               |                                                          | 1                                              |                                                       |      |                |                |                |       |

| V <sub>GATEH</sub>       | GATE Pin Output High Voltage                             | V <sub>IN</sub> = 10.65V                       |                                                       | •    | 10             | 10.25          | 10.5           | V     |

| I <sub>GATE(UP)</sub>    | GATE Pin Pull-Up Current                                 | V <sub>GATE</sub> = 4V                         |                                                       | •    | -7.5           | -11.5          | -15.5          | μA    |

| I <sub>GATE(OFF)</sub>   | GATE Turn-Off Current                                    | V <sub>SENSE</sub> = 300mV, V                  | <sub>GATE</sub> = 4V                                  | •    | 60             | 110            | 140            | mA    |

| ( )                      |                                                          | Gate Off, V <sub>GATE</sub> = 4                | V                                                     | •    | 60             | 110            | 140            | mA    |

| t <sub>PHL(SENSE)</sub>  | SENSE High to Current Limit                              | V <sub>SENSE</sub> = 100mV, C                  | <sub>GATE</sub> = 1pF                                 | •    |                | 0.5            | 1.5            | μs    |

|                          | Propagation Delay                                        | V <sub>SENSE</sub> = 300mV, C                  | <sub>GATE</sub> = 1pF                                 | •    |                | 0.2            | 0.5            | μs    |

| t <sub>PHL(GATE)</sub>   | GATE Off Propagation Delay                               | Input High (OV, EN,<br>C <sub>GATE</sub> = 1pF | •                                                     |      | 0.2            | 0.5            | μs             |       |

| t <sub>PHLCB</sub>       | Circuit Breaker Gate Off Delay                           | $V_{GATE} < 2V, C_{GATE} =$                    | •                                                     | 440  | 530            | 620            | μs             |       |

| I <sub>RAMP</sub>        | RAMP Pin Current                                         | V <sub>SS</sub> = 2.56V                        | •                                                     | -18  | -20            | -22            | μA             |       |

| V <sub>SS</sub>          | SS Pin Clamp Voltage                                     |                                                | •                                                     | 2.43 | 2.56           | 2.69           | V              |       |

| I <sub>SS(UP)</sub>      | SS Pin Pull-Up Current                                   | $V_{SS} = 0V$                                  |                                                       | •    | -7             | -10            | -13            | μA    |

| I <sub>SS(DN)</sub>      | SS Pin Pull-Down Current                                 | V <sub>SS</sub> = 2.56V                        |                                                       | •    | 6              | 12             | 20             | mA    |

| Input Pins               |                                                          | I.                                             |                                                       |      |                |                |                |       |

| V <sub>UVH(TH)</sub>     | UVH Threshold Voltage                                    | V <sub>UVH</sub> Rising                        | LTC4261C<br>LTC42611                                  | •    | 2.528<br>2.514 | 2.56<br>2.56   | 2.592<br>2.606 | V     |

| V <sub>UVL(TH)</sub>     | UVL Threshold Voltage                                    | V <sub>UVL</sub> Falling                       | LTC4261C<br>LTC42611                                  | •    | 2.262<br>2.250 | 2.291<br>2.291 | 2.320<br>2.332 | V     |

| $\Delta V_{UV(HYST)}$    | Built-In UV Hystersis                                    | UVH and UVL Tied                               | Together                                              |      | 256            | 269            | 282            | mV    |

| δV <sub>UV</sub>         | UVH, UVL Minimum Hysteresis                              |                                                |                                                       |      |                | 15             |                | mV    |

| V <sub>UVLR(TH)</sub>    | UVL Reset Threshold Voltage                              | V <sub>UVL</sub> Falling                       |                                                       | •    | 1.12           | 1.21           | 1.30           | V     |

| $\Delta V_{UVLR(HYST)}$  | UVL Reset Hysteresis                                     |                                                |                                                       |      |                | 60             |                | mV    |

| V <sub>OV(TH)</sub>      | OV Pin Threshold Voltage                                 | V <sub>OV</sub> Rising                         | LTC4261C<br>LTC4261I                                  | •    | 1.743<br>1.730 | 1.770<br>1.770 | 1.797<br>1.810 | V     |

| $\Delta V_{OV(HYST)}$    | OV Pin Hysteresis                                        |                                                |                                                       | •    | 18             | 37.5           | 62             | mV    |

| $\Delta V_{SENSE}$       | Current Limit Sense Voltage Threshold                    | V <sub>SENSE</sub> – V <sub>EE</sub>           |                                                       | ٠    | 45             | 50             | 55             | mV    |

| V <sub>INPUT(TH)</sub>   | ON, EN, PGI, FLTIN Threshold Voltage                     | ON, EN, PGI, FLTIN                             | Falling or Rising                                     | •    | 0.8            | 1.4            | 2              | V     |

| $\Delta V_{INPUT(HYST)}$ | ON, EN, PGI, FLTIN Hysteresis                            |                                                |                                                       |      |                | 170            |                | mV    |

| V <sub>PGIO(TH)</sub>    | PGIO Pin Input Threshold Voltage                         | V <sub>PGIO</sub> Rising                       |                                                       | •    | 1.10           | 1.25           | 1.40           | V     |

| $\Delta V_{PGIO(HYST)}$  | PGIO Pin Input Hysteresis                                |                                                |                                                       |      |                | 100            |                | mV    |

| INPUT                    | ON, EN, UVH, UVL, OV, SENSE, PGI,<br>FLTIN Input Current | ON, EN, UVH, UVL,                              | OV, SENSE, $\overline{PGI}$ , $\overline{FLTIN} = 3V$ | •    |                | 0              | ±2             | μA    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at I<sub>IN</sub> = 5mA, T<sub>A</sub> = 25°C. (Note 2)

| SYMBOL                        | PARAMETER                          | CONDITIONS                                                                                |   | MIN                         | ТҮР                         | MAX                         | UNITS  |

|-------------------------------|------------------------------------|-------------------------------------------------------------------------------------------|---|-----------------------------|-----------------------------|-----------------------------|--------|

| Timer                         |                                    | 1                                                                                         |   |                             |                             |                             |        |

| V <sub>TMR(H)</sub>           | TMR Pin High Threshold             | V <sub>TMR</sub> Rising                                                                   | • | 2.43                        | 2.56                        | 2.69                        | V      |

| V <sub>TMR(L)</sub>           | TMR Pin Low Threshold              | V <sub>TMR</sub> Falling                                                                  | • | 40                          | 75                          | 110                         | mV     |

| I <sub>TMR(UP)</sub>          | TMR Pin Pull-Up Current            | Turn-On and Auto-Retry (Except OC) Delays,<br>V <sub>TMR</sub> = 0.2V                     | • | -7                          | -10                         | -13                         | μA     |

|                               |                                    | Power Good, $\overline{PGI}$ Check and OC Auto-Retry Delays, V <sub>TMR</sub> = 0.2V      | • | -3.5                        | -5                          | -6.5                        | μA     |

| I <sub>TMR(DN)</sub>          | TMR Pin Pull-Down Current          | Delays Except $\overline{\text{PGI}}$ Check or OC Auto-Retry, $V_{TMR}$ = 2.56V           | • | 6                           | 12                          | 20                          | mA     |

|                               |                                    | $\overline{\text{PGI}}$ Check and OC Auto-Retry Delays, $V_{TRM}$ = 2.56V                 | • | 3                           | 5                           | 7                           | μA     |

| Output Pins                   |                                    |                                                                                           |   |                             |                             |                             |        |

| V <sub>PWRGD</sub>            | PG, PGIO Pins Output Low           | I <sub>PG</sub> , I <sub>PGI0</sub> = 3mA<br>  P <sub>G</sub> , I <sub>PGI0</sub> = 500μA | • |                             | 0.8<br>0.15                 | 1.6<br>0.4                  | V<br>V |

| I <sub>PWRGD</sub>            | PG, PGIO Pins Leakage Current      | $\overline{PG}$ , PGIO = 80V                                                              | • |                             | 0                           | ±10                         | μA     |

| ADC                           |                                    |                                                                                           |   |                             |                             |                             |        |

|                               | Resolution (No Missing Codes)      | (Note 5)                                                                                  | • | 10                          |                             |                             | Bits   |

| INL                           | Integral Nonlinearity              | SENSE                                                                                     | • | -2.5                        |                             | 2.5                         | LSB    |

|                               |                                    | ADIN2/OV, ADIN                                                                            | • | -1.25                       |                             | 1.25                        | LSB    |

| V <sub>OS</sub>               | Offset Error                       | SENSE                                                                                     | • | -1.75                       |                             | 1.75                        | LSB    |

|                               |                                    | ADIN2/OV, ADIN                                                                            | • | -1.25                       |                             | 1.25                        | LSB    |

|                               | Full-Scale Voltage                 | SENSE                                                                                     | • | 62.8                        | 64                          | 65.2                        | mV     |

|                               |                                    | ADIN2/0V, ADIN                                                                            | • | 2.514                       | 2.560                       | 2.606                       | V      |

|                               | Conversion Rate                    |                                                                                           | • | 5.5                         | 7.3                         | 9                           | Hz     |

| R <sub>ADIN</sub>             | ADIN, ADIN2 Pins Input Resistance  | ADIN, ADIN2 = 1.28V                                                                       | • | 2                           | 10                          |                             | MΩ     |

| I <sub>ADIN</sub>             | ADIN, ADIN2 Pins Input Current     | ADIN, ADIN2 = 2.56V                                                                       | • |                             | 0                           | ±2                          | μA     |

| I <sup>2</sup> C Interface    |                                    | 1                                                                                         |   |                             |                             |                             |        |

| V <sub>ADR(H)</sub>           | ADR0, ADR1 Input High Threshold    |                                                                                           | • | INTV <sub>CC</sub><br>- 0.8 | INTV <sub>CC</sub><br>- 0.5 | INTV <sub>CC</sub><br>- 0.3 | V      |

| V <sub>ADR(L)</sub>           | ADR0, ADR1 Input Low Threshold     |                                                                                           | • | 0.3                         | 0.5                         | 0.8                         | V      |

| I <sub>ADR(IN,HL)</sub>       | ADR0, ADR1 High, Low Input Current | ADR0, ADR1 = 0V, 5V                                                                       | • |                             |                             | ±80                         | μA     |

| I <sub>ADR(IN,Z)</sub>        | ADR0, ADR1 Hi-Z Input Current      | ADR0, ADR1 = 0.8V, (INTV <sub>CC</sub> - 0.8V)                                            | • | ±10                         |                             |                             | μA     |

| VALERT(OL)                    | ALERT Pin Output Low Voltage       | I <sub>ALERT</sub> = 4mA                                                                  | • |                             | 0.2                         | 0.4                         | V      |

| V <sub>SDAO(OL)</sub>         | SDAO Pin Output Low Voltage        | I <sub>SDAO</sub> = 4mA                                                                   | • |                             | 0.2                         | 0.4                         | V      |

| I <sub>SDAO</sub> , ALERT(IN) | SDAO, ALERT Input Current          | SDAO, $\overline{\text{ALERT}} = 5V$                                                      | • |                             | 0                           | ±5                          | μA     |

| V <sub>SDAI,SCL(TH)</sub>     | SDAI, SCL Input Threshold          |                                                                                           | • | 1.6                         | 1.8                         | 2                           | V      |

| I <sub>SDAI,SCL(IN)</sub>     | SDAI, SCL Input Current            | SDAI, SCL = 5V                                                                            | • |                             | 0                           | ±2                          | μA     |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $I_{IN} = 5mA$ , $T_A = 25^{\circ}C$ . (Note 2)

| SYMBOL                        | PARAMETER                                             | CONDITIONS           | MIN | TYP  | MAX | UNITS     |

|-------------------------------|-------------------------------------------------------|----------------------|-----|------|-----|-----------|

| I <sup>2</sup> C Interface Ti | ming (Note 5)                                         | 1                    |     |      |     | · · · · · |

| f <sub>SCL(MAX)</sub>         | Maximum SCL Clock Frequency                           |                      | 400 |      |     | kHz       |

| t <sub>LOW</sub>              | SCL Low Period                                        |                      |     | 0.65 | 1.3 | μs        |

| t <sub>HIGH</sub>             | SCL High Period                                       |                      |     | 50   | 600 | ns        |

| t <sub>BUF(MIN)</sub>         | Minimum Bus Free Time Between<br>Stop/Start Condition |                      |     | 0.12 | 1.3 | μs        |

| t <sub>hd,sta(MIN)</sub>      | Minimum Hold Time After (Repeated)<br>Start Condition |                      |     | 140  | 600 | ns        |

| t <sub>SU,STA(MIN)</sub>      | Minimum Repeated Start Condition<br>Set-Up Time       |                      |     | 30   | 600 | ns        |

| t <sub>SU,STO(MIN)</sub>      | Minimum Stop Condition Set-Up Time                    |                      |     | 30   | 600 | ns        |

| t <sub>hd,dati(Min)</sub>     | Minimum Data Hold Time Input                          |                      |     | -100 | 0   | ns        |

| t <sub>HD,DATO(MIN)</sub>     | Minimum Data Hold Time Output                         |                      | 300 | 600  | 900 | ns        |

| t <sub>SU,DAT(MIN)</sub>      | Minimum Data Set-Up Time Input                        |                      |     | 30   | 100 | ns        |

| t <sub>SP(MAX)</sub>          | Maximum Suppressed Spike Pulse<br>Width               |                      | 50  | 110  | 250 | ns        |

| t <sub>RST</sub>              | Stuck-Bus Reset Time                                  | SCL or SDAI Held Low | 25  | 66   |     | ms        |

| C <sub>X</sub>                | SCL,SDA Input Capacitance                             | SDAI Tied to SDA0    |     | 5    | 10  | pF        |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** All currents into pins are positive, all voltages are referenced to device GND ( $V_{EE}$ ) unless otherwise specified.

**Note 3:** An internal shunt regulator limits the V<sub>IN</sub> pin to a minimum of 10.65V. Driving this pin to voltages beyond 10.65V may damage the part. The pin can be safely tied to higher voltages through a resistor that limits the current below 50mA.

**Note 4:** An internal clamp limits the DRAIN pin to a minimum of 3.5V. Driving this pin to voltages beyond the clamp may damage the part. The pin can be safely tied to higher voltages through a resistor that limits the current below 2mA.

Note 5: Guaranteed by design and not subject to test.

### LTC4261

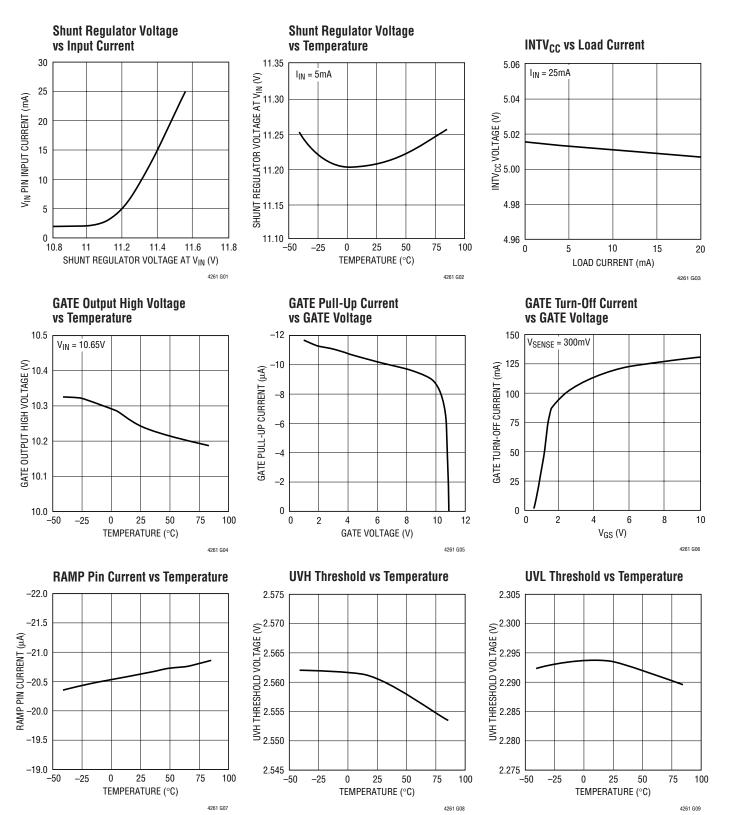

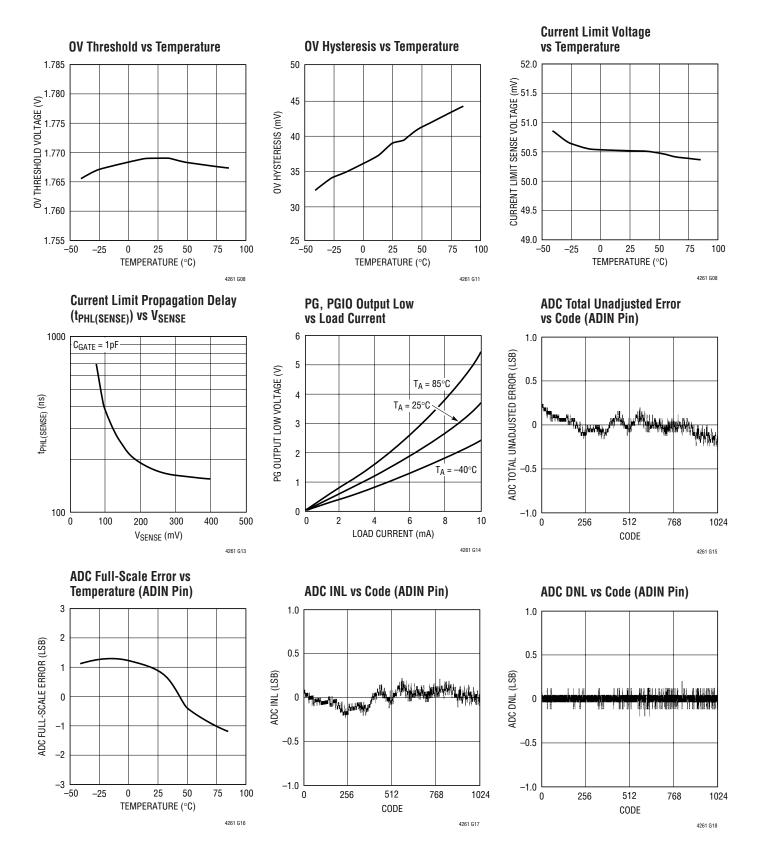

### **TYPICAL PERFORMANCE CHARACTERISTICS** $I_{IN} = 5 \text{ mA}, T_A = 25^{\circ}\text{C}, unless otherwise noted$

### **TYPICAL PERFORMANCE CHARACTERISTICS** $I_{IN} = 5mA$ , $T_A = 25^{\circ}C$ , unless otherwise noted

### LTC4261

### PIN FUNCTIONS (SSOP/QFN)

**ADIN (Pin 23/Pin 16):** ADC Input. A voltage between 0V and 2.56V applied to this pin is measured by the on-chip ADC. Tie to  $V_{EE}$  if unused.

**ADIN2 (Pin 10/NA):** Second ADC Input. Not available on QFN package.

**ADR0, ADR1 (Pins 24, 25/Pins 17, 18):** Serial Bus Address Inputs. Tying these pins to  $V_{EE}$ , OPEN or  $INTV_{CC}$  configures one of nine possible addresses. See Table 1 in Applications Information.

**ALERT** (Pin 3/Pin 24): Fault Alert Output. Open-drain logic output that pulls to  $V_{EE}$  when a fault occurs to alert the host controller. A fault alert is enabled by the ALERT register. See Applications Information. Connect to  $V_{EE}$  if unused.

**DRAIN (Pin 16/Pin 11):** Drain Sense Input. Connect an external 1M resistor between this pin and the drain terminal  $(V_{OUT})$  of the N-channel FET. When the DRAIN pin voltage is less than 1.77V and the GATE pin voltage is above  $V_Z - 1.2V$  the power good outputs are asserted after a delay. The voltage at this pin is internally clamped to 4V.

**EN** (Pin 26/Pin 19): Device Enable Input. Pull low to enable the N-channel FET to turn-on after a start-up debounce delay set by the TMR pin. When this pin is pulled high, the FET is off. Transitions on this pin will be recorded in the FAULT register. A high-to-low transition activates the logic to read the state of the ON pin and clear faults. Requires external pull-up. Debouncing with an external capacitor is recommended when used to monitor board present. Connect to  $V_{EE}$  if unused.

**Exposed Pad (Pin 25, QFN Only):** Exposed Pad may be left open or connected to device ground ( $V_{EE}$ ).

**FLTIN (Pin 22/NA):** General Purpose Fault Input. If this pin pulls low, the FAULT register bit B7 is latched to "1." This pin is used to sense an external fault condition and its status does not affect the FET control functions of the LTC4261. Not available on the QFN package. Connect to INTV<sub>CC</sub> if unused.

**GATE (Pin 15/Pin 10):** N-Channel FET Gate Drive Output. This pin is pulled up by an internal current source  $I_{GATE}$  (11.5µA when the SS pin reaches its clamping voltage). GATE stays low until V<sub>IN</sub> and INTV<sub>CC</sub> cross the UVLO thresholds, UV and OV conditions are satisified and an adjustable timer delay expires. During turn-off, short-circuit or undervoltage lockout ( $V_{IN}$  or  $INTV_{CC}$ ), a 110mA pull-down current between GATE and  $V_{EE}$  is activated.

**INTV<sub>CC</sub> (Pin 7/Pin 4):** Low Voltage (5V) Supply Output. This is the output of the internal linear regulator with an internal UVLO threshold of 4.25V. This voltage powers up the data converter and logic control circuitry. Bypass this pin with a  $0.1\mu$ F capacitor to V<sub>EE</sub>.

**ON (Pin 2/Pin 23):** On Control Input. A rising edge turns on the external N-channel FET while a falling edge turns it off. This pin is also used to configure the state of the FET ON register bit D3 in the CONTROL register (and hence the external FET) at power-up. For example if the ON pin is tied high, then the register bit D3 goes high one timer cycle after power-up. Likewise, if the ON pin is tied low, then the device remains off after power-up until the register bit D3 is set high using the I<sup>2</sup>C bus. A high-to-low transition on this pin clears faults.

**OV (Pin 11/Pin 7):** Overvoltage Detection Input. Connect this pin to an external resistive divider from  $V_{EE}$ . If the voltage at the pin rises above 1.77V, the N-channel FET is turned off. The overvoltage condition does not affect the status of the power good outputs. On the QFN package, this pin is also measured by the on-chip ADC. Connect to  $V_{EE}$  if unused.

**PG** (Pin 27/Pin 20): Power Good Status Output. This open-drain pin pulls low and stays latched a timer delay after the FET is on (when GATE reaches  $V_Z - 1.2V$  and DRAIN is within 1.77V of  $V_{EE}$ ). The power good output is reset in all GATE pull-down events except an overvoltage fault. Connect to  $V_{EE}$  if unused.

**PGI** (Pin 1/Pin 22): Power Good Input. This pin along with the PGI check timer serves as a watchdog to monitor the power-up of the DC/DC converter. The PGI pin must be low before the PGI check timer expires, otherwise the GATE pin pulls down and stays latched and a power bad fault is logged into the FAULT register. The PGI timer is started after the second power good is latched and its delay is equal to four times the start-up debounce delay. Connect to  $V_{EE}$  if unused.

### PIN FUNCTIONS (SSOP/QFN)

**PGIO (Pin 28/Pin 21):** General Purpose Input/Output. Opendrain logic output and logic input. Defaults to pull low a timer delay after the PG pin goes low to indicate a second power good output. Configure according to Table 6.

**RAMP (Pin 18/Pin 12):** Inrush Current Ramp Control Pin. The inrush current is set by placing a capacitor ( $C_R$ ) between the RAMP pin and the drain terminal of the FET. At start-up, the GATE pin is pulled up by  $I_{GATE(UP)}$  until the pass transistor begins to turn on. A current,  $I_{RAMP}$  then flows through  $C_R$  to ramp down the output voltage  $V_{OUT}$ . The value of  $I_{RAMP}$  is controlled by the SS pin voltage. When the SS pin reaches its clamp voltage (2.56V),  $I_{RAMP}$ = 20µA. The ramp rate of  $V_{OUT}$  and the load capacitor  $C_L$ set the inrush current:  $I_{INRUSH} = (C_L/C_R) \bullet I_{RAMP}$ .

**SCL (Pin 6/Pin 3):** Serial Bus Clock Input. Data at the SDAI pin is shifted in and data at the SDAO pin is shifted out on rising edges of SCL. This is a high impedance pin that is generally connected to the output of the incoming optoisolator driven by the SCL port of the master controller. An external pull-up resistor or current source is required. Pull up to INTV<sub>CC</sub> if unused.

**SDAI (Pin 5/Pin 2):** Serial Bus Data Input. This is a high impedance input pin used for shifting in command or data bits. An external pull-up resistor or current source is required. Normally connected to the output of the incoming optoisolator that is driven by the SDA port of the master controller. Pull up to  $INTV_{CC}$  if unused.

**SDAO (Pin 4/Pin 1):** Serial Bus Data Output. Open-drain output used for sending data back to the master controller or acknowledging a write operation. An external pull-up resistor or current source is required. Normally connected to the input of the outgoing optoisolator that outputs to the SDA port of the master controller. In the single-wire broadcast mode, the SDAO pin sends out selected data that is encoded with an internal clock.

**SENSE (Pin 14/Pin 9):** Current Limit Sense Input. Load current through the external sense resistor ( $R_S$ ) is monitored and controlled by an active current limit amplifier to 50mV/ $R_S$ . Once  $V_{SENSE}$  reaches 50mV, a circuit breaker timer starts and turns off the pass transistor after 530 $\mu$ s. In the event of a catastrophic short circuit, if  $V_{SENSE}$  crosses 150mV, a fast response comparator immediately pulls the GATE pin down to turn off the N-channel FET.

**SS (Pin 19/Pin 13):** Soft-Start Input. Connect a capacitor to this pin to control the rate of rise of inrush current (dl/dt) during start-up. An internal 10 $\mu$ A current source charging the external soft-start capacitor (C<sub>SS</sub>) creates a voltage ramp. This voltage is converted to a current to charge the GATE pin up and to ramp the output voltage down. The SS pin is internally clamped to 2.56V limiting I<sub>GATE(UP)</sub> to 11.5 $\mu$ A and I<sub>RAMP</sub> to 20 $\mu$ A. If the SS capacitor is absent, the SS pin ramps from 0V to 2.56V in 220 $\mu$ s.

**TMR (Pin 20/Pin 14):** Delay Timer Input. Connect a capacitor ( $C_{TMR}$ ) to this pin to create timing delays at start-up, when power good outputs pull down, during PGI check and when auto-retrying after faults (except overvoltage fault). Internal pull-up currents of 10µA and 5µA and pull-down currents of 5µA and 10mA configure the delay periods as multiples of a nominal delay of 256ms •  $C_{TMR}/\mu$ F. Delays for start-up and auto-retry following undervoltage or power bad fault are the same as the nominal delay. Delays for sequenced power good outputs are twice of the nominal delay. Delays for PGI check and auto-retry following over-current fault are four times the nominal delay.

**UVH (Pin 9/Pin 6):** Undervoltage High Level Input. Connect this pin to an external resistive divider from  $V_{EE}$ . If the voltage at the UVH pin rises above 2.56V the pass transistor is allowed to turn on. A small capacitor at this pin prevents transients and switching noise from affecting the UVH threshold. Connect to INTV<sub>CC</sub> if unused.

**UVL (Pin 8/Pin 5):** Undervoltage Low Level Input. Connect this pin to an external resistive divider from  $V_{EE}$ . If the voltage at the UVL pin drops below 2.291V, the pass transistor is turned off and the power good outputs go high impedance. Pulling this pin below 1.21V resets faults and allows the pass transistor to turn back on. Connect to INTV<sub>CC</sub> if unused.

**V**<sub>EE</sub> (**Pin 13/Pin 8**): Negative Supply Voltage Input and Device Ground. Connect this pin to the negative side of the power supply.

$V_{IN}$  (Pin 21/Pin 15): Positive Supply Input. Connect this pin to the positive supply through a dropping resistor. An internal shunt regulator clamps  $V_{IN}$  at 11.2V. An internal undervoltage lockout (UVLO) circuit holds the GATE low until  $V_{IN}$  is above 9V. Bypass this pin with a 1µF capacitor to  $V_{FF}$ .

### LTC4261

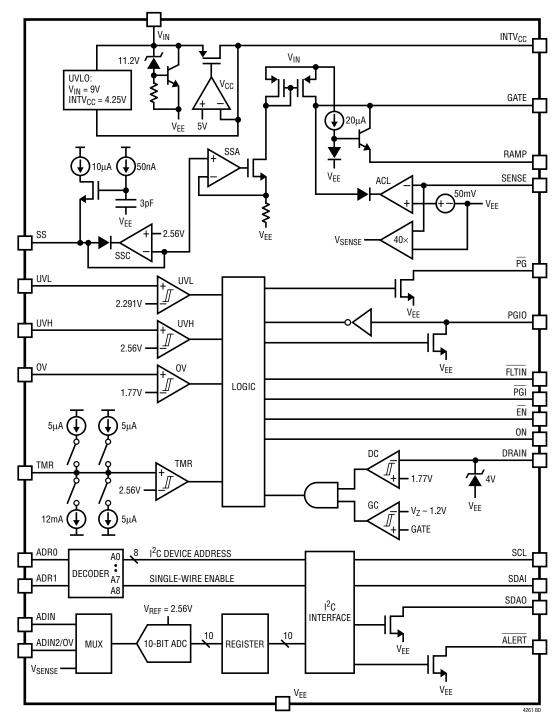

### **BLOCK DIAGRAM**

### OPERATION

The LTC4261 is designed to turn a board's supply voltage on and off in a controlled manner, allowing the board to be safely inserted or removed from a live -48V backplane. The device also features an on-board 10-bit ADC and I<sup>2</sup>C interface that allow monitoring board current, voltages and faults. The main functional circuits of the LTC4261 are illustrated in the Block Diagram.

In normal operation after a start-up debounce delay, the GATE pin turns on the external N-channel FET passing power to the load. The GATE pin is powered by a shunt regulated 11.2V supply on the V<sub>IN</sub> pin that is derived from –48V RTN through a dropping resistor. The turn-on sequence starts by pulling the SS pin up. The voltage at the SS pin is converted to a current,  $I_{GATE(UP)}$ , pulling the GATE up. When the pass FET starts to turn on and charge the load capacitor, the inrush current flowing through the FET is a function of the capacitor at RAMP (C<sub>R</sub>), the load capacitor (C<sub>L</sub>) and the ramp current (I<sub>RAMP</sub>) that flows from the RAMP pin to C<sub>R</sub>:

$$I_{\text{INRUSH}} = I_{\text{RAMP}} \bullet \frac{C_{\text{L}}}{C_{\text{R}}}$$

$I_{RAMP}$  and  $I_{GATE(UP)}$  are approximately proportional to the SS pin voltage and are limited to 20µA and 11.5µA, respectively when SS reaches its clamping voltage (2.56V).

The ACL amplifier is used for overcurrent and short-circuit protection. It monitors the load current through the SENSE pin voltage and a sense resistor  $R_S$ . In an overcurrent condition, the ACL amplifier limits the current to 50mV/ $R_S$  by pulling down GATE in an active servo loop. After a 530µs timeout, the ACL amplifier turns off the pass FET. In the event of a catastrophic short circuit, when V<sub>SENSE</sub> crosses 150mV, a fast response comparator pulls the GATE pin down with a 110mA current.

The DRAIN and the GATE voltages are monitored to determine if power is available for the load. Two power good signals are sequenced on the PG pin (first power good signal) and the PGIO pin (second power good signal), each with a debounce delay that is twice the start-up delay. The PGIO pin can also be used as a general purpose input or output. The PGI pin serves as a watchdog to monitor the output of the DC/DC module. If the module output fails to come up, the LTC4261 shuts down.

The TMR pin generates delays for initial start-<u>up</u>, auto-retry following a fault, power good outputs and PGI check.

The logic circuits are powered by an internally generated 5V supply (available on the INTV<sub>CC</sub> pin). Prior to turning on the pass FET, both  $V_{IN}$  and  $INTV_{CC}$  voltages must exceed their undervoltage lockout thresholds. In addition, the control inputs UVH, UVL, OV, EN, ON and PGI are monitored by comparators. The FET is held off until all start-up conditions are met.

A 10-bit analog to digital converter (ADC) is included in the LTC4261. The ADC measures SENSE resistor voltage as well as voltage at the ADIN2/OV (SSOP/QFN) and ADIN pins. The results are stored in on-board registers.

An I<sup>2</sup>C interface is provided to read the ADC data registers. It also allows the host to <u>poll the</u> device and determine if a fault has occurred. If the ALERT line is used as an interrupt, the host can respond to a fault in real time. The SDA line is divided into SDAI (input) and SDAO (output) to facilitate opto coupling with the system host. Two three-state pins, ADRO and ADR1, are used to decode eight device addresses. The interface can also be configured through the ADRO and ADR1 pins for a single-wire broadcast mode, sending ADC data and faults status through the SDAO pin to the host without clocking the SCL line. This single-wire, one-way communication simplifies system design by eliminating two optocouplers on SCL and SDAI that are required by an I<sup>2</sup>C interface.

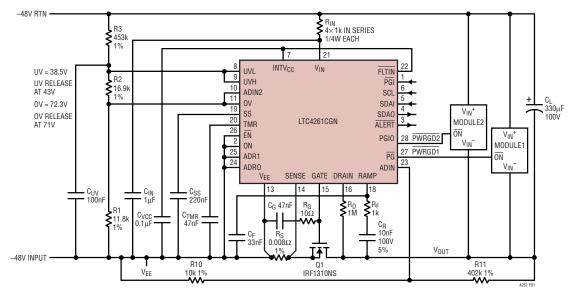

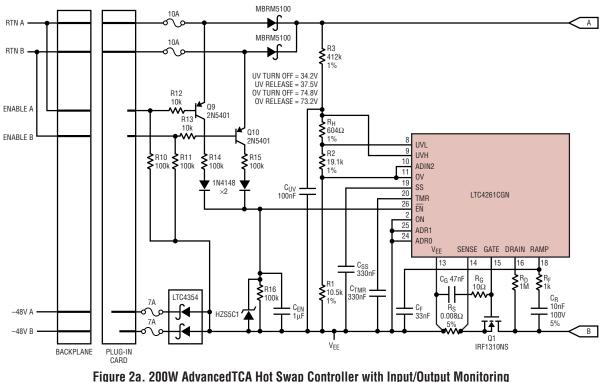

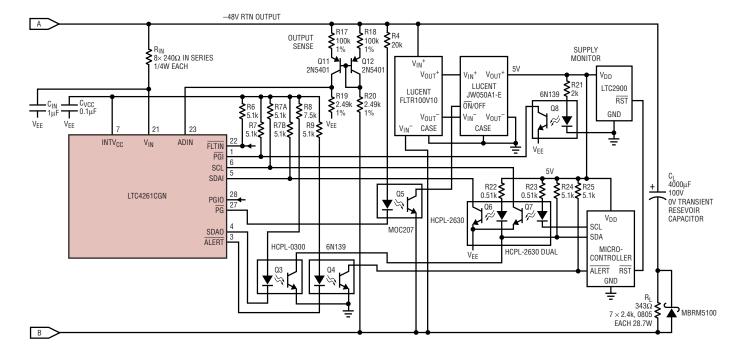

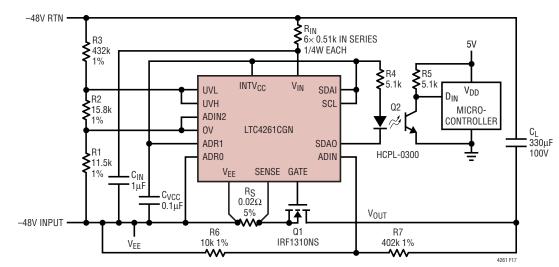

The LTC4261 is ideally suited for -48V distributed power systems and AdvancedTCA systems. A basic 200W application circuit using the LTC4261 is shown in Figure 1. A more complete application circuit with AdvancedTCA connections is shown in Figure 2.

#### **Input Power Supply**

Power for the LTC4261 is derived from the -48V RTN through an external current limiting resistor (R<sub>IN</sub>) to the V<sub>IN</sub> pin. An internal shunt regulator clamps the voltage at

Figure 1. –48V/200W Hot Swap Controller Using LTC4261 with Current, Input Voltage and  $V_{DS}$  Monitoring (5.6A Current Limit, 0.66A Inrush)

and Power Good Watchdog Using LTC4261 in I<sup>2</sup>C Mode (Part One)

$V_{\rm IN}$  to 11.2V (V<sub>Z</sub>) and provides power to the GATE driver. The data converter and logic control circuits are powered by an internal linear regulator that derives 5V from the 11.2V supply. The 5V output is available at the INTV<sub>CC</sub> pin for driving external circuits (up to 20mA load current).

Bypass capacitors of  $1\mu$ F and  $0.1\mu$ F are recommended at V<sub>IN</sub> and INTV<sub>CC</sub>, respectively. R<sub>IN</sub> should be chosen to accommodate the maximum supply current requirement of the LTC4261 (5mA) plus the supply current required by any external devices driven by the V<sub>IN</sub> and INTV<sub>CC</sub> pins at the minimum intended operation voltage.

$R_{IN} \leq \frac{V_{48V(MIN)} - V_{Z(MAX)}}{I_{IN(MAX)} + I_{EXTERNAL}}$

The maximum power dissipation in the resistor is:

$$P_{MAX} = \frac{\left(V_{48V(MAX)} - V_{Z(MIN)}\right)^2}{R_{IN}}$$

If the power dissipation is too high for a single resistor, use multiple low power resistors in series.

#### **Initial Start-Up and Inrush Control**

Several conditions must be satisfied before the FET turn-on sequence is started. First the voltage at V<sub>IN</sub> must exceed its 9V undervoltage lockout level. Next the internal supply INTV<sub>CC</sub> must cross its 4.25V undervoltage lockout level. This generates a 100µs to 160µs power-on-reset pulse during which the FAULT register bits are cleared and the CONTROL register bits are set or cleared as described in the register section. After the power-on-reset pulse, the voltages at the UVH, UVL and OV pins must satisfy UVH > 2.56V, UVL > 2.291V and OV < 1.77V to indicate that the input power is within the acceptable range and the EN pin must be pulled low. All the above conditions must be satisfied throughout the duration of the start-up debounce delay that is set by an external capacitor (C<sub>TMB</sub>) connected to the TMR pin. C<sub>TMR</sub> is charged with a pull-up current of  $10\mu$ A until the voltage at TMR reaches 2.56V. C<sub>TMR</sub> is then quickly discharged with a 12mA current. The initial delay expires when TMR is brought below 75mV. The duration of the start-up delay is given by:

$$t_D = 256 \text{ms} \cdot \frac{C_{TMR}}{1 \mu F}$$

Figure 2b. 200W AdvancedTCA Hot Swap Controller with Input/Output Monitoring and Power Good Watchdog Using LTC4261 in I<sup>2</sup>C Mode (Part Two)

### LTC4261

### **APPLICATIONS INFORMATION**

If any of the above conditions is violated before the start-up delay expires,  $C_{TMR}$  is quickly discharged and the turn-on sequence is restarted. After all the conditions are validated throughout the start-up delay, the ON pin is then checked. If it is high, the FET will be turned on. Otherwise, the FET will be turned on when the ON pin is raised high or the FET ON bit D3 in the CONTROL register is set to "1" through the I<sup>2</sup>C interface.

The FET turn-on sequence follows by charging an external capacitor at the SS pin ( $C_{SS}$ ) with a 10µA pull-up current and the voltage at SS ( $V_{SS}$ ) is converted to a current ( $I_{GATE(UP)}$ ) of 11.5µA·  $V_{SS}$ /2.56V for GATE pull-up. When the GATE reaches the FET threshold voltage, the inrush current starts to flow through the FET and a current ( $I_{RAMP}$ ) of 20µA·  $V_{SS}$ /2.56V flows out of the RAMP pin and through an external capacitor ( $C_R$ ) connected between RAMP and  $V_{OUT}$ . The SS voltage is clamped to 2.56V, which corresponds to  $I_{GATE(UP)} = 11.5$ µA and  $I_{RAMP} = 20$ µA. The RAMP pin voltage is regulated at 1.1V and the ramp rate of  $V_{OUT}$  determines the inrush current:

$$I_{\rm INRUSH} = 20\mu A \bullet \frac{C_{\rm L}}{C_{\rm R}}$$

The ramp rate of  $V_{\mbox{\scriptsize SS}}$  determines dl/dt of the inrush current:

$$\frac{dI_{INRUSH}}{dt} = 20\mu A \bullet \frac{C_L}{C_R} \bullet \frac{1\mu F}{256ms \bullet C_{SS}}$$

If  $C_{SS}$  is absent, an internal circuit pulls the SS pin from 0V to 2.56V in about 220 $\mu$ s.

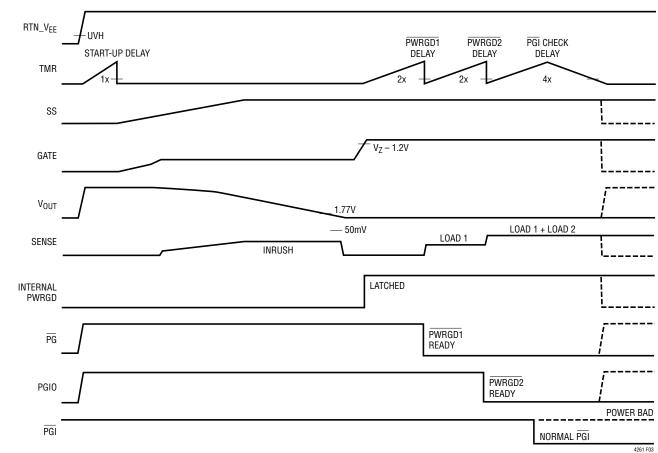

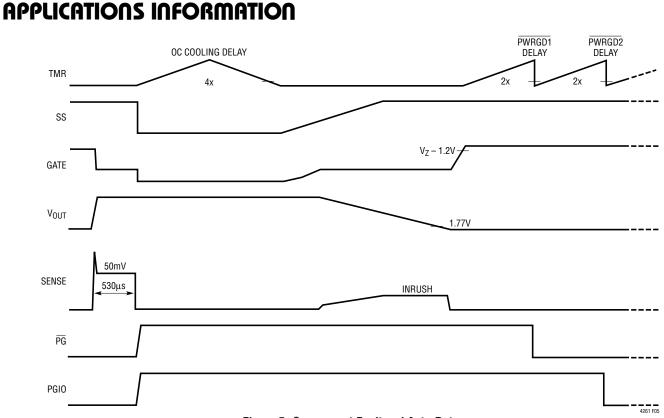

When  $V_{OUT}$  is ramped down to  $V_{EE}$ ,  $I_{GATE}$  returns to the GATE pin and pulls the GATE up to  $V_{GATEH}$ . Figure 3 illustrates the start-up sequence of the LTC4261.

During board insertion and input power step, an internal clamp turns on to hold the RAMP pin low. Capacitor  $C_F$  and resistor  $R_F$  suppress the noise at the RAMP pin. For proper operation,  $R_F \bullet C_R$  should not exceed 50µs. The recommended value of  $C_F$  is 3  $\bullet$   $C_R$ .

#### **Power Good Monitors**

When  $V_{DS}$  of the pass transistor falls below 1.77V and GATE pulls above  $V_Z - 1.2V$ , an internal power good signal is latched and a series of three delay cycles are started as shown in Figure 3. When the first delay cycle with a duration of  $2t_D$  expires, the PG pin pulls low as a power good signal to turn on the first module. When the second delay cycle (2t<sub>D</sub>) expires, the PGIO pin pulls low as a power good signal to turn on the second module. The third delay cycle with a duration of  $4t_D$  is for PGI check. Before the third delay cycle expires, the PGI pin must be pulled low by an external supply monitor (such as the LTC2900 in Figure 2) to keep the FET on. Otherwise, the FET is turned off and the power bad fault (PBAD) is logged in the FAULT register. The 2t<sub>D</sub> timer delay is obtained by charging  $C_{TMB}$  with a 5µA current and discharging  $C_{TMB}$ with a 12mA current when TMR reaches 2.56V. For the 4t<sub>D</sub> timer delay, the charging and discharging currents of  $C_{TMR}$  are both 5µA. The power good signals at PG and PGIO are reset in all FET turn-off conditions except the overvoltage fault.

#### **Turn-Off Sequence and Auto-Retry**

In any of the following conditions, the FET is turned off by pulling down GATE with a 110mA current, and  $C_{SS}$  and  $C_{TMR}$  are discharged with 12mA currents.

- 1. The ON pin is low or the ON bit in the CONTROL register is set to 0.

- 2. The EN pin is high.

- 3. The voltage at UVL is lower than 2.291V and the voltage at UVH is lower than 2.56V (undervoltage fault).

- 4. The voltage at OV is higher than 1.77V (overvoltage fault).

- 5. The voltage at  $V_{\text{IN}}$  is lower than 9V (V\_{\text{IN}} undervoltage lockout).

Figure 3. LTC4261 Turn-On Sequence

- The voltage at INTV<sub>CC</sub> is lower than 4.25V (INTV<sub>CC</sub> undervoltage lockout).

- 7.  $V_{SENSE} > 50 \text{mV}$  and the condition lasts longer than 530µs (overcurrent fault).

- 8. The PGI pin is high when the PGI check timer expires (power bad fault).

For conditions 1, 2, 5, 6, after the condition is cleared, the LTC4261 will automatically enter the FET turn-on sequence as previously described.

For any of the fault conditions 3, 4, 7, 8, the FET off mode is programmable by the corresponding auto-retry

bit in the CONTROL register. If the auto-retry bit is set to 0, the FET is latched off upon the fault condition. If the auto-retry bit is set to 1, after the fault condition is cleared, a delay timer is started. After the timer expires, the FET enters the auto-retry mode and GATE is pulled up. The auto-retry delay following the undervoltage fault or the power bad fault has a duration of  $t_D$ . The autoretry delay following the overcurrent fault has a duration of  $4t_D$  for extra cooling time. The auto-retry following the overvoltage fault does not have a delay. The auto-retry control bits and their defaults at power up are listed in Table 6.

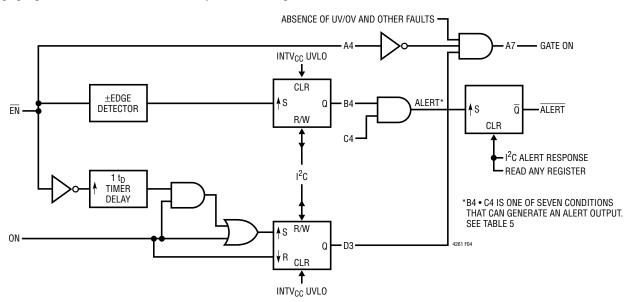

#### EN and ON

Figure 4 shows a logic diagram for  $\overline{EN}$  and ON as they relate to GATE, ALERT and internal registers A4, A7, B4, C4 and D3. Also affecting GATE is the status of UV, OV and several other fault conditions. The  $\overline{EN}$  and ON pins have 0.8V to 2V logic thresholds relative to V<sub>EE</sub> with a maximum input leakage current of ±2µA.

Register bit A4 indicates the present state of EN, and B4 is set high whenever  $\overline{\text{EN}}$  changes state. Rising and falling edges at the ON pin set and clear FET-on control bit, D3. Another path allows a falling edge at  $\overline{\text{EN}}$  to latch a high state at the ON pin (such as when ON is permanently pulled high) into D3 after a time delay. Both B4 and D3 can be set or cleared directly by I<sup>2</sup>C, and both are cleared low whenever INTV<sub>CC</sub> drops below its UVLO threshold. The condition of the GATE pin outp<u>ut</u> is controlled by register bit A7, which is the AND of A4, D3 and the absence of UV, OV and other faults.

#### **Overcurrent Protection and Overcurrent Fault**

The LTC4261 features two levels of protection from short-circuit and overcurrent conditions. Load current is monitored by the SENSE pin and resistor  $R_S$ . There are two distinct thresholds for the voltage at SENSE: 50mV for engaging the active current limit loop and starting a

530µs circuit breaker timer and 150mV for a fast GATE pull-down to limit peak current in the event of a catastrophic short circuit or an input step.

In an overcurrent condition, when the voltage drop across  $R_S$  exceeds 50mV, the current limit loop is engaged and an internal 530µs circuit breaker timer is started. The current limit loop servos the GATE to maintain a constant output current of 50mV/R<sub>S</sub>. When the circuit breaker timer expires, the FET is turned off by pulling GATE down with a 110mA current, the capacitors at SS and TMR are discharged and the power good signals are reset. At this time, the overcurrent present bit A2 and the overcurrent fault bit B2 are set, and the circuit breaker timer is reset.

After the FET is turned off, the overcurrent present bit A2 is cleared. If the overcurrent auto-retry bit D2 has been set, the FET will turn on again automatically after a cooling time of  $4t_D$ . Otherwise, the FET will remain off until the overcurrent fault bit B2 is reset. When the overcurrent fault bit is reset (see Resetting Faults), the FET is allowed to turn on again after a delay of  $4t_D$ . The  $4t_D$  cooling time associated with the overcurrent fault will not be interrupted by any other fault condition. See Figure 5 for operation of LTC4261 under overcurrent condition followed by auto-retry.

Figure 4. Logic Block Diagram of EN and ON Pins

Figure 5. Overcurrent Fault and Auto-Retry

In the case of a low impedance short circuit on the load side or an input step during battery replacement, current overshoot is inevitable. A fast SENSE comparator with a threshold of 150mV detects the overshoot and immediately pulls GATE low with a 110mA current. Once the SENSE voltage drops to 50mV, the current limit loop takes over and servos the current as previously described. If the short-circuit condition lasts longer than 530µs, the FET is shut down and the overcurrent fault is registered.

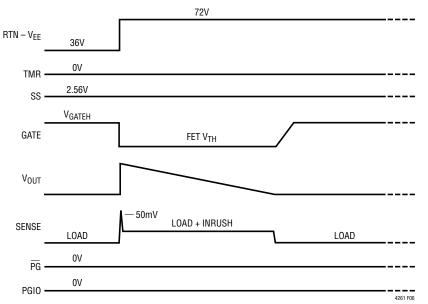

In the case of an input step, after an internal clamp pulls the RAMP pin down to 1.1V, the inrush control circuit takes over and the current limit loop is disengaged before the circuit breaker timer expires. From this point on, the device works as in the initial start-up:  $V_{OUT}$  is ramped down at the rate set by  $I_{RAMP}$  and  $C_R$  followed by GATE pull-up. The power good signals on the PG and PGIO pins, the TMR pin, and the SS pin are not interrupted through the input step sequence. The waveform in Figure 6 shows how the LTC4261 responds to an input step.

Note that the current limit threshold should be set sufficiently high to accommodate the sum of the load current and the inrush current to avoid engagement of the current limit loop in the event of an input step. The maximum value of the inrush current is given by:

$$I_{INRUSH} \le 0.8 \bullet \frac{45mV}{R_S} - I_{LOAD}$$

where the 0.8 factor is used as a worst case margin combined with the minumum threshold (45mV).

The active current limit circuit is compensated using the capacitor  $C_G$  with a series resistor  $R_G$  (10 $\Omega$ ) connected between GATE and  $V_{EE}$ , as shown in Figure 1. The suggested value for  $C_G$  is 50nF. This value should work for most pass transistors (Q1).

#### **Overvoltage Fault**

An overvoltage fault occurs when the OV pin rises above its 1.77V threshold. This shuts off the pass transistor immediately, sets the overvoltage present bit A0 and the overvoltage fault bit B0, and pulls the SS pin down. Note that the power good signals are not affected by the overvoltage fault. If the OV pin subsequently falls back below the threshold, the pass transistor will be allowed 4261f

Figure 6. -36V to -72V Step Response

to turn on again immediately (without delay) unless the overvoltage auto-retry has been disabled by clearing register bit D0.

#### **Undervoltage Comparator and Undervoltage Fault**

The LTC4261 provides two undervoltage pins, UVH and UVL, for adjustable UV threshold and hysteresis. The UVH and UVL pins have the following accurate thresholds:

For UVH rising,  $V_{UVH(TH)} = 2.56V$ , turn on

For UVL falling, V<sub>UVL(TH)</sub> = 2.291V, turn off

Both UVH and UVL pins have a minimum hysteresis of  $\delta V_{UV}$  (15mV typical). In either a rising or a falling input supply, the undervoltage comparator works in such a way that both the UVH and the UVL pins have to cross their thresholds for the comparator output to change state.

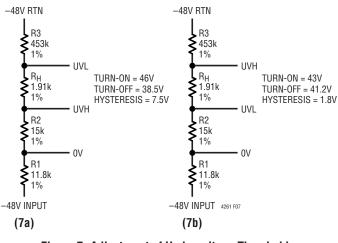

The UVH, UVL, and OV threshold ratio is designed to match the standard telecom operating range of 43V to 71V and UV hysteresis of 4.5V when UVH and UVL are tied together as in Figure 1, where the built-in UV hysteresis referred to the UVL pin is:

$\Delta V_{UV(HYST)} = V_{UVH(TH)} - V_{UVL(TH)} = 0.269V$

Using R1 = 11.8k, R2 = 16.9k and R3 = 453k as in Figure 1 gives a typical operating range of 43.0V to 70.7V, with

an undervoltage shutdown threshold of 38.5V and an overvoltage shutdown threshold of 72.3V.

The UV hysteresis can be adjusted by separating the UVH and the UVL pins with a resistor  $R_H$  (Figure 7). To increase the UV hysteresis, the UVL tap should be placed above the UVH tap as in Figure 7a. To reduce the UV hysteresis, place the UVL tap under the UVH tap as in Figure 7b. UV hysteresis referred to the UVL pin is given by:

$$\begin{split} &\text{for } V_{UVL} \geq V_{UVH}, \\ &\Delta V_{UVL(HYST)} = \Delta V_{UV(HYST)} + 2.56V \bullet \frac{R_{H}}{R1 + R2} \\ &\text{or for } V_{UVL} < V_{UVH}, \\ &\Delta V_{UVL(HYST)} = \Delta V_{UV(HYST)} - 2.56V \bullet \frac{R_{H}}{R1 + R2 + R_{H}} \end{split}$$

For  $V_{UVL} < V_{UVH}$ , the minimum UV hysteresis allowed is the minimum hysteresis at UVH and UVL:  $\delta V_{UV} = 15$ mV when  $R_{H(MAX)} = 0.11 \cdot (R1 + R2)$

The design of the LTC4261 protects the UV comparator from chattering even when  $R_H$  is larger than  $R_{H(MAX)}$ .

An undervoltage fault occurs when the UVL pin falls below 2.291V and the UVH pin falls below 2.56V –  $\delta V_{UV}$ . This activates the FET turn-off and sets the undervoltage present bit A1 and the undervoltage fault bit B1. The power good signals at PG and PGIO are also reset.

Figure 7. Adjustment of Undervoltage Thresholds for Larger (7a) or Smaller (7b) Hysteresis

The undervoltage present bit A1 is cleared when the UVH pin rises above 2.56V and the UVL pin rises above 2.291V +  $\delta V_{UV}$ . After a delay of t<sub>D</sub>, the FET will turn on again unless the undervoltage auto-retry has been disabled by clearing bit D1.

When power is applied to the device, if UVL is below the 2.291V threshold and UVH is below  $2.56V - \delta V_{UV}$  after INTV<sub>CC</sub> crosses its undervoltage lock out threshold (4.25V), an undervoltage fault will be logged in the fault register.

Because of the compromises of selecting from a table of discrete resistor values (1% resistors in 2% increments, 0.1% resistors in 1% increments), best possible OV and UV accuracy is achieved using separate dividers for each pin. This increases the total number of resistors from three or four to as many as six, but maximizes accuracy, greatly simplifies calculations and facilitates running changes to accommodate multiple standards or custom-ization without any board changes.

#### FET Short Fault

A FET short fault will be reported if the data converter measures a current sense voltage greater than or equal to 2mV while the FET is turned off. This condition sets the FET short present bit A5 and the FET short fault bit B5.

#### **Power Bad Fault**

After the FET is turned on and the power good outputs pull PG and PGIO low, a delay timer with duration of  $4t_D$  is started and the level of the PGI pin is checked (Figure 3). If the PGI pin is pulled below its 1.4V threshold before the PGI check timer expires, the FET will remain on. Otherwise, the FET is immediately turned off, the power good signals are reset and the power bad present bit A3 and the power bad fault bit B3 are set. After the FET is turned off, the power bad present bit A3 will be cleared. If the PGI pin is subsequently pulled low, the FET will remain off unless the power bad auto-retry has been enabled by setting bit D4 or the power bad fault bit B3 is cleared. In either of those two conditions, the FET will turn on again following a delay of  $t_D$  and the PGI pin is checked again as described above.

#### **External Fault Monitors**

The FLTIN pin (SSOP only) and the PGIO pin, when configured as general purpose input, allow monitoring of external fault conditions such as broken fuses. If FLTIN is pulled below its 1.4V threshold, bit B7 in the FAULT register is set. An associated alert bit, C7, is also available in the ALERT register. When the PGIO pin is configured as general purpose input, if the voltage at PGIO is above 1.25V, both bit A6 in the STATUS register and bit B6 in the FAULT register are set, though there is no alert bit associated with this fault. The external fault conditions do not directly affect the GATE control functions.

### **Fault Alerts**

When any of the fault bits in FAULT register B is set, an optional bus alert can be generated by setting the appropriate bit in the ALERT register C. This allows only selected faults to generate alerts. At power-up the default state is not to alert on faults. If an alert is enabled, the corresponding fault will cause the ALERT pin to pull low. After the bus master controller broadcasts the alert response address, the LTC4261 will respond with its address on the SDA line and release ALERT as shown in Figure 14. If there is

a collision between two LTC4261's responding with their addresses simultaneously, then the device with the <u>lower</u> address wins arbitration and responds first. The ALERT line will also be released if the device is addressed by the bus master.

Once the ALERT signal has been released for one fault, it will not be pulled low again until the FAULT register indicates a different fault has occurred, or the original fault is cleared and it occurs again. Note that this means repeated or continuing faults will not generate alerts until the associated FAULT register bit has been cleared.

#### **Resetting Faults**

Faults are reset with any of the following conditions. First, writing zeros to the FAULT register B will clear the associated fault bits. Second, the entire FAULT register is cleared when either the ON pin or bit D3 goes from high to low, or if  $INTV_{CC}$  falls below its 4.25V undervoltage lockout. Pulling the UVL pin below its 1.21V reset threshold also clears the entire FAULT register. When the UVL pin is brought back above 1.21V but below 2.291V, the undervoltage fault bit B1 is set if the UVH pin is below 2.56V. This can be avoided by holding the UVH pin above 2.56V while toggling the UVL pin to reset faults. Finally, when  $\overline{EN}$  is brought from high to low, all fault bits except bit B4 are cleared. The bit B4 that indicates an  $\overline{EN}$  change of state will be set.

Fault bits with associated conditions that are still present (as indicated in the STATUS Register A) cannot be cleared. The FAULT register will not be cleared when auto-retrying. When auto-retry is disabled, the existence of B0 (overvoltage), B1 (undervoltage), B2 (overcurrent) or B3 (power bad) fault keeps the FET off. After the fault bit is cleared and a delay of  $t_D$  (for B0, B1 and B3) or  $4t_D$ (for B4) expires, the FET will turn on again. Note that if the overvoltage fault bit B0 is cleared by writing a zero through I<sup>2</sup>C, the FET is allowed to turn on without a delay. If auto-retry is enabled, then a high value in A0, A1, A2 or A3 will hold the FET off and the FAULT register is ignored. Subsequently, when the A0, A1, A2 and A3 bits are cleared, the FET is allowed to turn on again.

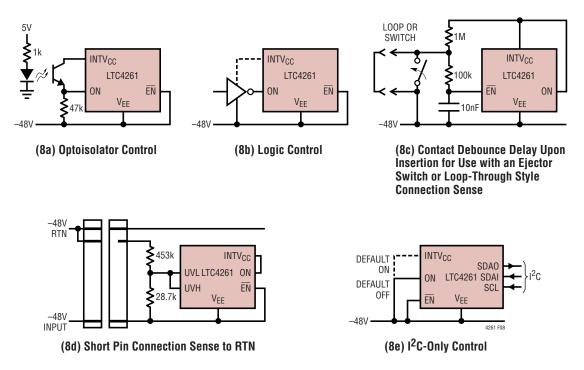

#### Turning the LTC4261 On and Off

Many methods of on/off control are possible using the ON, EN, UV/OV, FLTIN or PGIO pins along with the I<sup>2</sup>C port. The EN pin works well with logic inputs or floating switch contacts; I<sup>2</sup>C control is intended for systems where the board operates only under command of a central control processor and the ON pin is useful with signals referenced to RTN, as are the UV (UVH, UVL) and OV pins. PGIO and FLTIN control nothing directly, but are useful for I<sup>2</sup>C monitoring of connection sense or other important signals.

On/off control is possible with or without  $I^2C$  intervention. Further, the LTC4261 may reside on either the removable board or on the backplane. Even when operating autonomously, the  $I^2C$  port can still exercise control over the GATE output, although depending on how they are connected, EN and ON could subsequently override conditions set by  $I^2C$ . UV, OV and other fault conditions seize control as needed to turn off the GATE output, regardless of the state of EN, ON or the  $I^2C$  port. Figure 8 shows five configurations of on/off control of the LTC4261.

Determining factors in selecting a pin configuration for autonomous operation are the polarity and voltage of the controlling signal.

**Optical Isolation**. Figure 8a shows an optoisolator driving the ON pin. Rising and falling edges at the ON pin turn the GATE output on and off. If ON is already high when power is applied, GATE is delayed one  $t_D$  period. The status of ON can be examined or overridden through the I<sup>2</sup>C port at register bit D3. This circuit works in both backplane and board resident applications.

**Logic Control**. Figure 8b shows an application using logic signal control. Again, the ON pin is used as an input; all remarks made concerning optoisolator control apply here as well.

**Ejector Switch or Loop-Through Connection Sense**. Floating switch contacts or a connection sense loop also work well with the ON pin, replacing the phototransistor in Figure 8a. If an insertion debounce delay is desired,

use the EN pin as shown in Figure 8c. Like Figures 8a and 8b, this circuit works on either side of the backplane connector.

**Short Pin to RTN**. Figure 8d uses the UV divider string to detect board insertion. This method works equally well in both backplane and board resident applications.

**AdvancedTCA Style Control**. Figure 2 shows an ATCA application using  $\overline{EN}$  as the interface to the LTC4261. Register bit A4 allows the I<sup>2</sup>C port to monitor the status of  $\overline{EN}$  and by setting C4 high, bit B4 can generate an alert to instantly report any changes in the state of  $\overline{EN}$ .

**I<sup>2</sup>C Only Control**. To lock out  $\overline{EN}$  and ON, use the configuration shown in Figure 8e and control the GATE pin with register bit D3. The circuit defaults off at power up. To default on, connect the ON pin to INTV<sub>CC</sub>. Either FLTIN or PGIO can be used as an input to monitor a connection sense or other control signal. PGIO is configured as an input by setting register bits D6 and D7 high; its input state is stored at location B6. FLTIN is always an input whose state is available from register bit B7. FLTIN generates an alert if C7 is set high.

#### **Data Converter**

The LTC4261 incorporates a 10-bit analog-to-digital converter (ADC) that continuously monitors three different voltages at (in the sequence of) SENSE, ADIN2/OV (SSOP/QFN) and ADIN. The voltage between the SENSE pin and V<sub>EE</sub> is monitored with a 64mV full scale and 62.5 $\mu$ V resolution, and the data is stored in registers E and F. The ADIN and the ADIN2/OV pins are monitored with a 2.56V full scale and 2.5mV resolution. The data for the ADIN2/OV pin is stored in registers G and H. The data for the ADIN pin is stored in registers I and J.

The results in registers E, F, G, H, I and J are updated at a frequency of 7.3Hz. Setting CONTROL register bit D5 invokes a test mode that halts updating of these registers so that they can be written to and read from for software testing.

The ADIN and ADIN2 pins can be used to monitor input and output voltages of the Hot Swap controller as shown in Figures 1 and 2.

Figure 8. On/Off Control of the LTC4261

#### **Configuring the PGIO Pin**

Table 6 describes the possible states of the PGIO pin using the CONTROL register bits D6 and D7. At power-up the default state is for the PGIO pin to pull low when the second power good signal is ready. Other uses for the PGIO pin are to go high impedence when the second power good is ready, a general purpose output and a general purpose input. When the PGIO pin is configured as a general purpose output, the status of bit C6 is sent out to the pin. When it is configured as a general purpose input, if the input voltage at PGIO is higher than 1.25V, both bit A6 in the STATUS register and bit B6 in the FAULT register are set. If the input voltage at PGIO subsequently drops below 1.25V, bit A6 is cleared. Bit B6 can be cleared by resetting the FAULT register as described previously.

#### **Design Example**

As a design example, consider the 200W application with  $C_L = 330\mu F$  as shown in Figure 1. The operating voltage range is from 43V to 71V with a UV turn-off threshold of 38.5V.

The design flow starts with calculating the maximum input current:

$$I_{MAX} = \frac{200W}{36V} = 5.6A$$

where 36V is the minimum input voltage.

The selection of the sense resistor,  $R_S$ , is determined by the minimum current limit threshold and maximum input current:

$$R_{S} = \frac{\Delta V_{SENSE(MIN)}}{I_{MAX}} = \frac{45mV}{5.6A} = 8m\Omega$$

The inrush current is set to 0.66A using C<sub>R</sub>:

$$C_{R} = C_{L} \bullet \frac{I_{RAMP}}{I_{INRUSH}} = 330 \mu F \bullet \frac{20 \mu A}{0.66 A} = 10 n F$$

The value of  $R_{\text{F}}$  and  $C_{\text{F}}$  are chosen to 1k and 33nF as discussed previously.

The FET is selected to handle the maximum power dissipation during start-up or an input step. The latter usually results in a larger power due to summation of the inrush current charging  $C_L$  and the load current. For a 36V input step, the maximum  $P^2t$  in the FET is approximated by:

$$\mathsf{P}^2\mathsf{t} = \left(36\mathsf{V} \bullet \mathsf{I}_{\mathsf{MAX}}\right)^2 \bullet \frac{\mathsf{t}}{3}$$

where t is the time it takes to charge up  $C_L$ :

$$t = \frac{C_L \cdot 36V}{I_{INRUSH}} = \frac{330\mu F \cdot 36V}{0.66A} = 18ms$$

which gives a  $P^2t$  value of  $244W^2s$ .

Now the P<sup>2</sup>t given by the SOA (safe operating area) curves of candidate FETs must be lower than  $244W^2s$ . The SOA curves of the IRF1310NS provide for 5A at 50V (250W) for 10ms, which gives a P<sup>2</sup>t value of  $625W^2s$  and satisfies the requirement.

Sizing R1, R2 and R3 for the required UV and OV threshold voltages:

$$V_{UV(RISING)} = 43V$$

,  $V_{UV(FALLING)} = 38.5V$ , (using  $V_{UVH(TH)} = 2.56V$  and  $V_{UVH(TH)} = 2.291V$ )

$V_{OV(RISING)}$  = 72.3V,  $V_{OV(FALLING)}$  = 70.7V (using  $V_{OV(TH)}$  = 1.77V rising and 1.7325V falling)

#### **Layout Considerations**

To achieve accurate current sensing, a Kelvin connection is recommended. The minimum trace width for 1oz copper foil is 0.02" per amp to make sure the trace stays at a reasonable temperature. Using 0.03" per amp or wider is recommended. Note that 1oz copper exhibits a sheet resistance of about  $530\mu\Omega$ /square. Small resistances add up quickly in high current applications. To improve noise immunity, put the resistive divider to the UV and OV pins close to the chip and keep traces to V<sub>IN</sub> and V<sub>EE</sub> short. A 0.1µF capacitor from the UVH or UVL pin (and OV pin through resistor R2) to V<sub>EE</sub> helps reject supply noise.

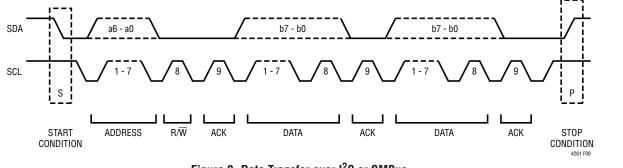

#### I<sup>2</sup>C Interface

The LTC4261 features an I<sup>2</sup>C interface to provide access to the ADC data registers and four other registers for monitoring and control of the pass FET. Figure 9 shows a general data transfer format using the I<sup>2</sup>C. The LTC4261 is a read-write slave device and supports SMBus bus Read Byte, Write Byte, Read Word and Write Word commands. The second word in a Read Word command will be identical to the first word. The second word in a Write Word command is ignored. The data formats for these commands are shown in Figures 10 to 13.

#### Using Optoisolators with SDA

The LTC4261 splits the SDA line into SDAI (input) and SDAO (output) for convenience of opto-coupling with the host. If optoisolators are not used then tie SDAI and SDAO together to form a normal SDA line. When using optoisolators, connect the SDAI to the output of the incoming optoisolator and connect the SDAO to the input of the outgoing optoisolator (see Figure 2). If the ALERT line is used as an interrupt for the host to respond to a fault in real time, connect the ALERT to an optoisolator in a way similar to that for the SDAO as shown in Figure 2.

#### START and STOP Conditions

When the bus is idle, both SCL and SDA must be high. A bus master signals the beginning of a transmission with a START condition by transiting SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP condition by transiting SDA from low to high while SCL is high. The bus is then free for another transmission.

#### Stuck-Bus Reset

The LTC4261 I<sup>2</sup>C interface features a stuck-bus reset timer. The low conditions of the SCL and the SDAI pins are ORed to start the timer. The timer is reset when both SCL and SDAI are pulled high. If the SCL pin or the SDAI pin is held low for over 66ms, the stuck-bus timer will expire and the internal I<sup>2</sup>C state machine will be reset

| S ADDRESS W A COMMAND A DATA A P                                                                          | S ADDRESS W A COMMAND A DATA A DATA A                   |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 0 0 1 a3:a0 0 0 X X X X b3:b0 0 b7:b0 0                                                                   | 0 0 1 a3:a0 0 0 X X X X b3:b0 0 b7:b0 0 X X X X X X X 0 |

| FROM MASTER TO SLAVE A: ACKNOWLEDGE (LOW) A: NOT ACKNOWLEDGE (HIGH) R: READ BIT (HIGH) W: WRITE BIT (LOW) | ** Figure 11. LTC4261 Serial Bus SDA Write Word Protoco |

| S: START CONDITION                                                                                        | S ADDRESS W A COMMAND A S ADDRESS R A DATA A            |

| P: STOP CONDITION                                                                                         | 0 0 1 a3:a0 0 0 X X X X b3:b0 0 00 1 a3:a0 1 0 b7:b0 1  |

Figure 10. LTC4261 Serial Bus SDA Write Byte Protocol

Figure 12. LTC4261 Serial Bus SDA Read Byte Protocol

| S | ADDRESS     | W | A | COMMAND       | A | S | ADDRESS     | R | A | DATA  | A | DATA  | Ā | Р |

|---|-------------|---|---|---------------|---|---|-------------|---|---|-------|---|-------|---|---|

|   | 0 0 1 a3:a0 | 0 | 0 | X X X X b3:b0 | 0 |   | 0 0 1 a3:a0 | 1 | 0 | b7:b0 | 0 | b7:b0 | 1 |   |

Figure 13, LTC4261 Serial Bus SDA Read Word Protocol

### LTC4261

### **APPLICATIONS INFORMATION**

to allow normal communication after the stuck-low condition is cleared. When the SCL pin and the SDAI pin are held low alternatively, if the ORed low period of SCL and SDAI exceeds 66ms before the timer reset condition (both SCL and SDAI are high) occurs, the stuck-bus timer will expire and the  $I^2C$  state machine is reset.

### I<sup>2</sup>C Device Addressing

Any of eight distinct  $I^2C$  bus addresses are selectable using the three-state pins ADR0 and ADR1, as shown in Table 1. Note that the configuration of ADR0 = L and ADR1 = H is used to enable the single-wire broadcasting mode. For the eight  $I^2C$  bus addresses, address bits B6, B5 and B4 are configured to (001) and the least significant bit B0 is the R/W bit. In addition, the LTC4261 will respond to two special addresses. Address (0011 111) is a mass write used to write to all LTC4261s, regardless of their individual address settings. Address (0001 100) is the SMBus Alert Response Address. If the LTC4261 is pulling low on the ALERT pin, it will acknowledge this address using the SMBus Alert Response Protocol.

#### Acknowledge

The acknowledge signal is used for handshaking between the transmitter and the receiver to indicate that the last byte of data was received. The transmitter always releases the SDA line during the acknowledge clock pulse. When the slave is the receiver, it must pull down the SDA line so that it remains LOW during this pulse to acknowledge receipt of the data. If the slave fails to acknowledge by leaving SDA HIGH, then the master can abort the transmission by generating a STOP condition. When the master is receiving data from the slave, the master must pull down the SDA line during the clock pulse to indicate receipt of the data. After the last byte has been received the master will leave the SDA line HIGH (not acknowledge) and issue a STOP condition to terminate the transmission.

### Write Protocol

The master begins communication with a START condition followed by the seven bit slave address and the R/W bit set to zero. The addressed LTC4261 acknowledges this and then the master sends a command byte which indicates which internal register the master wishes to write. The LTC4261 acknowledges this and then latches the lower four bits of the command byte into its internal Register Address pointer. The master then delivers the data byte and the LTC4261 acknowledges once more and latches the data into its internal register. The transmission is ended when the master sends a STOP condition. If the master continues sending a second data byte, as in a Write Word command, the second data byte will be acknowledged by the LTC4261 but ignored.

### **Read Protocol**

The master begins a read operation with a START condition followed by the seven bit slave address and the R/W bit set to zero. The addressed LTC4261 acknowledges this and then the master sends a command byte that indicates which internal register the master wishes to read. The LTC4261 acknowledges this and then latches the lower four bits of the command byte into its internal Register Address pointer. The master then sends a repeated START condition followed by the same seven bit address with the R/W bit now set to one. The LTC4261 acknowledges and sends the contents of the requested register. The transmission is ended when the master sends a STOP condition. If the master acknowledges the transmitted data byte, as in a Read Word command, the LTC4261 will repeat the requested register as the second data byte. Note that the Register Address pointer is not cleared at the end of the transaction. Thus the Receive Byte protocol can be used to repeatedly read a specific reaister.

#### **Alert Response Protocol**

The LTC4261 implements the SMBus Alert Response Protocol as shown in Figure 14. If enabled to do so through the ALERT register C, the LTC4261 will respond to faults by pulling the ALERT pin low. Multiple LTC4261s can share a common ALERT line and the protocol allows a master to determine which LTC4261s are pulling the line low. The master begins by sending a START bit followed by the special Alert Response Address (0001 100)b with the R/W bit set to one. Any LTC4261 that is pulling its ALERT pin low will acknowledge and begin sending back its individual slave address.

| s | ALERT<br>RESPONSE<br>ADDRESS | R | A | DEVICE<br>Address | Ā   | P     |

|---|------------------------------|---|---|-------------------|-----|-------|

|   | 0001100                      | 1 | 0 | 0 0 1 a3:a0 0     | 1   |       |

|   |                              |   |   |                   | 400 | 0.014 |

Figure 14. LTC4261 Serial Bus SDA Alert Response Protocol

An arbitration scheme ensures that the LTC4261 with the lowest address will have priority; all others will abort their response. The successful responder will then release its ALERT pin while any others will continue to hold their ALERT pins low. Polling may also be used to search for any LTC4261 that have detected faults. Any LTC4261 pulling its ALERT pin low will also release it if it is individually addressed during a read or write transaction.

The ALERT signal will not be pulled low again until the FAULT register indicates a different fault has occurred or the original fault is cleared and it occurs again. Note that this means repeated or continuing faults will not generate alerts until the associated FAULT register bit has been cleared.

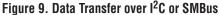

#### **Single-Wire Broadcast Mode**