LT1015

# High Speed Dual Line Receiver

#### **OBSOLETE:**

FOR INFORMATION PURPOSES ONLY

Contact Linear Technology for Potential Replacement

#### **FEATURES**

- Response Time: 10ns

- Setup Time for Latch: 2ns

- Operates on Single 5V Supply

- Dual Function in 8-Pin Package

- No Input Slew Rate Requirement

- Latch Function Included on Chip

- True Differential Inputs

#### **APPLICATIONS**

- High Speed Differential Line Receiver

- Pulse Height/Width Discriminator

- Timing and Delay Generators

- Analog to Digital Interface

#### DESCRIPTION

The LT®1015 is a dual high speed comparator intended for line receiver and other general purpose fast comparator functions. It has 10ns response time, true differential inputs, TTL outputs and operates from a single 5V supply. A unique output stage design virtually eliminates power supply glitching during transitions. This greatly reduces instability and crosstalk problems in multiple line applications. No minimum input slew rate is required as in previous TTL output comparators.

The LT1015 has a true Latch pin for retaining output data. Setup time is 2ns, allowing the comparators to capture data much faster than the actual flowthrough response time. 8-pin miniDIP and ceramic packages allow high packing density.

7, LTC and LT are registered trademarks of Linear Technology Corporation.

# TYPICAL APPLICATION

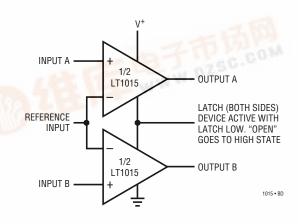

## **BLOCK DIAGRAM**

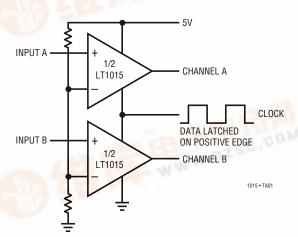

### 2-Channel 20MHz Clocked Line Receiver

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage 7V                    |

|--------------------------------------|

| Differential Input Voltage 5V        |

| Input Voltage                        |

| Positive Supply + 0.5V               |

| Negative1V                           |

| Input Current (Forced) Positive      |

| Latch Pin Voltage Supply + 1V        |

| Output Current (Continuous)±20mA     |

| Operating Temperature Range          |

| LT1015C 0°C to 70°C                  |

| LT1015M –55°C to 125°C*              |

| Storage Temperature65°C to 150°C     |

| Lead Temperature (Soldering, 10 sec) |

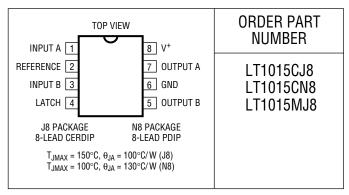

#### PACKAGE/ORDER INFORMATION

Consult factory for Industrial grade parts.

#### **ELECTRICAL CHARACTERISTICS**

$V^+ = 4.6V$  to 5.4V,  $V_{LATCH} = 0V$ , common mode input voltage = 2.5V,  $T_J = 25^{\circ}C$ , unless otherwise noted.

| PARAMETER                        | CONDITIONS                                                            |   | MIN      | TYP      | MAX  | UNITS |

|----------------------------------|-----------------------------------------------------------------------|---|----------|----------|------|-------|

| Input Offset Voltage (Note 1)    | V <sub>CM</sub> = 1.25V to (V + – 1.5V)                               | • |          | 1        | 20   | mV    |

| Input Bias Current               | $\Delta V_{IN} = 0V \text{ (Note 2)}$                                 | • |          | 15       | 30   | μΑ    |

| Reference Input Current          | $\Delta V_{IN} = 0V \text{ (Note 2)}$                                 | • |          | 30       | 60   | μΑ    |

| Voltage Gain (Note 3)            | V <sub>OUT</sub> = 0.5V to 2.5V, Load = 1 TTL Gate                    | • | 1000     | 2500     |      | V/V   |

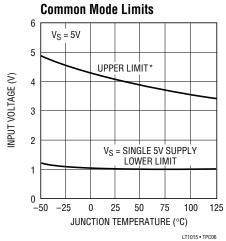

| Common Mode Input Range (Note 5) | Minimum Input                                                         | • |          | 1.0      | 1.25 | V     |

|                                  | Maximum Input                                                         | • | V+ - 1.5 | V+ - 1.0 |      | V     |

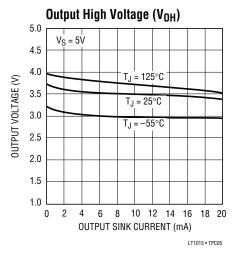

| Output High Voltage              | I <sub>OUT</sub> = 4mA                                                | • | 2.5      |          |      | V     |

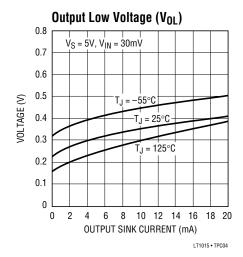

| Output Low Voltage               | I <sub>SINK</sub> = 4mA                                               | • |          | 0.3      | 0.5  | V     |

| Supply Current                   | V + = 5V                                                              | • |          | 55       | 70   | mA    |

| Latch Pin High Input Voltage     | Device Latched                                                        | • |          |          | 2    | V     |

| Latch Pin Low Input Voltage      | Device Active                                                         | • | 0.8      |          |      | V     |

| Latch Pin Current                |                                                                       | • |          |          | 1    | mA    |

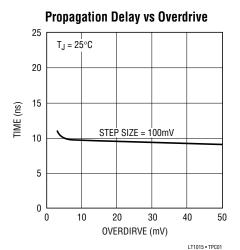

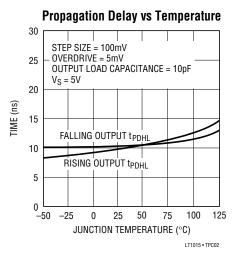

| Propagation Delay                | $\Delta V_{IN} \ge 20 \text{mV (Note 4)}$                             |   |          |          |      |       |

|                                  | $0^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 100^{\circ}\text{C}$ | • | 7        | 10       | 14   | ns    |

|                                  | -55°C ≤ T <sub>J</sub> ≤ 150°C                                        | • | 7        | 10       | 16   | ns    |

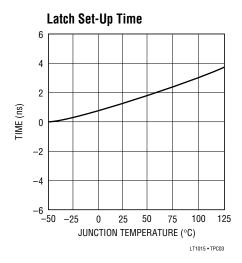

| Latch Setup Time                 |                                                                       |   |          | 2        |      | ns    |

The ● denotes specifications which apply over the full operating temperature range.

**Note 1:** Input offset voltage is the maximum required to drive the output to a low state of 0.5V and high state of 2.5V.

**Note 2:** Input currents are measured by applying a large positive differential input voltage. The resulting input current is divided by two to obtain input current at  $\Delta V_{\text{IN}} = 0V$ .

Note 3: Voltage gain is guaranteed by design, but not tested.

**Note 4:** Propagation delay is sample tested in production with a large overdrive. The limit is guard banded to account for the slight increase ( $\approx 500$ ps) at 20mV overdrive.

**Note 5:** Common mode input range is the voltage range over which the differential input offset voltage is less than 20mV. If both inputs remain inside this common mode range, propagation delay will be unaffected. It will also be normal if the signal input is below the 1.25V lower limit when the input transition begins. An increase in propagation delay of up to 10ns may occur if the signal input is above the upper common mode limit when the transition begins. Sine wave inputs may not be affected when the peak exceeds the common mode range if the signal is inside the common mode range for 10ns before threshold is reached.

# TYPICAL PERFORMANCE CHARACTERISTICS

\* UPPER LIMIT TRACKS 5V SUPPLY. 4.1V LIMIT AT 25 °C WILL DROP TO 3.8V WHEN  $V_S = 4.7V$

PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

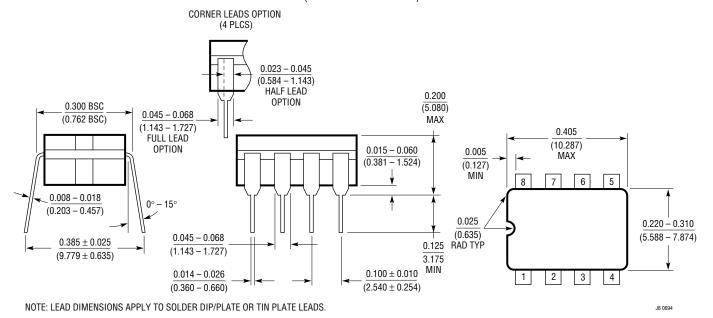

#### J8 Package 8-Lead CERDIP (Narrow 0.300, Hermetic)

(LTC DWG # 05-08-1110)

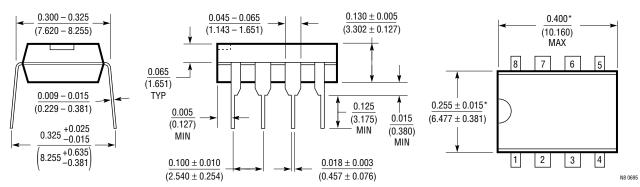

#### **N8 Package** 8-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                   | COMMENTS                                                    |

|-------------|-----------------------------------------------|-------------------------------------------------------------|

| LT1016      | Ultrafast Precision Comparator                | 10ms Propagation Delay, Complimentary TTL Outputs           |

| LT1116      | 12ns, Single-Supply Ground Sensing Comparator | Inputs Can Exceed Positive Supply Up to 15V                 |

| LTC®1520    | 50Mbits/s Precision Quad Line Driver          | 18ns Propagation Delay Over Temperature Rail-to-Rail Inputs |