# LTC1326/LTC1326-2.5

# Micropower Precision Triple Supply Monitors

#### **FEATURES**

- Simultaneously Monitors Three Supplies LTC1326: 5V, 3.3V and ADJ LTC1326-2.5: 2.5V, 3.3V and ADJ

- Guaranteed Threshold Accuracy: ±0.75%

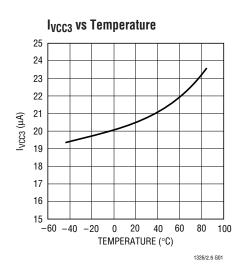

- Low Supply Current: 20µA

- Internal Reset Time Delay: 200ms

- Manual Push-Button Reset Input

- Active Low and Active High Reset Outputs

- Active Low "Soft" Reset Output

- Power Supply Glitch Immunity

- Guaranteed RESET for V<sub>CC3</sub> ≥ 1V or V<sub>CC5</sub> ≥ 1V or V<sub>CC25</sub> ≥ 1V

- 8-Pin SO and MSOP Packages

#### **APPLICATIONS**

- Desktop Computers

- Notebook Computers

- Intelligent Instruments

- Portable Battery-Powered Equipment

# DESCRIPTION

The LTC®1326/LTC1326-2.5 are triple supply monitors intended for systems with multiple supply voltages. They provide micropower operation, small size and high accuracy supply monitoring.

Tight 0.75% threshold accuracy and glitch immunity ensure reliable reset operation without false triggering. The  $20\mu A$  typical supply current makes the LTC1326/LTC1326-2.5 ideal for power-conscious systems.

The RST output is guaranteed to be in the correct state for  $V_{CC3}$ ,  $V_{CC5}$  or  $V_{CC25}$  down to 1V. The LTC1326/LTC1326-2.5 can be configured to monitor one, two or three inputs, depending on system requirements.

A manual push-button reset input provides the ability to generate a very narrow "soft" reset pulse (100µs typ) or a 200ms reset pulse equivalent to a power-on reset. Both SRST and RST outputs are open-drain and can be OR-tied with other reset sources.

7, LTC and LT are registered trademarks of Linear Technology Corporation.

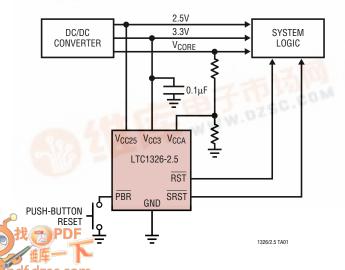

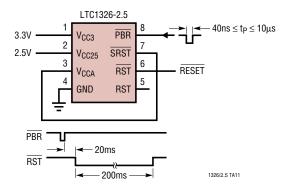

# TYPICAL APPLICATION

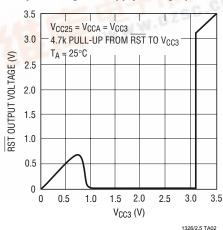

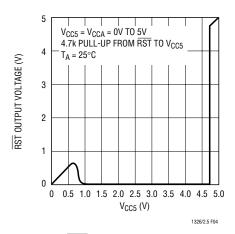

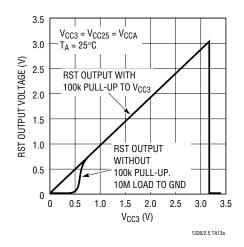

#### RST Output Voltage vs Supply Voltage (LTC1326-2.5)

## **ABSOLUTE MAXIMUM RATINGS**

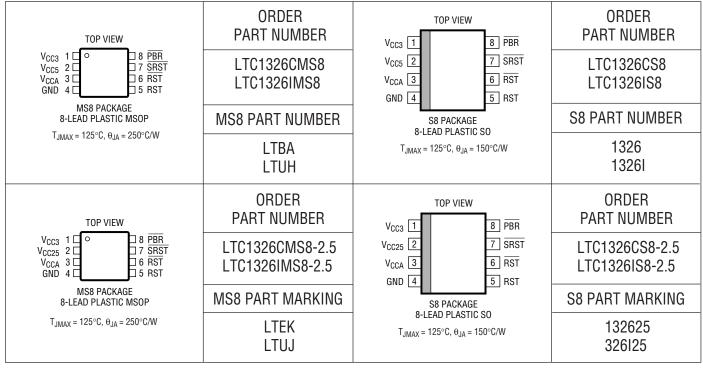

# PACKAGE/ORDER INFORMATION

PBR ...... -7V to 7V

Consult factory for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC3} = 3.3V$ ,  $V_{CC5} = 5V$  (for LTC1326),  $V_{CC25} = 2.5V$  (for LTC1326-2.5),  $V_{CC3} = V_{CC3}$ ,  $T_A = 25^{\circ}C$  unless otherwise noted.

| SYMBOL            | PARAMETER                                       | CONDITIONS                                                                                                          |   | MIN            | TYP            | MAX            | UNITS |

|-------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|-------|

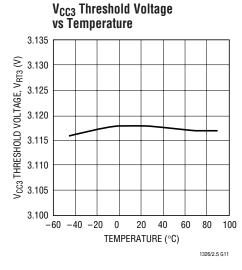

| V <sub>RT3</sub>  | Reset Threshold V <sub>CC3</sub>                | $ \begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq 85^{\circ}C \end{array} $ | • | 3.094<br>3.052 | 3.118<br>3.118 | 3.135<br>3.143 | V     |

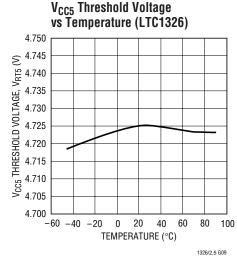

| V <sub>RT5</sub>  | Reset Threshold V <sub>CC5</sub> (LTC1326)      | $ \begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq 85^{\circ}C \end{array} $ | • | 4.687<br>4.625 | 4.725<br>4.725 | 4.750<br>4.762 | V     |

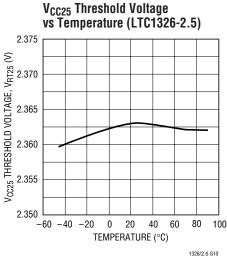

| V <sub>RT25</sub> | Reset Threshold V <sub>CC25</sub> (LTC1326-2.5) | $ \begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq 85^{\circ}C \end{array} $ | • | 2.344<br>2.312 | 2.363<br>2.363 | 2.375<br>2.381 | V     |

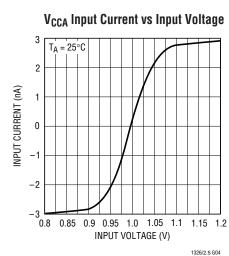

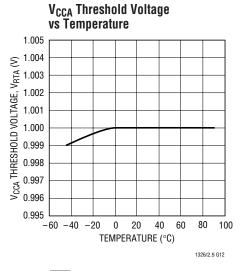

| V <sub>RTA</sub>  | Reset Threshold V <sub>CCA</sub>                | $ \begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq 85^{\circ}C \end{array} $ | • | 0.992<br>0.980 | 1.000<br>1.000 | 1.007<br>1.007 | V     |

| V <sub>CC</sub>   | V <sub>CC3</sub> Operating Voltage              | RST in Correct Logic State                                                                                          | • | 1              |                | 7              | V     |

| I <sub>VCC3</sub> | V <sub>CC3</sub> Supply Current                 | PBR = V <sub>CC3</sub>                                                                                              | • |                | 20             | 40             | μА    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25\,^{\circ}\text{C}$ .  $V_{CC3} = 3.3V$ ,  $V_{CC5} = 5V$  (for LTC1326),  $V_{CC25} = 2.5V$  (for LTC1326-2.5),  $V_{CCA} = V_{CC3}$ ,  $T_A = 25\,^{\circ}\text{C}$  unless otherwise noted.

| SYMB0L             | PARAMETER                                                      | CONDITIONS                                                                                                                     |                                                                                                                                                 |   | MIN                  | TYP                  | MAX               | UNITS                    |

|--------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|----------------------|-------------------|--------------------------|

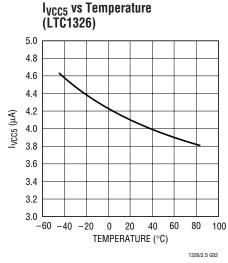

| I <sub>VCC5</sub>  | V <sub>CC5</sub> Input Current (LTC1326)                       | V <sub>CC5</sub> = 5V                                                                                                          |                                                                                                                                                 | • |                      | 4                    | 7                 | μА                       |

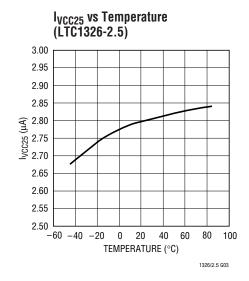

| I <sub>VCC25</sub> | V <sub>CC25</sub> Input Current (LTC1326-2.5)                  | V <sub>CC25</sub> = 2.5V                                                                                                       |                                                                                                                                                 | • |                      | 2.8                  | 7                 | μА                       |

| I <sub>VCCA</sub>  | V <sub>CCA</sub> Input Current                                 | $V_{CCA} = 1V$ $0^{\circ}C \le T_A \le 70^{\circ}C$ $-40^{\circ}C \le T_A \le 85^{\circ}C$                                     |                                                                                                                                                 | • | -5<br>-15            | 0                    | 5<br>15           | nA<br>nA                 |

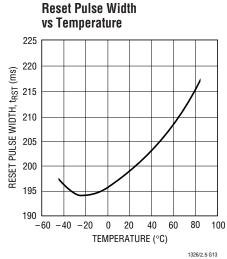

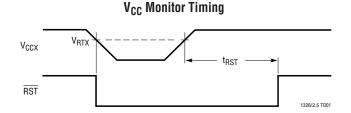

| t <sub>RST</sub>   | Reset Pulse Width                                              | $\overline{RST}$ Low with 10kΩ Pull-Up to V <sub>CC3</sub><br>0°C ≤ T <sub>A</sub> ≤ 70°C<br>-40°C ≤ T <sub>A</sub> ≤ 85°C     |                                                                                                                                                 | • | 140<br>140           | 200<br>200           | 280<br>300        | ms<br>ms                 |

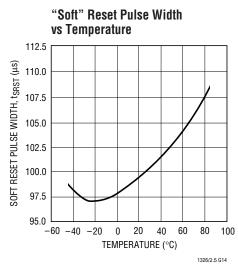

| t <sub>SRST</sub>  | Soft Reset Pulse Width                                         | SRST Low with 10kΩ                                                                                                             | Pull-Up to V <sub>CC3</sub>                                                                                                                     | • | 50                   | 100                  | 200               | μs                       |

| t <sub>UV</sub>    | V <sub>CC</sub> Undervoltage Detect to RST                     | V <sub>CC25</sub> , V <sub>CC3</sub> or V <sub>CCA</sub> I<br>Threshold V <sub>RT</sub> by Mo                                  |                                                                                                                                                 |   |                      | 13                   |                   | μS                       |

| I <sub>PBR</sub>   | PBR Pull-Up Current                                            | $\overline{PBR} = 0V$ $0^{\circ}C \le T_{A} \le 70^{\circ}C$ $-40^{\circ}C \le T_{A} \le 85^{\circ}C$                          |                                                                                                                                                 | • | 3<br>3               | 7<br>7               | 10<br>15          | μ <b>Α</b><br>μ <b>Α</b> |

| V <sub>IL</sub>    | PBR, RST Input Low Voltage                                     |                                                                                                                                |                                                                                                                                                 | • |                      |                      | 0.8               | V                        |

| V <sub>IH</sub>    | PBR, RST Input High Voltage                                    |                                                                                                                                |                                                                                                                                                 | • | 2                    |                      |                   | V                        |

| t <sub>PW</sub>    | PBR Min Pulse Width                                            |                                                                                                                                |                                                                                                                                                 | • | 40                   |                      |                   | ns                       |

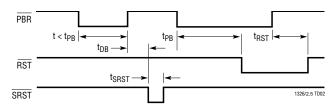

| t <sub>DB</sub>    | PBR Debounce                                                   | Deassertion of PBR Input to SRST Output (PBR Pulse Width = 1µs)                                                                |                                                                                                                                                 | • |                      | 20                   | 35                | ms                       |

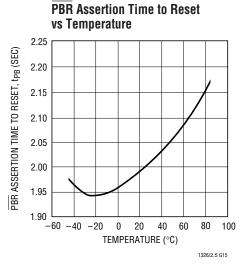

| t <sub>PB</sub>    | PBR Assertion Time for Transition from Soft to Hard Reset Mode | $\overline{PBR}$ Held Less Than $V_{IL}$<br>$0^{\circ}C \leq T_A \leq 70^{\circ}C$<br>$-40^{\circ}C \leq T_A \leq 85^{\circ}C$ |                                                                                                                                                 | • | 1.4<br>1.4           | 2.0<br>2.0           | 2.8<br>3.0        | S<br>S                   |

| $V_{OL}$           | RST Output Voltage Low                                         | I <sub>SINK</sub> = 5mA                                                                                                        |                                                                                                                                                 | • |                      | 0.15                 | 0.4               | V                        |

|                    |                                                                | $\begin{split} I_{SINK} &= 100 \mu A, \\ 0^{\circ}C &\leq T_{A} \leq 70^{\circ}C \end{split}$                                  | V <sub>CC3</sub> = 1V, V <sub>CC5</sub> = 0V<br>V <sub>CC3</sub> = 0V, V <sub>CC5</sub> = 1V<br>V <sub>CC3</sub> = 1V, V <sub>CC5</sub> = 1V    | • |                      | 0.05<br>0.05<br>0.05 | 0.4<br>0.4<br>0.4 | V<br>V<br>V              |

|                    |                                                                | $I_{SINK}$ = 100 $\mu$ A,<br>-40°C $\leq$ T <sub>A</sub> $\leq$ 85°C                                                           | $V_{CC3} = 1.1V, V_{CC5} = 0V$ $V_{CC3} = 0V, V_{CC5} = 1.1V$ $V_{CC3} = 1.1V, V_{CC5} = 1.1V$                                                  | • |                      | 0.05<br>0.05<br>0.05 | 0.4<br>0.4<br>0.4 | V<br>V<br>V              |

|                    |                                                                | $I_{SINK}$ = 100 $\mu$ A,<br>0°C $\leq$ T <sub>A</sub> $\leq$ 70°C                                                             | V <sub>CC3</sub> = 1V, V <sub>CC25</sub> = 0V<br>V <sub>CC3</sub> = 0V, V <sub>CC25</sub> = 1V<br>V <sub>CC3</sub> = 1V, V <sub>CC25</sub> = 1V | • |                      | 0.05<br>0.05<br>0.05 | 0.4<br>0.4<br>0.4 | V<br>V<br>V              |

|                    |                                                                | $I_{SINK} = 100\mu A,$<br>$-40^{\circ}C \le T_A \le 85^{\circ}C$                                                               | $V_{CC3} = 1.1V, V_{CC25} = 0V$ $V_{CC3} = 0V, V_{CC25} = 1.1V$ $V_{CC3} = 1.1V, V_{CC25} = 1.1V$                                               | • |                      | 0.05<br>0.05<br>0.05 | 0.4<br>0.4<br>0.4 | V<br>V                   |

|                    | SRST Output Voltage Low                                        | I <sub>SINK</sub> = 2.5mA                                                                                                      |                                                                                                                                                 | • |                      | 0.15                 | 0.4               | V                        |

|                    | RST Output Voltage Low                                         | I <sub>SINK</sub> = 2.5mA                                                                                                      |                                                                                                                                                 | • |                      | 0.15                 | 0.4               | V                        |

| V <sub>OH</sub>    | RST Output Voltage High (Note 3)                               | I <sub>SOURCE</sub> = 1μA<br>I <sub>SOURCE</sub> = 1μA                                                                         |                                                                                                                                                 | • | V <sub>CC3</sub> – 1 |                      |                   | V                        |

|                    | SRST Output Voltage High (Note 3)                              |                                                                                                                                |                                                                                                                                                 | • | V <sub>CC3</sub> – 1 |                      |                   | V                        |

|                    | RST Output Voltage High                                        | I <sub>SOURCE</sub> = 600μA                                                                                                    |                                                                                                                                                 | • | V <sub>CC3</sub> – 1 |                      |                   | V                        |

| t <sub>PHL</sub>   | Prop Delay RST to RST<br>High Input to Low Output              | C <sub>RST</sub> = 20pF                                                                                                        |                                                                                                                                                 |   |                      | 25                   |                   | ns                       |

| t <sub>PLH</sub>   | Prop Delay RST to RST<br>Low Input to High Output              | C <sub>RST</sub> = 20pF                                                                                                        |                                                                                                                                                 |   |                      | 45                   |                   | ns                       |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . LTC1326 Only  $V_{CC3} = 3.3V$ ,  $V_{CC5} = 5V$ ,  $V_{CCA} = V_{CC3}$ ,  $T_A = 25^{\circ}C$  unless otherwise noted.

| SYMBOL           | PARAMETER                               | CONDITIONS                                               | MIN | TYP                     | MAX | UNITS |

|------------------|-----------------------------------------|----------------------------------------------------------|-----|-------------------------|-----|-------|

| V <sub>OVR</sub> | V <sub>CC5</sub> Reset Override Voltage | Override V <sub>CC5</sub> Ability to Assert RST (Note 4) |     | / <sub>CC3</sub> ±0.025 | )   | V     |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2: All voltage values are with respect to GND.

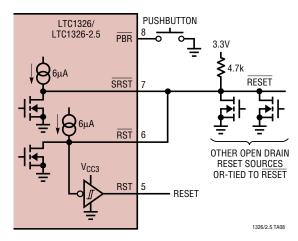

**Note 3:** The output pins  $\overline{SRST}$  and  $\overline{RST}$  have weak internal pull-ups to  $V_{CC3}$  of  $6\mu A$  typ. However, external pull-up resistors may be used when faster rise times are required.

**Note 4:** The  $V_{CC5}$  reset override voltage is valid for an operating range less than approximately 4.15V. Above this point the override is turned off and the  $V_{CC5}$  pin functions normally.

#### TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

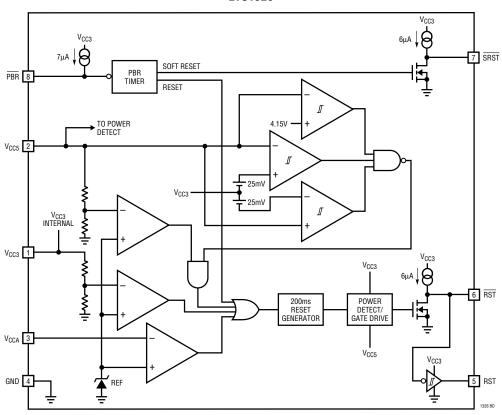

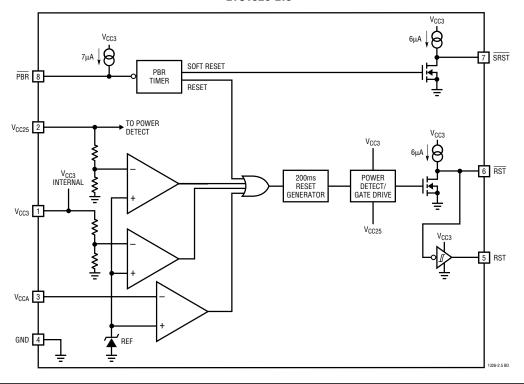

**V<sub>CC3</sub> (Pin 1):** 3.3V Sense Input and Power Supply Pin for the IC. Bypass to ground with  $\geq 0.1 \mu F$  ceramic capacitor.

$V_{CC5}$  (Pin 2) (LTC1326): 5V Sense Input. Used as gate drive for the RST output FET when the voltage on  $V_{CC3}$  is less than the voltage on  $V_{CC5}$ . If unused, it can be tied to  $V_{CC3}$  (see Dual and Single Supply Monitor Operation in the Applications Information section).

$V_{CC25}$  (Pin 2) (LTC1326-2.5): 2.5V Sense Input. Used as gate drive for RST output FET when the voltage on  $V_{CC3}$  is less than the voltage on  $V_{CC25}$ . If unused, it can be tied to  $V_{CC3}$ .

$V_{CCA}$  (Pin 3): 1V Sense, High Impedance Input. Can be used as a logic input with a 1V threshold. If unused, it can be tied to either  $V_{CC3}$  or  $V_{CC25}$ .

GND (Pin 4): Ground.

**RST (Pin 5):** Reset Logic Output. Active high CMOS <u>logic</u> output, drives high to  $V_{CC3}$ , buffered complement of RST. An external pull-down on the RST pin will drive this pin high.

**RST (Pin 6):** Reset Logic Output. Active low, open-drain logic output with weak pull-up to  $V_{CC3}$ . Can be pulled up greater than  $V_{CC3}$  when interfacing to 5V logic. Asserted when one or more of the supplies are below trip thresholds and held for 200ms after all supplies become valid. Also asserted after  $\overline{PBR}$  is held low for more than 2 seconds and for an additional 200ms after  $\overline{PBR}$  is released.

SRST (Pin 7): Soft Reset. Active low, open-drain logic output with weak pull-up to  $V_{CC3}$ . Can be pulled up greater than  $V_{CC3}$  when interfacing to 5V logic. Asserted for  $100\mu s$  after  $\overline{PBR}$  is held low for less than 2 seconds and released.

**PBR** (**Pin 8**): Push-Button Reset. Active low logic input with weak pull-up to  $V_{CC3}$ . Can be pulled up greater than  $V_{CC3}$  when interfacing to 5V logic. When asserted for less than 2 seconds, outputs a soft reset 100µs pulse on the SRST pin. When PBR is asserted for greater than 2 seconds, the RST output is forced low and remains low until 200ms after PBR is released.

# **BLOCK DIAGRAMS**

LTC1326

LTC1326-2.5

#### TIMING DIAGRAMS

#### **Push-Button Reset Function Timing**

#### APPLICATIONS INFORMATION

#### **Operation**

The LTC1326/LTC1326-2.5 are micropower, high accuracy triple supply monitoring circuits. The parts have two basic functions: generation of a reset when power supplies are out of <u>range</u>, and generation of reset or a "soft" reset when the <u>PBR</u> pin is pulled low.

#### **Supply Monitoring**

All three  $V_{CC}$  inputs must be above predetermined thresholds for 200ms before the reset output is released. The parts will assert reset during power-up, power-down and brownout conditions on any one or more of the  $V_{CC}$  inputs.

On power-up, either the  $V_{CC5}$  or  $V_{CC3}$  pin on the LTC1326, or the  $V_{CC25}$  or  $V_{CC3}$  pin on the LTC1326-2.5, can power the drive circuits for the RST pin. This ensures that RST will be low when  $V_{CC5}$ ,  $V_{CC25}$  or  $V_{CC3}$  reaches 1V. As long as any one of the  $V_{CC}$  inputs is below its predetermined threshold, RST will stay a logic low. Once all of the  $V_{CC}$  inputs rise above their thresholds, an internal timer is started and RST is released after 200ms. The RST pin outputs the inverted state of what is seen on RST pin.

RST is reasserted whenever any one of the  $V_{CC}$  inputs drops below its predetermined threshold and remains asserted until 200ms after all of the  $V_{CC}$  inputs are above their thresholds.

On power-down, once any of the  $V_{CC}$  inputs drop below its threshold, RST is held at a logic low. A logic low of 0.4V is guaranteed until  $V_{CC3}$  and  $V_{CC5}$  on the LTC1326 or  $V_{CC3}$  and  $V_{CC25}$  on the LTC1326-2.5 drop below 1V.

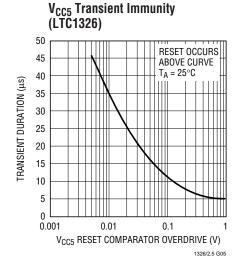

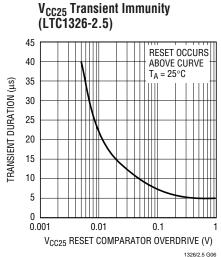

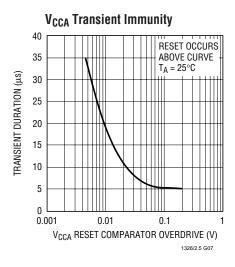

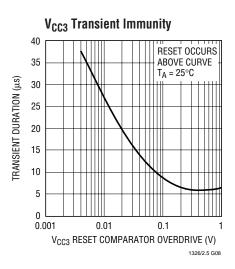

The three internal precision voltage comparators have response times that are typically 13 $\mu$ s. This slow response time helps prevent mistriggering due to transients on each of the V<sub>CC</sub> inputs. The part's ability to suppress transients can be improved by bypassing each of the V<sub>CC</sub> inputs with a 0.1 $\mu$ F capacitor to ground.

#### **Push-Button Reset**

The parts provide a push-button reset input pin. The PBR input has an internal pull-up current source to  $V_{CC3}$ . If the PBR pin is not used it can be left floating.

When the PBR is pulled low for less than  $t_{PB}$  ( $\approx 2$  sec), a narrow (100µs typ) soft reset pulse is generated on the SRST output pin after the button is released. The pushbutton circuitry contains an internal debounce counter which delays the output of the soft reset pulse by typically 20ms. This pin can be OR-tied to the RST pin and issue what is called a "soft" reset. The SRST thereby resets the microprocessor without interrupting the DRAM refresh cycle. In this manner DRAM information remains undisturbed. Alternatively, SRST may be monitored by the processor to initiate a software-controlled reset.

When the  $\overline{PBR}$  pin is held low for longer than  $t_{PB}$  ( $\approx 2$  sec), a standard reset is generated on the  $\overline{RST}$  and RST pins. Once the 2 second period has elapsed, a reset signal is produced by the push-button logic, thereby clearing the reset counter. Once the button is released, the reset counter begins counting the reset period (200ms nominal). Consequently, the reset outputs remain asserted for approximately 200ms after the button is released.

#### APPLICATIONS INFORMATION

During a supply induced reset condition, the ability of the PBR pin to force a soft reset condition on the SRST pin is disabled. In other words SRST will remain high. If the PBR pin is held low, both during and after a supply induced reset (low RST), the RST pin will remain low until 200ms after the PBR goes high.

#### Power Detect/Gate Drive

The LTC1326/LTC1326-2.5 for the most part are powered internally from the  $V_{CC3}$  pin. The exception is at the gate drive of the output FET on the RST pin. On the input to this FET is power detection circuitry used to detect and drive the gate from either the 3.3V input pin ( $V_{CC3}$ ) or the 5V input pin ( $V_{CC5}$ ) on the LTC1326 or the 2.5V input pin ( $V_{CC25}$ ) on the LTC1326-2.5. The gate drive is derived from the pin with the highest potential. This ensures the part pulls the RST pin low as soon as either input pin is  $\geq 1V$ .

#### **Dual and Single Supply Monitor Operation**

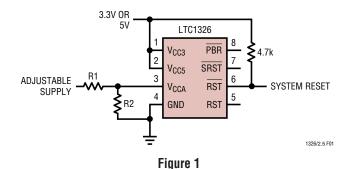

The  $V_{CC3}$ ,  $V_{CC5}$  and  $V_{CCA}$  inputs may be individually disabled by the following override techniques which allow the LTC1326 or LTC1326-2.5 to be used as a dual or single supply monitor.

#### LTC1326 Override Functions

The  $V_{CCA}$  pin, if unused, can be tied to either  $V_{CC3}$  or  $V_{CC5}$ . This is an obvious solution since the trip points for  $V_{CC3}$  and  $V_{CC5}$  will always be greater than the trip point for  $V_{CCA}$ .

The  $V_{CC5}$  input trip point is disabled if its voltage is equal to the voltage on  $V_{CC3}\pm25$ mV and the voltage on  $V_{CC5}$  is less than 4.15V. In this manner, the part will behave as a 3.3V monitor and the  $V_{CC5}$  reset will be disabled.

The  $V_{CC5}$  trip point is reenabled when the voltage on  $V_{CC5}$  is equal to the voltage on  $V_{CC3}\pm25\text{mV}$  and the two inputs are greater than approximately 4.15V. In this manner, the LTC1326 can function as a 5V monitor with the 3.3V monitor disabled.

When monitoring either 3.3V or 5V with  $V_{CC3}$  strapped to  $V_{CC5}$  (see Figure 1), the LTC1326 determines which is the

appropriate range. The LTC1326 handles this <u>situation</u> as shown in Figure 2. Above 1V and below  $V_{RT3}$ , RST is held low. From  $V_{RT3}$  to approximately 4.15V, the LTC1326 assumes 3.3V supply monitoring and RST is deasserted. Above approximately 4.15V, the LTC1326 operates as a 5V monitor. In most systems, the 5V supply will pass through the 3.1V to 4.15V region in <200ms during power-up, and the RST output will behave as desired. Table 1 summarizes the state of RST and RST at various operating voltages with  $V_{CC3} = V_{CC5}$ .

Table 1. Override Truth Table ( $V_{CC3} = V_{CC5}$ )

| INPUTS (V <sub>CC3</sub> = V <sub>CC5</sub> = V <sub>CC</sub> ) | RST | RST |

|-----------------------------------------------------------------|-----|-----|

| $0V \le V_{CC} \le 1V$                                          | _   | _   |

| $1V \le V_{CC} \le V_{RT3}$                                     | 0   | 1   |

| $V_{RT3} \le V_{CC} \le 4.15V$                                  | 1   | 0   |

| $4.15V \le V_{CC} \le V_{RT5}$                                  | 0   | 1   |

| $V_{RT5} \le V_{CC}$                                            | 1   | 0   |

5 V<sub>CC3</sub> = V<sub>CC5</sub> = V<sub>CCA</sub> = OV TO 5V 4.7k PULL-UP FROM RST TO V<sub>CC3</sub>

3 0 1 2 3 4 5

SUPPLY VOLTAGE (V)

Figure 2. RST Voltage vs Supply Voltage

#### APPLICATIONS INFORMATION

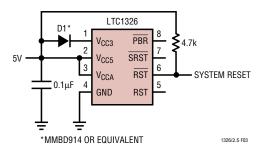

Figure 3 contains a simple circuit for 5V systems that can't risk the RST output going high in the 3.1V to 4.15V range (possibly due to very slow rise time on the 5V supply). Diode D1 powers the LTC1326 while dropping  $\approx\!0.6V$  from the  $V_{CC5}$  pin to the  $V_{CC3}$  pin. This prevents the part's internal override circuit from being activated. Without the override circuit active, the RST pin stays low until  $V_{CC5}$  reaches  $V_{RT5}\cong 4.725V$  (See Figure 4).

Figure 3. LTC1326 Monitoring a Single 5V Supply. D1 Used to Avoid RST High Near 3.3V to 4V (See Figure 2).

Figure 4. RST Output Voltage Characteristics of the Circuit in Figure 3

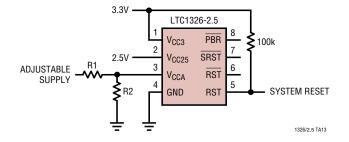

#### LTC1326-2.5 Override Functions

The  $V_{CCA}$  pin, if unused, can be tied to either  $V_{CC3}$  or  $V_{CC25}$ . This is an obvious solution since the trip points for  $V_{CC3}$  and  $V_{CC25}$  will always be greater than the trip point for  $V_{CCA}$ . Likewise, the  $V_{CC25}$ , if unused, can be tied to  $V_{CC3}$ .  $V_{CC3}$  must always be used. Tying  $V_{CC3}$  to  $V_{CC25}$  and operating off of a 2.5V supply will result in the continuous assertion of  $\overline{RST}$ .

#### **Extending ESD Tolerance on the PBR Input Pin**

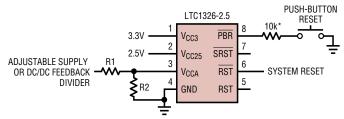

The  $\overline{PBR}$  pin is susceptible to ESD since it may be brought out to a front panel in normal applications. The ESD tolerance of this pin can be increased by adding a resistor in series with the  $\overline{PBR}$  pin. A 10k resistor can increase the ESD tolerance of the  $\overline{PBR}$  pin to approximately 10kV. The  $\overline{PBR}$ 's internal pull-up current of  $7\mu A$  typical means there is only 70mV (150mV max) dropped across the resistor. See Figure 5.

\*OPTIONAL RESISTOR EXTENDS ESD TOLERANCE OF PBR INPUT TO APPROXIMATELY 10kV

Figure 5. Triple Supply Monitor (3.3V, 2.5V and Adjustable) with Extended ESD Tolerance

# TYPICAL APPLICATIONS

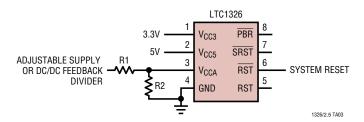

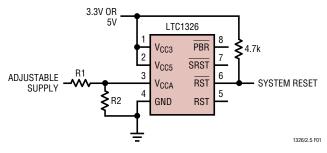

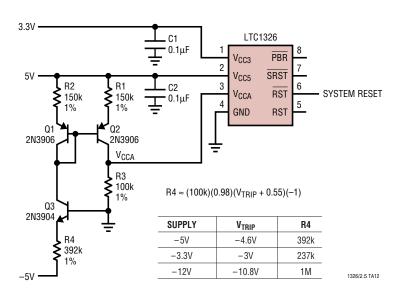

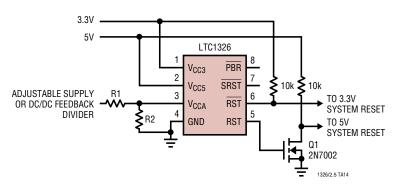

#### Triple Supply Monitor (3.3V, 5V and Adjustable)

#### Dual Supply Monitor (3.3V and 5V, Defeat V<sub>CCA</sub> Input)

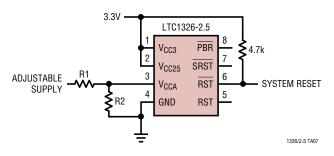

#### **Dual Supply Monitor (3.3V or 5V Plus Adj)**

REFER TO LTC1326 OVERRIDE FUNCTIONS IN THE APPLICATIONS INFORMATION SECTION.

#### Dual Supply Monitor (3.3V Plus Adj)

# TYPICAL APPLICATIONS

SRST Tied to RST and OR-Tying Other Sources to RST to Generate Reset and Reset

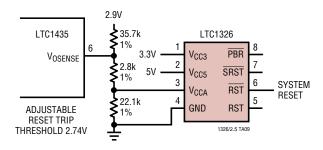

#### Using V<sub>CCA</sub> Tied to DC/DC Feedback Divider

# Using the Short Pulse Width, Push-Button Soft Reset Feature to Initiate Hard Reset

# TYPICAL APPLICATIONS

#### **Monitoring a Negative Supply**

#### Reset Valid for V<sub>CC3</sub> Down to 0V

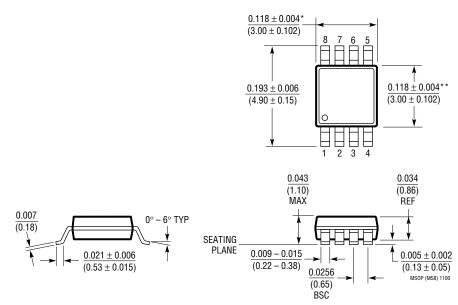

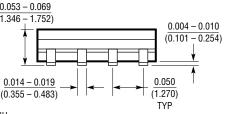

### PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

#### MS8 Package 8-Lead Plastic MSOP (LTC DWG # 05-08-1660)

- $^{\star}\,$  DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

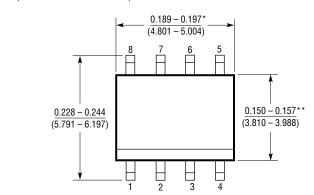

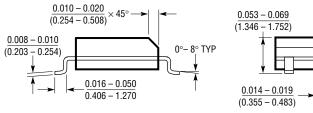

# PACKAGE DESCRIPTION

$\label{lem:decomposition} \textbf{Dimensions in inches (millimeters) unless otherwise noted.}$

#### \$8 Package 8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

S08 0996

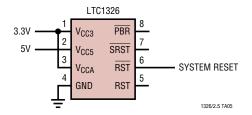

# TYPICAL APPLICATION

Triple Supply Monitor with 3.3V and 5V System Resets

# **RELATED PARTS**

| PART NUMBER             | DESCRIPTION                                              | COMMENTS                                                                                         |

|-------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| LTC690                  | 5V Supply Monitor, Watchdog Timer and Battery Backup     | 4.65V Threshold                                                                                  |

| LTC694-3.3              | 3.3V Supply Monitor, Watchdog Timer and Battery Backup   | 2.9V Threshold                                                                                   |

| LTC699                  | 5V Supply Monitor and Watchdog Timer                     | 4.65V Threshold                                                                                  |

| LTC1232                 | 5V Supply Monitor, Watchdog Timer and Push-Button Reset  | 4.37V/4.62V Threshold                                                                            |

| LTC1443/LTC1444/LTC1445 | Micropower Quad Comparators with 1% Reference            | LTC1443 has 1.182V Reference, LTC1444/LTC1445<br>have 1.221V Reference and Adjustable Hysteresis |

| LTC1536                 | Precision Triple Supply Monitor for PCI Applications     | Meets PCI t <sub>FAIL</sub> Timing Specifications                                                |

| LTC1540                 | Nanopower Comparator with 2% Reference                   | 1.182V Reference, 300nA Supply Current, 8-Pin MSOP                                               |

| LTC1726-2.5             | Micropower Triple Supply Monitor for 2.5V, 3.3V and ADJ  | Adjustable RESET and Watchdog Time Outs                                                          |

| LTC1726-5               | Micropower Triple Supply Monitor for 5V, 3.3V and ADJ    | Adjustable RESET and Watchdog Time Outs                                                          |

| LTC1727-2.5             | Micropower Triple Supply Monitor with Individual Outputs | 2.338V, 3.086V, 1V Thresholds (±1.5%) 2.5, 3.3V, ADJ                                             |

| LTC1727-5               | Micropower Triple Supply Monitor with Individual Outputs | 4.675V, 3.086V, 1V Thresholds (±1.5%) 5V, 3.3V, ADJ                                              |

| LTC1728-1.8             | Micropower Triple Supply Monitor in 5-Pin SOT-23 Package | 2.805V, 1.683V,1V Thresholds (±1.5%) 3V, 1.8V, ADJ                                               |

| LTC1728-2.5             | Micropower Triple Supply Monitor in 5-Pin SOT-23 Package | 2.338V, 3.086V, 1V Thresholds (±1.5%) 2.5, 3.3V, ADJ                                             |

| LTC1728-5               | Micropower Triple Supply Monitor in 5-Pin SOT-23 Package | 4.675V, 3.086V, 1V Thresholds (±1.5%) 5V, 3.3V, ADJ                                              |

| LTC1985-1.8             | Micropower Triple Supply Monitor for 3V, 1.8V and ADJ    | Push-Pull RESET Output, SOT-23                                                                   |