EVALUATION KIT

AVAILABLE

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## General Description

The MAX6876 EEPROM-configurable, multivoltage power tracker/supervisor monitors four system voltages and ensures proper power-up and power-down conditions for systems requiring voltage tracking and/or sequencing. The MAX6876 provides a highly configurable solution as key thresholds and timing parameters are programmed through an I<sup>2</sup>C\* interface and these values are stored in internal EEPROM. The MAX6876 also provides supervisory functions and an overcurrent detection circuit.

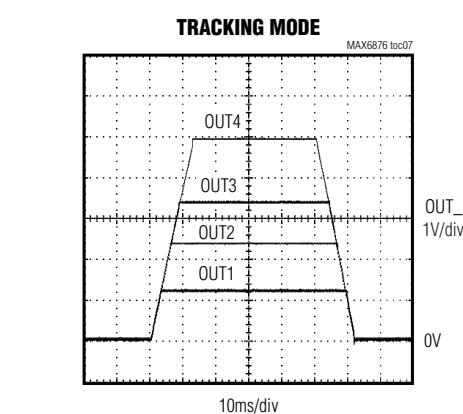

The MAX6876 features programmable undervoltage and overvoltage thresholds for each input supply. When all voltages are within specifications, the device turns on the external n-channel MOSFETs to either sequence or track the voltages to the system. All of the voltages can be sequenced or tracked or powered up with a combination of the two options. During tracking, the voltage at the GATE of each MOSFET is increased to slowly turn on each supply. The voltages at the source of each MOSFET are compared to each other to ensure that the voltage differential between each monitored supply does not exceed 250mV (typ). Tracking is dynamically adjusted to force all outputs to track within a  $\pm 125$ mV window from a reference ramp; if, for any reason, any supply fails to track within  $\pm 250$ mV from the reference ramp, a FAULT output is asserted, the power-up mode is terminated, and all outputs are powered off. Power-up mode is also terminated if the controlled voltages fail to complete the ramp-up within a programmable FAULT timeout. The MAX6876 features latch-off and autoretry modes to power on again after a fault condition has been detected.

Other features of the MAX6876 include a reset circuit, a manual reset input (MR), and a margin disable input (MARGIN). The device also features outputs for indicating a power-good condition (PG<sub>—</sub>) and an overcurrent condition (OC), and a bus-removal (REM) output.

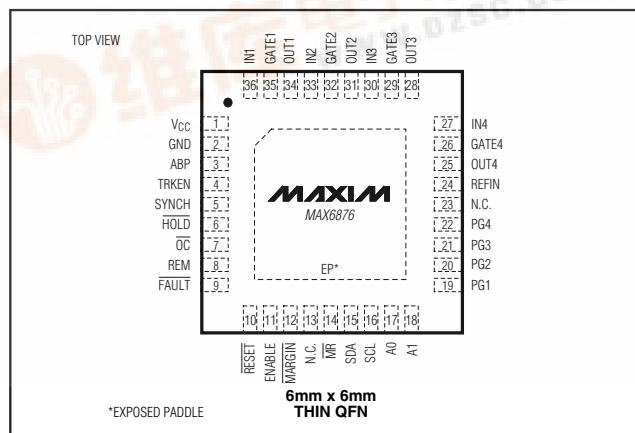

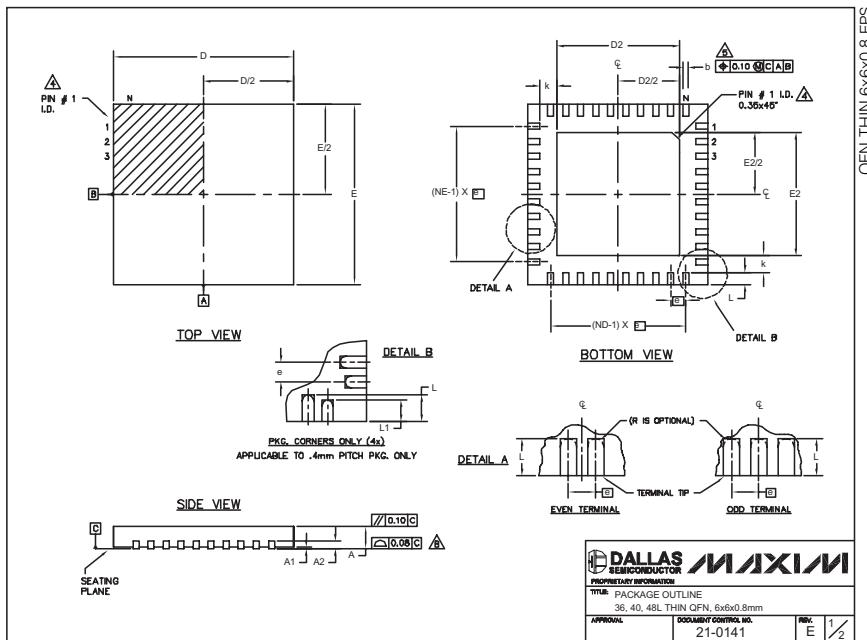

The MAX6876 is available in a small 6mm x 6mm, 36-pin thin QFN package and is fully specified over the extended -40°C to +85°C temperature range.

## Applications

Multivoltage Systems

Storage Equipment

Networking Systems

Servers/Workstations

Telecom

\*Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

SMBus is a trademark of Intel Corp.

## Features

- ◆ Tracking/Sequencing for Up to Four Supply Voltages (With One MAX6876 Device) and Tracking for Up to 16 Supply Voltages (Using Four MAX6876 Devices)

- ◆ EEPROM-Configurable Tracking/Sequencing Control

- ◆ Bus Voltage Independent Operation (MAX6876 Is Powered from the Tracked Supply Voltages or Always-On Supply)

- ◆ EEPROM-Selectable Undervoltage/Overvoltage-Lockout Thresholds for Each Input Supply

- ◆ EEPROM-Selectable Power-Up/Down Slew Rate

- ◆ Programmable Power-Good Output Thresholds and Timing

- ◆ Global Adjustable Undervoltage Lockout or Logic ENABLE Input

- ◆ Independent Internal Charge Pumps to Enhance External n-Channel FETs (VGATE\_SOURCE = 5V)

- ◆ Post Power-Up Selectable Overcurrent Detection

- ◆ 0.5V to 5.5V IN\_ Threshold Range

- ◆  $\pm 1.5\%$  Threshold Accuracy

- ◆ I<sup>2</sup>C/SMBus™-Compatible Serial Interface

- ◆ Small 6mm x 6mm, 36-Pin Thin QFN Package

## Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE | PKG CODE |

|------------|----------------|-------------|----------|

| MAX6876ETX | -40°C to +85°C | 36 Thin QFN | T3666-3  |

## Pin Configuration

MAX6876

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## ABSOLUTE MAXIMUM RATINGS

(All voltages are referenced to GND, unless otherwise noted.)

|                                                                      |                                                 |

|----------------------------------------------------------------------|-------------------------------------------------|

| GATE.....                                                            | -0.3V to (IN <sub>+</sub> + 6V)                 |

| IN1–IN4, V <sub>CC</sub> .....                                       | -0.3V to +6V                                    |

| OUT1–OUT4, SYNCH, ABP, REFIN.....                                    | -0.3V to Max (IN1–IN4, V <sub>CC</sub> ) + 0.3V |

| ENABLE, TRKEN, HOLD, FAULT, MR, MARGIN.....                          | -0.3V to +6V                                    |

| RESET, PG1–PG4, OC, REM.....                                         | -0.3V to +6V                                    |

| SDA, SCL, A0, A1.....                                                | -0.3V to +6V                                    |

| Input/Output Current (all pins except OUT <sub>-</sub> and GND)..... | ±20mA                                           |

|                                                                                                                      |                 |

|----------------------------------------------------------------------------------------------------------------------|-----------------|

| OUT <sub>-</sub> , GND Current.....                                                                                  | ±50mA           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) 36-Pin, 6mm x 6mm Thin QFN (derate 26.3mW/°C above +70°C)..... | 2105mW          |

| Operating Temperature Range.....                                                                                     | -40°C to +85°C  |

| Storage Temperature Range.....                                                                                       | -65°C to +150°C |

| Maximum Junction Temperature.....                                                                                    | +150°C          |

| Lead Temperature (soldering, 10s).....                                                                               | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub>, IN1–IN4 = +2.7V to +5.5V; ENABLE = MARGIN = MR = ABP = TRKEN; T<sub>A</sub> = -40°C to +85°C, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                        | SYMBOL              | CONDITIONS                                                                                         |                                                                                               | MIN  | TYP  | MAX              | UNITS |  |

|----------------------------------|---------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------------------|-------|--|

| Operating Voltage Range (Note 2) | V <sub>CC</sub>     | GATE <sub>-</sub> = PG <sub>-</sub> = RESET = 0                                                    |                                                                                               | 1.4  |      | 5.5              | V     |  |

|                                  |                     | Voltage on ABP (from V <sub>CC</sub> or IN1–IN4) to ensure the device is fully operational         |                                                                                               | 2.7  |      |                  |       |  |

| Undervoltage Lockout             | V <sub>UVLO</sub>   | Minimum voltage on ABP (from V <sub>CC</sub> or IN1–IN4) to ensure the device is EEPROM configured |                                                                                               | 2.5  |      | V                |       |  |

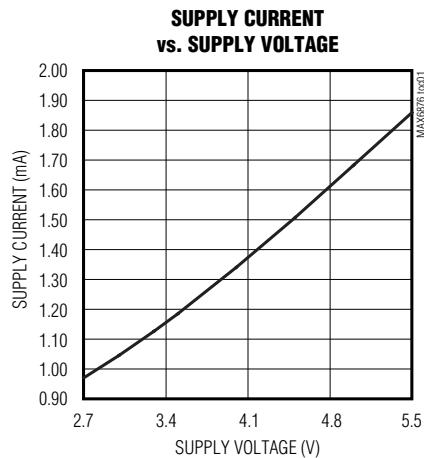

| Supply Current                   | I <sub>CC</sub>     | V <sub>CC</sub> = 5.5V, IN1–IN4 = 3.3V, no load                                                    |                                                                                               | 1.8  | 3    | 4                | mA    |  |

|                                  |                     | Configuration registers or memory access, no load                                                  |                                                                                               | 2.5  |      |                  |       |  |

| IN <sub>-</sub> Threshold Range  | V <sub>TH</sub>     | IN1–IN4 (in 20mV increments)                                                                       |                                                                                               | 1.00 | 5.50 | 3.05             | V     |  |

|                                  |                     | IN1–IN4 (in 10mV increments)                                                                       |                                                                                               | 0.50 |      |                  |       |  |

| Threshold Accuracy               |                     | TA = 0°C to +85°C                                                                                  | 0.5V < IN <sub>-</sub> < 5.5V, IN <sub>-</sub> falling for UV, rising for OV                  | -1.5 | +1.5 | %                |       |  |

|                                  |                     |                                                                                                    | 2V < IN <sub>-</sub> < 5.5V, IN <sub>-</sub> falling for UV, rising for OV (20mV increments)  | -2.5 | +2.5 | %                |       |  |

|                                  |                     |                                                                                                    | 1V < IN <sub>-</sub> < 2V, IN <sub>-</sub> falling for UV, rising for OV (20mV increments)    | -50  | +50  | mV               |       |  |

|                                  |                     |                                                                                                    | 1V < IN <sub>-</sub> < 3.05V, IN <sub>-</sub> falling for UV, rising for OV (10mV increments) | -2.5 | +2.5 | %                |       |  |

|                                  |                     |                                                                                                    | 0.5V < IN <sub>-</sub> < 1V, IN <sub>-</sub> falling for UV, rising for OV (10mV increments)  | -25  | +25  | mV               |       |  |

| Threshold Hysteresis             | V <sub>TH_HYS</sub> |                                                                                                    |                                                                                               | 0.5  |      | %V <sub>TH</sub> |       |  |

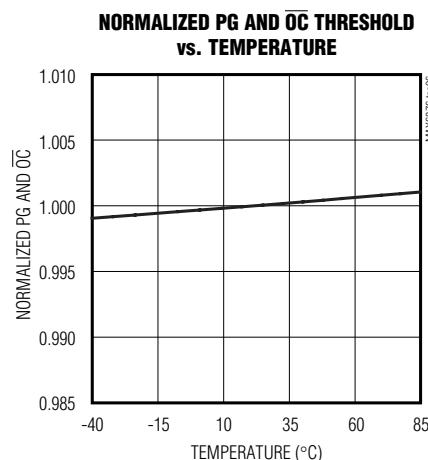

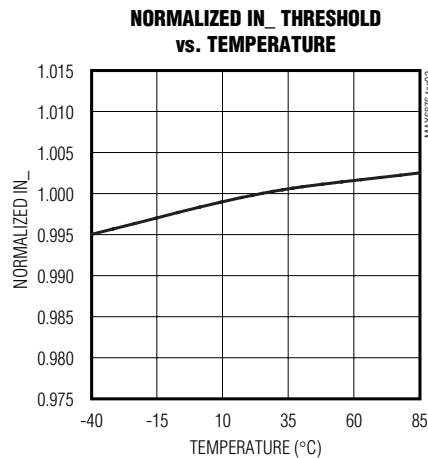

| RESET Threshold Tempco           | ΔV <sub>TH/C</sub>  |                                                                                                    |                                                                                               | 50   |      | ppm/°C           |       |  |

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC}$ ,  $IN1-IN4 = +2.7V$  to  $+5.5V$ ;  $ENABLE = \overline{MARGIN} = \overline{MR} = ABP = TRKEN$ ;  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise specified. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                                 | SYMBOL                                      | CONDITIONS                                                    |                                            |                                    | MIN   | TYP  | MAX   | UNITS     |

|-----------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------|--------------------------------------------|------------------------------------|-------|------|-------|-----------|

| Tracking-Differential-Voltage Hold Ramp (Note 3)          | $V_{TRK}$                                   | $V_{OUT\_} > V_{TH\_PL}$<br>$V_{OUT\_} < V_{TH\_PG}$          |                                            |                                    | 95    | 125  | 155   | mV        |

| Tracking-Differential-Voltage Hysteresis                  |                                             |                                                               |                                            |                                    |       | 25   |       | mV        |

| Tracking-Differential FAULT Voltage (Note 3)              | $V_{TRK\_F}$                                | $V_{OUT\_} > V_{TH\_PL}$<br>$V_{OUT\_} < V_{TH\_PG}$          |                                            |                                    | 200   | 250  | 300   | mV        |

| FAULT Timeout Period (Note 4)                             | $t_{FAULTUP}$ ,<br>$t_{FAULTDOWN}$          | Register contents<br>(Table 16)                               | 00                                         |                                    | 20    | 25   | 30    | ms        |

|                                                           |                                             |                                                               | 01                                         |                                    | 40    | 50   | 60    |           |

|                                                           |                                             |                                                               | 10                                         |                                    | 80    | 100  | 120   |           |

|                                                           |                                             |                                                               | 11                                         |                                    | 160   | 200  | 240   |           |

| FAULT to GATE Delay                                       | $t_{FG}$                                    |                                                               |                                            |                                    |       | 2    |       | $\mu s$   |

| IN1-IN4 Input Impedance                                   | $R_{IN1-4}$                                 | For $IN\_$ voltages < the highest $IN\_$ supply               |                                            |                                    | 55    | 90   | 145   | $k\Omega$ |

| OUT1-OUT4 Input Impedance                                 | $R_{OUT1-4}$                                | OUT <sub>1</sub> pulldown disabled                            |                                            |                                    | 70    | 100  | 130   | $k\Omega$ |

| Power-On Delay                                            | $t_{PO}$                                    | $V_{ABP} \geq V_{UVLO}$                                       |                                            |                                    |       | 3    |       | ms        |

| IN <sub>1</sub> to GATE <sub>1</sub> Delay                | $t_{D-GATE}$                                | IN <sub>1</sub> _falling/rising, 100mV overdrive              |                                            |                                    |       | 6    |       | $\mu s$   |

| OUT <sub>1</sub> to PG <sub>1</sub> Delay                 | $t_{POK}$                                   | Register contents<br>(Table 16)                               | OUT <sub>1</sub> _rising, 100mV overdrive  |                                    |       | 3    |       | ms        |

|                                                           |                                             |                                                               | OUT <sub>1</sub> _falling, 100mV overdrive |                                    |       | 25   |       | $\mu s$   |

| GATE, RESET, Autoretry Timeout Period (Notes 5, 6)        | $t_{RESET}$ ,<br>$t_{AUTO}$ ,<br>$t_{GATE}$ | Register contents<br>(Table 16)                               | 000                                        |                                    | 25    |      |       | $\mu s$   |

|                                                           |                                             |                                                               | 001                                        |                                    | 10    | 12.5 | 15    | ms        |

|                                                           |                                             |                                                               | 010                                        |                                    | 20    | 25   | 30    |           |

|                                                           |                                             |                                                               | 011                                        |                                    | 40    | 50   | 60    |           |

|                                                           |                                             |                                                               | 100                                        |                                    | 80    | 100  | 120   |           |

|                                                           |                                             |                                                               | 101                                        |                                    | 160   | 200  | 240   |           |

|                                                           |                                             |                                                               | 110                                        |                                    | 320   | 400  | 480   |           |

|                                                           |                                             |                                                               | 111                                        |                                    | 1280  | 1600 | 1920  |           |

| OC Timeout Period                                         | $t_{OC}$                                    | Register contents<br>(Table 16)                               | 00                                         |                                    | 10    | 12.5 | 15    | ms        |

|                                                           |                                             |                                                               | 01                                         |                                    | 40    | 50   | 60    |           |

|                                                           |                                             |                                                               | 10                                         |                                    | 80    | 100  | 120   |           |

|                                                           |                                             |                                                               | 11                                         |                                    | 160   | 200  | 240   |           |

| Track/Sequence Slew Rate Rising or Falling                | $TRKSLEW$                                   | Register contents<br>(Table 16)                               | 00                                         | $T_A = 0^\circ C$ to $+85^\circ C$ | 560   | 800  | 1040  | V/s       |

|                                                           |                                             |                                                               |                                            | $T_A = -40^\circ C$ to $0^\circ C$ | 480   | 800  | 1120  |           |

|                                                           |                                             |                                                               | 01                                         | $T_A = 0^\circ C$ to $+85^\circ C$ | 280   | 400  | 520   |           |

|                                                           |                                             |                                                               |                                            | $T_A = -40^\circ C$ to $0^\circ C$ | 240   | 400  | 560   |           |

|                                                           |                                             |                                                               | 10                                         | $T_A = 0^\circ C$ to $+85^\circ C$ | 140   | 200  | 260   |           |

|                                                           |                                             |                                                               |                                            | $T_A = -40^\circ C$ to $0^\circ C$ | 120   | 200  | 280   |           |

|                                                           |                                             |                                                               | 11                                         | $T_A = 0^\circ C$ to $+85^\circ C$ | 70    | 100  | 130   |           |

|                                                           |                                             |                                                               |                                            | $T_A = -40^\circ C$ to $0^\circ C$ | 60    | 100  | 140   |           |

| IN <sub>1</sub> to OUT <sub>1</sub> Overcurrent Threshold | $V_{TH\_OC}$                                | Register contents<br>(Table 16),<br>OUT <sub>1</sub> _falling | 00                                         |                                    | 96.25 | 97.5 | 98.75 | %         |

|                                                           |                                             |                                                               | 01                                         |                                    | 93.75 | 95   | 96.25 |           |

|                                                           |                                             |                                                               | 10                                         |                                    | 91.25 | 92.5 | 93.75 |           |

|                                                           |                                             |                                                               | 11                                         |                                    | 88.75 | 90   | 91.25 |           |

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC}$ ,  $IN_1-IN_4 = +2.7V$  to  $+5.5V$ ;  $ENABLE = \overline{MARGIN} = \overline{MR} = ABP = TRKEN$ ;  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise specified. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                                                                                                      | SYMBOL            | CONDITIONS                                                              |    | MIN          | TYP        | MAX          | UNITS     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------|----|--------------|------------|--------------|-----------|--|--|

| IN_ to OUT_ Power-Good Threshold                                                                                               | $V_{TH\_PG}$      | Register contents (Table 16), OUT_rising                                | 00 | 93.75        | 95         | 96.25        | %         |  |  |

|                                                                                                                                |                   |                                                                         | 01 | 91.25        | 92.5       | 93.75        |           |  |  |

|                                                                                                                                |                   |                                                                         | 10 | 88.75        | 90         | 91.25        |           |  |  |

|                                                                                                                                |                   |                                                                         | 11 | 86.25        | 87.5       | 88.75        |           |  |  |

| $V_{TH\_PG}$ and $V_{TH\_OC}$ Hysteresis                                                                                       | $V_{OUT\_HYS}$    |                                                                         |    | 0.5          |            |              | %         |  |  |

| Power Low Threshold                                                                                                            | $V_{TH\_PL}$      | OUT_falling                                                             |    | 125          | 142        | 165          | mV        |  |  |

| Power Low Hysteresis                                                                                                           | $V_{TH\_PL\_HYS}$ |                                                                         |    | 10           |            |              | mV        |  |  |

| OUT_ to GND Pulldown Impedance (When Enabled)                                                                                  |                   | $ABP \geq 2.5V$                                                         |    | 100          |            |              | $\Omega$  |  |  |

| REM Output Low                                                                                                                 | $V_{OL\_REM}$     | $ABP \geq 2.5V$ , $I_{SINK} = 4mA$                                      |    | 0.3          |            |              | V         |  |  |

|                                                                                                                                |                   | $ABP \geq 4.0V$ , $I_{SINK} = 15mA$                                     |    | 0.4          |            |              |           |  |  |

| Output Low PG1–PG4, $\overline{HOLD}$ , $\overline{FAULT}$ , $\overline{OC}$ , $\overline{RESET}$ (Note 2)                     | $V_{OL}$          | $ABP \geq 1.4V$ , $I_{SINK} = 50\mu A$ ( $PG_-, \overline{RESET}$ only) |    | 0.3          |            |              | V         |  |  |

|                                                                                                                                |                   | $ABP \geq 2.5V$ , $I_{SINK} = 1mA$                                      |    | 0.3          |            |              |           |  |  |

|                                                                                                                                |                   | $ABP \geq 4.0V$ , $I_{SINK} = 4mA$                                      |    | 0.4          |            |              |           |  |  |

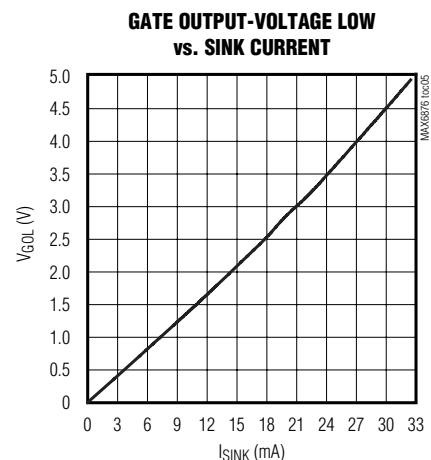

| GATE1–GATE4 Output Low                                                                                                         | $V_{GOL}$         | $ABP \geq 1.4V$ , $I_{SINK} = 50\mu A$                                  |    | 0.3          |            |              | V         |  |  |

|                                                                                                                                |                   | $ABP \geq 2.5V$ , $I_{SINK} = 1mA$                                      |    | 0.3          |            |              |           |  |  |

|                                                                                                                                |                   | $ABP \geq 4.0V$ , $I_{SINK} = 4mA$                                      |    | 0.8          |            |              |           |  |  |

| PG1–PG4, $\overline{HOLD}$ , $\overline{FAULT}$ , $\overline{OC}$ , $\overline{RESET}$ , REM Output Open-Drain Leakage Current | $I_{LKG}$         | Output deasserted                                                       |    | -1           | +1         |              | $\mu A$   |  |  |

| GATE_ Output-Voltage High                                                                                                      | $V_{GOH}$         | $I_{GATE\_} = 0.5\mu A$                                                 |    | $IN\_ + 4.4$ | $IN\_ + 5$ | $IN\_ + 5.8$ | V         |  |  |

| GATE_ Pullup Current                                                                                                           | $I_{GATEUP}$      | During power-up/down, $V_{GATE\_} = 1V$                                 |    | 2.5          | 4.5        |              | $\mu A$   |  |  |

| GATE_ Pulldown Current                                                                                                         | $I_{GATEDOWN}$    | During power-up/down, $V_{GATE\_} = 4V$                                 |    | 2.5          | 4.5        |              | $\mu A$   |  |  |

| MARGIN, $\overline{FAULT}$ , $\overline{HOLD}$ , $\overline{MR}$ , ENABLE Input Voltage                                        | $V_{IL}$          |                                                                         |    | 0.3 x ABP    |            |              | V         |  |  |

|                                                                                                                                | $V_{IH}$          |                                                                         |    | 0.6 x ABP    |            |              |           |  |  |

| MR Input Pulse Width                                                                                                           | $t_{MR}$          |                                                                         |    | 2            |            |              | $\mu s$   |  |  |

| FAULT, HOLD, MARGIN, $\overline{MR}$ , ENABLE Glitch Rejection                                                                 |                   |                                                                         |    | 100          |            |              | ns        |  |  |

| Digital Input to Logic Delay, $\overline{FAULT}$ , $\overline{HOLD}$ , $\overline{MARGIN}$ , $\overline{MR}$ , ENABLE          | $t_D$             |                                                                         |    | 1            |            |              | $\mu s$   |  |  |

| MARGIN, $\overline{MR}$ Digital Input to ABP Pullup Resistance                                                                 | $R_P$             |                                                                         |    | 70           | 100        | 130          | $k\Omega$ |  |  |

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC}$ , IN1–IN4 = +2.7V to +5.5V; ENABLE =  $\overline{MARGIN} = \overline{MR} = \overline{ABP} = \overline{TRKEN}$ ;  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$ , unless otherwise specified. Typical values are at  $T_A = +25^\circ\text{C}$ .) (Note 1)

| PARAMETER                                        | SYMBOL       | CONDITIONS                     | MIN                  | TYP       | MAX   | UNITS            |

|--------------------------------------------------|--------------|--------------------------------|----------------------|-----------|-------|------------------|

| TRKEN Input Delay                                | $t_{EN}$     | TRKEN falling, 100mV overdrive | 2                    |           |       | $\mu\text{s}$    |

| TRKEN Reference Voltage Range                    | $V_{TRKEN}$  | Input rising                   | 1.245                | 1.285     | 1.320 | V                |

|                                                  |              | Input falling                  | 1.225                | 1.25      | 1.275 |                  |

| TRKEN Input Current                              | $I_{TRKEN}$  | $V_{TRKEN} = 1.25\text{V}$     | -100                 |           | +100  | $\text{nA}$      |

| Reference Input Voltage Range                    | $V_{REFIN}$  |                                | 1.225                | 1.25      | 1.275 | V                |

| Reference Input Resistance                       | $R_{REFIN}$  | $V_{REFIN} = 1.25\text{V}$     | 500                  |           |       | $\text{k}\Omega$ |

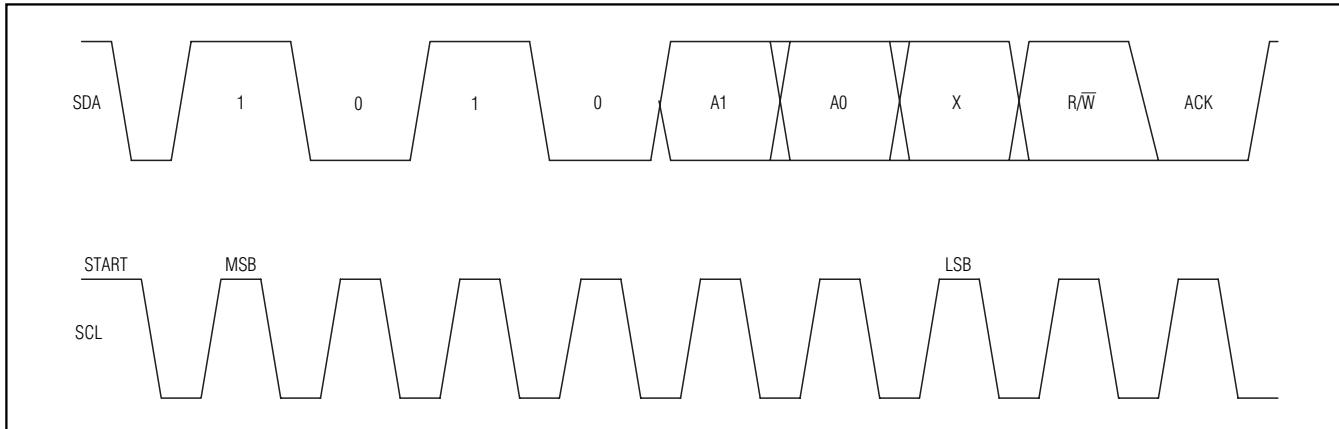

| <b>SERIAL INTERFACE LOGIC (SDA, SCL, A0, A1)</b> |              |                                |                      |           |       |                  |

| Logic-Input Low Voltage                          | $V_{IL}$     |                                |                      | 0.3 x ABP |       | V                |

| Logic-Input High Voltage                         | $V_{IH}$     |                                | 0.6 x ABP            |           |       | V                |

| Input Leakage Current                            | $I_{ILKG}$   |                                |                      | 1         |       | $\mu\text{A}$    |

| Output-Voltage Low                               | $V_{OL}$     | $I_{SINK} = 3\text{mA}$        |                      | 0.4       |       | V                |

| Output Leakage Current                           | $I_{OLKG}$   |                                |                      | 1         |       | $\mu\text{A}$    |

| Input/Output Capacitance                         | $C_{I/O}$    |                                | 10                   |           |       | $\text{pF}$      |

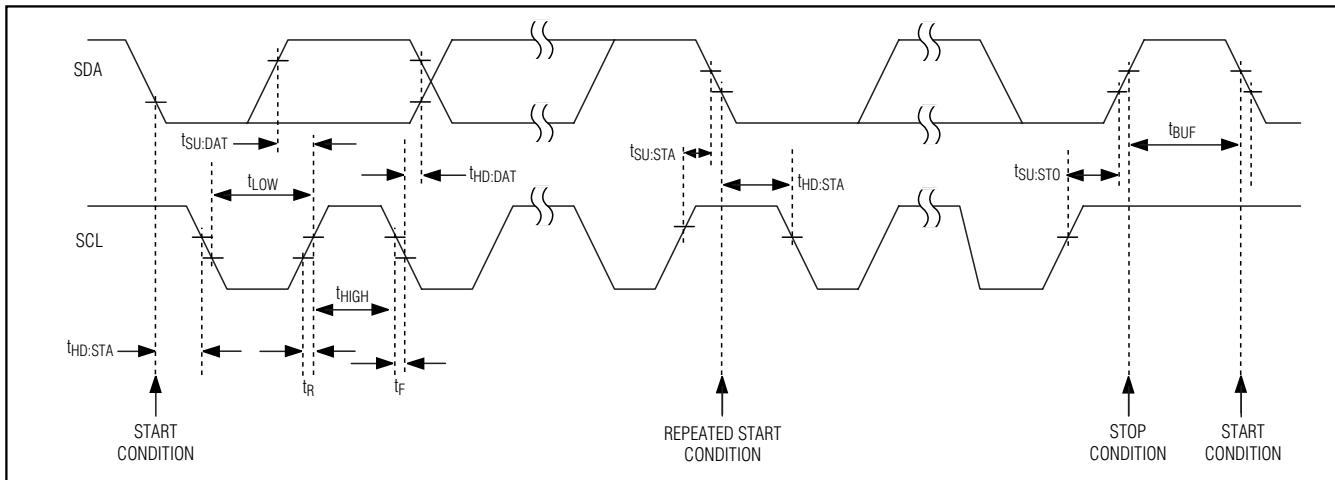

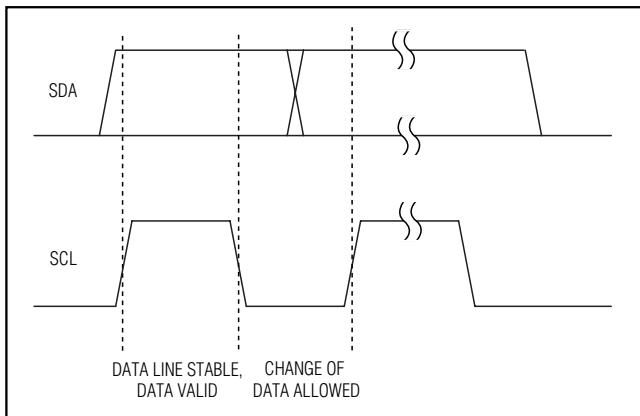

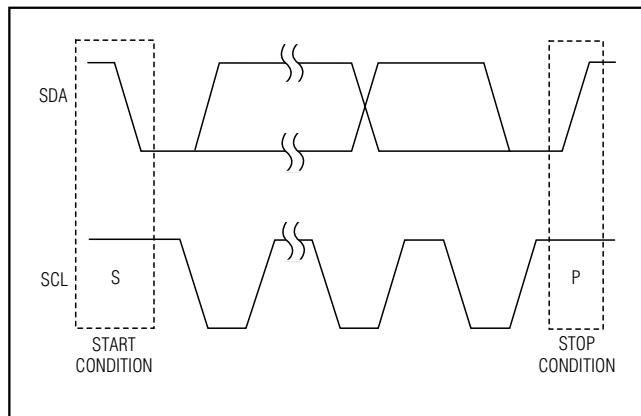

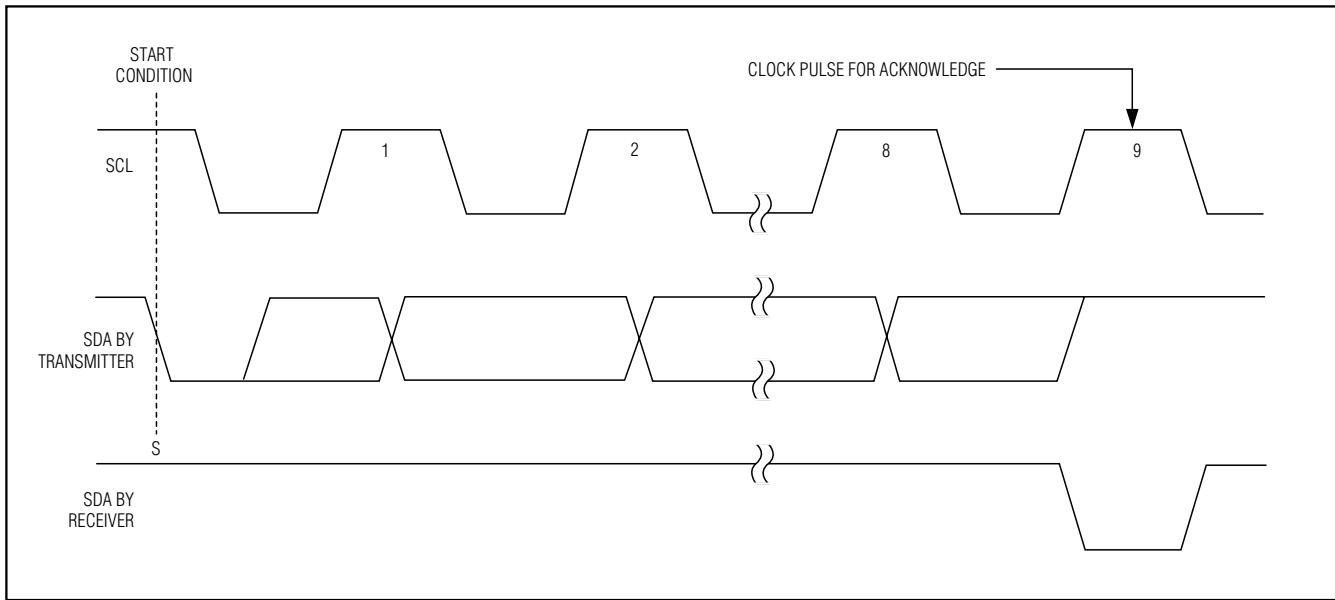

| <b>SERIAL INTERFACE TIMING (SDA, SCL)</b>        |              |                                |                      |           |       |                  |

| Serial Clock Frequency                           | $f_{SCL}$    |                                |                      | 400       |       | kHz              |

| Clock Low Period                                 | $t_{LOW}$    |                                | 1.3                  |           |       | $\mu\text{s}$    |

| Clock High Period                                | $t_{HIGH}$   |                                | 0.6                  |           |       | $\mu\text{s}$    |

| Bus Free Time                                    | $t_{BUF}$    |                                | 1.3                  |           |       | $\mu\text{s}$    |

| START Setup Time                                 | $t_{SU:STA}$ |                                | 0.6                  |           |       | $\mu\text{s}$    |

| START Hold Time                                  | $t_{HD:STA}$ |                                | 0.6                  |           |       | $\mu\text{s}$    |

| STOP Setup Time                                  | $t_{SU:STO}$ |                                | 0.6                  |           |       | $\mu\text{s}$    |

| Clock Low to Valid Output                        | $t_{AA}$     |                                | 0.1                  | 0.9       |       | $\mu\text{s}$    |

| Data Out Hold Time                               | $t_{DH}$     |                                | 50                   |           |       | ns               |

| Data In Setup Time                               | $t_{SU:DAT}$ |                                | 100                  |           |       | ns               |

| Data In Hold Time                                | $t_{HD:DAT}$ |                                | 0                    |           |       | ns               |

| SCL/SDA Rise Time                                | $t_R$        |                                |                      | 300       |       | ns               |

| SCL/SDA Fall Time                                | $t_F$        |                                |                      | 300       |       | ns               |

| Transmit SDA Fall Time                           | $t_F$        | $C_{BUS} = 400\text{pF}$       | 20 + 0.1 x $C_{BUS}$ | 300       |       | ns               |

| SCL/SDA Noise Suppression Time                   | $t_I$        |                                |                      | 50        |       | ns               |

| Byte Write Cycle Time                            | $t_{WR}$     |                                |                      | 11        |       | ms               |

**Note 1:** Specifications guaranteed for the stated global conditions. 100% production tested at  $T_A = +25^\circ\text{C}$  and  $T_A = +85^\circ\text{C}$ . Specifications at  $T_A = -40^\circ\text{C}$  are guaranteed by design.

**Note 2:** The internal supply voltage, measurable on ABP, is equal to the maximum of IN1–IN4 and  $V_{CC}$  supplies.

**Note 3:** Differential between each of the OUT\_ and the SYNCH ramp voltage during power-up/down measured as  $V_{OUT\_} - 2 \times V_{SYNCH}$ .

**Note 4:** FAULT timeout starts to count at the beginning of each sequence of power-up/down and clears when the programmed OUT\_ voltages track successfully.

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC}$ ,  $IN1-IN4 = +2.7V$  to  $+5.5V$ ;  $ENABLE = \overline{MARGIN} = \overline{MR} = ABP = TRKEN$ ;  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise specified. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

**Note 5:** The MAX6876 programmed as a single device; GATE timeout has counted prior to beginning each sequence of power-up. GATE timeout is not enabled during power-down or when the device is programmed as a master/slave.

**Note 6:** The MAX6876 programmed as a single device, the autoretry time begins to count at the assertion of the  $\overline{FAULT}$  signal. The MAX6876 programmed as a master/slave device; the autoretry time begins to count at the deassertion of the common  $\overline{FAULT}$  signal.

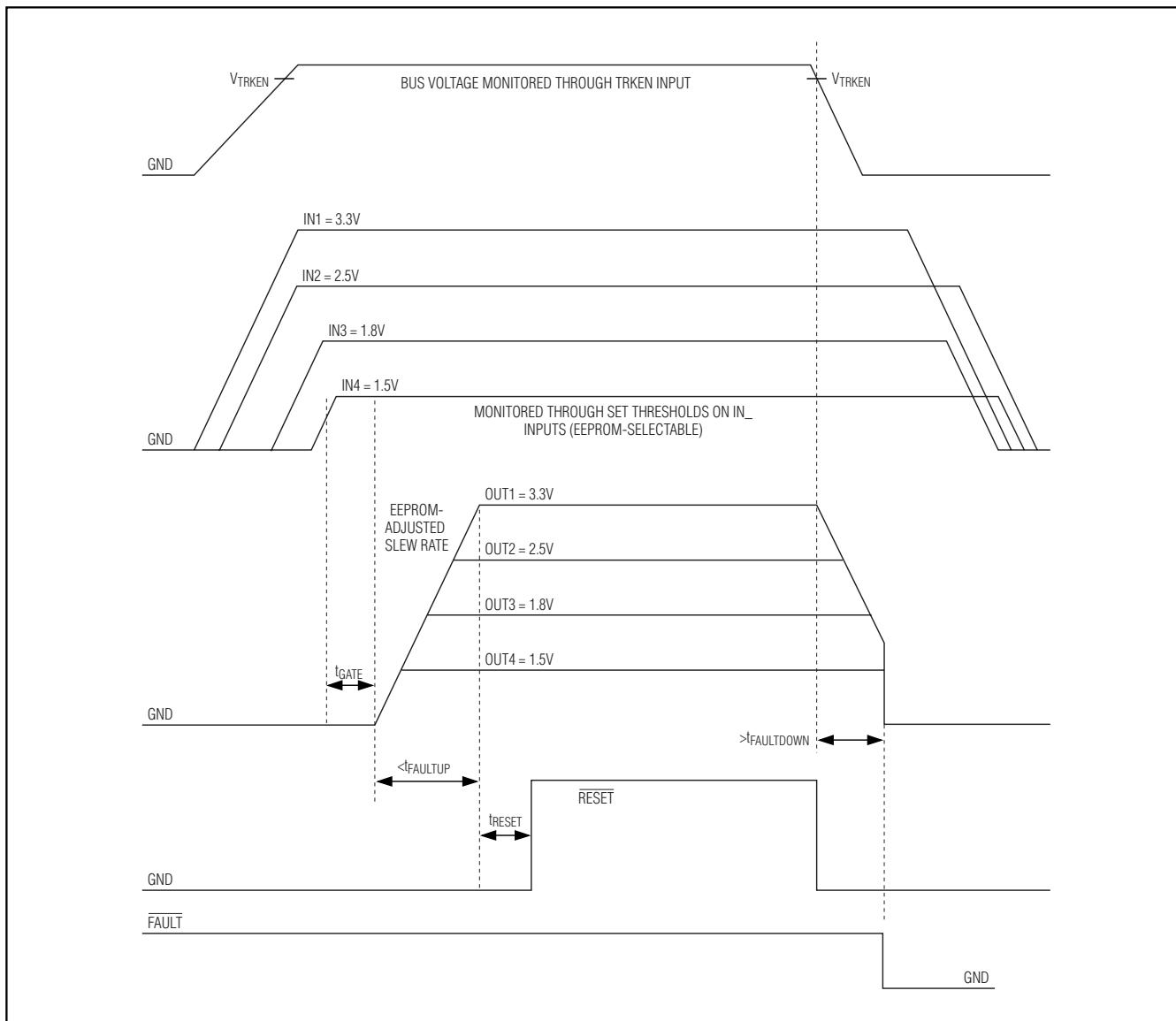

## Timing Diagrams

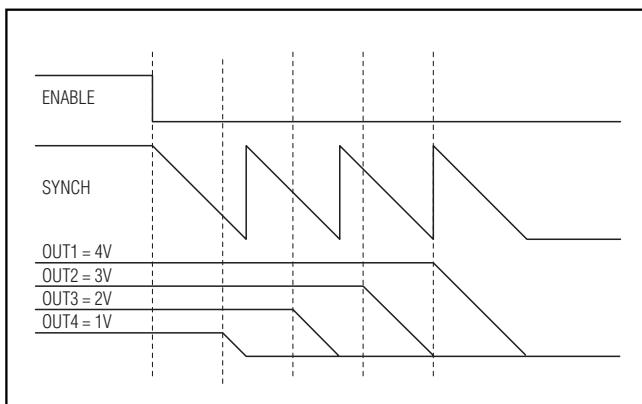

Figure 1. Tracking Timing Diagram

## EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

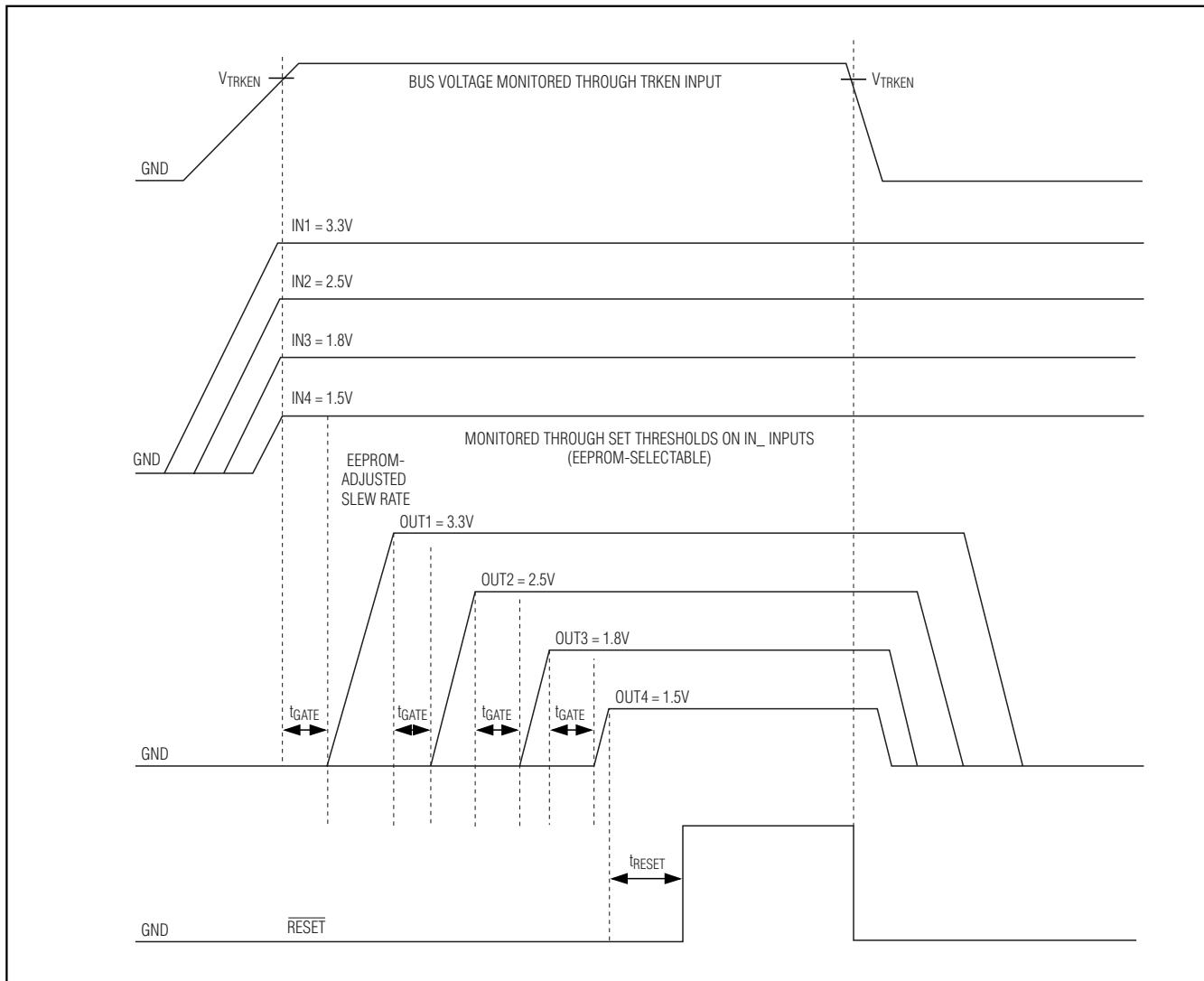

### Timing Diagrams (continued)

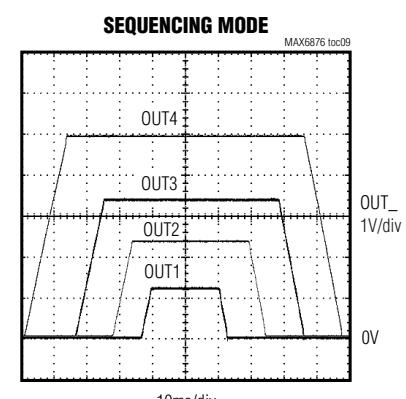

Figure 2. Sequencing Timing Diagram

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

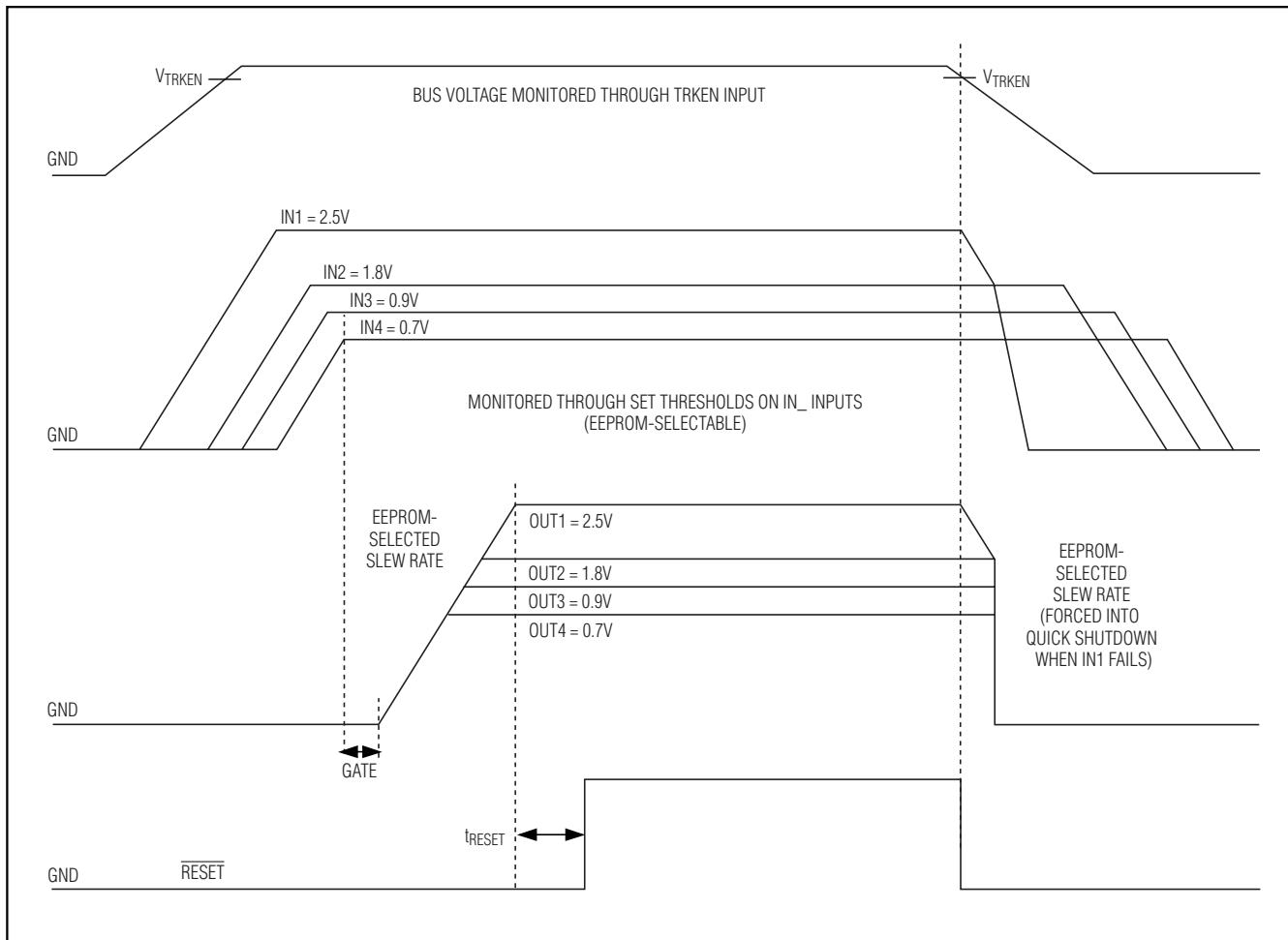

## Timing Diagrams (continued)

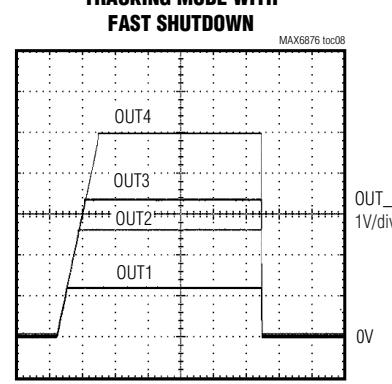

Figure 3. Voltage Tracking with Forced Shutdown (IN1 UV Failure)

Figure 4. Sequencing Ramp Down Diagram

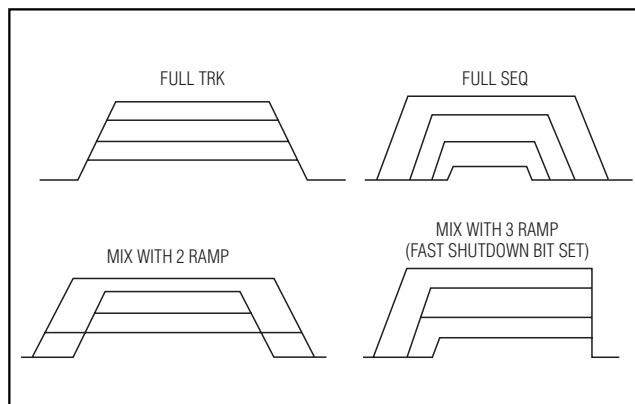

Figure 5. Mixed-Mode Tracking/Sequencing Examples

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

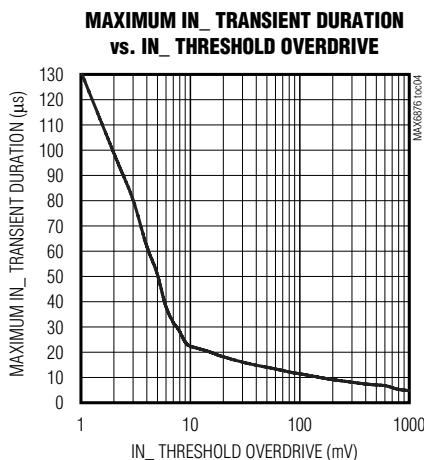

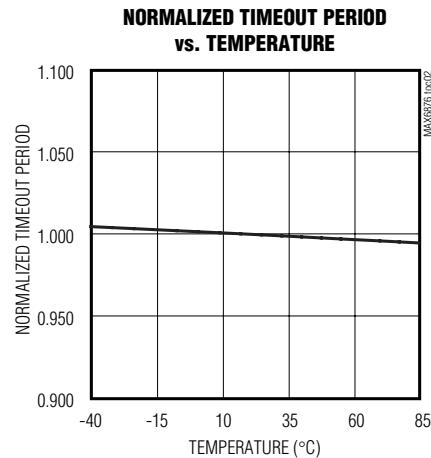

## Typical Operating Characteristics

( $V_{CC} = 3.3V$ , ENABLE =  $\overline{MARGIN} = \overline{MR} = \overline{ABP} = \overline{TRKEN}$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## Typical Operating Characteristics (continued)

( $V_{CC} = 3.3V$ ,  $ENABLE = \overline{MARGIN} = \overline{MR} = \overline{ABP} = \overline{TRKEN}$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

## Pin Description

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{CC}$ | Optional Supply Voltage Input. Connect $V_{CC}$ to an alternate (i.e., always-on) supply if desired. $V_{CC}$ supports operation/communication when the monitored supplies are not powered or are below the minimum required operating voltage. In a master/slave application, connect all $V_{CC}$ pins to a common supply line.                                                                                                                                                                                                                                                                                         |

| 2   | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | ABP      | Internal Analog Bypass. Bypass ABP with a $1\mu F$ capacitor to GND. ABP maintains the device supply voltage during rapid power-down conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | TRKEN    | Tracking Enable Input. TRKEN must be higher than $1.285V$ to enable voltage tracking power-up operation. When TRKEN falls below $1.25V$ (3% hysteresis), OUT <sub>_</sub> tracks down. Connect TRKEN to an external resistor-divider network to set the desired monitor threshold. Connect TRKEN to ABP if not used.                                                                                                                                                                                                                                                                                                      |

| 5   | SYNCH    | Selectable Tracking Synchronization Output/Input. SYNCH allows multiple MAX6876 devices to control tracking of multiple power supplies (up to 16 voltages on the same I <sup>2</sup> C bus). One device is programmed as SYNCH master and all other devices are programmed as slaves. SYNCH on the master outputs the common ramp voltage to which all OUT <sub>_</sub> voltages are tracked (with active control loops). SYNCH of the slave devices is input for the ramp control voltage (no internal ramp is generated in the slaves) (see the SYNCH section). Connect SYNCH to other SYNCH pins only.                 |

| 6   | HOLD     | Active-Low, Open-Drain Synchronization Hold Output/Input. HOLD communicates synchronization status between master/slave devices in multiple MAX6876 applications. The HOLD output remains asserted while selected tracking IN <sub>_</sub> inputs are below their selected thresholds (the slave device can delay tracking start until its inputs are at their required stable voltage levels) or held low by the master when it is counting the autoretry time after a detected fault condition (see the <i>Synchronization Hold Output (HOLD)</i> section). Slave device SYNCH are inputs for the ramp control voltage. |

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## Pin Description (continued)

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | $\overline{OC}$ | Active-Low, Open-Drain Overcurrent Output. $\overline{OC}$ asserts low if any monitored IN <sub>+</sub> to OUT <sub>+</sub> voltage falls out of the selected percentage of the IN <sub>+</sub> voltage range (V <sub>TH_OC</sub> ) for more than the programmed t <sub>OC</sub> . $\overline{OC}$ monitoring begins only after supply tracking or sequencing has been completed and is disabled during power-down operation.                                                                    |

| 8      | REM             | Open-Drain Bus Removal Output. REM signals when it is safe to remove the card after a controlled track/sequence-down operation. REM goes high impedance when all V <sub>OUT_</sub> < V <sub>TH_PL</sub> . REM requires an external pullup resistor. In master/slave mode, REM can be ORed together (the common REM connection remains low if any V <sub>OUT_</sub> > V <sub>TH_PL</sub> threshold) (see the <i>Typical Application Circuit</i> and the <i>Bus Removal Output (REM)</i> section). |

| 9      | FAULT           | Active-Low, Open-Drain Tracking Fault Alert Output or Input. FAULT asserts low if a tracking failure is present for longer than the specified fault period or if tracking voltages fails by more than $\pm 250\text{mV}$ (see the $\overline{FAULT}$ section).                                                                                                                                                                                                                                   |

| 10     | RESET           | Active-Low, Open-Drain Reset or Power-Good Output. $\overline{RESET}$ is low during power-up and power-down tracking. RESET goes high after all selected OUT <sub>+</sub> outputs exceed their selected thresholds and the reset timeout period t <sub>RESET</sub> has expired. The reset timeout period is internally selectable. RESET requires an external pullup resistor.                                                                                                                   |

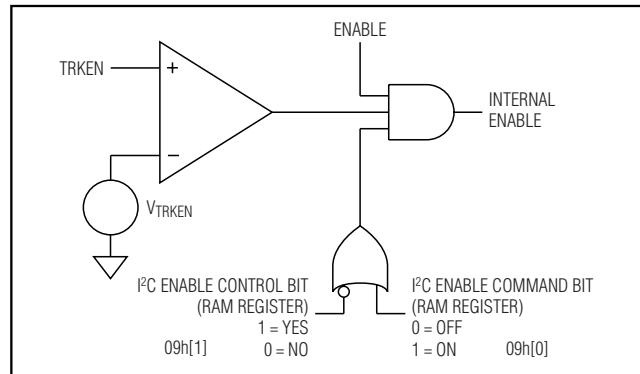

| 11     | ENABLE          | Logic ENABLE Input. ENABLE must be high to enable voltage tracking/sequencing power-up operation. OUT <sub>+</sub> begins tracking down when ENABLE is low. Connect to ABP if not used.                                                                                                                                                                                                                                                                                                          |

| 12     | MARGIN          | Active-Low Margin Input. The MARGIN function allows systems to be tested with supply voltages outside their normal ranges without affecting supply tracking/sequencing or reset states. MARGIN functionality is usually enabled after systems have powered up in normal mode. The MARGIN functionality is disabled (returns to normal monitoring mode) after MARGIN returns high. MARGIN is internally pulled up to ABP through a $100\text{k}\Omega$ resistor.                                  |

| 13, 23 | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14     | $\overline{MR}$ | Active-Low Manual Reset Input. When $\overline{MR}$ is low, RESET goes low and remains asserted for the selected timeout period after $\overline{MR}$ is pulled high. $\overline{MR}$ is internally pulled up to ABP through a $100\text{k}\Omega$ resistor.                                                                                                                                                                                                                                     |

| 15     | SDA             | Serial-Interface Data Input/Output (Open-Drain). SDA requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16     | SCL             | Serial-Interface Clock Input. SCL requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17     | A0              | Serial-Interface Address Inputs. The inputs allow up to four MAX6876 devices to be addressed when sharing a common data bus. A1 and A0 should be connected to GND or ABP.                                                                                                                                                                                                                                                                                                                        |

| 18     | A1              | Power-Good Output, Open-Drain. Each PG <sub>+</sub> output signals when its monitored OUT <sub>+</sub> voltage is within the selected percentage of the IN <sub>+</sub> voltage range (V <sub>TH_PG</sub> ). PG <sub>+</sub> is low until OUT <sub>+</sub> exceeds the programmable threshold (V <sub>TH_PG</sub> ) for more than t <sub>POK</sub> . PG <sub>+</sub> outputs are open-drain and require external pullups if used.                                                                |

| 19     | PG1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20     | PG2             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21     | PG3             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22     | PG4             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

MAX6876

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | REFIN | Reference Voltage Input. The MAX6876 can be configured to use the internal 1.25V reference or an external voltage reference. REFIN is tri-stated when using the internal reference. REFIN provides the threshold voltage for the voltage detectors when using an external voltage reference. Use an external voltage reference when tighter voltage-detector accuracy is desired. When configured to an internal reference, leave REFIN unconnected. When configured for an external reference, connect a 1.225V to 1.275V reference to REFIN.                                                                           |

| 25  | OUT4  | Monitored Output Voltage. The OUT4 output is monitored to control the supply slew rate and tracking performance. OUT1–OUT4 begin to track up after the internal supply (ABP) exceeds the minimum voltage requirements, $V_{TRKEN} > 1.285V$ threshold, ENABLE is logic high, and IN1–IN4 are all within their selected thresholds. The OUT4 output falls out of the tracking equation as OUT4 approaches IN4; other OUT_ supplies continue tracking up without signaling a system fault. OUT_ outputs are tracked down during power-off conditions.                                                                      |

| 26  | GATE4 | Gate Drive for External n-Channel FETs. GATE4 begins enhancing the external n-channel FETs when all monitored inputs are within their selected thresholds (0.5V to 5.5V), at least one IN_ input or VCC is above the minimum operating voltage, $V_{TRKEN} > 1.285V$ threshold, and the ENABLE input is logic high. During power-up mode, GATE_ voltages are enhanced with internal control loops forcing all OUT_ voltages to track the reference ramp (SYNCH) at a programmed slew rate. An internal charge pump boosts GATE4 to $V_{IN4} + 5V$ to fully enhance the external n-channel FET when power-up is complete. |

| 27  | IN4   | Supply Voltage and Tracked Input Voltage. Nominal supply range is 0.5V to 5V. IN1, IN2, IN3, IN4, or VCC must be greater than the internal UVLO ( $V_{ABP} = 2.7V$ ) to enable the tracking functionality. The IN4 input is monitored with internally selected thresholds to ensure all supplies have stabilized before tracking (or sequencing) is enabled.                                                                                                                                                                                                                                                             |

| 28  | OUT3  | Monitored Output Voltage. OUT3 is monitored to control the supply slew rate and tracking performance. OUT1–OUT4 begin to track up after the internal supply (ABP) exceeds the minimum voltage requirements, $V_{TRKEN} > 1.285V$ threshold, ENABLE is logic high, and IN1–IN4 are all within their selected thresholds. The OUT3 output falls out of the tracking equation as OUT3 approaches IN3; other OUT_ supplies continue tracking up without signaling a system fault. OUT_ outputs are tracked down during power-off conditions.                                                                                 |

| 29  | GATE3 | Gate Drive for External n-Channel FETs. GATE3 begins enhancing the external n-channel FETs when all monitored inputs are within their selected thresholds (0.5V to 5.5V), at least one IN_ input or VCC is above the minimum operating voltage, $V_{TRKEN} > 1.285V$ threshold, and the ENABLE input is logic high. During power-up mode, GATE_ voltages are enhanced with internal control loops forcing all OUT_ voltages to track the reference ramp (SYNCH) at a programmed slew rate. An internal charge pump boosts GATE3 to $V_{IN3} + 5V$ to fully enhance the external n-channel FET when power-up is complete. |

| 30  | IN3   | Supply Voltage and Tracked Input Voltage. Nominal supply range is 0.5V to 5V. IN1, IN2, IN3, IN4, or VCC must be greater than the internal UVLO ( $V_{ABP} = 2.7V$ ) to enable the tracking functionality. IN3 is monitored with internally selected thresholds to ensure all supplies have stabilized before tracking (or sequencing) is enabled.                                                                                                                                                                                                                                                                       |

| 31  | OUT2  | Monitored Output Voltage. OUT2 is monitored to control the supply slew rate and tracking performance. OUT1–OUT4 begin to track up after the internal supply (ABP) exceeds the minimum voltage requirements, $V_{TRKEN} > 1.285V$ threshold, ENABLE is logic high, and IN1–IN4 are all within their selected thresholds. OUT2 output falls out of the tracking equation as OUT2 approaches IN2; other OUT_ supplies continue tracking up without signaling a system fault. OUT_ outputs are tracked down during power-off conditions.                                                                                     |

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32  | GATE2 | Gate Drive for External n-Channel FETs. GATE2 begins enhancing the external n-channel FETs when all monitored inputs are within their selected thresholds (0.5V to 5.5V), at least one IN_ input or Vcc is above the minimum operating voltage, $V_{TRKEN} > 1.285V$ threshold, and the ENABLE input is logic high. During power-up mode, GATE_ voltages are enhanced with internal control loops forcing all OUT_ voltages to track the reference ramp (SYNCH) at a programmed slew rate. An internal charge pump boosts GATE2 to $V_{IN2} + 5V$ to fully enhance the external n-channel FET when power-up is complete. |

| 33  | IN2   | Supply Voltage and Tracked Input Voltage. Nominal supply range is 0.5V to 5V. IN1, IN2, IN3, IN4, or Vcc must be greater than the internal UVLO ( $V_{ABP} = 2.7V$ ) to enable the tracking functionality. IN2 is monitored with internally selected thresholds to ensure all supplies have stabilized before tracking (or sequencing) is enabled.                                                                                                                                                                                                                                                                       |

| 34  | OUT1  | Monitored Output Voltage. Each OUT1 is monitored to control the supply slew rate and tracking performance. OUT1-OUT4 begin to track up after the internal supply (ABP) exceeds the minimum voltage requirements, $V_{TRKEN} > 1.285V$ threshold, ENABLE is logic high, and IN1-IN4 are all within their selected thresholds. The OUT1 output falls out of the tracking equation as OUT1 approaches IN1; other OUT_ supplies continue tracking up without signaling a system fault. OUT_ outputs are tracked down during power-off conditions.                                                                            |

| 35  | GATE1 | Gate Drive for External n-Channel FETs. GATE1 begins enhancing the external n-channel FETs when all monitored inputs are within their selected thresholds (0.5V to 5.5V), at least one IN_ input or Vcc is above the minimum operating voltage, $V_{TRKEN} > 1.285V$ threshold, and the ENABLE input is logic high. During power-up mode, GATE_ voltages are enhanced with internal control loops forcing all OUT_ voltages to track the reference ramp (SYNCH) at a programmed slew rate. An internal charge pump boosts GATE1 to $V_{IN1} + 5V$ to fully enhance the external n-channel FET when power-up is complete. |

| 36  | IN1   | Supply Voltage and Tracked Input Voltage. Nominal supply range is 0.5V to 5V. IN1, IN2, IN3, IN4, or Vcc must be greater than the internal UVLO ( $V_{ABP} = 2.7V$ ) to enable the tracking functionality. IN1 is monitored with internally selected thresholds to ensure all supplies have stabilized before tracking (or sequencing) is enabled.                                                                                                                                                                                                                                                                       |

| —   | EP    | Exposed Paddle. Exposed paddle is internally connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

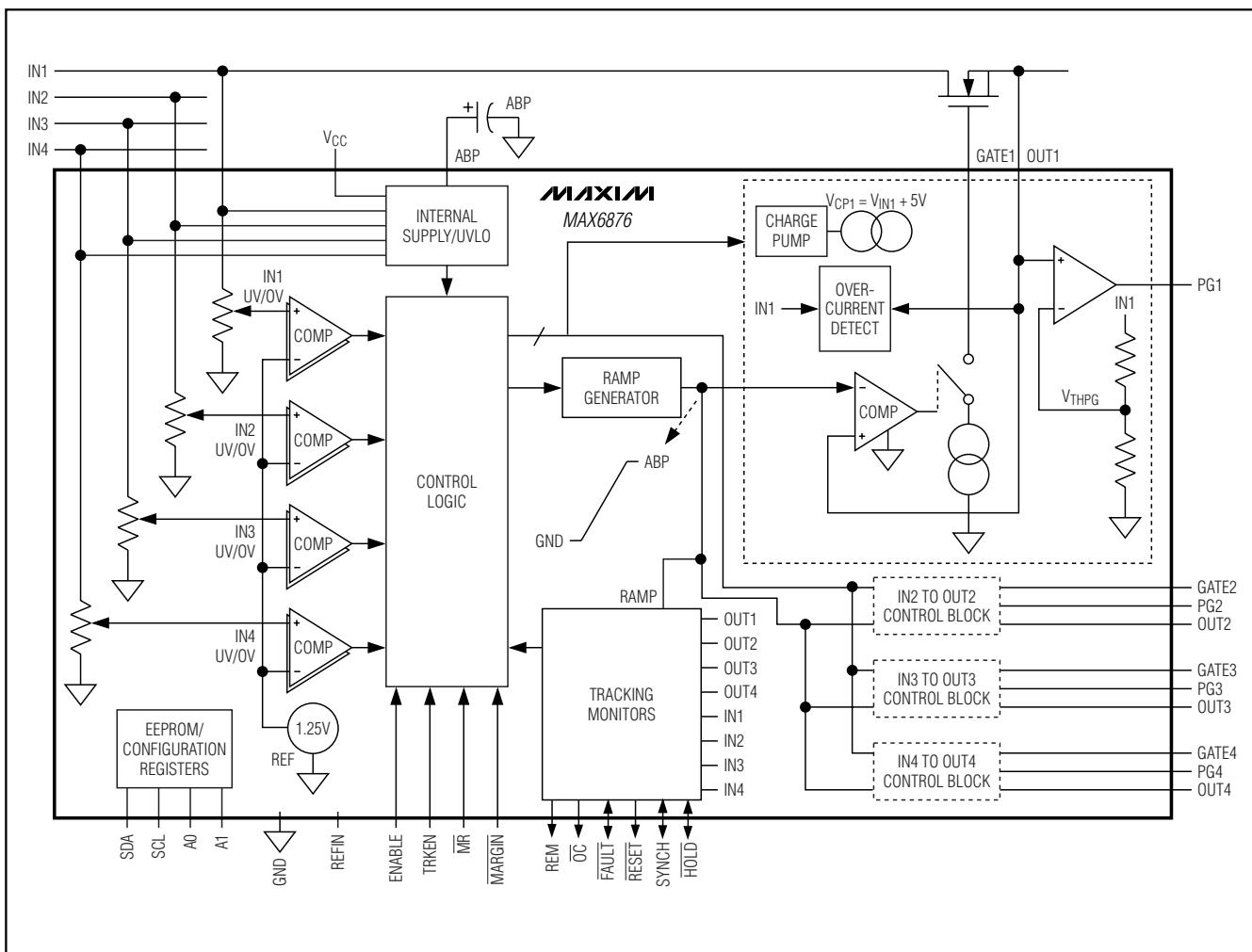

## Detailed Description

The MAX6876 EEPROM-configurable, multivoltage power tracker/supervisor monitors four system voltages and ensures proper power-up and power-down conditions for systems requiring voltage tracking and/or sequencing. The MAX6876 provides a highly configurable solution as key thresholds and timing parameters are programmed through an I<sup>2</sup>C interface and these values are stored in internal EEPROM. In addition to tracking and sequencing voltages, the MAX6876 also provides supervisory functions as well as an over-current detection circuit.

The MAX6876 features programmable undervoltage and overvoltage thresholds for each input supply. The thresholds are EEPROM configured in 10mV (0.5V to 3.05V) or 20mV (1.0V to 5.5V) increments. When all of the voltages are within their specifications, the device turns on the external n-channel MOSFETs to either sequence or track the voltages to the system. All of the voltages can be sequenced or tracked or powered up with a combination of the two options. During voltage tracking, the voltage at the GATE of each MOSFET is increased to slowly turn on each OUT\_. The GATE delay is EEPROM-selectable from 25μs to 1.6s. The

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

## Functional Diagram

voltages at the sources of the MOSFETs are compared to each other to ensure that the voltage differential between each monitored supply does not exceed 250mV (typ). Tracking is dynamically adjusted to force all outputs to track within a  $\pm 125$ mV window from a reference ramp; if, for any reason, any supply fails to track within  $\pm 250$ mV from the reference ramp, the FAULT output is asserted, the power-up mode is terminated, and all outputs are powered off. Power-up mode is in the same way terminated if the controlled voltages fail to complete the ramp up within a programmable FAULT timeout. The MAX6876 generates all required voltages (with internal charge pumps) and timing to control up to four external n-channel MOSFETs for the OUT1-OUT4 supply voltages.

A synchronization feature allows up to 16 voltages to be tracked simultaneously. In addition, HOLD and SYNCH communicate synchronization status between master/slave devices in multiple MAX6876 applications. Other features of the MAX6876 include a reset circuit with an I<sup>2</sup>C-programmable timeout feature. A manual reset input (MR) and a margin disable input (MARGIN) allow for more control during the manufacturing process. The device also features four power-good outputs (PG<sub>1</sub>-<sub>4</sub>), an overcurrent output (OC), and a bus-removal safe (REM) output. The device has an accurate internal 1.25V reference; for greater accuracy, connect an external +1.25V reference to REFIN.

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

**Table 1. Master/Slave Settings**

| REGISTER ADDRESS | EEPROM MEMORY ADDRESS | BIT RANGE | DESCRIPTION                                                                                                                                                                                                                                                                  |

|------------------|-----------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09h              | 29h                   | [7:6]     | <p>If “00,” the device configuration is a single device.</p> <p>If “01,” the device configuration is multiple devices, slave.</p> <p>If “10,” the device configuration is multiple devices, slave.</p> <p>If “11,” the device configuration is multiple devices, master.</p> |

### Modes of Operation

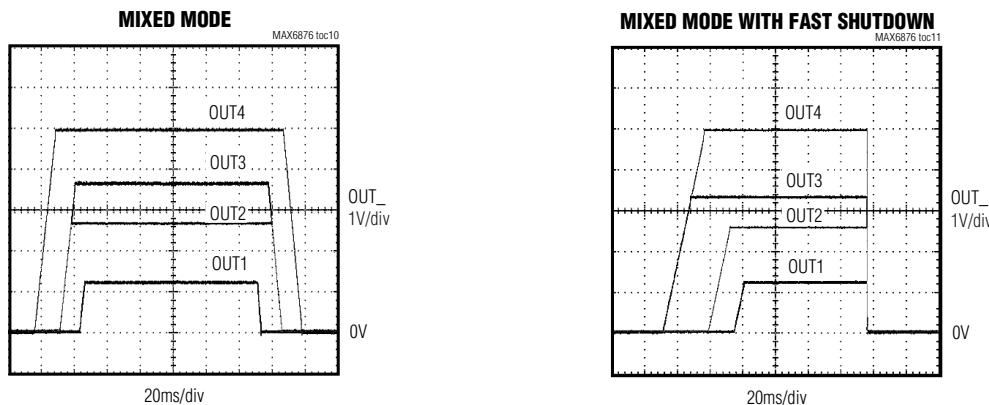

The MAX6876 provides three different modes of operation: tracking, sequencing, and mixed modes. The mixed mode is a combination of both tracking and sequencing modes (see the *Mixed Mode (Tracking/Sequencing)* section).

### Tracking

When all selected inputs exceed their selected thresholds,  $VTRKEN > 1.285V$ , and ENABLE is logic high, the tracking process is initialized. The MAX6876 generates an internal ramp voltage that drives the control loops for the desired tracked voltage. The tracking functionality is monitored with a comparator control block (see the *Functional Diagram* and Figure 5). The comparators monitor and control each output voltage with respect to the common tracking ramp voltage to stay within a  $\pm 125mV$  differential window, monitor each tracked output voltage with respect to its input voltage, and monitor each output voltage with respect to GND during power-up/retry cycles. Under normal conditions each OUT<sub>\_</sub> voltage will track the ramp voltage until the OUT<sub>\_</sub> voltage approximates the IN<sub>\_</sub> voltage (the external n-channel FET is saturated). The slew rate for the ramp voltage is selected through EEPROM.

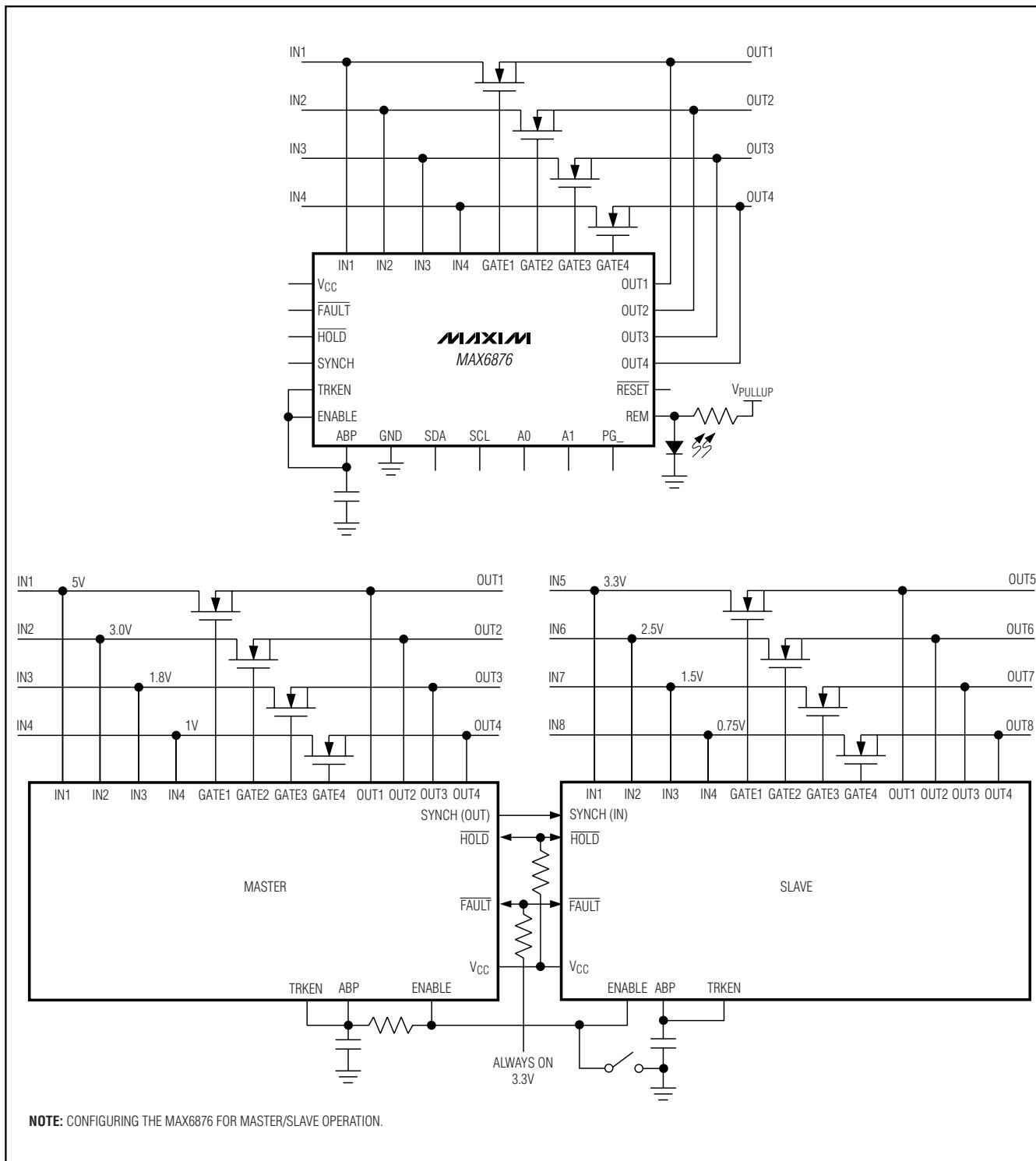

### Master/Slave Operation (Tracking Only)

To support voltage tracking for more than four supplies, combine multiple MAX6876 devices. Two MAX6876 devices (one master/one slave) track up to eight supply voltages and four MAX6876 devices (one master and three slaves) track up to 16 supply voltages. Each device must be programmed to act in master or slave mode (only one master is allowed); the default state is single device (see Table 1). The MAX6876 outputs the ramp control voltage with the SYNCH output when configured as a master device. This ramp allows multiple devices to synchronize with the master when slave SYNCHs are configured as inputs. For proper functionality control, connect all ENABLE pins together. In master/slave mode, all controlled supplies are tracked up/down (no mixed sequencing/tracking modes are supported). In master-slave application, the part is

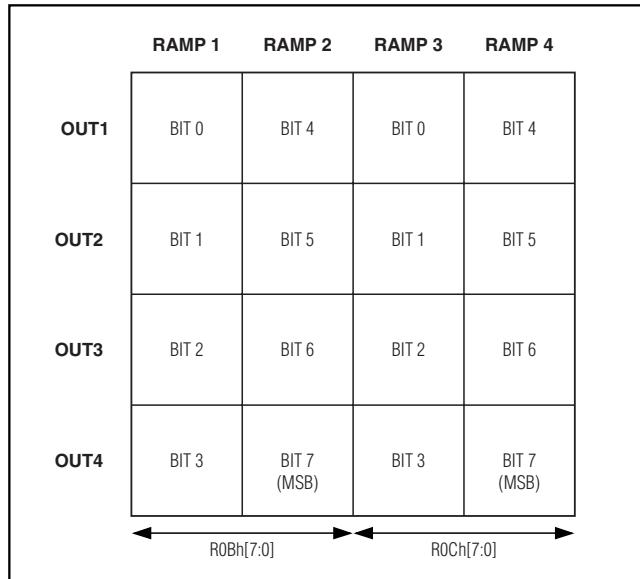

Figure 6. Mapping Tracking and Sequencing Modes

intended to provide only tracking for the four supplies (only one ramp is generated). To control one particular channel, insert a “1” in any of the four possible positions (one row for each channel contains 4 bits) and the circuit will generate the proper signals (see Figure 6).

For multiple MAX6876 operations, the ramp control voltage is brought out of the master's SYNCH (programmed as an output) and into the slave's SYNCH (programmed as an input). The highest tracked supply must be connected to one of the master's IN<sub>\_</sub> inputs. When all IN<sub>\_</sub> threshold conditions are met (on master and slaves), the master ramp begins rising at the selected ramp slew rate. During normal operation all OUT<sub>\_</sub> voltages (for master and slave) track the ramp voltage. If the slave's OUT<sub>\_</sub> voltages do not properly follow the ramp voltage (exceed 125mV differential), the slave device asserts HOLD low. The master recognizes the HOLD and holds the ramp voltage, allowing the slave's slower OUT<sub>\_</sub> voltages to

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

catch up. When the slave's voltages approach the ramp voltage, the slave releases HOLD and the master allows the ramp voltage to begin rising again. All tracking must be completed by the selected tracking fault timeout period or the supplies are powered down. The slave HOLD output is asserted low until the selected tracking IN\_ voltages are within their selected thresholds. This ensures that the master does not begin the tracking operation until the slave's input voltages (IN\_) have properly stabilized.

## Sequencing

The sequencing operation can be initialized by properly setting the bit of registers 0Bh and 0Ch. During a sequencing power-up phase, each OUT\_ is independently powered on with a controlled slew rate. No more than one supply is powered on for each generated ramp. The bits of registers 0Bh and 0Ch establish the turn-on order. During each phase, the ramp is enabled to start only after the tGATE timeout has been counted. The sequencing phase will be considered complete when all the channels programmed to power on reach the independently set PG\_ thresholds (see Figure 5).

## Mixed Mode (Tracking/Sequencing)

The MAX6876 is fully programmable to generate up to four ramps during power-up or power-down modes. Each OUT\_ voltage independently is programmed to follow any of the control ramps generated by the MAX6876. To do the latter, set the bits on register 0Bh and 0Ch to "1" for each channel. The following are programming examples of different power-up modes (→ = sequence, / = track):

0Bh = 0000 1111 0Ch = 0000 0000 tracking mode:

OUT1/OUT2/OUT3/OUT4 on Ramp1

0Bh = 1000 0100 0Ch = 0010 0001 sequencing mode:

OUT3 → OUT4 → OUT1 → OUT2 on Ramp1,

Ramp2, Ramp3, Ramp4

0Bh = 1100 0001 0Ch = 0010 0000 mix mode\*: OUT1

→ OUT4/OUT3 → OUT2 on Ramp1, Ramp2, Ramp4

\*(Ramp3 is not considered because no OUT\_ outputs are selected by bit [0:3] of 0Ch.)

Drive ENABLE or TRKEN low or use a software command to initiate a controlled power-down. The MAX6876 powers down the OUT\_ voltages in a reverse sequence from the one at power-up when this option is selected.

For example, with the following power-up sequence:

OUT1 → OUT4/OUT3 → OUT2

then the power-down sequence will be:

OUT2 → OUT4/OUT3 → OUT1

## Configuring Tracking and Sequencing Modes

To configure tracking and sequencing modes, insert "1" and "0" into the 0Bh and 0Ch registers (see Table 2). Figure 6 shows how to map for tracking and sequencing modes. Each OUT\_ output can follow one of the four possible ramps in tracking or sequencing mode (16 bits are available) and one bit set to "1," means that the channel of the interested row is powered up/down by the corresponding ramp (see Figure 6).

- 1) If the depicted table (in Figure 6) is made by all "1s," the part simply generates a single ramp (all channels in tracking mode since the first column is full of "1s,") and it ignores the remaining values of the other 12 bits.

- 2) If one row contains more than one symbol "1," only the first encountered (columns starting with R0Bh [3:0]) is taken into account and the channel is powered up/down with the corresponding ramp.

- 3) If there is one (or more) row in which all 4 bits are set to "0," it means that the device will not control that particular channel.

- 4) If there is one (or more) column where all 4 bits are set to "0," the device skips that ramp and its associate tD-GATE.

In master-slave applications, the device is intended to provide only tracking for the four supplies (only one ramp can be generated). To control one particular channel, only insert a "1" in any of the four possible positions (one row for each channel contains 4 bits) and the device generates the proper signals. When three or less ramps are needed, use consecutive ramps starting with ramp 1.

## Power-Down and Power-Up

When all the IN\_ inputs are within the selected threshold range and the internal enable is logic high (Figure 7), the device initiates a power-up phase. During power-up, the OUT\_ outputs are forced by an internal loop that controls the GATE\_ of the external MOSFET to follow the reference ramp voltage. This phase for each individual ramp must be completed within the programmable fault timeout time; otherwise, the part will force a shutdown on the GATE\_. Once the power-up is completed, a power-down phase can be initiated by forcing the internal enable low. Two power-down options are available: a fast-shutdown option where all GATE\_ gates are quickly turned off or a reverse-order option. This reverse-order option allows the OUT\_ voltage to be powered down with a controlled slew rate and in the reverse order they have been powered up (see Figure 2).

# EEPROM-Programmable, Quad, Power-Supply Tracker/Sequencer Circuit

**Table 2. Configuring Tracking and Sequencing Modes**

| REGISTER ADDRESS | EEPROM MEMORY ADDRESS | BIT RANGE | DESCRIPTION                                                                                                                                                                                                                                  |

|------------------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|