### **General Description**

The MAX6846-MAX6849 are a family of ultra-low-power battery monitors with integrated microprocessor (uP) supervisors. The user-adjustable battery monitors are offered with single or dual low-battery output options that can be used to signal when the battery is OK (enabling full system operation), when the battery is low (for lowpower system operation), and when the battery is dead (to disable system operation). These devices also have an independent µP supervisor that monitors VCC and provides an active-low reset output. A manual reset function is available to reset the  $\mu P$  with a pushbutton.

The MAX6846-MAX6849 are ideal for single-cell lithiumion (Li+) or multicell alkaline/NiCd/NiMH applications. When the battery voltage drops below each adjusted low threshold, the low-battery outputs are asserted to alert the system. When the voltage rises above the adjusted high thresholds, the outputs are deasserted after a 150ms minimum timeout period, ensuring the voltages have stabilized before power circuitry is activated or providing microprocessor reset timing.

These devices have user-adjustable battery threshold voltages, providing a wide hysteresis range to prevent chattering that can result due to battery recovery after load removal. Single low-battery outputs are supplied by the MAX6846/MAX6847 and dual low-battery outputs are supplied by the MAX6848/MAX6849. All battery monitors have open-drain low-battery outputs.

The MAX6846-MAX6849 monitor system voltages (VCC) from 1.8V to 3.3V with seven fixed reset threshold options. Each device is offered with two minimum reset timeout periods of 150ms or 1200ms. The MAX6846/ MAX6848 are offered with an open-drain RESET output and the MAX6847/MAX6849 are offered with a pushpull RESET output.

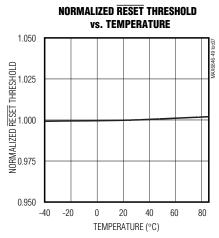

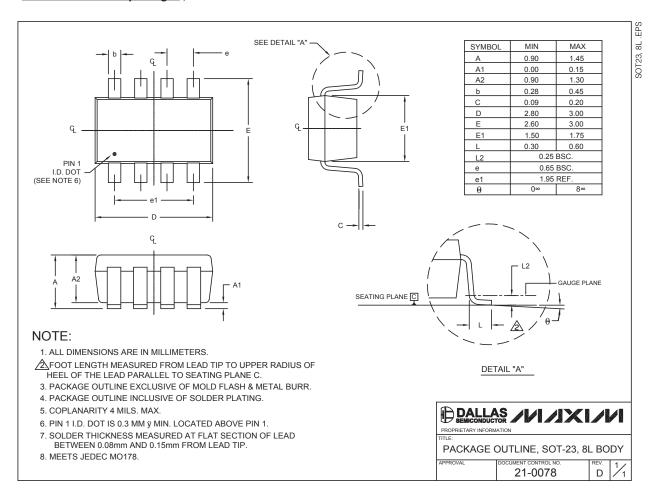

The MAX6846-MAX6849 are offered in a SOT23 package and are fully specified over a -40°C to +85°C temperature range.

## **Applications**

Battery-Powered Systems (Single-Cell Li+ or Multicell NiMH, NiCd, Alkaline)

Portable Medical Devices

Digital Cameras

Pagers

**PDAs**

MP3 Players

AXM

**Electronic Toys**

## **Features**

- User-Adjustable Thresholds for Monitoring Single-Cell Li+ or Multicell Alkaline/NiCd/NiMH **Applications**

- Single and Dual Low-Battery Output Options

- ♦ Independent µP Reset with Manual Reset

- ◆ Factory-Set Reset Thresholds for Monitoring 1.8V to 3.3V Systems

- ♦ Available with 150ms (min) or 1.2s (min) V<sub>CC</sub> **Reset Timeout Period Options**

- ♦ 150ms (min) LBO Timeout Period

- Immune to Short-Battery Voltage Transients

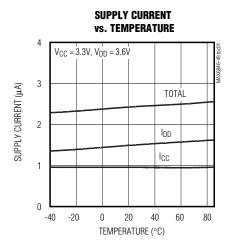

- ♦ Low Current (2.5µA, typ at 3.6V)

- ♦ -40°C to +85°C Operating Temperature Range

- ♦ Small 8-Pin SOT23 Packages

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX6846KA_DT | -40°C to +85°C | 8 SOT23-8   |

| MAX6847KA_DT | -40°C to +85°C | 8 SOT23-8   |

| MAX6848KA_DT | -40°C to +85°C | 8 SOT23-8   |

| MAX6849KA_DT | -40°C to +85°C | 8 SOT23-8   |

**Note:** The first "\_" is the V<sub>CC</sub> reset threshold level, suffix found in Table 1. The "\_" after the D is a placeholder for the reset timeout period suffix found in Table 2. All devices are available in tape-and-reel only. There is a 2500 piece minimum order increment for standard versions (see Standard Versions table). Sample stock is typically held on standard versions only. Nonstandard versions require a minimum order increment of 10,000 pieces. Contact factory for availability.

Devices are available in both leaded and lead-free packaging. Specify lead-free by replacing "-T" with "+T" when ordering.

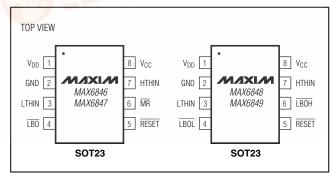

## Pin Configurations

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| VDD, VCC to GND                    | -0.3V to +6V* |

|------------------------------------|---------------|

| Open-Drain LBO. LBOH. LBOL to GND. |               |

| Open-Drain RESET to GND            |               |

| Push-Pull RESET to GND             |               |

| HTHIN, LTHIN to GND                |               |

| MR to GND                          | ` ,           |

|                                    | ( 00 ,        |

| Input/Output Current, All Pins     | 20MA          |

Continuous Power Dissipation (TA = +70°C)

8-Pin SOT23 (derate 8.9mW/°C above +70°C).......714mW

Operating Temperature Range .....-40°C to +85°C

Junction Temperature .....+150°C

Storage Temperature Range ....-65°C to +150°C

Lead Temperature (soldering, 10s) .....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 1.6 \text{V to } 5.5 \text{V}, V_{CC} = 1.2 \text{V to } 5.5 \text{V}, T_{A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise specified. Typical values are at  $T_{A} = +25 ^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                        | SYMBOL             | CONDITIONS                                                                                    | MIN | TYP | MAX | UNITS |

|--------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| V <sub>DD</sub> Operating Voltage Range          | $V_{\mathrm{DD}}$  |                                                                                               | 1.6 |     | 5.5 | V     |

| V <sub>CC</sub> Operating Voltage Range          | V <sub>CC</sub>    | $T_A = 0$ °C to +85°C                                                                         | 1.0 |     | 5.5 | V     |

| VCC Operating Voltage Hange                      | VCC                | $T_A = -40$ °C to $+85$ °C                                                                    | 1.2 |     | 5.5 | V     |

| V <sub>CC</sub> + V <sub>DD</sub> Supply Current | ICC + IDD          | V <sub>DD</sub> = 3.6V, V <sub>CC</sub> = 3.3V, no load (Note 2)                              |     | 2.5 | 7   | μΑ    |

| MAX6846/MAX6847 V <sub>DD</sub> THRESI           | HOLDS              |                                                                                               |     |     |     |       |

| HTHIN Threshold                                  | Vнтн               | HTHIN rising, LBO is deasserted when HTHIN rises above V <sub>HTH</sub>                       | 600 | 615 | 630 | mV    |

| LTHIN Threshold                                  | VLTH               | LTHIN falling, $\overline{\text{LBO}}$ is asserted when LTHIN falls below V <sub>LTH</sub>    | 600 | 615 | 630 | mV    |

| MAX6848/MAX6849 V <sub>DD</sub> THRESI           | HOLDS              |                                                                                               |     |     |     |       |

| HTHIN+ Threshold                                 | V <sub>HTH+</sub>  | HTHIN rising, $\overline{\text{LBOH}}$ is deasserted when HTHIN rises above V <sub>HTH+</sub> | 600 | 615 | 630 | mV    |

| HTHIN- Threshold                                 | VHTH-              | HTHIN falling, LBOH is asserted when HTHIN falls below V <sub>HTH</sub> -                     | 567 | 582 | 597 | mV    |

| LTHIN+ Threshold                                 | V <sub>LTH+</sub>  | LTHIN rising, \( \overline{LBOL} \) is deasserted when LTHIN rises above \( V_{LTH+} \)       | 600 | 615 | 630 | mV    |

| LTHIN- Threshold                                 | V <sub>LTH</sub> - | LTHIN falling, TBOL is asserted when LTHIN falls below V <sub>LTH</sub> -                     | 567 | 582 | 597 | mV    |

| MAX6846-MAX6849                                  |                    |                                                                                               |     |     |     |       |

| HTHIN/LTHIN Leakage Current                      | ILKG               | V <sub>HTHIN</sub> or V <sub>LTHIN</sub> ≥ 400mV                                              |     |     | 20  | nA    |

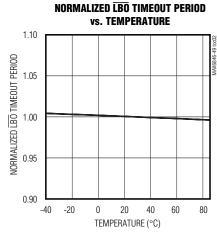

| LBO, LBOL, LBOH Timeout Period                   | tLBOP              | HTHIN/LTHIN rising above threshold                                                            | 150 | 225 | 300 | ms    |

| LBO, LBOL, LBOH Delay Time                       | tLBOD              | HTHIN/LTHIN falling below threshold                                                           |     | 100 |     | μs    |

|                                                  |                    | $(V_{DD} \text{ or } V_{CC}) \ge 1.2V$ , $I_{SINK} = 50\mu\text{A}$ , asserted low            |     |     | 0.3 |       |

| LBO, LBOL, LBOH Output Low                       | .,,                | $(V_{DD} \text{ or } V_{CC}) \ge 1.6V,  I_{SINK} = 100 \mu\text{A},$ asserted low             |     |     | 0.3 |       |

| LBO, LBOE, LBOH Output LOW                       | VoL                | (V <sub>DD</sub> or V <sub>CC</sub> ) ≥ 2.7V, I <sub>SINK</sub> = 1.2mA, asserted low         |     |     | 0.3 | V     |

|                                                  |                    | (V <sub>DD</sub> or V <sub>CC</sub> ) ≥ 4.5V, I <sub>SINK</sub> = 3.2mA, asserted low         |     |     | 0.3 |       |

<sup>\*</sup>Applying 7V for a duration of 1ms does not damage the device.

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 1.6V \text{ to } 5.5V, V_{CC} = 1.2V \text{ to } 5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                            | SYMBOL           | CONDITIONS                                                                                     | MIN                   | TYP   | MAX   | UNITS |  |

|------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------|-----------------------|-------|-------|-------|--|

| LBO, LBOL, LBOH Output<br>Open-Drain Leakage Current |                  | Output deasserted                                                                              |                       |       | 500   | nA    |  |

|                                                      |                  | MAX68 T                                                                                        | 3.000                 | 3.075 | 3.150 | 1     |  |

|                                                      |                  | MAX68 S                                                                                        | 2.850                 | 2.925 | 3.000 |       |  |

|                                                      |                  | MAX68 R                                                                                        | 2.550                 | 2.625 | 2.700 |       |  |

| V <sub>CC</sub> Reset Threshold                      | V <sub>TH</sub>  | MAX68 Z                                                                                        | 2.250                 | 2.313 | 2.375 | V     |  |

|                                                      |                  | MAX68 Y                                                                                        | 2.125                 | 2.188 | 2.250 |       |  |

|                                                      |                  | MAX68 W                                                                                        | 1.620                 | 1.665 | 1.710 |       |  |

|                                                      |                  |                                                                                                | 1.530                 | 1.575 | 1.620 |       |  |

| V <sub>CC</sub> Reset Hysteresis                     |                  |                                                                                                |                       | 0.3   |       | %     |  |

| V <sub>CC</sub> to RESET Delay                       | t <sub>RD</sub>  | V <sub>CC</sub> falling at 10mV/µs from (V <sub>TH</sub> + 100mV) to (V <sub>TH</sub> - 100mV) |                       | 50    |       | μs    |  |

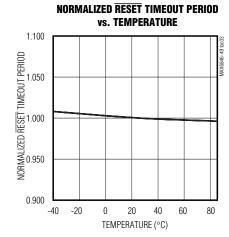

| V - <del>DECET</del> T:                              |                  | MAX68 D3                                                                                       | 150                   | 225   | 300   | ms    |  |

| V <sub>CC</sub> to RESET Timeout Period              | t <sub>RP</sub>  | MAX68 D7                                                                                       | 1200                  | 1800  | 2400  |       |  |

|                                                      | VIL              |                                                                                                | 0.3 x V <sub>CC</sub> |       |       |       |  |

| MR Input Voltage                                     | V <sub>IH</sub>  |                                                                                                |                       |       | V     |       |  |

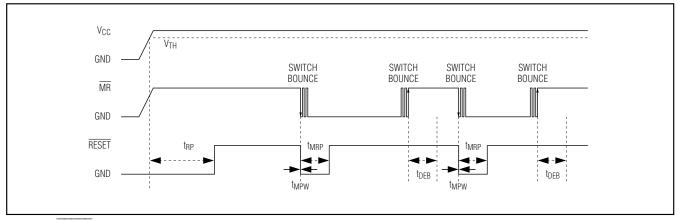

| MR Minimum Pulse Width                               | t <sub>MPW</sub> |                                                                                                | 1                     |       |       | μs    |  |

| MR Glitch Rejection                                  |                  |                                                                                                |                       | 100   |       | ns    |  |

| MR to RESET Delay                                    |                  |                                                                                                |                       | 200   |       | ns    |  |

| MR Reset Timeout Period                              | tmrp             |                                                                                                | 150                   | 225   | 300   | ms    |  |

| MR Pullup Resistance                                 |                  | MR to V <sub>CC</sub>                                                                          | 750                   | 1500  | 2250  | Ω     |  |

| MR Rising Debounce Period                            | tDEB             | (Note 3)                                                                                       | 150                   | 225   | 300   | ms    |  |

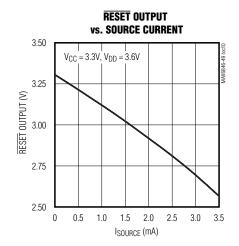

| RESET Output High<br>(Push-Pull)                     |                  | V <sub>CC</sub> ≥ 1.53V, I <sub>SOURCE</sub> = 100µA, RESET deasserted                         | 0.8 x V <sub>CC</sub> |       |       |       |  |

|                                                      | VOH              | V <sub>CC</sub> ≥ 2.55V, I <sub>SOURCE</sub> = 500µA, RESET deasserted                         | 0.8 x V <sub>CC</sub> |       |       | V     |  |

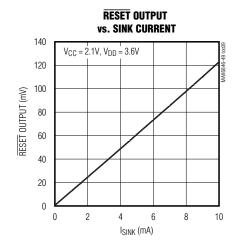

| RESET Output Low                                     |                  | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub> = 50µA, RESET asserted                               |                       |       | 0.3   |       |  |

|                                                      | V                | V <sub>CC</sub> ≥ 1.2V, I <sub>SINK</sub> = 100μA, RESET asserted                              |                       |       | 0.3   |       |  |

|                                                      | VoL              | V <sub>CC</sub> ≥ 2.12V, I <sub>SINK</sub> = 1.2mA, RESET asserted                             |                       |       | 0.3   | V     |  |

| RESET Output Leakage Current (Open Drain)            |                  | RESET deasserted                                                                               |                       |       | 500   | nA    |  |

Note 1: Production testing done at T<sub>A</sub> = +25°C; limits over temperature guaranteed by design only.

Note 2: The device is powered up by the highest voltage between  $V_{\mbox{\scriptsize DD}}$  and  $V_{\mbox{\scriptsize CC}}.$

Note 3: MR input ignores falling input pulses, which occur within the MR debounce period (t<sub>DEB</sub>) after a valid MR reset assertion. This prevents invalid reset assertion due to switch bounce.

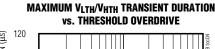

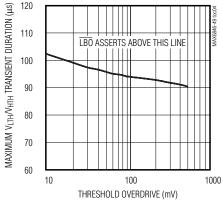

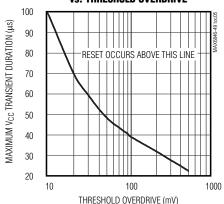

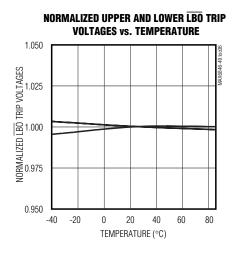

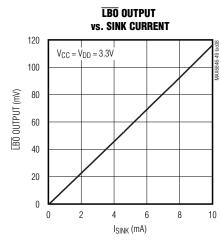

### **Typical Operating Characteristics**

$(V_{DD} = 3.6V, V_{CC} = 3.3V, unless otherwise specified. Typical values are at T_A = +25°C.)$

## $\begin{array}{c} \text{MAXIMUM V}_{\text{CC}} \text{ TRANSIENT DURATION} \\ \text{vs. THRESHOLD OVERDRIVE} \end{array}$

## Typical Operating Characteristics (continued)

$(V_{DD} = 3.6V, V_{CC} = 3.3V, unless otherwise specified. Typical values are at T_A = +25°C.)$

**Pin Description**

| PIN             |                 | NAME     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX6846/MAX6847 | MAX6848/MAX6849 | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 1               | 1               | $V_{DD}$ | V <sub>DD</sub> Supply. Device power supply if V <sub>DD</sub> is greater than V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 2               | 2               | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 3               | 3               | LTHIN    | LTH Threshold Monitor Input. A resistor-divider network sets the low threshold associated with $\overline{\text{LBOL}}$ and $\overline{\text{LBO}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 4               | _               | ĪBO      | Low-Battery Output, Active-Low, Open-Drain. LBO is asserted when LTHIN drops below the V <sub>LTH</sub> specification and remains asserted until HTHIN rises above the V <sub>HTH</sub> specification for at least 150ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 5               | 5               | RESET    | Reset Output, Active-Low, Push-Pull, or Open-Drain. $\overline{\text{RESET}}$ goes from high to low when the V <sub>CC</sub> input drops below the selected reset threshold and remains low for the V <sub>CC</sub> reset timeout period after V <sub>CC</sub> exceeds the reset threshold. $\overline{\text{RESET}}$ is one-shot edge-trigger pulsed low for the $\overline{\text{MR}}$ reset timeout period when the $\overline{\text{MR}}$ input is pulled low. $\overline{\text{RESET}}$ is an open-drain output for the MAX6846/MAX6848, and a push-pull output for the MAX6849. The push-pull outputs are referenced to V <sub>CC</sub> . $\overline{\text{RESET}}$ is guaranteed to be in the correct logic state for V <sub>DD</sub> or V <sub>CC</sub> $\geq$ 10V. |  |

| 6               |                 | MR       | Manual Reset Input, Active-Low, Internal 1.5k $\Omega$ Pullup to V <sub>CC</sub> . Pull $\overline{\text{MR}}$ low to assert a one-shot reset output pulse for the $\overline{\text{MR}}$ reset timeout period. Leave unconnected or connect to V <sub>CC</sub> if unused. The $\overline{\text{MR}}$ input is debounced for $\overline{\text{MR}}$ rising edges to prevent false reset events.                                                                                                                                                                                                                                                                                                                                                                             |  |

| 7               | 7               | HTHIN    | HTH Threshold Monitor Input. A resistor-divider network sets the high threshold associated with $\overline{\text{LBOH}}$ and $\overline{\text{LBO}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 8               | 8               | Vcc      | V <sub>CC</sub> Voltage Input. Input for V <sub>CC</sub> reset threshold monitor and device power supply if V <sub>CC</sub> is greater than V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| _               | 6               | LBOH     | Low-Battery Output High, Active-Low, Open-Drain. $\overline{\text{LBOH}}$ is asserted when HTHIN drops below the V <sub>HTH-</sub> specification. $\overline{\text{LBOH}}$ is deasserted when HTHIN rises above the V <sub>HTH+</sub> specification for at least 150ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| _               | 4               | LBOL     | Low-Battery Output Low, Active-Low, Open-Drain. $\overline{\text{LBOL}}$ is asserted when LTHIN drops below the $V_{\text{LTH-}}$ specification. $\overline{\text{LBOL}}$ is deasserted when LTHIN rises above the $V_{\text{LTH+}}$ specification for at least 150ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

### **Detailed Description**

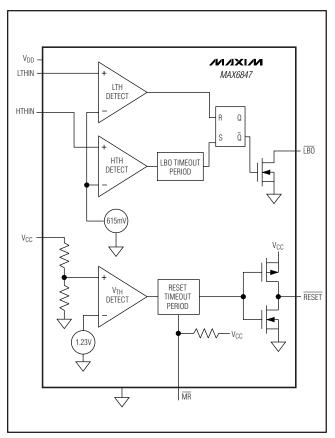

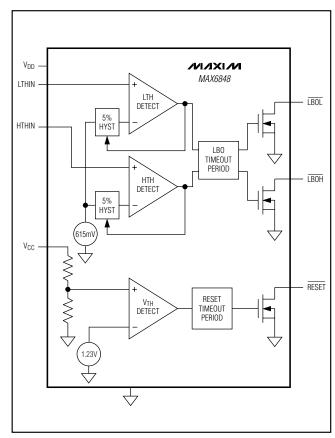

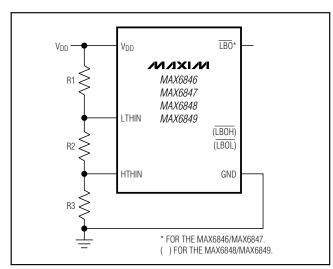

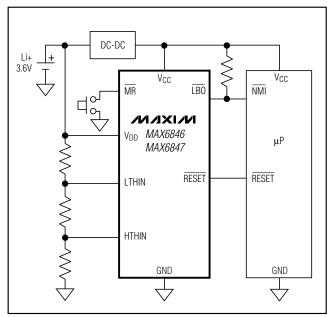

The MAX6846–MAX6849 family is available with several monitoring options. The MAX6846/MAX6847 have single low-battery outputs and the MAX6848/MAX6849 have dual low-battery outputs (see Figures 1a and 1b).

The MAX6846–MAX6849 combine a 615mV reference with two comparators, logic, and timing circuitry to provide the user with information about the charge state of the power-supply batteries. The MAX6848/MAX6849 monitor separate high-voltage and low-voltage thresholds to determine battery status. The output(s) can be used to signal when the battery is charged, when the battery is low, and when the battery is empty. User-

adjustable thresholds are ideal for monitoring single-cell Li+ or multicell alkaline/NiCd/NiMH power supplies.

When the power-supply voltage drops below the specified low threshold, the low-battery output asserts. When the voltage rises above the specified high threshold following a 150ms (min) timeout period, the low-battery output is deasserted. This ensures the supply voltage has stabilized before power-converter or microprocessor activity is enabled.

These devices also have an independent  $\mu P$  supervisor that monitors V<sub>CC</sub> and provides an active-low reset output. A manual reset function is available to allow the user to reset the  $\mu P$  with a pushbutton.

Figure 1a. MAX6847 Functional Diagram

#### **Low-Battery Output**

The low-battery outputs are available in active-low (LBO, LBOL, LBOH), open-drain configurations. The low-battery outputs can be pulled to a voltage independent of VCC or VDD, up to 5.5V. This allows the device to monitor and operate from direct battery voltage while interfacing to higher voltage microprocessors.

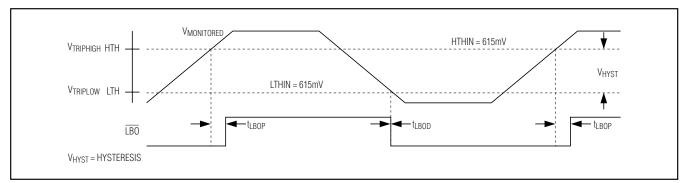

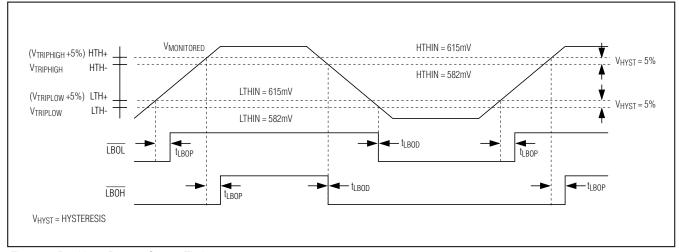

The MAX6846/MAX6847 single-output voltage monitors provide a single low-battery output, LBO. LBO asserts when LTHIN drops below V<sub>LTH</sub> and remains asserted for at least 150ms after HTHIN rises above V<sub>HTH</sub> (see Figure 2). The MAX6848/MAX6849 dual-output voltage monitors provide two low-battery outputs: LBOH and LBOL. LBOH asserts when HTHIN drops below V<sub>HTH-</sub> and remains asserted for at least 150ms after HTHIN

Figure 1b. MAX6848 Functional Diagram

rises above V<sub>HTH+</sub>.  $\overline{\text{LBOL}}$  asserts when LTHIN drops below V<sub>LTH-</sub> and remains asserted for at least 150ms after LTHIN rises above V<sub>LTH+</sub> (see Figure 3). For fast-rising V<sub>DD</sub> input, the  $\overline{\text{LBOL}}$  timeout period must complete before the  $\overline{\text{LBOH}}$  timeout period begins.

#### Reset Output

The MAX6846–MAX6849 provide an active-low reset output (RESET). RESET is asserted when the voltage at V<sub>CC</sub> falls below the reset threshold level. Reset remains asserted for the reset timeout period after V<sub>CC</sub> exceeds the threshold. If V<sub>CC</sub> goes below the reset threshold before the reset timeout period is completed, the internal timer restarts (see Figure 4). The MAX6846/MAX6848 have open-drain reset outputs, while the MAX6847/MAX6849 have push-pull reset outputs.

Figure 2. Single Low-Battery Output Timing

Figure 3. Dual Low-Battery Output Timing

Figure 4. RESET Timing Diagram

#### **Manual Reset**

Many microprocessor-based products require manual reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset while the monitored supplies remain above their reset thresholds. These devices have a dedicated active-low MR pin. When MR is pulled low, RESET asserts a one-shot low pulse for the MR reset timeout period. The MR input has an internal  $1.5k\Omega$  pullup resistor to VCC and can be left unconnected if not used. MR can be driven with CMOSlogic levels, open-drain/open-collector outputs, or a momentary pushbutton switch to GND (the MR function is internally debounced for the t<sub>DEB</sub> timeout period) to create a manual reset function. If MR is driven from long cables, or if the device is used in a noisy environment, connect a 0.1µF capacitor from MR to GND to provide additional noise immunity (see Figure 4).

#### **Hysteresis**

Hysteresis increases the comparator's noise margin by increasing the upper threshold or decreasing the lower threshold. The hysteresis prevents the output from oscillating (chattering) when monitor input is near the low-battery threshold. This is especially important for applications where the load on the battery creates significant fluctuations in battery voltages (see Figures 2 and 3).

For the MAX6846/MAX6847, hysteresis is set using three external resistors (see Figure 5). The MAX6848/MAX6849 have dual, low-battery input levels. Each input level has a 5% (typ) hysteresis.

## **Applications Information**

# Resistor-Value Selection (Programming the Adjustable Thresholds) MAX6846/MAX6847

$$V_{LTH} = V_{HTH} = 615 \text{mV}$$

$$V_{TRIPLOW} = V_{LTH} \times \left(\frac{R1 + R2 + R3}{R2 + R3}\right)$$

$$V_{TRIPHIGH} = V_{HTH} \times \left(\frac{R1 + R2 + R3}{R3}\right)$$

$$R_{TOTAL} = R1 + R2 + R3$$

Use the following steps to determine values for R1, R2, and R3 of Figure 5.

1) Choose a value for R<sub>TOTAL</sub>, the sum of R1, R2, and R3. Because the MAX6846/MAX6847 have very high input impedance, R<sub>TOTAL</sub> can be up to  $500k\Omega$ .

Figure 5. Adjustable Threshold Selection

2) Calculate R3 based on R<sub>TOTAL</sub> and the desired upper trip point:

$$R3 = \frac{615\text{mV} \times R_{\text{TOTAL}}}{V_{\text{TRIPHIGH}}}$$

Calculate R2 based on R<sub>TOTAL</sub>, R3, and the desired lower trip point:

$$R2 = \left(\frac{615\text{mV} \times R_{TOTAL}}{V_{TRIPLOW}}\right) - R3$$

4) Calculate R1 based on RTOTAL, R3, and R2:

$$R1 = R_{TOTAI} - R2 - R3$$

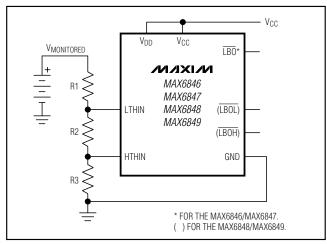

MAX6848/MAX6849

$$V_{TRIPLOW} = V_{LTH-} \times \left(\frac{R1 + R2 + R3}{R2 + R3}\right)$$

**LBOH** low-trip level:

$$V_{TRIPHIGH} = V_{HTH-} \times \left(\frac{R1 + R2 + R3}{R3}\right)$$

$$R_{TOTAL} = R1 + R2 + R3$$

Use the following steps to determine values for R1, R2, and R3 of Figure 5.

- 1) Choose a value for R<sub>TOTAL</sub>, the sum of R1, R2, and R3. Because the MAX6848/MAX6849 have very high input impedance, R<sub>TOTAL</sub> can be up to  $500k\Omega$ .

- 2) Calculate R3 based on R<sub>TOTAL</sub> and the desired upper trip point:

$$R3 = \frac{582mV \times R_{TOTAL}}{V_{TRIPHIGH}}$$

3) Calculate R2 based on R<sub>TOTAL</sub>, R3, and the desired lower trip point:

$$R2 = \left(\frac{582mV \times R_{TOTAL}}{V_{TRIPLOW}}\right) - R3$$

4) Calculate R1 based on RTOTAL, R3, and R2:

$$R1 = R_{TOTAL} - R2 - R3$$

5) LBOL high-trip level:

VTRIPLOW × 1.05

6) LBOH high-trip level:

VTRIPHIGH × 1.05

#### **Monitoring Multicell Battery Applications**

For monitoring multicell Li+ (or a higher number of alkaline/NiCd/NiMH cells), connect  $V_{DD}$  to a supply voltage between 1.6V to 5.5V. Figure 6 shows  $V_{DD}$  connected directly to  $V_{CC}$ . To calculate the values of R1, R2, and R3, see the *Resistor-Value Selection* section.

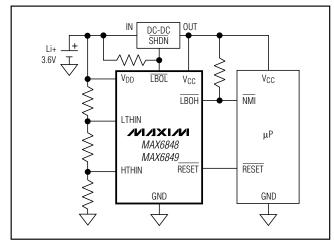

#### **DC-DC Converter Application**

The MAX6848/MAX6849 dual battery monitors can be used in conjunction with a DC-DC converter to power microprocessor systems using a single Li+ cell or two

Figure 6. Monitoring Multicell Li+ Applications

to three alkaline/NiCd/NiMH cells. The LBOH output indicates that the battery voltage is weak, and is used to warn the microprocessor of potential problems. Armed with this information, the microprocessor can reduce system power consumption. The LBOL output indicates the battery is empty and system power should be disabled. By connecting LBOL to the SHDN pin of the DC-DC converter, power to the microprocessor is removed. Microprocessor power does not return until the battery has recharged to a voltage greater than V<sub>LTH+</sub> (see Figure 7).

# Table 1. Factory-Trimmed VCC Reset Threshold Levels

| PART NO.<br>SUFFIX<br>(_) | V <sub>CC</sub> NOMINAL<br>RESET<br>THRESHOLD (V) |

|---------------------------|---------------------------------------------------|

| Т                         | 3.075                                             |

| S                         | 2.925                                             |

| R                         | 2.625                                             |

| Z                         | 2.313                                             |

| Y                         | 2.188                                             |

| W                         | 1.665                                             |

| V                         | 1.575                                             |

Table 2. VCC Reset Timeout Period Suffix Guide

| TIMEOUT       | ACTIVE TIMEOUT PERIOD (ms) |      |  |

|---------------|----------------------------|------|--|

| PERIOD SUFFIX | MIN                        | MAX  |  |

| D3            | 150                        | 300  |  |

| D7            | 1200                       | 2400 |  |

Figure 7. DC-DC Converter Application

#### **Selector Guide**

| PART    | OPEN-DRAIN<br>RESET | PUSH-PULL RESET | SINGLE LOW-<br>BATTERY OUTPUT | DUAL LOW-BATTERY<br>OUTPUT |

|---------|---------------------|-----------------|-------------------------------|----------------------------|

| MAX6846 | X                   | _               | X                             | _                          |

| MAX6847 | _                   | X               | X                             | _                          |

| MAX6848 | X                   | _               | _                             | X                          |

| MAX6849 | _                   | Χ               | _                             | Х                          |

### Standard Versions Table

| PART         | TOP MARK |

|--------------|----------|

| MAX6846KARD3 | AEJI     |

| MAX6846KASD3 | AEJD     |

| MAX6846KAWD3 | AEJK     |

| MAX6846KAZD3 | AEJJ     |

| MAX6847KARD3 | AEJE     |

| MAX6847KASD3 | AEJL     |

| MAX6847KAWD3 | AEJN     |

| MAX6847KAZD3 | AEJM     |

| MAX6848KARD3 | AEJP     |

| MAX6848KASD3 | AEJO     |

| MAX6848KAWD3 | AEJR     |

| MAX6848KAZD3 | AEJQ     |

| MAX6849KARD3 | AEJT     |

| MAX6849KASD3 | AEJS     |

| MAX6849KAWD3 | AEJV     |

| MAX6849KAZD3 | AEJU     |

## **Typical Application Circuit**

### **Chip Information**

TRANSISTOR COUNT: 1478

PROCESS: BiCMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.