19-2620: Rev 1: 3/03

##

## 100MHz to 2500MHz, 45dB RF Detector in a UCSP

### **General Description**

The MAX4003 low-cost, low-power logarithmic amplifier is designed to detect the power levels of RF power amplifiers (PAs) operating from 100MHz to 2500MHz. A typical dynamic range of 45dB makes this logarithmic amplifier useful in a variety of wireless applications including cellular handset PA control, TSSI for wireless terminal devices, and other transmitter power measurements. This logarithmic amplifier provides much wider measurement range and superior accuracy than typical diode-based detectors. Excellent temperature stability is achieved over the full operating range of -40°C to +85°C.

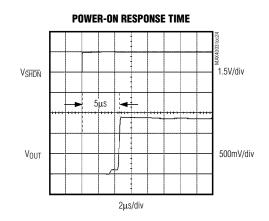

The MAX4003 logarithmic amplifier is a voltage-measuring device with a typical signal range of -58dBV to -13dBV. The input signal is internally AC-coupled by an on-chip 5pF capacitor in series with a  $2k\Omega$  resistance. This highpass coupling, with a corner at 16MHz, sets the lowest operating frequency and allows the input signal source to be DC grounded. The MAX4003 also features a power-on delay, which holds the detector output (OUT) low for approximately 5µs to ensure glitchless controller output.

The MAX4003 is available in an 8-bump chip-scale package (UCSP™), an 8-pin µMAX package, and an 8-pin thin QFN package. The device consumes 5.9mA with a 3.0V supply and only 13µA when the device is in shutdown.

### **Applications**

Cellular Handsets (TDMA, CDMA, GPRS, GSM) TSSI for Wireless Terminal Devices Transmitter Power Measurement and Control **RSSI** for Fiber Modules

UCSP is a trademark of Maxim Integrated Products, Inc.

#### **Features**

- **♦ Complete RF Detector**

- ♦ Frequency Range from 100MHz to 2500MHz

- ♦ Input Range of -58dBV to -13dBV (-45dBm to 0dBm into  $50\Omega$ )

- ♦ Fast Response: 70ns in 10dB Steps

- ◆ Low-Current Consumption: 5.9mA at V<sub>CC</sub> = 3.0V

- ♦ 13µA (typ) Shutdown Current

- ♦ Available in 8-Bump UCSP or 8-Pin µMAX and Thin QFN Packages

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN/BUMP-<br>PACKAGE | TOP<br>MARK |  |

|--------------|----------------|----------------------|-------------|--|

| MAX4003EBL-T | -40°C to +85°C | 8 UCSP-8             | ABV         |  |

| MAX4003EUA   | -40°C to +85°C | 8 µMAX               | _           |  |

| MAX4003ETA-T | -40°C to +85°C | 8 Thin QFN-EP        | ADG         |  |

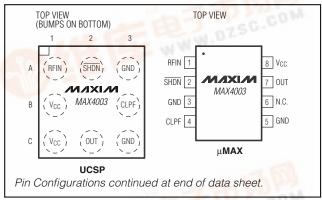

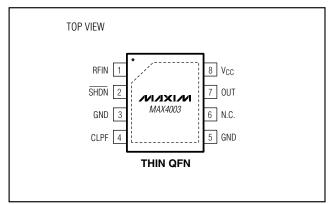

### Pin Configurations

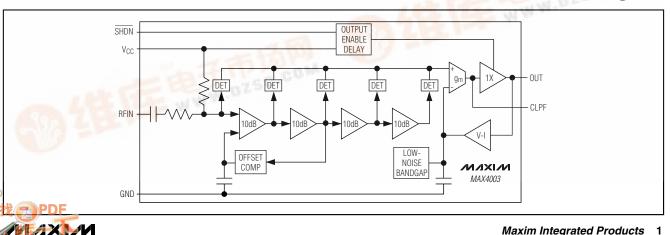

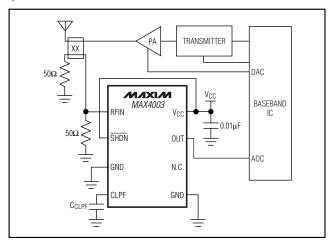

### Functional Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(VCC = 3.0V, VSHDN = VCC, CCLPF = 0.1µF, TA = -40°C to +85°C. Typical values are at TA = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                    | SYMBOL                                | CONDITIONS                          |              | MIN   | TYP | MAX    | UNITS |

|------------------------------|---------------------------------------|-------------------------------------|--------------|-------|-----|--------|-------|

| Supply Voltage               | Vcc                                   |                                     |              | 2.7   |     | 5.0    | V     |

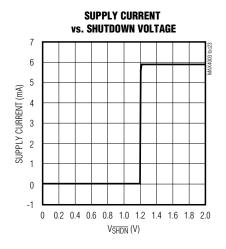

| Complete Comment             | la a                                  | V                                   | VSHDN = 1.8V |       | 5.9 | 10     | mA    |

| Supply Current               | lcc                                   | $V_{CC} = 5.0V$                     | VSHDN = 0.8V |       | 13  | 30     | μΑ    |

| Charteleure Insuit Carrent   | I                                     | V <sub>SHDN</sub> = 3.0V            |              |       | 5   | 20     | μΑ    |

| Shutdown Input Current       | ISHDN                                 | VSHDN = 0V                          |              | -0.01 | ±5  |        |       |

| Logic High Threshold Voltage | VIH                                   |                                     |              | 1.8   |     |        | V     |

| Logic Low Threshold Voltage  | VIL                                   |                                     |              |       |     | 0.8    | V     |

| DETECTOR OUTPUT              |                                       |                                     |              |       |     |        |       |

| Valta da Danasa              | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | RFIN = 0dBm                         |              | 1.45  |     | V      |       |

| Voltage Range                | Vout                                  | RFIN = -45dBm                       | 0.36         |       |     |        |       |

| Output Voltage in Shutdown   | Vout                                  | VSHDN = 0V                          |              | 1     |     | mV     |       |

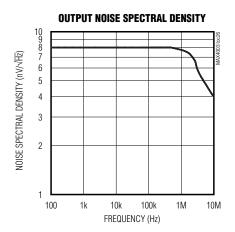

| Output-Referred Noise        |                                       | $f_0 = 150kHz$                      |              | 8     |     | nV/√Hz |       |

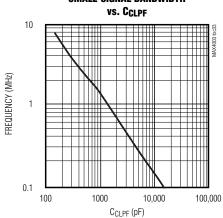

| Small-Signal Bandwidth       | BW                                    | C <sub>CLPF</sub> = 150pF           |              | 8     |     | MHz    |       |

| Slew Rate                    |                                       | $V_{OUT} = 0.36V \text{ to } 1.45V$ |              | 5     |     | V/µs   |       |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC}=3.0V, V_{\overline{SHDN}}=V_{CC}, C_{CLPF}=0.1\mu F, f_{RF}=100MHz$  to 2500MHz,  $T_{A}=-40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_{A}=+25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                           | SYMBOL          | CONDITIONS                                | MIN  | TYP  | MAX   | UNITS |  |

|-------------------------------------|-----------------|-------------------------------------------|------|------|-------|-------|--|

| RF Input Frequency Range            | f <sub>RF</sub> |                                           | 100  |      | 2500  | MHz   |  |

| RF Input Voltage Range              | V <sub>RF</sub> | (Note 2)                                  | -58  |      | -13   | dBV   |  |

| Equivalent RF Input Power Range PRF |                 | With 50Ω termination (Note 2)             | -45  |      | 0     | dBm   |  |

|                                     |                 | $f_{RF} = 100MHz, T_A = +25^{\circ}C$     | 22.8 | 25.5 | 28.2  |       |  |

| La marithmia Clara                  |                 | f <sub>RF</sub> = 100MHz                  | 22.5 |      | 28.5  | mV/dB |  |

| Logarithmic Slope                   |                 | $f_{RF} = 900MHz$                         |      | 25.0 |       |       |  |

|                                     |                 | f <sub>RF</sub> = 1900MHz                 |      | 29.0 |       |       |  |

|                                     |                 | $f_{RF} = 100MHz, T_A = +25^{\circ}C$ -62 |      | -57  | -51.7 |       |  |

| Logarithmic Intercept               | Б               | f <sub>RF</sub> = 100MHz                  | -64  |      | -50   | -ID   |  |

|                                     | Рх              | f <sub>RF</sub> = 900MHz                  |      | -57  |       | dBm   |  |

|                                     |                 | $f_{RF} = 1900MHz$ -56                    |      |      |       |       |  |

| DEIN Input Impedance                | R <sub>IN</sub> |                                           |      | 2    |       | kΩ    |  |

| RFIN Input Impedance                | CIN             |                                           |      | 0.5  |       | рF    |  |

Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C and are guaranteed by design for T<sub>A</sub> = -40°C to +85°C as specified. All production AC tests are done at 100MHz.

Note 2: Typical minimum and maximum range of the detector.

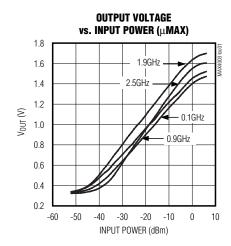

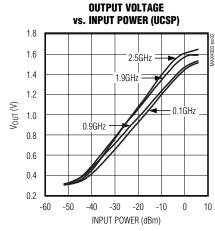

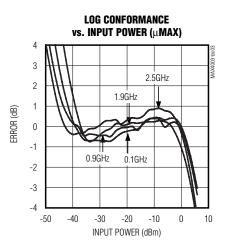

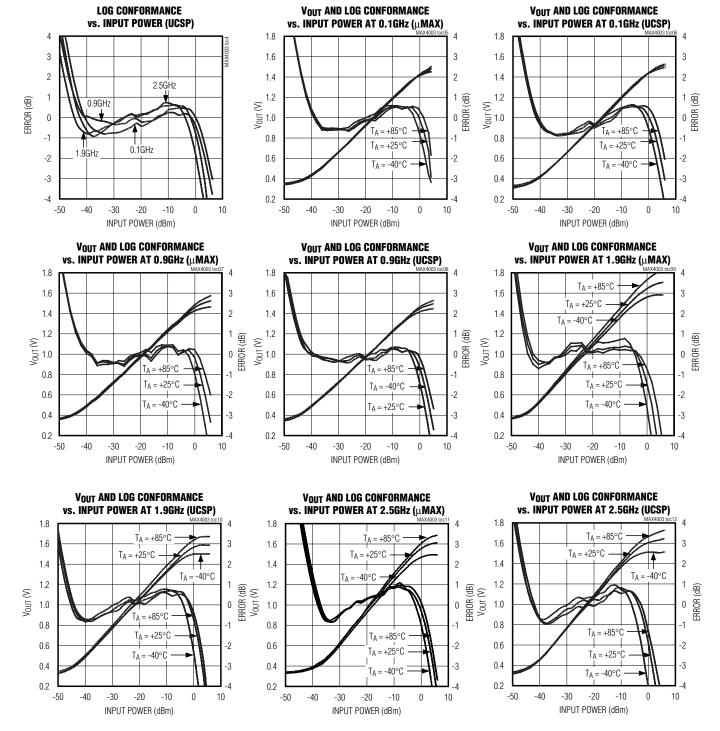

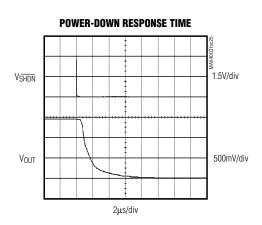

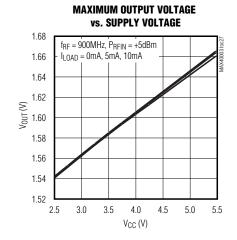

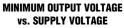

## Typical Operating Characteristics

$(V_{CC} = V_{\overline{SHDN}} = 3.0V, C_{CLPF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

$(V_{CC} = V_{\overline{SHDN}} = 3.0V, C_{CLPF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

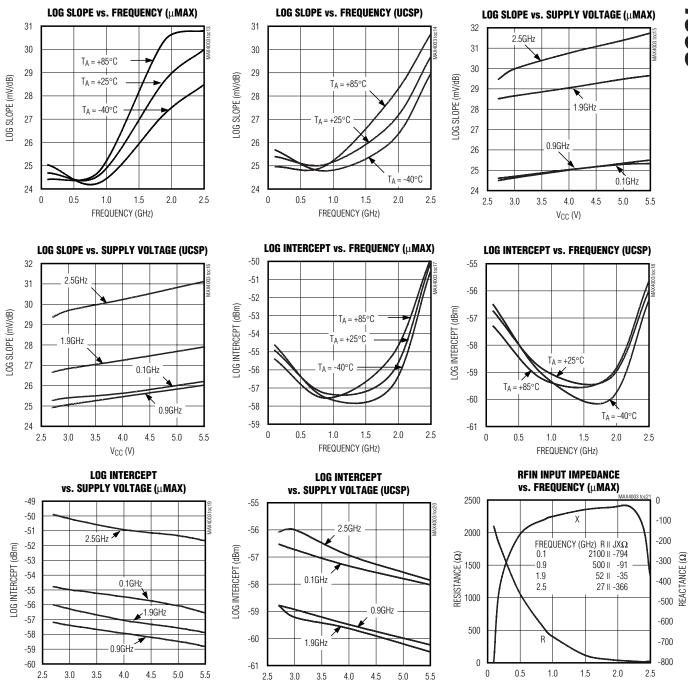

## Typical Operating Characteristics (continued)

$(V_{CC} = V_{\overline{SHDN}} = 3.0V, C_{CLPF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

V<sub>CC</sub> (V)

V<sub>CC</sub> (V)

FREQUENCY (GHz)

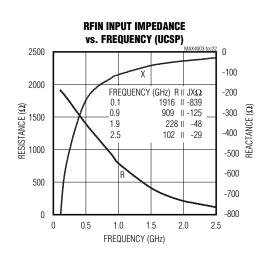

## **Typical Operating Characteristics (continued)**

$(V_{CC} = V_{\overline{SHDN}} = 3.0V, C_{CLPF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V_{CC} = V_{\overline{SHDN}} = 3.0V, C_{CLPF} = 0.1 \mu F, T_A = +25 ^{\circ}C, unless otherwise noted.)$

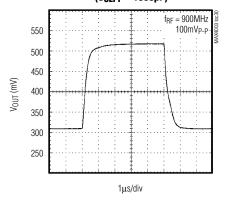

### SMALL-SIGNAL STEP RESPONSE

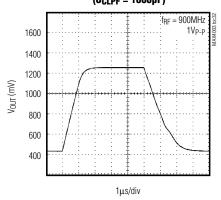

#### SMALL-SIGNAL STEP RESPONSE (C<sub>CLPF</sub> = 1000pF)

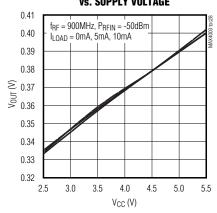

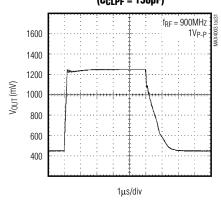

LARGE-SIGNAL STEP RESPONSE (CCLPF = 150pF)

#### LARGE-SIGNAL STEP RESPONSE (C<sub>CLPF</sub> = 1000pF)

#### SMALL-SIGNAL BANDWIDTH

### **Pin Description**

| PIN               |            |      |                                                                                                                                                     |  |  |  |  |

|-------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| μΜΑΧ/<br>Thin QFN | · I UCSP I |      | DESCRIPTION                                                                                                                                         |  |  |  |  |

| 1                 | A1         | RFIN | RF Input. Requires off-chip $50\Omega$ impedance match.                                                                                             |  |  |  |  |

| 2                 | A2         | SHDN | Shutdown Input. A logic LOW on SHDN shuts down the entire IC.                                                                                       |  |  |  |  |

| 3, 5              | A3, C3     | GND  | Ground. Connect to PC board ground plane.                                                                                                           |  |  |  |  |

| 4                 | В3         | CLPF | Lowpass Filter Connection. Connect external capacitor between CLPF and GND to set the control-loop bandwidth.                                       |  |  |  |  |

| 6                 | _          | N.C. | No Connection. Leave this pin unconnected or connect to GND.                                                                                        |  |  |  |  |

| 7                 | C2         | OUT  | Detector Output. Connect this buffer output to baseband ADC.                                                                                        |  |  |  |  |

| 8                 | B1, C1     | Vcc  | Supply Voltage. Bypass with capacitor as close to the pin as possible. The bypass capacitor must not share its ground vias with any other branches. |  |  |  |  |

#### **Detailed Description**

The MAX4003 logarithmic amplifier comprises four main amplifier/limiter stages, each with a small-signal gain of 10dB. The output stage of each amplifier/limiter stage is applied to a full-wave rectifier (detector). A detector stage also precedes the first stage. In total, five detectors, each separated by 10dB, comprise the logarithmic amplifier strip (see *Functional Diagram*).

A portion of the PA output power is coupled into RFIN of the logarithmic amplifier detector through a directional coupler, and is applied to the logarithmic amplifier strip. Each detector stage generates a rectified current, and these currents are summed to form a logarithmic function. The detected output is applied to a high-gain transconductance (g<sub>m</sub>) stage, which is buffered and then applied to OUT. OUT is applied to an ADC typically found in the baseband IC which, in turn, controls the

Figure 1. MAX4003 Typical Application Circuit

PA biasing with its DAC output (Figure 1).

In a control loop, the detector output voltage range is approximately 0.36V for the minimum input signal, -45dBm, to 1.45V at the maximum input range, 0dBm. The logarithmic intercept of the detector output with respect to the RF input can be obtained by drawing a best fit line of the Output Voltage vs. RF Input Power graph. The logarithmic slope is defined as the change in the detector output vs. the change in RF input. The MAX4003 slope at low frequencies is approximately 25.5mV/dB. Variation in temperature and supply voltage does not alter the slope significantly, as shown in the *Typical Operating Characteristics*.

### Applications Information

#### **Filter Capacitor and Transient Response**

In general, the choice of filter only partially determines the time-domain response of a PA detector loop. However, some simple conventions may be applied to discuss transient response. A large filter capacitor, CCLPF, dominates time-domain response, but the loop bandwidth remains a factor of the PA gain-control range (see *Typical Operating Characteristics*). The bandwidth is maximized at power outputs near the center of the PA's range and minimized at the low and high power levels, when the slope of the gain control curve is lowest.

A smaller valued CCLPF results in an increased-loop bandwidth inversely proportional to the capacitor value. Inherent phase lag in the PA's control path, usually caused by parasitics at the OUT pin, ultimately results in the addition of complex poles in the AC loop equation. To avoid this secondary effect, experimentally determine the lowest usable CCLPF for the power ampli-

fier of interest. This requires full consideration of the intricacies of the PA detector control function. The worst-case condition, where the PA output is smallest (gain function is steepest), should be used because the PA control function is nonlinear. An additional zero can be added to improve loop dynamics by placing a resistor in series with CCLPF.

#### **Waveform Considerations**

Although the input level of the MAX4003 is specified in dBm, the logarithmic amplifier actually responds to rectified voltage signals rather than a true RMS power. It is important to realize that input signals with identical root-mean-square power but with unique waveforms result in different logarithmic outputs.

Differing signal waveforms result in either an upward or downward shift in the logarithmic intercept. However, the logarithmic slope remains the same.

#### **Layout Considerations**

As with any RF circuit, the MAX4003 circuit layout affects performance. To ensure maximum power transfer between  $50\Omega$  sources and the MAX4003 input, suitable matching networks should be implemented. The VCC input should be bypassed as close as possible to the device with multiple vias connecting the capacitor to the ground plane.

#### **UCSP Reliability**

The UCSP represents a unique package that greatly reduces board space compared to other packages. UCSP reliability is integrally linked to the user's assembly methods, circuit board material, and usage environment. The user should closely review these areas when considering use of a UCSP. This form factor may not perform equally to a packaged product through traditional mechanical reliability tests. Performance through operating life test and moisture resistance remains uncompromised as it is primarily determined by the wafer fabrication process. Mechanical stress performance is a greater consideration for a UCSP. UCSP solder joint contact integrity must be considered since the package is attached through direct solder contact to the user's PC board. Testing done to characterize the UCSP reliability performance shows that it can perform reliably through environmental stresses. Results of environmental stress tests and additional usage data and recommendations are detailed in the UCSP application note found on Maxim's website. www.maxim-ic.com.

Chip Information

**TRANSISTOR COUNT: 358**

### Pin Configurations (continued)

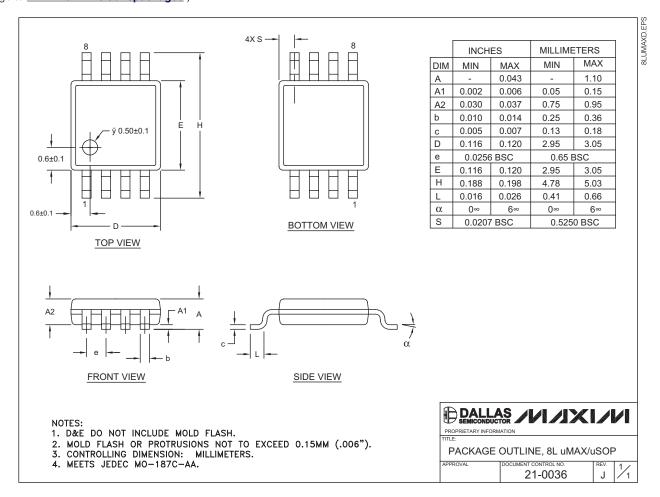

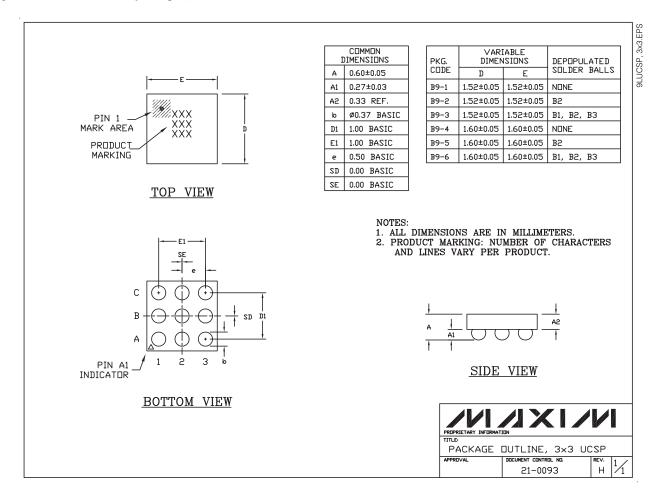

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

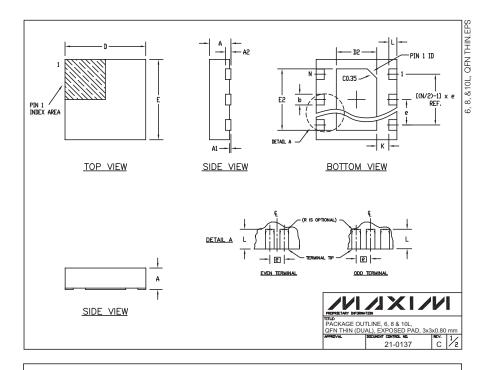

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |           |      |  |  |  |

|-------------------|-----------|------|--|--|--|

| SYMBOL            | MIN.      | MAX. |  |  |  |

| Α                 | 0.70      | 0.80 |  |  |  |

| D                 | 2.90      | 3.10 |  |  |  |

| E                 | 2.90      | 3.10 |  |  |  |

| A1                | 0.00      | 0.05 |  |  |  |

| L                 | 0.20      | 0.40 |  |  |  |

| k                 | 0.25 MIN  |      |  |  |  |

| A2                | 0.20 REF. |      |  |  |  |

| PACKAGE VARIATIONS |    |           |           |          |                |           |               |

|--------------------|----|-----------|-----------|----------|----------------|-----------|---------------|

| PKG. CODE          | N  | D2        | E2        | е        | JEDEC SPEC     | b         | [(N/2)-1] x e |

| T633-1             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      |

| T833-1             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| T1033-1            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

- NOTES:

1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY SHALL NOT EXCEED 0.08 mm.

3. WARPAGE SHALL NOT EXCEED 0.10 mm.

4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTIC(S).

5. DRAWING CONFORMS TO JEDEC MO220.

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.