# 捷多邦,专业PCB打样工厂,24小时加急出货

# 3-PHASE BRUSHLESS DC MOTOR CONTROLLER/DRIVER WITH LINEAR CURRENT CONTROL AND POWER DMOS OUTPUTS

8925

#### ABSOLUTE MAXIMUM RATINGS AT $T_A = +25^{\circ}C$

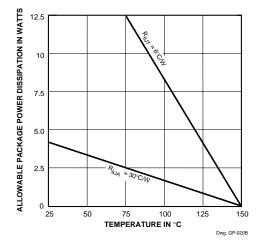

Output current rating may be restricted to a value determined by system concerns and factors. These include: system duty cycle and timing, ambient temperature, and use of any heatsinking and/or forced cooling. For reliable operation, the specified maximum junction temperature should not be exceeded.

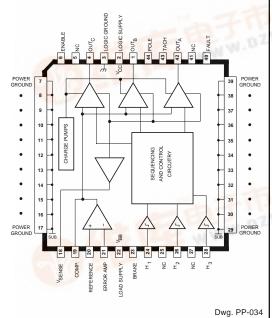

The A8925CEB is a DMOS three-phase brushless dc motor controller/driver designed for use in Winchester disk drives and other data storage applications. The power output stages are capable of  $\pm 4$  A output currents and have DMOS power outputs with less than 0.25  $\Omega$ r<sub>DS(on)</sub> for low power dissipation. Intrinsic ground clamp and flyback diodes protect the output drivers when switching inductive loads. Thermal shutdown circuitry is provided to protect the device from excessive junction temperature.

A transconductance amplifier is used to linearly regulate the load current and control motor speed. Internal current-sensing circuitry eliminates the need for external sense resistors. Analog and digital control circuitry provide complete sequencing of the output drivers as well as providing brake, disable, and tachometer functions. A FAULT output flag indicates the presence of an under-voltage condition on the 12 V supply, excessive junction temperature, or an invalid Hall input combination. The A8925CEB's commutation logic is compatible with motors that have digital Hall-effect sensors with 120° of electrical separation. Internal charge pump circuitry is provided to drive the N-channel DMOS source drivers to their required gate voltages.

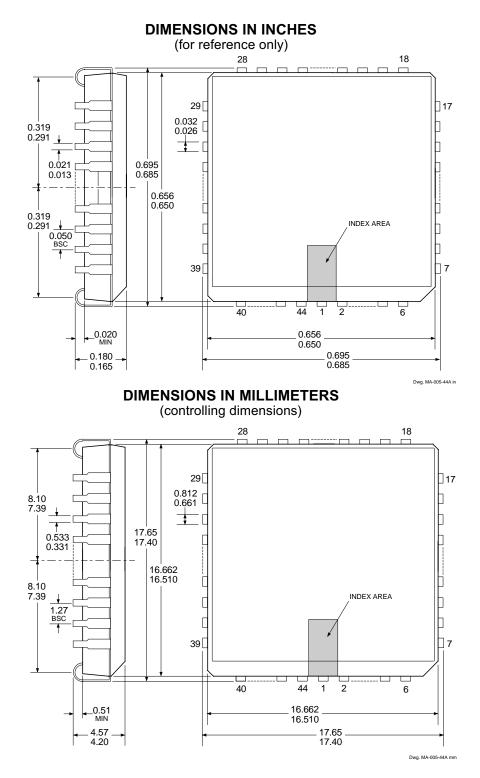

The A8925CEB is provided in a 44-lead PLCC power package for surface-mount applications. The copper batwing provides for maximum allowable package power dissipation in the smallest possible construction.

#### FEATURES

- DMOS Outputs

- Low r<sub>DS(on)</sub> 0.25 Ω Maximum

- Linear Current Control

- Internal Commutation Circuitry

- Internal Current Sensing

- Thermal Shutdown Circuitry

- Under Voltage Detection Circuitry

- Fault Output Flag

- Power Surface-Mount Package

Always order by complete part number: A8925CEB .

# ELECTRICAL CHARACTERISTICS AT $T_A = +25^{\circ}C$ , $V_{CC} = V_{BB} = 12 V$

|                             |                      |                                    | Limits |      |      |       |  |

|-----------------------------|----------------------|------------------------------------|--------|------|------|-------|--|

| Characteristic              | Symbol               | Test Conditions                    | Min.   | Тур. | Max. | Units |  |

| Logic Supply Voltage        | V <sub>CC</sub>      | Operating                          | 10     | 12   | 14   | V     |  |

| Load Supply Voltage         | V <sub>BB</sub>      | Operating                          | 10     | 12   | 14   | V     |  |

| Supply Current              | I <sub>CC</sub>      | Operating                          | —      | 30   | 50   | mA    |  |

|                             |                      | V <sub>ENABLE</sub> = 0 V          | _      | 2.0  | 4.0  | mA    |  |

| Thermal Shutdown            | TJ                   |                                    | —      | 165  | _    | °C    |  |

| Output Drivers              | ·                    | ·                                  | -      |      |      | -     |  |

| Output ON Resistance        | r <sub>DS(on)</sub>  | $I_{OUT}$ = ±4.0 A, Pulse Test     | —      | 0.20 | 0.25 | Ω     |  |

| Output Sustaining Voltage   | V <sub>DS(sus)</sub> | I <sub>OUT</sub> = 4.0 A, L = 2 mH | 14     | _    | _    | V     |  |

| Clamp Diode Forward Voltage | V <sub>F</sub>       | I <sub>F</sub> = ±4.0 A            | —      | 1.5  | 2.0  | V     |  |

| Output Leakage Current      | I <sub>DSX</sub>     | V <sub>OUT</sub> = 14 V            | —      | 10   | 300  | μA    |  |

|                             |                      | V <sub>OUT</sub> = 0 V             | —      | -10  | -300 | μΑ    |  |

| Control Logic               |                      | -                                  | •      |      |      |       |  |

| Logic Input Voltage         | V <sub>IN(0)</sub>   | ENABLE, POLE                       | _      |      | 0.8  | V     |  |

|                             | V <sub>IN(1)</sub>   |                                    | 2.4    |      |      | V     |  |

| Logic Input Voltage         | V <sub>IN(0)</sub>   | BRAKE                              |        | _    | 0.8  | V     |  |

|                             | V <sub>IN(1)</sub>   |                                    | 3.0    |      |      | V     |  |

| Logic Input Current         | I <sub>IN(0)</sub>   | V <sub>IN</sub> = 0.8 V            |        | _    | -1.0 | μΑ    |  |

|                             | I <sub>IN(1)</sub>   | V <sub>IN</sub> = 2.4 V            | _      |      | 1.0  | μA    |  |

NOTE: Negative current is defined as coming out of (sourcing) the specified device terminal.

Continued next page ...

#### **ELECTRICAL CHARACTERISTICS CONTINUED**

|                                 |                     |                                           | Limits   |        |        |       |  |

|---------------------------------|---------------------|-------------------------------------------|----------|--------|--------|-------|--|

| Characteristic                  | Symbol              | Test Conditions                           | Min.     | Тур.   | Max.   | Units |  |

| Logic Output Voltage            | V <sub>OUT(0)</sub> | I <sub>OUT</sub> = 3 mA                   | -        | —      | 0.8    | V     |  |

| (FAULT, TACH)                   | V <sub>OUT(1)</sub> | I <sub>OUT</sub> = -50 μA                 | 2.0      |        | —      | V     |  |

| Error Amplifier                 |                     | ·                                         |          |        |        |       |  |

| Input Bias Current              | I <sub>IB</sub>     | V <sub>CM</sub> = 0.01 V                  | _        | 5.0    | 10     | μA    |  |

| Input Offset Voltage            | V <sub>OS</sub>     | V <sub>CM</sub> = 1.0 V                   | _        | 3.0    | 5.0    | mV    |  |

| Input Common-Mode Voltage Range | V <sub>IC</sub>     |                                           | 0.01     | _      | 6.0    | V     |  |

| Error Voltage Gain              | A <sub>VD</sub>     | $V_{S OUT} / V_{S IN}$ , $V_{CM} = 1.0 V$ | _        | 80     | _      | dB    |  |

| Unity Gain Bandwidth            | BW                  |                                           | _        | 1.0    |        | MHz   |  |

| Common-Mode Rejection Ratio     | CMRR                |                                           | _        | 80     |        | dB    |  |

| Power Supply Rejection Ratio    | PSRR                |                                           | _        | 50     | _      | dB    |  |

| Miscellaneous                   |                     |                                           |          |        |        |       |  |

| Current Sense Gain              | A <sub>iCS</sub>    | I <sub>OUT</sub> = -1.0 A                 | 1/1k     | 1/1.2k | 1/1.4k |       |  |

| Current-Sense Matching          |                     | I <sub>OUT</sub> = -1.0 A                 | _        | ±3.0   | ±5.0   | %     |  |

| Under-Voltage Trip Point        | V <sub>CC</sub>     |                                           | 8.0      |        | 9.5    | V     |  |

| Hall Input Current              | I <sub>IN(0)</sub>  | V <sub>IN</sub> = 0 V                     | —        | -500   | -1000  | μA    |  |

|                                 | I <sub>IN(1)</sub>  | V <sub>IN</sub> = 5.0 V                   | _        | -250   | -500   | μA    |  |

| Hall Input Threshold            | V <sub>IN</sub>     |                                           |          | 3.8    | _      | V     |  |

| Hall Input Pull-Up Resistance   | R <sub>PU</sub>     |                                           | <u> </u> | 25     | _      | kΩ    |  |

NOTE: Negative current is defined as coming out of (sourcing) the specified device terminal.

#### **COMMUTATION TRUTH TABLE**

| Hall Sensor Inputs |                |                |        |       |       | Outputs          |                  |                  |

|--------------------|----------------|----------------|--------|-------|-------|------------------|------------------|------------------|

| H <sub>1</sub>     | H <sub>2</sub> | H <sub>3</sub> | ENABLE | BRAKE | FAULT | OUT <sub>A</sub> | OUT <sub>B</sub> | OUT <sub>c</sub> |

| High               | Low            | High           | High   | High  | High  | High             | Low              | Z                |

| High               | Low            | Low            | High   | High  | High  | High             | Z                | Low              |

| High               | High           | Low            | High   | High  | High  | Z                | High             | Low              |

| Low                | High           | Low            | High   | High  | High  | Low              | High             | Z                |

| Low                | High           | High           | High   | High  | High  | Low              | Z                | High             |

| Low                | Low            | High           | High   | High  | High  | Z                | Low              | High             |

| High               | High           | High           | High   | High  | Low   | Z                | Z                | Z                |

| Low                | Low            | Low            | High   | High  | Low   | Z                | Z                | Z                |

| Х                  | Х              | Х              | Low    | High  | Х     | Z                | Z                | Z                |

| Х                  | Х              | Х              | Х      | Low   | Х     | Low              | Low              | Low              |

X = Irrelevant

Z = High Impedance

#### **TERMINAL FUNCTIONS**

| Term. | Terminal Name      | Function                                                                                                             |  |  |  |

|-------|--------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1     | OUT <sub>B</sub>   | Power DMOS output.                                                                                                   |  |  |  |

| 2     | LOGIC SUPPLY       | V <sub>CC</sub> ; low-current 12 V supply for the logic.                                                             |  |  |  |

| 3     | LOGIC GROUND       | Low-level logic ground.                                                                                              |  |  |  |

| 4     | OUT <sub>C</sub>   | Power DMOS output.                                                                                                   |  |  |  |

| 6     | ENABLE             | Active high chip enable.                                                                                             |  |  |  |

| 7–17  | POWER GROUND       | Power ground and thermal heat sink.                                                                                  |  |  |  |

| 18    | V <sub>SENSE</sub> | External precision resistor for sense-FET current.                                                                   |  |  |  |

| 19    | COMP.              | Compensation; error amplifier output.                                                                                |  |  |  |

| 20    | REFERENCE          | V <sub>REF</sub> ; voltage input that sets the power output current.                                                 |  |  |  |

| 21    | ERROR AMP.         | Input that controls the current in the load.                                                                         |  |  |  |

| 22    | LOAD SUPPLY        | V <sub>BB</sub> ; high-current 12 V supply for the voice-coil motor.                                                 |  |  |  |

| 23    | BRAKE              | A logic low turns OFF all source drivers and turns ON all sink drivers (shorts the windings to ground).              |  |  |  |

| 24    | H <sub>1</sub>     | High-level input from a Hall sensor.                                                                                 |  |  |  |

| 26    | H <sub>2</sub>     | High-level input from a Hall sensor.                                                                                 |  |  |  |

| 28    | H <sub>3</sub>     | High-level input from a Hall sensor.                                                                                 |  |  |  |

| 29–39 | POWER GROUND       | Power ground and thermal heat sink.                                                                                  |  |  |  |

| 40    | FAULT              | A logic low at this output indicates a thermal shutdown, under -voltage fault, or an invalid Hall input combination. |  |  |  |

| 42    | OUT <sub>A</sub>   | Power DMOS output.                                                                                                   |  |  |  |

| 43    | TACH               | Speed reference output; the H <sub>1</sub> Hall input divided by the number of motor poles.                          |  |  |  |

| 44    | POLE               | Designates four- or eight-pole motor; Low = 4 pole, High = 8 pole.                                                   |  |  |  |

#### FUNCTIONAL DESCRIPTION

Power Outputs (OUT<sub>A</sub>, OUT<sub>B</sub>, and OUT<sub>C</sub>). The power outputs of the A8925CEB are DMOS transistors with a maximum  $r_{DS(on)}$ of 0.25  $\Omega$ . Intrinsic ground clamp and flyback diodes clamp transient voltage spikes when switching inductive loads. Internal charge pump circuitry is used to drive the gates of the N-channel source drivers to their required gate voltages.

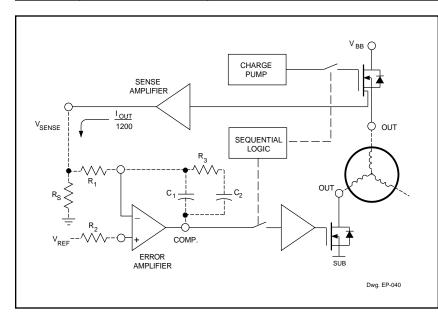

**Current Control.** Current in the load is monitored by an internal sense amplifier that produces an output current that is approximately one twelve hundredth that of the load current (see Figure). This current is output to the V<sub>SENSE</sub> terminal and develops a voltage

Continued next page...

across R<sub>S</sub> that equals R<sub>S</sub> • I<sub>LOAD</sub>/1200. This sense voltage (V<sub>SENSE</sub>) is compared to a reference voltage (V<sub>REF</sub>) and an error voltage is developed that is gated in by the sequential control logic to drive the gate of the appropriate output sink transistor. A transconductance control function is thus realized where I<sub>OUT</sub> = V<sub>REF</sub> • 1200/R<sub>S</sub>. External components C<sub>1</sub>, C<sub>2</sub>, R<sub>1</sub>, R<sub>2</sub>, and R<sub>3</sub> are compensation components used to obtain optimal response and settling of the current control loop. Information on how to select these components is available.

**FAULT.** The FAULT terminal when low indicates the presence of one of three fault conditions:

- An under-voltage condition on the logic supply. The trip point for this function is between 8 and 9.5 volts.

- An invalid Hall input combination ... all inputs High or all inputs Low.

- C) An excessive device junction temperature. The thermal shutdown circuitry disables the output drivers in addition to forcing the FAULT output signal low.

**TACH and POLE.** In order to develop a low-jitter tachometer signal (TACH) for use in controlling motor speed, the A8925CEB divides the frequency of the H<sub>1</sub> input by the number of poles in the motor. This eliminates the jitter caused by variations in Halleffect device placement , sensitivity, and magnet strengths by always changing state when looking at the same magnet/sensor pair. The resulting TACH signal changes state every mechanical revolution of the motor. The POLE input sets the TACH signal for fourpole motors when Low or eight-pole motors when High. HALL INPUTS (H<sub>1</sub>, H<sub>2</sub>, H<sub>3</sub>). The A8925CEB is configured for use with open-collector Hall-effect devices. Internal 25 k $\Omega$  pull up resistors to 10 volts are connected to these inputs.

**ENABLE.** The ENABLE terminal when Low puts the device in a low current consumption, power-down mode. When ENABLE is High the device is active.

**BRAKE.** When the BRAKE input goes Low the output source drivers are disabled and the gates of the sink drivers are pulled high and left floating. This achieves optimum passive braking performance since the sink power DMOS output drivers are ON until the motor has fully completed braking. The braking control circuitry operates off the load supply ( $V_{BB}$ ) to allow it to remain operational during power loss by using the back-EMF voltage of the motor as it's supply.

**LOAD SUPPLY (V**<sub>BB</sub>). This terminal is the power supply connection for the power output drivers and braking control circuitry. This terminal should be decoupled with a large-value capacitor to absorb load currents dumped back into the supply during the de-energization of motor windings. These currents can cause the supply voltage to exceed the maximum voltage rating of the device if not properly decoupled. The intrinsic ground clamp and flyback diodes will rectify the motor's back-EMF voltage during power loss. In applications were use of the motor's back-EMF voltage is desired a series diode should be used to isolate this terminal from the logic supply (V<sub>CC</sub>). This is to avoid dumping the charge back into the supply and therefor clamping the voltage available from rectification of the motor's back-EMF voltage.

**LOGIC SUPPLY (V<sub>CC</sub>).** This is the 12 volt supply terminal for the A8925CEB and powers all circuitry except the power outputs and brake control circuitry.

**LOGIC GROUND.** This must be connected to the power ground terminals in systems that do not use separate power and logic grounds.

**POWER GROUND.** Terminals 7 through 17 and 29 through 39 are webbed together and attach to the die mounting area to form a low thermal resistance path to allow heat to be conducted out of the device. The power dissipation of the package can be further enhanced by soldering these terminals to a large area of copper foil on the printed wiring board.

NOTES: 1. Webbed lead frame. Leads 7 through 17 and 29 through 39 are internally one piece. 2. Exact body and lead configuration at vendor's option within limits shown.

- Exact body and lead configuration at vendor's option

Lead spacing tolerance is non-cumulative.

- #allogue

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

115 Northoast Cutoff Box 15036