### 查询MAX1798AEGP供应商

19-1655: Rev 1: 2/01

EVALUATION KIT MANUAL AVAILABLE

# CDMA Cellular/PCS System Power Supplies

# **General Description**

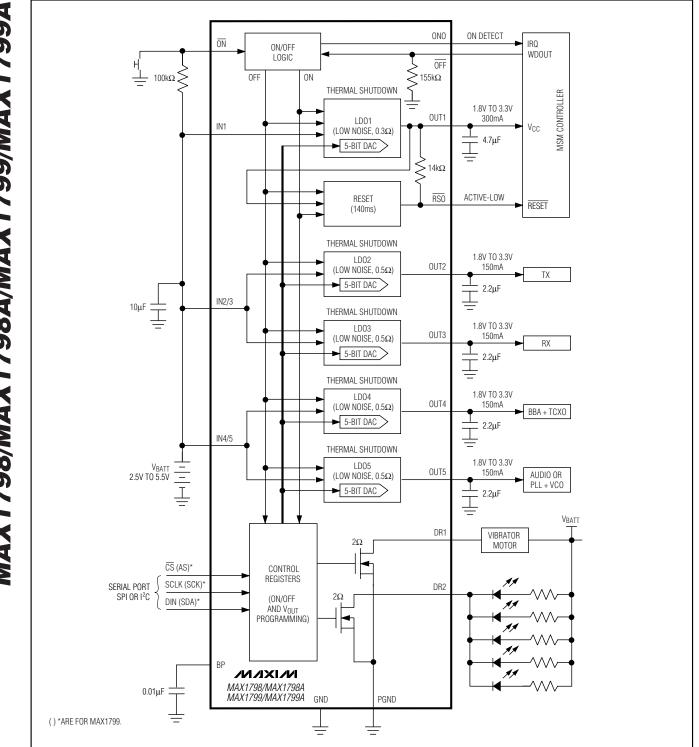

The MAX1798/MAX1798A/MAX1799/MAX1799A system power supplies are designed specifically for CDMA cellular/PCS handsets. Each device contains five lowdropout linear regulators (LDOs), a 140ms (min) reset timer, a serial interface, push-on/push-off control logic, and two general-purpose open-drain outputs. Only the serial interface is different between the MAX1798/ MAX1798A/MAX1799/MAX1799A: the MAX1798/ MAX1798A feature an SPI™-compatible serial interface, and the MAX1799/MAX1799A feature an I<sup>2</sup>C<sup>TM</sup>-compatible interface. The "A" parts have a -13% reset threshold, the non-A parts have a 9.5% threshold. The "A" parts have a 175 delay on a reset-triggered shutdown, the non-A shutdown instantly.

Each linear regulator features extremely low dropout voltage, specified at two-thirds of the maximum output current. LDO1 is rated for 300mA, while LDOS 2–5 are each rated for 150mA. All LDOs are optimized for low noise and isolation. Each LDO can be individually enabled and disabled through the serial port, as well as individually programmed to any of 32 voltages from 1.8V to 3.3V.

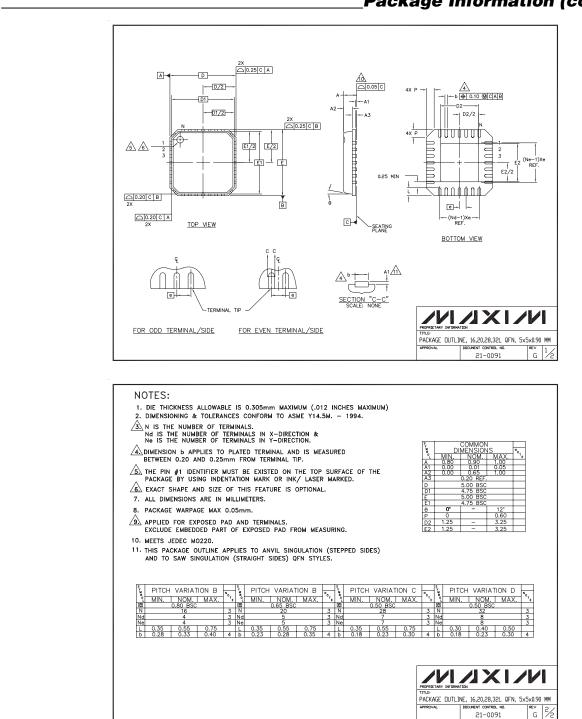

The MAX1798/MAX1798A/MAX1799/MAX1799As' wide 2.5V to 5.5V input voltage range makes them compatible with a wide range of input supplies, including a single lithium-ion (Li+) cell battery. Both devices are available in thermally-enhanced 20-pin TSSOP and QFN exposed pad (EP) packages. Evaluation kits in TSSOP (MAX1798EVKIT and MAX1799EVKIT) are available to facilitate designs.

**WEAXN**

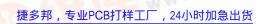

# **Typical Operating Circuit**

\_Features

- One 300mA Low-Noise LDO

- Four 150mA Low-Noise LDOs

- 45µV<sub>RMS</sub> Noise from 10Hz to 100kHz

- >60dB Crosstalk Isolation Below 10kHz

- >60dB PSRR Below 10kHz

- 125mV (max) Dropout (OUT1 at 200mA)

- 100mV (max) Dropout (OUT2–5 at 100mA)

- Programmable Output Voltages 1.8V to 3.3V in 32 Steps

- 140ms (min) Reset Timer

- SPI- or I<sup>2</sup>C-Compatible Serial Interface

- Push-On/Push-Off Control Logic

- Two 150mA General Purpose Open-Drain Outputs

- Overcurrent and Thermal Protection (all LDOs)

- ♦ 1µA Shutdown Current

- 20-Pin Thermally-Enhanced TSSOP or QFN Packages

# **Applications**

CDMA Cellular/PCS Handsets

PDAs, Palmtops, and Handy-Terminals Single-Cell Li+ Systems

Single-Cell LI+ Systems

2- or 3-Cell NiMH, NiCd, or Alkaline Systems

# **Ordering Information**

| PART        | TEMP                        | PIN-        | INTER- |

|-------------|-----------------------------|-------------|--------|

| FANI        | RANGE                       | PACKAGE     | FACE   |

| MAX1798EGP  | <mark>-40°C to +85°C</mark> | 20 QFN      | SPI    |

| MAX1798EUP  | -40°C to +85°C              | 20 TSSOP-EP | SPI    |

| MAX1798AEGP | -40°C to +85°C              | 20 QFN      | SPI    |

| MAX1798AEUP | -40°C to +85°C              | 20 TSSOP-EP | SPI    |

Ordering Information continued and Pin Configurations appear at end of data sheet.

SPI is a trademark of Motorola, Inc. I<sup>2</sup>C is a trademark of Philips Corp.

<sup>60</sup>For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

# **ABSOLUTE MAXIMUM RATINGS**

| OFF, DR1, DR2 to GND                | 0.3V to +6V                         |

|-------------------------------------|-------------------------------------|

| IN1, IN2/3, IN4/5, DIN (SDA) to GND | 0.3V to +6V                         |

| SCLK (SCK), BP, ON to GND           | 0.3V to +6V                         |

| RSO, ONO to GND                     | 0.3V to (V <sub>OUT1</sub> + 0.3V)  |

| PGND to GND                         | ±0.3V                               |

| OUT1, CS (AS) to GND                | 0.3V to (V <sub>IN1</sub> + 0.3V)   |

| OUT2, OUT3 to GND                   | 0.3V to (V <sub>IN2/3</sub> + 0.3V) |

| OUT4, OUT5 to GND                   | 0.3V to (V <sub>IN4/5</sub> + 0.3V) |

|                                     |                                     |

| Continuous Sink Current                               |                      |

|-------------------------------------------------------|----------------------|

| DR1, DR2                                              | 100mA <sub>RMS</sub> |

| RSO                                                   | 25mA                 |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                      |

| 20-Pin QFN (derate 20mW/°C above +70°C)               | 1.6W                 |

| 20-Pin TSSOP (derate 26mW/°C above +70°C)             | 2.1W                 |

| Operating Temperature Range40                         | °C to +85°C          |

| Junction Temperature                                  | +150°C               |

| Storage Temperature Range65°                          |                      |

| Lead Temperature (soldering, 10s)                     | +300°C               |

|                                                       |                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN2/3} = V_{IN4/5} = V_{SCLK} (SCK) = V_{DIN} (SDA) = V_{\overline{CS}} (AS) = V_{\overline{OFF}} = 3.6V; \overline{ON} = GND = PGND = 0; RSO, ONO, DR1, DR2 = open; BP bypassed with 0.01\muF, OUT1 bypassed with 4.7\muF; OUT2, OUT3, OUT4, OUT5 bypassed with 2.2\muF; OUT1-5 set to 2.98V, T_A = 0°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                                         | SYMBOL    | COND                                                                                                          | ITIONS                   | MIN   | ТҮР    | MAX   | UNITS             |

|---------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------|--------------------------|-------|--------|-------|-------------------|

| IN1, IN2/3, IN4/5 Operating<br>Voltage            |           |                                                                                                               |                          | 2.5   |        | 5.5   | V                 |

| Undervoltage Lockout IN1                          | VUVLO-1   | IN1 rising edge                                                                                               |                          | 2.10  | 2.30   | 2.45  | V                 |

| Undervoltage Lockout IN2/3                        | VUVLO-2/3 | IN2/3 rising edge                                                                                             |                          | 2.10  | 2.30   | 2.45  | V                 |

| Undervoltage Lockout IN4/5                        | VUVLO-4/5 | IN4/5 rising edge                                                                                             |                          | 2.10  | 2.30   | 2.45  | V                 |

| Power-On Reset Threshold                          |           | IN1 falling edge                                                                                              |                          | 0.9   |        | 2.1   | V                 |

| Supply Current in Shutdown                        | ISHDN     | $\overline{OFF} = 0, \overline{ON} = IN1$                                                                     |                          |       | 1      | 10    | μA                |

| Supply Current (Standby)                          | ION       | OUT1 ON, other regula                                                                                         | ators OFF $I_{OUT1} = 0$ |       | 113    | 230   | μA                |

| Supply Current (All Outputs On)                   |           | All regulators ON, IOU                                                                                        | T_ = 0                   |       | 367    | 680   | μA                |

| BP Voltage                                        |           | I <sub>BP</sub> ≤ 1nA                                                                                         |                          | 1.231 | 1.250  | 1.269 | V                 |

| BP Supply Rejection                               |           | $2.5V \leq V_{\rm IN1} \leq 5.5V$                                                                             |                          |       | 0.2    | 5     | mV                |

| OUT1 REGULATOR                                    |           |                                                                                                               | ·                        |       |        |       |                   |

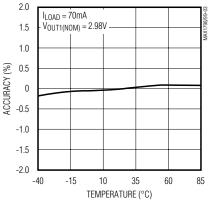

| Output Accuracy                                   |           | I <sub>OUT1</sub> = 70mA (Note 3                                                                              | )                        | -2    |        | 2     | %                 |

| Output Accuracy<br>(Line and Load)                |           | $1\text{mA} \leq I_{OUT1} \leq 300\text{mA}$ $2.5\text{V} \leq \text{V}_{IN1} \leq 5.5\text{V}, \text{V}_{O}$ | ·                        | -3    |        | 3     | %                 |

| Nominal Voltage Adjust Range                      |           | 32 steps through seria                                                                                        | l interface; Tables 2, 3 | 1.8   |        | 3.3   | V                 |

| Dranaut Valtage                                   |           | I <sub>OUT1</sub> = 1mA (Notes 1                                                                              | , 3)                     |       | 1      |       | mV                |

| Dropout Voltage                                   |           | I <sub>OUT1</sub> = 200mA (Notes                                                                              | s 1, 3)                  |       | 73     | 125   | IIIV              |

| Load Regulation                                   |           | $0.1 \text{mA} \le I_{OUT1} \le 300 \text{m}$                                                                 | nA                       |       | -0.003 |       | %/mA              |

| Line Regulation                                   |           | $2.5V \le V_{IN1} \le 5.5V, V_{O}$                                                                            | UT1 = 1.8V (Note 3)      | -0.15 | -0.03  | 0.11  | %/V               |

| Current Limit                                     |           |                                                                                                               |                          | 320   | 500    | 850   | mA                |

| Output-Discharge Switch<br>Resistance in Shutdown |           | Regulator output turned off                                                                                   |                          |       | 25     | 300   | Ω                 |

| OUT1 Reset Threshold                              |           | OUT1 rising and                                                                                               | (MAX1798/MAX1799)        | -9.5  | -7.5   | -5.5  | %                 |

|                                                   |           | falling                                                                                                       | (MAX1798A/MAX1799A)      | -15   | -13    | -11   | 70                |

| Output Voltage Noise                              |           | f = 10Hz to $100kHz$ , C                                                                                      | -<br>Ουτ = 4.7μF         |       | 45     |       | μV <sub>RMS</sub> |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2/3} = V_{IN4/5} = V_{SCLK} (SCK) = V_{DIN} (SDA) = V_{\overline{CS}} (AS) = V_{\overline{OFF}} = 3.6V; \overline{ON} = GND = PGND = 0; RSO, ONO, DR1, DR2 = open; BP bypassed with 0.01\muF, OUT1 bypassed with 4.7\muF; OUT2, OUT3, OUT4, OUT5 bypassed with 2.2\muF; OUT1-5 set to 2.98V, T_A = 0°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                                           | SYMBOL      | CONDITIONS                                                                                         | MIN            | ТҮР    | MAX  | UNITS       |

|-----------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------|----------------|--------|------|-------------|

| OUT2-5 REGULATORS                                   | I           |                                                                                                    |                |        |      | I           |

| Output Accuracy                                     |             | I <sub>OUT</sub> = 50mA (Note 3)                                                                   | -2             |        | 2    | %           |

| Output Accuracy<br>(Line and Load)                  |             | 1mA ≤ I <sub>OUT</sub> ≤ 150mA,<br>2.5V ≤ V <sub>IN</sub> ≤ 5.5V, V <sub>OUT</sub> = 1.8V (Note 3) | -3             |        | 3    | %           |

| Nominal Voltage Adjust Range                        |             | 32 steps through serial interface; Tables 2, 3                                                     | 1.8            |        | 3.3  | V           |

| Dropout Voltage                                     |             | $I_{OUT} = 1mA$ (Notes 1, 3)                                                                       |                | 1      | 100  | mV          |

| Lood Doculation                                     |             | IOUT_ = 100mA (Notes 1, 3)                                                                         |                | 50     | 100  | 0/ /ma A    |

| Load Regulation                                     |             | $1\text{mA} \le I_{OUT} \le 150\text{mA}$<br>2.5V \le V_{IN} \le 5.5V, V_{OUT} = 1.8V (Note 3)     | -0.15          | -0.005 | 0.11 | %/mA<br>%/V |

| Current Limit                                       |             | $2.50 \le 0   _{N_{-}} \le 5.50, 0   _{-} = 1.60 (100   _{-} = 3)$                                 | 160            | 250    | 500  | mA          |

| Output-Discharge Switch<br>Resistance               |             | Regulator output turned off                                                                        | 100            | 110    | 300  | Ω           |

| Output Voltage Noise                                |             | f = 10Hz to 100kHz, COUT = 2.2µF                                                                   |                | 45     |      | μVRMS       |

| 1 0                                                 | S (ON, OFF. | RSO, DIN (SDA), SCLK (SCK), CS (AS))                                                               |                |        |      | P-1100      |

| Reset Timer                                         |             |                                                                                                    | 140            | 235    | 430  | ms          |

| Watchdog Timer                                      |             |                                                                                                    | 35             | 60     | 110  | ms          |

| OUT1 Shutdown Timer<br>(MAX1798A/MAX1799A only)     |             |                                                                                                    | 175            | 295    | 540  | ms          |

| Input Low Level                                     | VIL         |                                                                                                    |                |        | 0.4  | V           |

| Input High Level                                    | VIH         |                                                                                                    | 1.6            |        |      | V           |

| SDA Output Low Level                                |             | I <sub>DIN (SDA)</sub> = 3mA                                                                       |                |        | 0.4  | v           |

| (MAX1799 only)                                      |             | I <sub>DIN (SDA)</sub> = 6mA                                                                       |                |        | 0.6  | v           |

| OFF Pulldown Resistance                             |             | <del>OFF</del> = 5.5V                                                                              | 80             | 155    | 360  | kΩ          |

| ONO Output Low Level                                |             | I <sub>ONO</sub> = 1mA                                                                             |                | 0.05   | 0.5  | V           |

| ONO Output High Level                               |             | I <sub>ONO</sub> = -1mA                                                                            | Vout1 -<br>0.5 |        |      | V           |

| RSO Output Low Level                                |             | $I_{RSO} = 1mA, V_{IN1} = 1V$                                                                      |                |        | 0.5  | V           |

| RSO Output High Level<br>(Internal Pullup Resistor) |             | I <sub>RSO</sub> = 0                                                                               | Vout1 -<br>0.5 |        |      | V           |

| RSO Reset Resistance                                |             | RSO = 2.48V                                                                                        | 9              | 14     | 19   | kΩ          |

| DR1, DR2 Output Low Level                           |             | I <sub>DR1</sub> = I <sub>DR2</sub> = 100mA (Note 3)                                               | 1              | 0.2    | 0.5  | V           |

| DR1, DR2 OFF Current<br>(Leakage)                   | IOFF        | $V_{DR1} = V_{DR2} = 5.5V$                                                                         | -1             |        | 1    | μA          |

| THERMAL SHUTDOWN                                    | 1           | 1                                                                                                  | 1              |        |      | 1           |

| Threshold                                           |             |                                                                                                    |                | 160    |      | °C          |

| Hysteresis                                          |             |                                                                                                    |                | 10     |      | °C          |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2/3} = V_{IN4/5} = V_{SCLK} (SCK) = V_{DIN} (SDA) = V_{\overline{CS}} (AS) = V_{\overline{OFF}} = 3.6V; \overline{ON} = GND = PGND = 0; RSO, ONO, DR1, DR2 = open; BP bypassed with 0.01 \mu F, OUT1 bypassed with 4.7 \mu F; OUT2, OUT3, OUT4, OUT5 bypassed with 2.2 \mu F; OUT1-5 set to 2.98V, T_A = 0°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                                                                                                      | SYMBOL              | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|----------------------------------------------------------------------------------------------------------------|---------------------|------------|-----|-----|-----|-------|

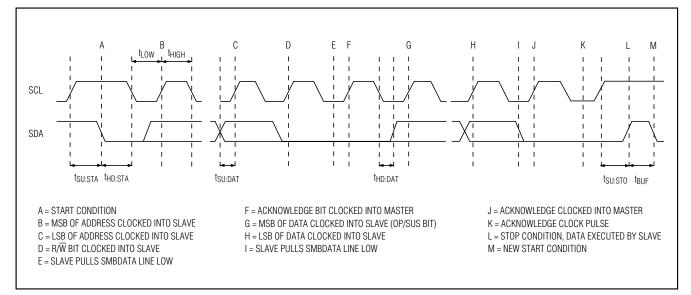

| I <sup>2</sup> C (SMB) TIMING (MAX1799/MA                                                                      | AX1799A)            |            |     |     |     |       |

| Clock Frequency                                                                                                | SCK                 |            |     |     | 400 | kHz   |

| Bus-Free Time Between START and STOP                                                                           | <sup>t</sup> BUF    |            | 1.3 |     |     | μs    |

| Hold Time Repeated START<br>Condition                                                                          | <sup>t</sup> HD_STA |            | 0.6 |     |     | μs    |

| SCK Low Period                                                                                                 | tLOW                |            | 1.3 |     |     | μs    |

| SCK High Period                                                                                                | thigh               |            | 0.6 |     |     | μs    |

| Setup Time Repeated START<br>Condition                                                                         | tsu_sta             |            | 0.6 |     |     | μs    |

| Data Hold Time                                                                                                 | thd_dat             |            | 0   |     |     | μs    |

| Data Setup Time                                                                                                | tsu_dat             |            | 100 |     |     | ns    |

| Maximum Pulse Width of Spikes<br>that Must Be Suppressed by the<br>Input Filter of Both SDA and<br>SCK Signals | tsp                 |            |     | 50  |     | ns    |

| Setup Time for STOP Condition                                                                                  | tsu_sto             |            | 0.6 |     |     | μs    |

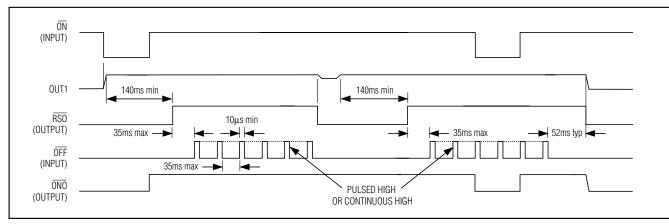

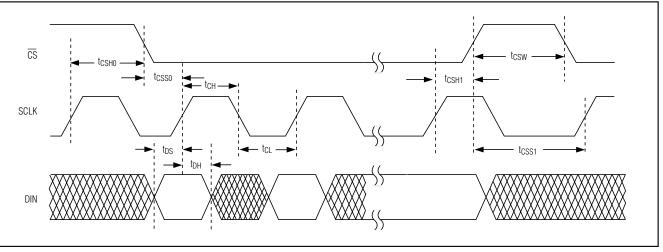

| SPI TIMING (MAX1798/MAX1798                                                                                    | BA)                 |            |     |     |     |       |

| SCLK Clock Frequency                                                                                           | <b>f</b> SCLK       |            |     |     | 2   | MHz   |

| SCLK Low Period                                                                                                | t <sub>cl</sub>     |            | 125 |     |     | ns    |

| SCLK High Period                                                                                               | t <sub>ch</sub>     |            | 125 |     |     | ns    |

| Data Hold Time                                                                                                 | <sup>t</sup> HD_DAT |            | 0   |     |     | ns    |

| Data Setup Time                                                                                                | tsu_dat             |            | 125 |     |     | ns    |

| CS Assertion to SCLK Rising<br>Edge Setup Time                                                                 | tCSS                |            | 200 |     |     | ns    |

| CS Deassertion to SCLK Rising<br>Edge Setup Time                                                               | tCS1                |            | 200 |     |     | ns    |

| SCLK Rising Edge to CS<br>Deassertion                                                                          | tcsh                |            | 200 |     |     | ns    |

| SCLK Rising Edge to CS<br>Assertion                                                                            | tcso                |            | 200 |     |     | ns    |

| CS High Period                                                                                                 | tcsw                |            | 300 |     |     | ns    |

|                                                                                                                | I                   |            |     |     |     | I     |

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN2/3} = V_{IN4/5} = V_{SCLK} (SCK) = V_{DIN} (SDA) = V_{\overline{CS}} (AS) = V_{\overline{OFF}} = 3.6V; \overline{ON} = GND = PGND = 0; RSO, ONO, DR1, DR2 = open; BP bypassed with 0.01 \muF, OUT1 bypassed with 4.7 \muF; OUT2, OUT3, OUT4, OUT5 bypassed with 2.2 \muF; OUT1-5 set to 2.98V, TA = -40°C to +85°C, unless otherwise noted.) (Note 2)$

| PARAMETER                                         | SYMBOL    | COND                                                                                                    | ITIONS                                                                                                                        | MIN   | TYP | MAX   | UNITS |

|---------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| IN1, IN2/3, IN4/5 Operating<br>Voltage            |           | (Note 1)                                                                                                |                                                                                                                               | 2.5   |     | 5.5   | V     |

| Undervoltage Lockout IN1                          | VUVLO-1   | IN1 rising edge                                                                                         |                                                                                                                               | 2.10  |     | 2.45  | V     |

| Undervoltage Lockout IN2/3                        | VUVLO-2/3 | IN2/3 rising edge                                                                                       |                                                                                                                               | 2.10  |     | 2.45  | V     |

| Undervoltage Lockout IN4/5                        | VUVLO-4/5 | IN4/5 rising edge                                                                                       |                                                                                                                               | 2.10  |     | 2.45  | V     |

| Power-On Reset Threshold                          |           | IN1 falling edge                                                                                        |                                                                                                                               | 0.9   |     | 2.1   | V     |

| Supply Current in Shutdown                        | ISHDN     | $\overline{OFF} = 0, \overline{ON} = IN1$                                                               |                                                                                                                               |       |     | 10    | μA    |

| Supply Current (Standby)                          | ION       | OUT1 ON, other regula                                                                                   | ators OFF $I_{OUT1} = 0$                                                                                                      |       |     | 230   | μA    |

| Supply Current (All Outputs On)                   |           | All regulators ON, IOU-                                                                                 | r_ = 0                                                                                                                        |       |     | 680   | μA    |

| BP Voltage                                        |           | I <sub>BP</sub> ≤ 1nA                                                                                   |                                                                                                                               | 1.225 |     | 1.275 | V     |

| OUT1 REGULATOR                                    |           |                                                                                                         |                                                                                                                               |       |     |       |       |

| Output Accuracy                                   |           | I <sub>OUT1</sub> = 70mA (Note 3)                                                                       | )                                                                                                                             | -2.5  |     | 2.5   | %     |

| Output Accuracy<br>(Line and Load)                |           |                                                                                                         | $1\text{mA} \le I_{\text{OUT1}} \le 300\text{mA},$<br>2.5V $\le V_{\text{IN1}} \le 5.5$ V, $V_{\text{OUT1}} = 1.8$ V (Note 3) |       |     | 3.5   | %     |

| Nominal-Voltage Adjust Range                      |           | 32 steps through serial interface; Tables 2, 3                                                          |                                                                                                                               | 1.8   |     | 3.3   | V     |

| Dropout Voltage                                   |           | I <sub>OUT1</sub> = 200mA (Notes 1, 3)                                                                  |                                                                                                                               |       |     | 125   | mV    |

| Line Regulation                                   |           | $2.5V \le V_{IN1} \le 5.5V, V_{O}$                                                                      | UT1 = 1.8V (Note 3)                                                                                                           | -0.15 |     | 0.11  | %/V   |

| Current Limit                                     |           |                                                                                                         |                                                                                                                               | 320   |     | 850   | mA    |

| Output-Discharge Switch<br>Resistance in Shutdown |           | Regulator output turne                                                                                  | d off                                                                                                                         |       |     | 300   | Ω     |

|                                                   |           | OUT1 rising and                                                                                         | MAX1798/MAX1799                                                                                                               | -9.5  |     | -5.5  |       |

| OUT1 Reset Threshold                              |           | falling                                                                                                 | MAX1798A/MAX1799A                                                                                                             | -15   |     | -11   | %     |

| OUT2-5 REGULATORS                                 |           |                                                                                                         | 1                                                                                                                             |       |     |       |       |

| Output Accuracy                                   |           | I <sub>OUT</sub> = 50mA (Note 3)                                                                        | )                                                                                                                             | -2.5  |     | 2.5   | %     |

| Output Accuracy<br>(Line and Load)                |           | $1\text{mA} \le I_{OUT} \le 150\text{mA}$ $2.5\text{V} \le \text{V}_{IN} \le 5.5\text{V}, \text{V}_{O}$ |                                                                                                                               | -3.5  |     | 3.5   | %     |

| Nominal-Voltage Adjust Range                      |           | 32 steps through serial interface; Tables 2, 3                                                          |                                                                                                                               | 1.8   |     | 3.3   | V     |

| Dropout Voltage                                   |           | I <sub>OUT</sub> = 100mA (Notes                                                                         | 1, 3)                                                                                                                         |       |     | 100   | mV    |

| Line Regulation                                   |           | 2.5V ≤ V <sub>IN</sub> ≤ 5.5V, V <sub>O</sub>                                                           | UT_ = 1.8V (Note 3)                                                                                                           | -0.15 |     | 0.11  | %/V   |

| Current Limit                                     |           |                                                                                                         |                                                                                                                               | 160   |     | 500   | mA    |

| Output-Discharge Switch<br>Resistance in Shutdown |           | Regulator output turne                                                                                  | d off                                                                                                                         |       |     | 300   | Ω     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2/3} = V_{IN4/5} = V_{SCLK} (SCK) = V_{DIN} (SDA) = V_{\overline{CS}} (AS) = V_{\overline{OFF}} = 3.6V; \overline{ON} = GND = PGND = 0; RSO, ONO, DR1, DR2 = open; BP bypassed with 0.01 \mu F, OUT1 bypassed with 4.7 \mu F; OUT2, OUT3, OUT4, OUT5 bypassed with 2.2 \mu F; OUT1-5 set to 2.98V, T_A = -40°C to +85°C, unless otherwise noted.) (Note 2)$

| PARAMETER                                           | SYMBOL              | CONDITIONS                                                                                          | MIN                        | ТҮР | МАХ | UNITS |

|-----------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|----------------------------|-----|-----|-------|

| LOGIC AND CONTROL INPUTS                            | (ON, OFF, I         | RSO DIN (SDA), SCLK (SCK), CS (AS))                                                                 |                            |     |     |       |

| Reset Timer                                         |                     |                                                                                                     | 140                        |     | 430 | ms    |

| Watchdog Timer                                      |                     |                                                                                                     | 35                         |     | 110 | ms    |

| OUT1 Shutdown Timer<br>(MAX1798A/MAX1799A only)     |                     |                                                                                                     | 175                        |     | 540 | ms    |

| Input Low Level                                     | VIL                 |                                                                                                     |                            |     | 0.4 | V     |

| Input High Level                                    | VIH                 |                                                                                                     | 1.6                        |     |     | V     |

| SDA Output Low Level                                |                     | I <sub>DIN (SDA)</sub> = 3mA                                                                        |                            |     | 0.4 | v     |

| (MAX1799 only)                                      |                     | I <sub>DIN</sub> (SDA) = 6mA                                                                        |                            |     | 0.6 |       |

| Logic Input Current                                 |                     | $0 \le V_{IN} \le V_{IN1}$ ; $\overline{ON}$ , DIN (SDA), SCLK (SCK), and $\overline{CS}$ (AS) only | -1                         |     | 1   | μA    |

| OFF Pulldown Resistance                             |                     | $\overline{OFF} = 5.5V$                                                                             | 80                         |     | 360 | kΩ    |

| ONO Output Low Level                                |                     | I <sub>ONO</sub> = 1mA                                                                              |                            |     | 0.5 | V     |

| ONO Output High Level                               |                     | I <sub>ONO</sub> = -1mA                                                                             | V <sub>OUT1</sub> -<br>0.5 |     |     | V     |

| RSO Output Low Level                                |                     | $I_{RSO} = 1mA, V_{IN1} = 1V$                                                                       |                            |     | 0.5 | V     |

| RSO Output High Level<br>(Internal Pullup Resistor) |                     | I <sub>RSO</sub> = 0                                                                                | Vout1 -<br>0.5             |     |     | V     |

| RSO Reset Resistance                                |                     | RSO = 2.48V                                                                                         | 9                          |     | 19  | kΩ    |

| DR1, DR2 Output Low Level                           |                     | I <sub>DR1</sub> = I <sub>DR2</sub> = 100mA (Note 3)                                                |                            |     | 0.5 | V     |

| DR1, DR2 OFF Current<br>(Leakage)                   | IOFF                | $V_{DR1} = V_{DR2} = 5.5V$                                                                          | -1                         |     | 1   | μA    |

| I <sup>2</sup> C (SMB) TIMING (MAX1799/M            | AX1799A)            |                                                                                                     |                            |     |     |       |

| Clock Frequency                                     | SCK                 |                                                                                                     |                            |     | 400 | kHz   |

| Bus-Free Time Between START and STOP                | tBUF                |                                                                                                     | 1.3                        |     |     | μs    |

| Hold Time Repeated START<br>Condition               | thd_sta             |                                                                                                     | 0.6                        |     |     | μs    |

| SCK Low Period                                      | tLOW                |                                                                                                     | 1.3                        |     |     | μs    |

| SCK High Period                                     | thigh               |                                                                                                     | 0.6                        |     |     | μs    |

| Setup Time Repeated START<br>Condition              | tsu_sta             |                                                                                                     | 0.6                        |     |     | μs    |

| Data Hold Time                                      | thd_dat             |                                                                                                     | 0                          | 89  |     | μs    |

| Data Setup Time                                     | t <sub>SU_DAT</sub> |                                                                                                     | 100                        |     |     | ns    |

| Setup Time for STOP Condition                       | tsu_sto             |                                                                                                     | 0.6                        |     |     | μs    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2/3} = V_{IN4/5} = V_{SCLK} (SCK) = V_{DIN} (SDA) = V_{\overline{CS}} (AS) = V_{\overline{OFF}} = 3.6V; \overline{ON} = GND = PGND = 0; RSO, ONO, DR1, DR2 = open; BP bypassed with 0.01 \mu F, OUT1 bypassed with 4.7 \mu F; OUT2, OUT3, OUT4, OUT5 bypassed with 2.2 \mu F; OUT1-5 set to 2.98V, T_A = -40°C to +85°C, unless otherwise noted.) (Note 2)$

| PARAMETER                                          | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|------------------|------------|-----|-----|-----|-------|

| SPI TIMING (MAX1798/MAX179                         | 8A)              |            |     |     |     | 1     |

| SCLK Clock Frequency                               | fsclk            |            |     |     | 2   | MHz   |

| SCLK Low Period                                    | t <sub>cl</sub>  |            | 125 |     |     | ns    |

| SCLK High Period                                   | t <sub>ch</sub>  |            | 125 |     |     | ns    |

| Data Hold Time                                     | thd_dat          |            | 0   |     |     | ns    |

| Data Setup Time                                    | tsu_dat          |            | 125 |     |     | ns    |

| CS Assertion to SCLK Rising<br>Edge Setup Time     | tcss             |            | 200 |     |     | ns    |

| CS Deassertion to SCLK Rising<br>Edge Setup Time   | tCS1             |            | 200 |     |     | ns    |

| SCLK Rising Edge to $\overline{CS}$<br>Deassertion | tcsн             |            | 200 |     |     | ns    |

| SCLK Rising Edge to $\overline{CS}$ Assertion      | tcso             |            | 200 |     |     | ns    |

| CS High Period                                     | t <sub>CSW</sub> |            | 300 |     |     | ns    |

Note 1: The dropout voltage is defined as (VIN - VOUT) when VOUT is 100mV below the value of VOUT for VIN = VOUT + 1V.

Note 2: Specifications to -40°C are guaranteed by design, not production tested.

Note 3: Specifications are guaranteed by design, not production tested in the EGP (QFN) package.

### $(T_A = +25^{\circ}C, unless otherwise noted.)$

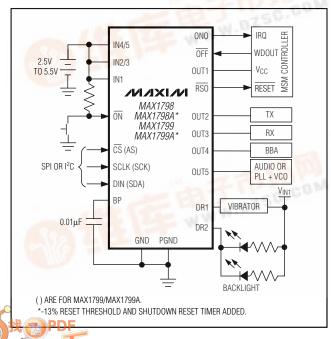

### OUTPUT VOLTAGE ACCURACY (OUT1) vs. temperature

**Typical Operating Characteristics**

# MAX1798/MAX1798A/MAX1799/MAX1799A

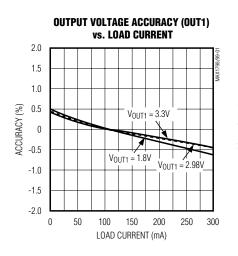

# **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

MAX1798/MAX1798A/MAX1799/MAX1799A

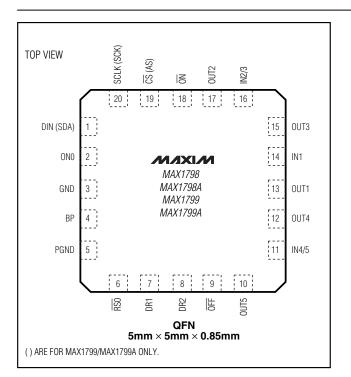

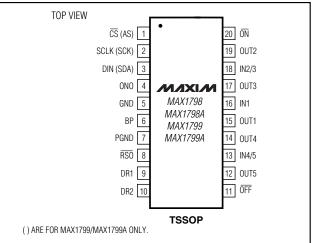

# **Pin Description**

| PIN   |                |               |                                                                                                                                                                                                                                                                                                              |

|-------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | TSSOP QFN NAME |               | FUNCTION                                                                                                                                                                                                                                                                                                     |

| 1     | 19             | CS (AS)       | Chip-Select Input for SPI (MAX1798/MAX1798A). Address Select Input for I <sup>2</sup> C (MAX1799/MAX1799A).                                                                                                                                                                                                  |

| 2     | 20             | SCLK<br>(SCK) | Clock Input for Serial Interface. Data is read on the rising edge of the clock. SCLK for MAX1798/MAX1798A. SCK for MAX1799/MAX1799A.                                                                                                                                                                         |

| 3     | 1              | DIN<br>(SDA)  | Data Input for Serial Interface. Data is read on the rising edge of the clock. DIN for MAX1798/MAX1798A. SDA for MAX1799/MAX1799A.                                                                                                                                                                           |

| 4     | 2              | ONO           | ON Output. Indicates the state of $\overline{ON}$ . After initial power-up, the logic level of this pin follows that of $\overline{ON}$ . Used to signal the microcontroller ( $\mu$ C) for an OFF request (allows push-on/push-off).                                                                        |

| 5     | 3              | GND           | Ground                                                                                                                                                                                                                                                                                                       |

| 6     | 4              | BP            | 1.25V Reference Bypass. Connect a 0.01µF bypass capacitor to GND for reduced noise. <b>Do not load this pin.</b>                                                                                                                                                                                             |

| 7     | 5              | PGND          | Power Ground                                                                                                                                                                                                                                                                                                 |

| 8     | 6              | RSO           | Reset Output. Holds the $\mu$ C system reset line low during initial startup and whenever OUT1 falls out of regulation. RSO has a 140ms (min) timeout period and is an open-drain output with an internal 14k $\Omega$ pullup to OUT1. The RSO line maintains a valid low output level for IN1 as low as 1V. |

| 9     | 7              | DR1           | $2\Omega$ Open-Drain Driver Output 1. Maximum sink current is 150mA (100mA <sub>RMS</sub> ). Can drive up to 10 LEDs for backlight or a vibrator motor.                                                                                                                                                      |

| 10    | 8              | DR2           | $2\Omega$ Open-Drain Driver Output 2. Maximum sink current is 150mA (100mA <sub>RMS</sub> ). Can drive up to 10 LEDs for backlight or a vibrator motor.                                                                                                                                                      |

| 11    | 9              | OFF           | OFF Input. A low level to this pin when $\overline{ON}$ is high turns off the IC once the watchdog timer has timed out. A high-level input keeps the chip on. There is an internal 155k $\Omega$ pulldown resistor at this input.                                                                            |

| 12    | 10             | OUT5          | Output 5, Output of Linear Regulator 5; 150mA (max) Output Current. Connect a 2.2µF ceramic bypass capacitor to PGND.                                                                                                                                                                                        |

| 13    | 11             | IN4/5         | Supply Inputs 4 and 5. Voltage supply for linear regulators 4 and 5.                                                                                                                                                                                                                                         |

| 14    | 12             | OUT4          | Output 4, Output of Linear Regulator 4; 150mA (max) Output Current. Connect a 2.2µF ceramic bypass capacitor to PGND.                                                                                                                                                                                        |

| 15    | 13             | OUT1          | Output 1, Output of Linear Regulator 1; 300mA (max) Output Current. Connect a 4.7µF ceramic bypass capacitor to PGND.                                                                                                                                                                                        |

| 16    | 14             | IN1           | Supply Input 1. Voltage supply for linear regulator 1 and serial interface.                                                                                                                                                                                                                                  |

| 17    | 15             | OUT3          | Output 3, Output of Linear Regulator 3; 150mA (max) Output Current. Connect a 2.2µF ceramic bypass capacitor to PGND.                                                                                                                                                                                        |

| 18    | 16             | IN2/3         | Supply Inputs 2 and 3. Voltage supply for linear regulators 2 and 3.                                                                                                                                                                                                                                         |

| 19    | 17             | OUT2          | Output 2, Output of Linear Regulator 2; 150mA (max) Output Current. Connect a 2.2µF ceramic bypass capacitor to PGND.                                                                                                                                                                                        |

| 20    | 18             | ŌN            | ON Input. An active-low turns on the device, enabling LDO1, RESET, the ON/OFF logic, and the serial interface.                                                                                                                                                                                               |

| FUNCTION           |    | COMMAND |    |                     | DIN (SDA) |            |    |     |  |

|--------------------|----|---------|----|---------------------|-----------|------------|----|-----|--|

| FUNCTION           | C2 | C1      | C0 | D4                  | D3        | D2         | D1 | D0  |  |

| Update DAC Outputs | 0  | 0       | 0  | U5                  |           |            | U2 | U1  |  |

| OUT1 DAC           | 0  | 0       | 1  | DAC1 (Table 2)      |           |            |    |     |  |

| OUT2 DAC           | 0  | 1       | 0  |                     | D,        | AC1 (Table | 2) |     |  |

| OUT3 DAC           | 0  | 1       | 1  |                     | D,        | AC1 (Table | 2) |     |  |

| OUT4 DAC           | 1  | 0       | 0  |                     | D,        | AC1 (Table | 2) |     |  |

| OUT5 DAC           | 1  | 0       | 1  | DAC1 (Table 2)      |           |            |    |     |  |

| Driver Outputs     | 1  | 1       | 0  | X X X DR2 DR1       |           |            |    | DR1 |  |

| ON/OFF Conrol      | 1  | 1       | 1  | ON5 ON4 ON3 ON2 ON1 |           |            |    | ON1 |  |

# Table 1. Control Data Byte

Note: C2 is MSB, and D0 is LSB. X = Don't care.

# **Detailed Description**

The MAX1798/MAX1798A/MAX1799/MAX1799A drive CDMA cellular and PCS handsets or systems with inputs from 2.5V to 5.5V. The devices contain five LDOs, two open-drain outputs, and a reset output as shown in Figure 1. All outputs are individually programmable through either an SPI (MAX1798/MAX1798A) or I<sup>2</sup>C (MAX1799/MAX1799A) serial-port interface. The outputs may be turned on or off individually through the serial interface. Their output voltages are adjustable from 1.8V to 3.3V in 32 increments. At power-up, all outputs are at a default value of 2.98V, but only OUT1 is on. OUT1 is rated for 300mA and optimized for low dropout. OUT2–5 are rated for 150mA. All LDOs are optimized for low noise, high isolation, and low dropout.

### Linear Regulator 1

Regulator 1 is a low-dropout linear regulator that sources 300mA (max), operating from a 2.5V to 5.5V input voltage (V<sub>IN1</sub>). OUT1 is turned on by using the on button. OUT1 is turned off by using either the off pin or the serial port. Its output can be adjusted from 1.8V to 3.3V from the SPI or I<sup>2</sup>C serial-port interface by setting the control data byte (Table 1). OUT1 is always on when the MAX1798/MAX1798A/MAX1799/MAX1799A are on. If OUT1 is turned off, the entire IC shuts down. If VIN1 falls below 1V, a POR circuit resets all LDO voltages to 2.98V and OUT1 is left on while OUT2–5 are turned off.

## **Linear Regulators 2–5**

Regulators 2–5 are LDOs that source 150mA (max) from input voltages ( $V_{IN2/3}$  and  $V_{IN4/5}$ ) of 2.5V to 5.5V. OUT2–5 can be turned on or off and adjusted from 1.8V to 3.3V through the SPI or I<sup>2</sup>C serial-port interface by setting the control data byte (Table 1). At power-up,

OUT2–5 are set to 2.98V, but turned off. The control data byte must be used to turn them on. If V<sub>IN1</sub> falls below 1V, a POR circuit resets all LDO voltages to 2.98V and OUT2–5 are turned off. If V<sub>IN2/3</sub> or V<sub>IN4/5</sub> fall below 2.15V, the UVLO circuit turns off the corresponding output, but all LDO voltages remain at their prior settings. OUT2–5 are optimized for low noise and high isolation.

## **Open-Drain Outputs**

The open-drain N-channel MOSFETs (DR1 and DR2, Figure 2) have a nominal  $2\Omega$  on-resistance and can be used to drive up to 10 LEDs for backlight or a vibrator motor. DR1 and DR2 can sink 100mA<sub>RMS</sub> (max). At power-up, DR1 and DR2 are high impedance and are commanded on by the control data byte.

# RSO

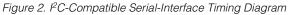

$\overline{RSO}$  is an open-drain output, connected to OUT1 through an internal  $14k\Omega$  resistor. At power-up, OUT1 turns on and  $\overline{RSO}$  is held low for 140ms (min). When  $\overline{RSO}$  goes high,  $\overline{OFF}$  must be brought high within 35ms to keep OUT1 on. Otherwise, if  $\overline{OFF}$  is low, the watchdog timer circuit counts down 35ms (min), and  $\overline{RSO}$  is actively held low while the entire device turns off.

The MAX1798/MAX1799  $\overline{\text{RSO}}$  goes low when OUT1 droops by more than 7.5% ±2% of its programmed output voltage. The MAX1798A/MAX1799A  $\overline{\text{RSO}}$  goes low when OUT1 droops by more than 13% ±2% of its programmed output voltage.  $\overline{\text{RSO}}$  stays low for 140ms (min) after OUT1 rises above the threshold. During this time, the watchdog timer circuit is inactive.

The MAX1798A/MAX1799A have an additional timer circuit to shut down the regulators when the  $\overline{\text{RSO}}$  and watchdog timer time out. If the OUT1 voltage level ever exceeds the  $\overline{\text{RSO}}$  threshold level before the reset and

Figure 3. Push-On/Push-Off Startup and Shutdown Timing Diagram

watchdog timers time out, the shutdown timer is reset. The shutdown timer requires continuous low RSO signal and continuous nontriggered watchdog timer to shut down the regulators.

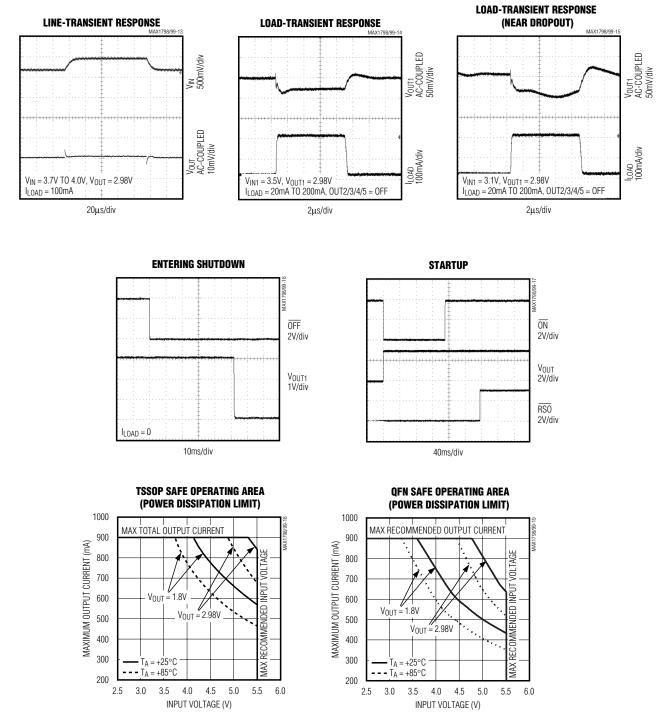

# **ON** and **OFF** Logic

See Figure 3. The MAX1798/MAX1798A/MAX1799/MAX1799A power up when V<sub>IN1</sub> is greater than 2.5V and  $\overline{ON}$  is low ( $\overline{ON}$  button is pressed down momentarily). When  $\overline{ON}$  returns high, the device remains on. It turns on OUT1 and the serial interface port. Once OUT1 is in regulation,  $\overline{RSO}$  stays low an additional

140ms (min). At this time, OUT1 is on and set to 2.98V, while OUT2–5 are disabled and set to 2.98V. To stay on, the OFF pin must be in a high state within 35ms (min) or the device will shut down and can only be turned on by pressing the ON button. While ON is held low, the status of OFF is irrelevant and OUT1 and the serial port are on.

After initial power-up, the logic level of ONO follows the logic level of  $\overline{ON}$  but is level-shifted to OUT1 high voltage. This signal can be used to interrupt the system controller, which can subsequently manage an orderly shutdown through the serial port by turning off OUT1.

### Hard Shutdown

To shut down the MAX1798/MAX1798A/MAX1799/ MAX1799A, drive OFF low or allow the internal resistor to pull down OFF while ON is high. The device shuts down after the watchdog timer has cleared (35ms min, 52ms typ). During shutdown, all LDO outputs and RSO are actively pulled to GND, the open-drain drivers are in a high-impedance state, and the serial port and reset timer are inactive. Previously programmed output voltage data is retained in the internal registers as long as VIN1 > 2.1V. If the device is turned back on by the ON button, OUT1 automatically is enabled with the preshutdown output voltage. OUT2–5 automatically return to their preshutdown voltages once they are enabled through the serial interface.

### Soft Shutdown

The serial port can also be used to shut down the MAX1798/MAX1798A/MAX1799/MAX1799A. Using the control data byte to disable OUT1 will shut down the entire device. Once shut down, the only means to turn on the device is through a momentary low on the ON button.

### **Control Data Byte**

The control data byte is 8 bits long (3 command bits and 5 data bits). The first 3 bits specify the action to be taken, while the last 5 bits set the output voltage or ON/OFF status. Each regulator has an individual DAC that sets the output voltage. The DAC registers are double buffered to allow for simultaneous updating of all outputs. The output voltage is programmed per Table 2 or Table 3. At power-up, if no specific voltage is programmed, OUT1-5 will be set for 2.98V. All DAC programming must be shifted from the double buffer to the DACs with the update DAC command (Table 1, 000XXXXX) for the programmed voltages to be seen at the LDO outputs. The DACs can be updated one at a time or all at once after all desired outputs are programmed. The ON/OFF status of the LDOs and drivers is not double-buffered and takes immediate effect upon CS returning high (SPI compatible) or upon the ninth rising edge of SCK during the command byte (Figure 2, edge L). A one turns on the LDO output or driver output, and a zero turns it off.

### SPI-Compatible Serial Interface

Use an SPI-compatible 3-wire serial interface with the MAX1798/MAX1798A to control the ON/OFF state and output voltage of each regulator, the ON/OFF state of the drivers, and to shut down the device. Figures 4a and 4b are timing diagrams for the SPI protocol. The MAX1798/MAX1798A is a write-only device and uses

CS along with SCLK and DIN to communicate. The serial port operates when the device is enabled, even when RSO is low. The MAX1798/MAX1798A can support a 2MHz (max) data rate. This SPI-compatible port uses the CPOL = CPHA = 0 protocol.

### I<sup>2</sup>C-Compatible Serial Interface

Use an I<sup>2</sup>C-compatible 2-wire serial interface with the MAX1799/MAX1799A to control the ON/OFF state and output voltage of each regulator, the ON/OFF state of the drivers, and to shut down the device. Use standard I<sup>2</sup>C-compatible write-byte commands to program the IC. Figure 2 is a timing diagram for the I<sup>2</sup>C protocol. The MAX1799/MAX1799A is always a slave to the bus master. The serial port operates when the device is enabled, even when OUT1 and RSO are low. When AS is high, the address is 0111111. When AS is low, the address is 1001111. Two MAX1799/MAX1799A devices can be controlled by a single bus master.

### **Output Voltage**

The MAX1798/MAX1798A/MAX1799/MAX1799A are supplied with factory-set output voltages. At power-up, all DACS are set for 2.98V, while only OUT1 is enabled; all other LDO outputs and drivers are off. OUT2–5, DR1, and DR2 must be enabled on with the serial port. OUT2–5 can be individually programmed through the serial port from 1.8V to 3.3V in 32 steps, either while on or off. OUT1 can be programmed in 32 steps from 1.8V to 3.3V only while on. (If OUT1 is off, the serial port is also off, and OUT1 cannot be programmed.) If OUT1 is turned off through the serial port or the  $\overline{OFF}$  pin, the entire chip, including the serial port, will be shut down. However, all previously programmed DAC settings will be retained as long as a valid supply voltage is maintained on IN1 (VIN1 > 2.1V).

### **Current Limit**

The MAX1798/MAX1798A/MAX1799/MAX1799A include current limiting on each LDO output. OUT1 has a current limit set at 500mA (320mA min), while OUT2–5 have current limits set at 250mA (160mA min). When the LDO output is in current limit, the current-limiter device monitors and controls the pass transistor's gate voltage, limiting the output current available from the LDO. Once the excessive load is removed, normal function resumes automatically.

# Table 2. OUT1–5 Output Voltages (Binary Format)

| REGULATOR<br>OUTPUT<br>VOLTAGE (V) | DAC_ DATA |    |    |    |    |  |  |  |  |  |  |

|------------------------------------|-----------|----|----|----|----|--|--|--|--|--|--|

| OUT1–<br>OUT5                      | D4        | D3 | D2 | D1 | D0 |  |  |  |  |  |  |

| 1.800                              | 0         | 0  | 0  | 0  | 0  |  |  |  |  |  |  |

| 1.827                              | 0         | 0  | 0  | 0  | 1  |  |  |  |  |  |  |

| 1.854                              | 0         | 0  | 0  | 1  | 0  |  |  |  |  |  |  |

| 1.883                              | 0         | 0  | 0  | 1  | 1  |  |  |  |  |  |  |

| 1.912                              | 0         | 0  | 1  | 0  | 0  |  |  |  |  |  |  |

| 1.942                              | 0         | 0  | 1  | 0  | 1  |  |  |  |  |  |  |

| 1.974                              | 0         | 0  | 1  | 1  | 0  |  |  |  |  |  |  |

| 2.006                              | 0         | 0  | 1  | 1  | 1  |  |  |  |  |  |  |

| 2.039                              | 0         | 1  | 0  | 0  | 0  |  |  |  |  |  |  |

| 2.074                              | 0         | 1  | 0  | 0  | 1  |  |  |  |  |  |  |

| 2.109                              | 0         | 1  | 0  | 1  | 0  |  |  |  |  |  |  |

| 2.146                              | 0         | 1  | 0  | 1  | 1  |  |  |  |  |  |  |

| 2.184                              | 0         | 1  | 1  | 0  | 0  |  |  |  |  |  |  |

| 2.224                              | 0         | 1  | 1  | 0  | 1  |  |  |  |  |  |  |

| 2.265                              | 0         | 1  | 1  | 1  | 0  |  |  |  |  |  |  |

| 2.308                              | 0         | 1  | 1  | 1  | 1  |  |  |  |  |  |  |

| 2.352                              | 1         | 0  | 0  | 0  | 0  |  |  |  |  |  |  |

| 2.398                              | 1         | 0  | 0  | 0  | 1  |  |  |  |  |  |  |

| 2.445                              | 1         | 0  | 0  | 1  | 0  |  |  |  |  |  |  |

| 2.495                              | 1         | 0  | 0  | 1  | 1  |  |  |  |  |  |  |

| 2.547                              | 1         | 0  | 1  | 0  | 0  |  |  |  |  |  |  |

| 2.601                              | 1         | 0  | 1  | 0  | 1  |  |  |  |  |  |  |

| 2.657                              | 1         | 0  | 1  | 1  | 0  |  |  |  |  |  |  |

| 2.716                              | 1         | 0  | 1  | 1  | 1  |  |  |  |  |  |  |

| 2.777                              | 1         | 1  | 0  | 0  | 0  |  |  |  |  |  |  |

| 2.842                              | 1         | 1  | 0  | 0  | 1  |  |  |  |  |  |  |

| 2.909                              | 1         | 1  | 0  | 1  | 0  |  |  |  |  |  |  |

| 2.980                              | 1         | 1  | 0  | 1  | 1  |  |  |  |  |  |  |

| 3.054                              | 1         | 1  | 1  | 0  | 0  |  |  |  |  |  |  |

| 3.132                              | 1         | 1  | 1  | 0  | 1  |  |  |  |  |  |  |

| 3.214                              | 1         | 1  | 1  | 1  | 0  |  |  |  |  |  |  |

| 3.300                              | 1         | 1  | 1  | 1  | 1  |  |  |  |  |  |  |

# Table 3. OUT1–5 Output Voltages (Hexadecimal Format)

| ·                                  |           |      |      |      |      |

|------------------------------------|-----------|------|------|------|------|

| REGULATOR<br>OUTPUT<br>VOLTAGE (V) | DAC_ DATA |      |      |      |      |

| OUT1–<br>OUT5                      | OUT5      | OUT4 | ОИТЗ | OUT2 | OUT1 |

| 1.800                              | AO        | 80   | 60   | 40   | 20   |

| 1.827                              | A1        | 81   | 61   | 41   | 21   |

| 1.854                              | A2        | 82   | 62   | 42   | 22   |

| 1.883                              | A3        | 83   | 63   | 43   | 23   |

| 1.912                              | A4        | 84   | 64   | 44   | 24   |

| 1.942                              | A5        | 85   | 65   | 45   | 25   |

| 1.974                              | A6        | 86   | 66   | 46   | 26   |

| 2.006                              | A7        | 87   | 67   | 47   | 27   |

| 2.039                              | A8        | 88   | 68   | 48   | 28   |

| 2.074                              | A9        | 89   | 69   | 49   | 29   |

| 2.109                              | AA        | 8A   | 6A   | 4A   | 2A   |

| 2.146                              | AB        | 8B   | 6B   | 4B   | 2B   |

| 2.184                              | AC        | 8C   | 6C   | 4C   | 2C   |

| 2.224                              | AD        | 8D   | 6D   | 4D   | 2D   |

| 2.265                              | AE        | 8E   | 6E   | 4E   | 2E   |

| 2.308                              | AF        | 8F   | 6F   | 4F   | 2F   |

| 2.352                              | B0        | 90   | 70   | 50   | 30   |

| 2.398                              | B1        | 91   | 71   | 51   | 31   |

| 2.445                              | B2        | 92   | 72   | 52   | 32   |

| 2.495                              | B3        | 93   | 73   | 53   | 33   |

| 2.547                              | B4        | 94   | 74   | 54   | 34   |

| 2.601                              | B5        | 95   | 75   | 55   | 35   |

| 2.657                              | B6        | 96   | 76   | 56   | 36   |

| 2.716                              | B7        | 97   | 77   | 57   | 37   |

| 2.777                              | B8        | 98   | 78   | 58   | 38   |

| 2.842                              | B9        | 99   | 79   | 59   | 39   |

| 2.909                              | BA        | 9A   | 7A   | 5A   | ЗA   |

| 2.980                              | BB        | 9B   | 7B   | 5B   | 3B   |

| 3.054                              | BC        | 9C   | 7C   | 5C   | 3C   |

| 3.132                              | BD        | 9D   | 7D   | 5D   | 3D   |

| 3.214                              | BE        | 9E   | 7E   | 5E   | ЗE   |

| 3.300                              | BF        | 9F   | 7F   | 5F   | ЗF   |

Figure 4a. Serial-Interface Timing Diagram

Figure 4b. Detailed Serial-Interface Timing Diagram

## **Thermal-Overload Protection**

The MAX1798/MAX1798A/MAX1799/MAX1799A integrate a separate thermal monitor for each linear regulator. When the junction temperature of any LDO exceeds  $T_J = +160^{\circ}$ C, the specific thermal sensor signals the shutdown logic, turning off the pass transistor and allowing that LDO to cool. The thermal sensor turns the pass transistor on again after the LDO's junction temperature cools by 10°C, resulting in a pulsed output during continuous thermal-overload conditions. Due to the substrate's thermal conductivity, a thermal overload on one LDO may possibly affect other LDOs on the device.

Thermal-overload protection is designed to protect the MAX1798/MAX1798A/MAX1799/MAX1799A in the event of fault conditions. For continual operation, do not exceed the absolute maximum junction-temperature rating of  $T_J = +150^{\circ}$ C.

### **Noise Reduction**

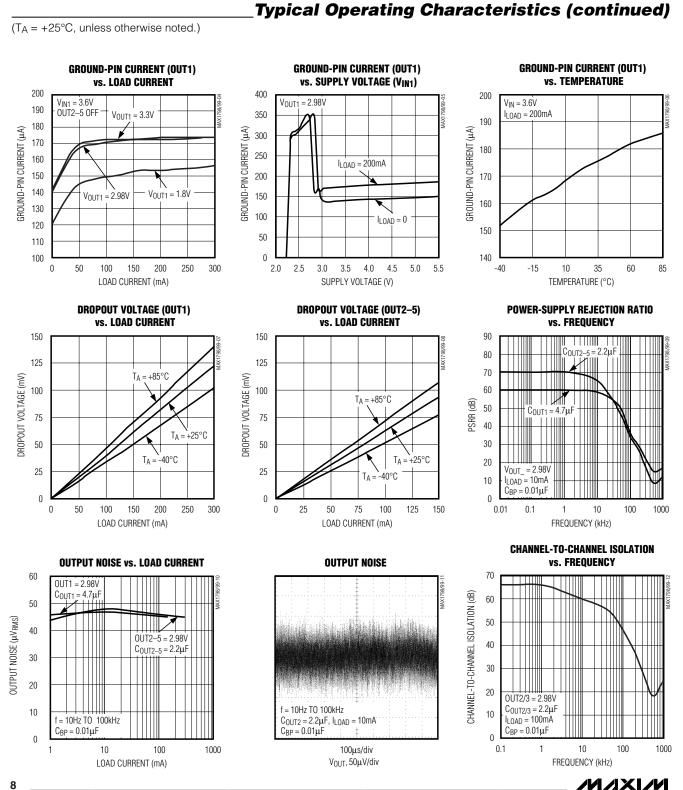

Bypass BP to GND with an external  $0.01\mu$ F bypass capacitor. The MAX1798/MAX1798A/MAX1799/MAX1799A exhibit  $45\mu$ V<sub>RMS</sub> of output voltage noise. Graphs of Output Noise vs. Load Current, Output Noise (10Hz to 100kHz), PSRR vs. Frequency, and Channel-to-Channel Isolation vs. Frequency appear in the *Typical Operating Characteristics*.

# **Applications Information**

### Capacitor Selection and Regulator Stability

Use a 10 $\mu$ F low-ESR ceramic capacitor on the MAX1798/MAX1798A/MAX1799/MAX1799A's input if all the supply inputs are connected together. Larger input capacitance and lower ESR provide better supply noise rejection and line-transient response. If IN1, IN2/3, and IN4/5 are connected to different supply voltages, bypass each input with a 4.7 $\mu$ F low-ESR ceramic capacitor.

A minimum 4.7 $\mu$ F low-ESR ceramic capacitor is recommended on OUT1, and a minimum 2.2 $\mu$ F low-ESR ceramic capacitor is recommended on OUT2–5. The MAX1798/MAX1798A/MAX1799/MAX1799A are stable with output capacitors in the ESR range of 10m $\Omega$  to 1 $\Omega$ . Use larger capacitors to reduce noise and improve load-transient response, stability, and power-supply rejection.

Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature. With dielectrics such as Z5U and Y5V, it may be necessary to use a minimum 4.7 $\mu$ F on OUT2–5 to ensure stability at temperatures below -10°C. With X7R or X5R dielectrics, 2.2 $\mu$ F should be sufficient at all operating temperatures. Tantalum capacitors may cause instability with the MAX1798/MAX1798A/MAX1799/MAX1799A and are not recommended for this application.

Use a  $0.01\mu$ F bypass capacitor at BP for low outputvoltage noise. Increasing the capacitance will slightly decrease the output noise but will increase the startup time. Values above  $0.1\mu$ F provide no performance advantage and are not recommended.

### **Line-Transient Considerations**

The MAX1798/MAX1798A/MAX1799/MAX1799A are designed to deliver low dropout voltages and low quiescent currents in battery-powered systems. Powersupply rejection is >60dB at low frequencies and rolls off above 10kHz. See the Power-Supply Rejection Ratio (PSRR) vs. Frequency graph in the *Typical Operating Characteristics*. When operating from sources other than batteries, improved supply noise rejection and transient response can be achieved by increasing the values of the input and output bypass capacitors and through passive filtering techniques. The *Typical Operating Characteristics* show the MAX1798/MAX1798A/MAX1799/ MAX1799A line- and load-transient responses.

### Load-Transient Considerations

The MAX1798/MAX1798A/MAX1799/MAX1799A loadtransient response graphs (see *Typical Operating Characteristics*) show three components of the output response: the output capacitor's ESR spike, the regulator's transient settling response, and the DC shift due to the LDO's load regulation. Increasing the output capacitor's value and decreasing the ESR reduce the overshoot.

### **Dropout Voltage**

A regulator's minimum input-output voltage differential (dropout voltage) determines the lowest usable supply voltage. In battery-powered systems, this determines the useful end-of-life battery voltage. Because the MAX1798/MAX1798A/MAX1799/MAX1799A use P-channel MOSFET pass transistors, their dropout voltage is a function of drain-to-source on-resistance (RDS(ON)) multiplied by the load current. See the Dropout Voltage (OUT1) vs. Load Current graph in the *Typical Operating Characteristics.*

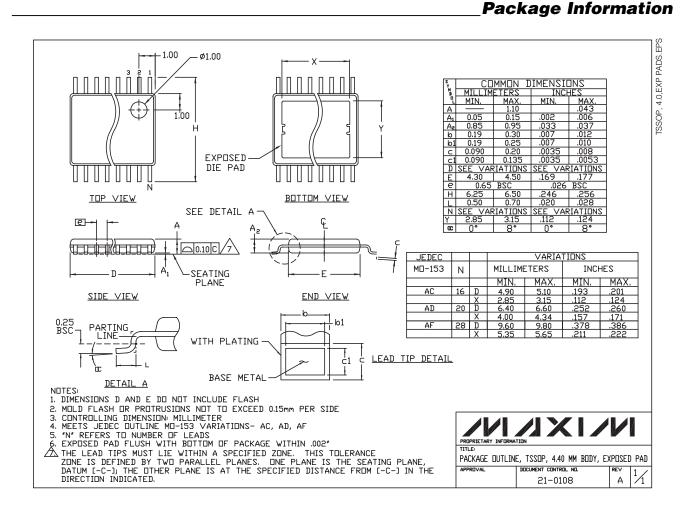

# Ordering Information (continued)

| PART        | TEMP<br>RANGE  | PIN-<br>PACKAGE | INTER-<br>FACE   |

|-------------|----------------|-----------------|------------------|

| MAX1799EGP  | -40°C to +85°C | 20 QFN          | I <sup>2</sup> C |

| MAX1799EUP  | -40°C to +85°C | 20 TSSOP-EP     | I <sup>2</sup> C |

| MAX1799AEGP | -40°C to +85°C | 20 QFN          | I <sup>2</sup> C |

| MAX1799AEUP | -40°C to +85°C | 20 TSSOP-EP     | I <sup>2</sup> C |

## Chip Information

TRANSISTOR COUNT: 1735

MAX1798/MAX1798A/MAX1799/MAX1799A

Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

20

21-0091