# MC68HC908GR16

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://motorola.com/semiconductors

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

**Revision History**

# **Revision History**

| Date              | Revision<br>Level | Description                                                                                         | Page<br>Number(s) |

|-------------------|-------------------|-----------------------------------------------------------------------------------------------------|-------------------|

| February,<br>2003 | N/A               | Initial release                                                                                     | N/A               |

|                   |                   | Reorganized to meet latest publication standards for M68HC08 Family documentation                   | N/A               |

| May,<br>2003      | 1.0               | Section 16. Serial Peripheral Interface (SPI) Module — Removed all references to DMAS               | 215               |

| 2003              |                   | Figure 4-2. CGM External Connections — Figure updated for consistency                               | 68                |

|                   |                   | Table 4-4. Example Filter Component Values — Table updated to reflect           new resistor values | 80                |

MOTOROLA

# **List of Sections**

| Section 1. General Description19                                      |

|-----------------------------------------------------------------------|

| Section 2. Memory                                                     |

| Section 3. Analog-to-Digital Converter (ADC)47                        |

| Section 4. Clock Generator Module (CGM)59                             |

| Section 5. Configuration Register (CONFIG)                            |

| Section 6. Computer Operating Properly (COP) Module                   |

| Section 7. Central Processor Unit (CPU)                               |

| Section 8. External Interrupt (IRQ)103                                |

| Section 9. Keyboard Interrupt Module (KBI)                            |

| Section 10. Low-Power Modes117                                        |

| Section 11. Low-Voltage Inhibit (LVI)125                              |

| Section 12. Input/Output Ports (PORTS)129                             |

| Section 13. Resets and Interrupts145                                  |

| Section 14. Enhanced Serial Communications<br>Interface (ESCI) Module |

| Section 15. System Integration Module (SIM)195                        |

| Section 16. Serial Peripheral Interface (SPI) Module215               |

| Section 17. Timebase Module (TBM)                                     |

| Section 18. Timer Interface Module (TIM)245                           |

| Section 19. Development Support                                       |

| Section 20. Electrical Specifications                                 |

| Section 21. Ordering Information<br>and Mechanical Specifications     |

**List of Sections**

Data Sheet

\_

# **Table of Contents**

## **Section 1. General Description**

| 1.1    | Introduction                                                                     | . 19 |

|--------|----------------------------------------------------------------------------------|------|

| 1.2    | Features                                                                         | . 19 |

| 1.2.1  | Standard Features of the MC68HC908GR16                                           | . 19 |

| 1.2.2  | Features of the CPU08                                                            | . 21 |

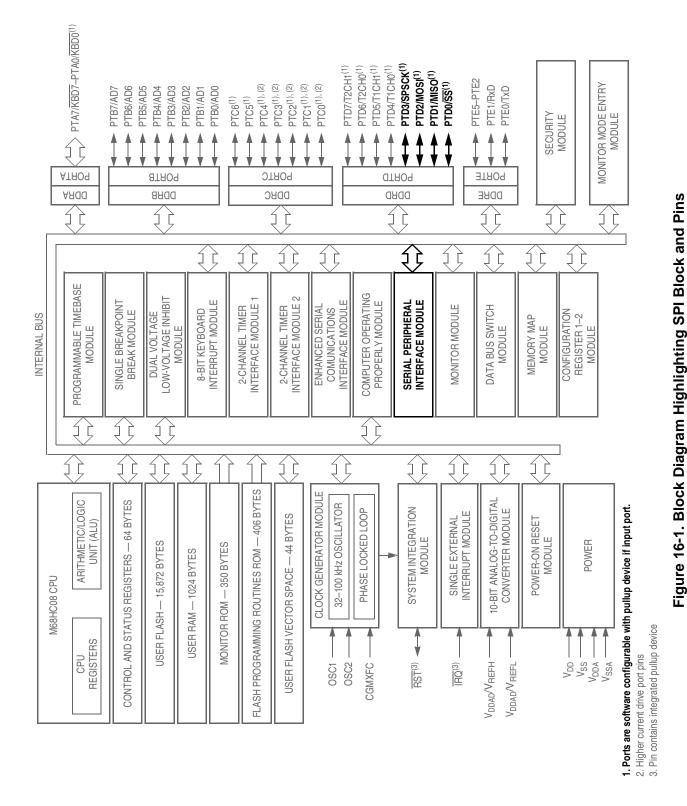

| 1.3    | MCU Block Diagram                                                                | . 21 |

| 1.4    | Pin Assignments.                                                                 | . 21 |

| 1.5    | Pin Functions                                                                    | . 24 |

| 1.5.1  | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                         | . 24 |

| 1.5.2  | Oscillator Pins (OSC1 and OSC2)                                                  | . 24 |

| 1.5.3  | External Reset Pin (RST)                                                         |      |

| 1.5.4  | External Interrupt Pin (IRQ)                                                     |      |

| 1.5.5  | CGM Power Supply Pins (V <sub>DDA</sub> and V <sub>SSA</sub> )                   |      |

| 1.5.6  | External Filter Capacitor Pin (V <sub>CGMXFC</sub> )                             | . 25 |

| 1.5.7  | ADC Power Supply/Reference Pins                                                  |      |

|        | (V <sub>DDAD</sub> /V <sub>REFH</sub> and V <sub>SSAD</sub> /V <sub>REFL</sub> ) | . 25 |

| 1.5.8  | Port A Input/Output (I/O) Pins (PTA7/KBD7–PTA0/KBD0)                             |      |

| 1.5.9  | Port B I/O Pins (PTB7/AD7–PTB0/AD0).                                             |      |

| 1.5.10 |                                                                                  | . 25 |

| 1.5.11 | Port D I/O Pins (PTD7/T2CH1–PTD0/SS)                                             |      |

| 1.5.12 | Port E I/O Pins (PTE5–PTE2, PTE1/RxD, and PTE0/TxD)                              | . 26 |

|        | Section 2. Memory                                                                |      |

| 2.1    | Introduction                                                                     | . 27 |

| 2.2    | Linimplemented Memory Leoptions                                                  |      |

|         | 111100000101111111111111111111111111111 |

|---------|-----------------------------------------|

| 2.2     | Unimplemented Memory Locations 27       |

| 2.3     | Reserved Memory Locations 27            |

| 2.4     | Input/Output (I/O) Section              |

| 2.5     | Random-Access Memory (RAM) 38           |

| 2.6     | FLASH Memory (FLASH)                    |

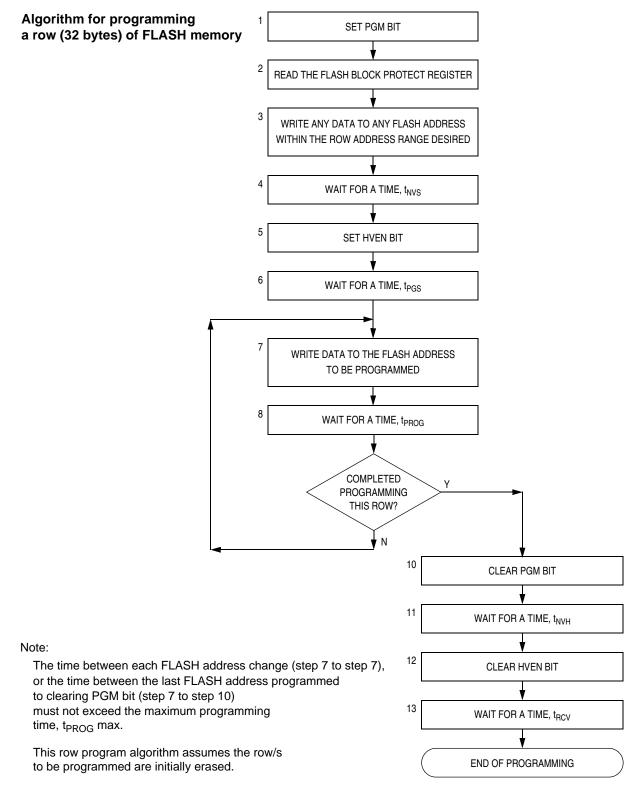

| 2.6.1   | Functional Description                  |

| 2.6.1.1 | FLASH Control Register                  |

| 2.6.1.2 | FLASH Page Erase Operation 40           |

| 2.6.1.3 | FLASH Mass Erase Operation 41           |

| 2.6.1.4 | FLASH Program/Read Operation            |

| 2.6.1.5 | FLASH Block Protection 44               |

| 2.6.1.6 | FLASH Block Protect Register 44         |

| 2.6.2   | Wait Mode                               |

| 2.6.3   | Stop Mode 46                            |

|         |                                         |

MC68HC908GR16 — Rev. 1.0

# Table of Contents

# Section 3. Analog-to-Digital Converter (ADC)

| 3.1     | Introduction                                        | 47 |

|---------|-----------------------------------------------------|----|

| 3.2     | Features                                            | 47 |

| 3.3     | Functional Description                              | 47 |

| 3.3.1   | ADC Port I/O Pins.                                  | 47 |

| 3.3.2   | Voltage Conversion                                  | 49 |

| 3.3.3   | Conversion Time                                     |    |

| 3.3.4   | Conversion                                          | 50 |

| 3.3.5   | Accuracy and Precision                              | 50 |

| 3.3.6   | Result Justification                                | 50 |

| 3.4     | Monotonicity                                        | 52 |

| 3.5     | Interrupts                                          | 52 |

| 3.6     | Low-Power Modes                                     | 52 |

| 3.6.1   | Wait Mode                                           |    |

| 3.6.2   | Stop Mode                                           | 52 |

| 3.7     | I/O Signals                                         | 52 |

| 3.7.1   | ADC Analog Power Pin (V <sub>DDAD</sub> )           |    |

| 3.7.2   | ADC Analog Ground Pin (V <sub>SSAD</sub> )          |    |

| 3.7.3   | ADC Voltage Reference High Pin (V <sub>REFH</sub> ) |    |

| 3.7.4   | ADC Voltage Reference Low Pin (V <sub>REFL</sub> )  |    |

| 3.7.5   | ADC Voltage In (V <sub>ADIN</sub> )                 |    |

| 3.8     | I/O Registers                                       | 53 |

| 3.8.1   | ADC Status and Control Register                     | 54 |

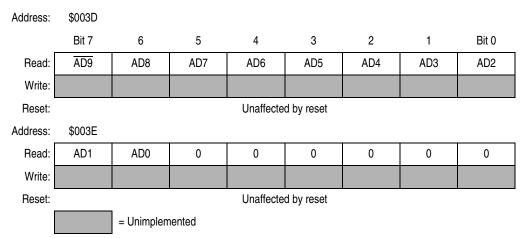

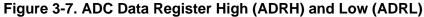

| 3.8.2   | ADC Data Register High and Data Register Low        | 55 |

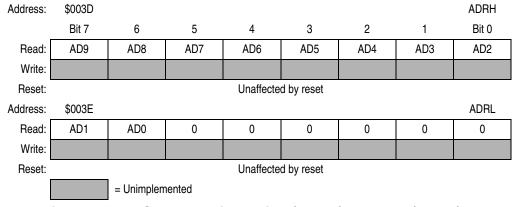

| 3.8.2.1 | Left Justified Mode                                 | 55 |

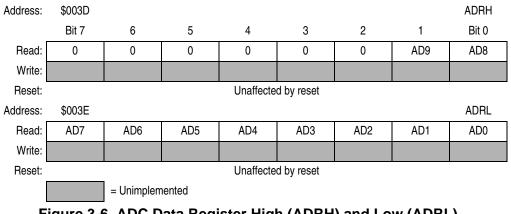

| 3.8.2.2 | Right Justified Mode                                | 56 |

| 3.8.2.3 | Left Justified Signed Data Mode                     | 56 |

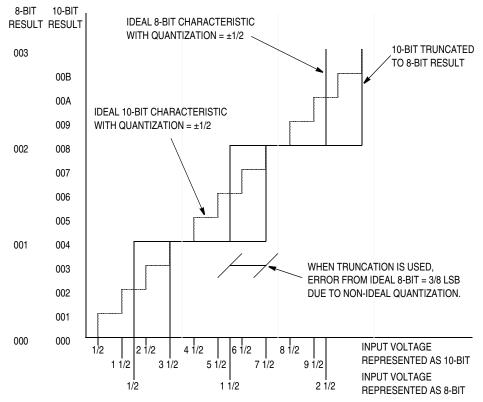

| 3.8.2.4 | Eight Bit Truncation Mode                           | 57 |

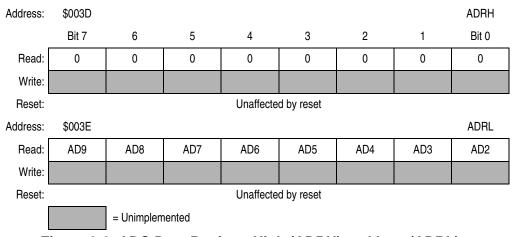

| 3.8.3   | ADC Clock Register 8                                | 57 |

|         |                                                     |    |

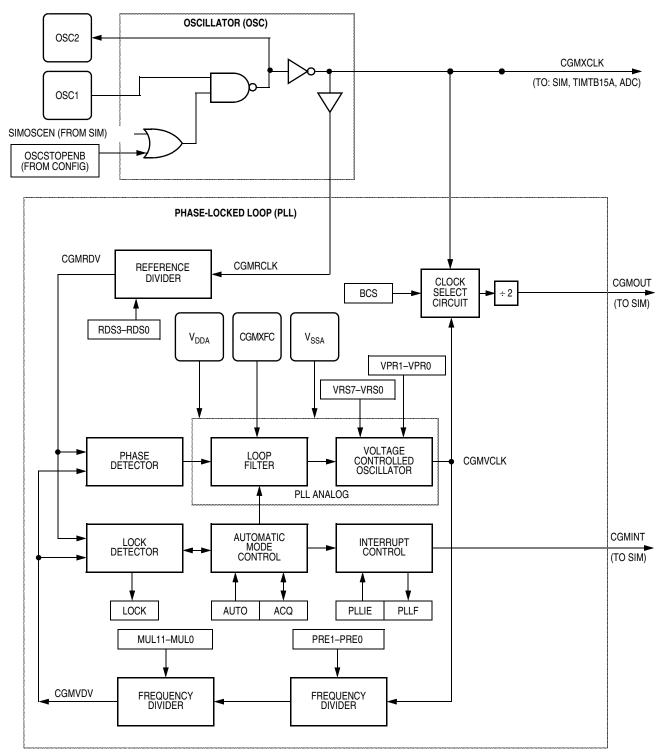

# Section 4. Clock Generator Module (CGM)

| 4.1   | Introduction                             |

|-------|------------------------------------------|

| 4.2   | Features                                 |

| 4.3   | Functional Description 59                |

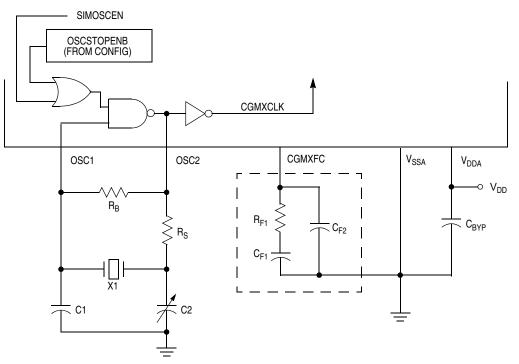

| 4.3.1 | Crystal Oscillator Circuit 61            |

| 4.3.2 | Phase-Locked Loop Circuit (PLL)          |

| 4.3.3 | PLL Circuits                             |

| 4.3.4 | Acquisition and Tracking Modes           |

| 4.3.5 | Manual and Automatic PLL Bandwidth Modes |

| 4.3.6 | Programming the PLL 64                   |

| 4.3.7 | Special Programming Exceptions           |

| 4.3.8 | Base Clock Selector Circuit 67           |

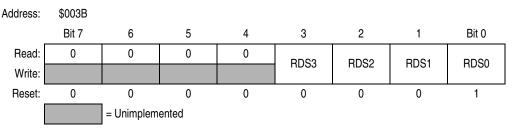

| 4.3.9 | CGM External Connections 67              |

|       |                                          |

Table of Contents

| 4.4    | I/O Signals                                         | 69        |

|--------|-----------------------------------------------------|-----------|

| 4.4.1  | Crystal Amplifier Input Pin (OSC1)                  | 69        |

| 4.4.2  | Crystal Amplifier Output Pin (OSC2)                 |           |

| 4.4.3  | External Filter Capacitor Pin (CGMXFC)              | 69        |

| 4.4.4  | PLL Analog Power Pin (V <sub>DDA</sub> )            |           |

| 4.4.5  | PLL Analog Ground Pin (V <sub>SSA</sub> )           | <b>69</b> |

| 4.4.6  | Oscillator Enable Signal (SIMOSCEN)                 |           |

| 4.4.7  | Oscillator Stop Mode Enable Bit (OSCSTOPENB)        |           |

| 4.4.8  | Crystal Output Frequency Signal (CGMXCLK)           |           |

| 4.4.9  | CGM Base Clock Output (CGMOUT)                      |           |

| 4.4.10 | CGM CPU Interrupt (CGMINT)                          |           |

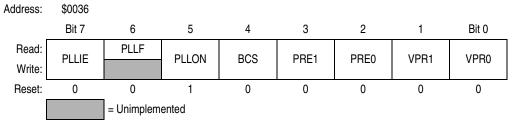

| 4.5    | CGM Registers                                       |           |

| 4.5.1  | PLL Control Register                                |           |

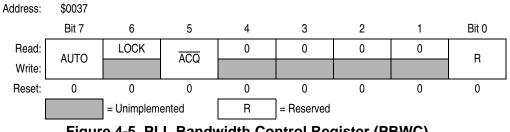

| 4.5.2  | PLL Bandwidth Control Register                      |           |

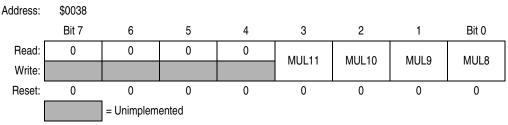

| 4.5.3  | PLL Multiplier Select Register High                 |           |

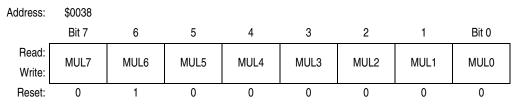

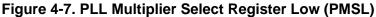

| 4.5.4  | PLL Multiplier Select Register Low                  |           |

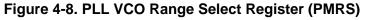

| 4.5.5  | PLL VCO Range Select Register                       |           |

| 4.5.6  | PLL Reference Divider Select Register               | 76        |

| 4.6    | Interrupts                                          | 76        |

| 4.7    | Special Modes                                       | 77        |

| 4.7.1  | Wait Mode                                           | 77        |

| 4.7.2  | Stop Mode                                           | 77        |

| 4.7.3  | CGM During Break Interrupts                         | 78        |

| 4.8    | Acquisition/Lock Time Specifications                | 78        |

| 4.8.1  | Acquisition/Lock Time Definitions                   | 78        |

| 4.8.2  | Parametric Influences on Reaction Time              | 79        |

| 4.8.3  | Choosing a Filter.                                  | 80        |

|        |                                                     |           |

|        | Section 5. Configuration Register (CONFIG)          |           |

| 5.1    | Introduction                                        | 81        |

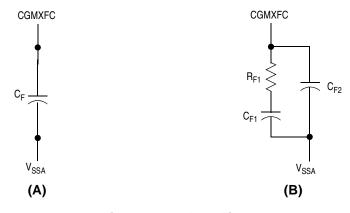

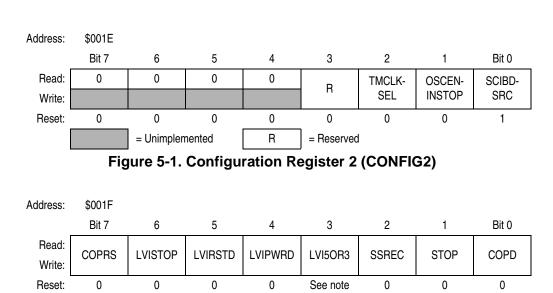

| 5.2    | Functional Description                              | 81        |

|        |                                                     |           |

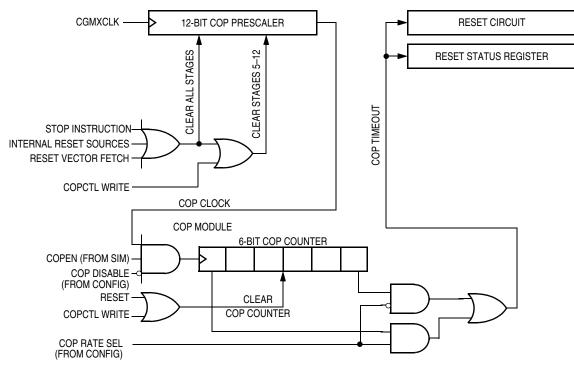

|        | Section 6. Computer Operating Properly (COP) Module |           |

| 6.1    | Introduction                                        | 85        |

| 6.2    | Functional Description                              | 85        |

| 6.3    | I/O Signals                                         | 86        |

| 6.3.1  | СĞМХСЬК                                             |           |

| 6.3.2  | STOP Instruction                                    |           |

| 6.3.3  | COPCTL Write                                        |           |

| 6.3.4  | Power-On Reset                                      | 86        |

| 6.3.5  | Internal Reset                                      | 87        |

| 6.3.6  | Reset Vector Fetch                                  | 87        |

| 6.3.7  | COPD (COP Disable)                                  | 87        |

| 6.3.8  | COPRS (COP Rate Select)                             | 87        |

| 6.4    | COP Control Register                                | 87        |

|        |                                                     |           |

# Table of Contents

| 6.5   | Interrupts                              | 87 |

|-------|-----------------------------------------|----|

| 6.6   | Monitor Mode                            | 87 |

| 6.7   | Low-Power Modes                         |    |

| 6.7.1 | Wait Mode                               | 88 |

| 6.7.2 | Stop Mode                               | 88 |

| 6.8   | COP Module During Break Mode            | 88 |

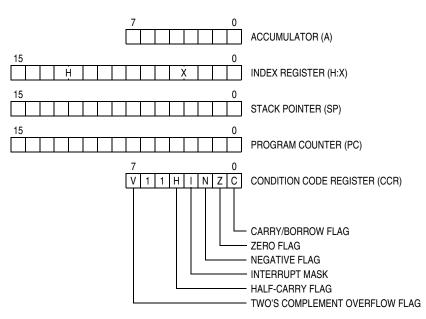

|       | Section 7. Central Processor Unit (CPU) |    |

| 7.1   | Introduction                            | 89 |

| 7.2   | Features                                | 89 |

| 73    | CPU Registers                           | 90 |

| 7.3   | CPU Registers                  |

|-------|--------------------------------|

| 7.3.1 | Accumulator                    |

| 7.3.2 | Index Register                 |

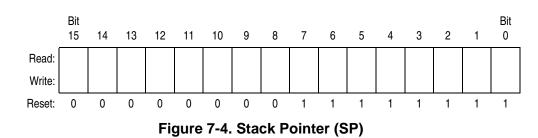

| 7.3.3 | Stack Pointer                  |

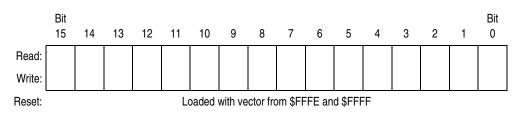

| 7.3.4 | Program Counter                |

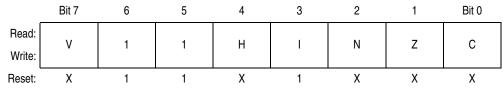

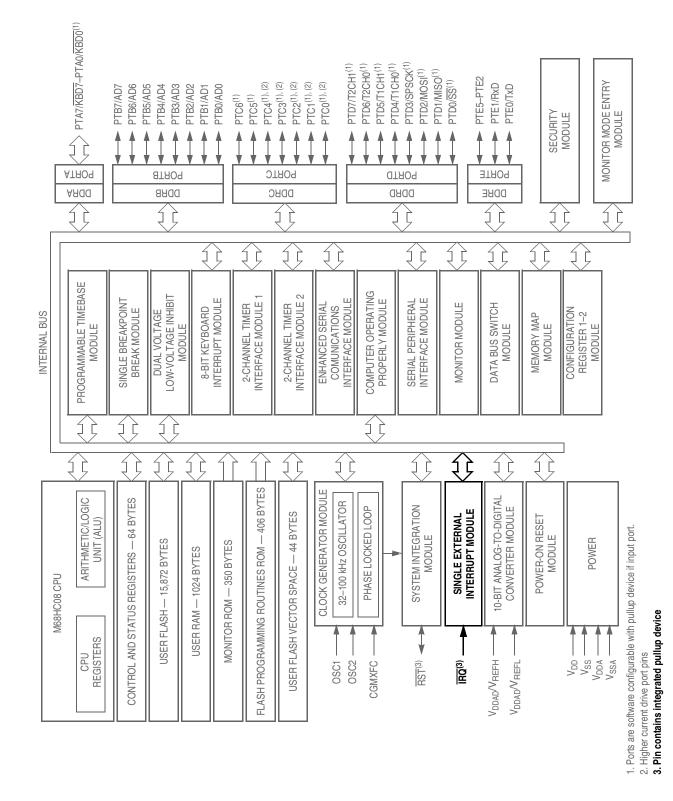

| 7.3.5 | Condition Code Register        |

| 7.4   | Arithmetic/Logic Unit (ALU) 93 |

| 7.5   | Low-Power Modes                |

| 7.5.1 | Wait Mode                      |

| 7.5.2 | Stop Mode                      |

| 7.6   | CPU During Break Interrupts    |

| 7.7   | Instruction Set Summary        |

| 7.8   | Opcode Map 101                 |

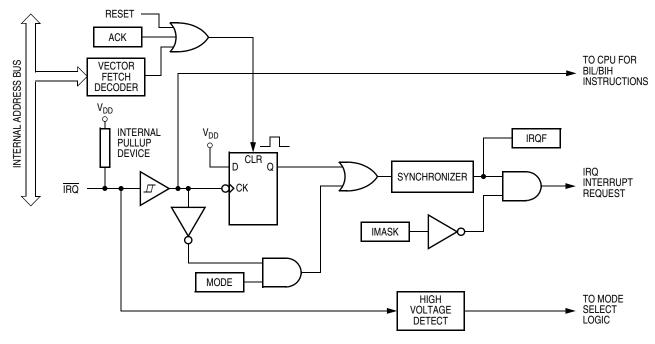

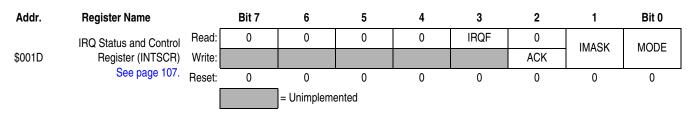

## Section 8. External Interrupt (IRQ)

| 8.1 | Introduction                          | 3 |

|-----|---------------------------------------|---|

| 8.2 | Features                              | 3 |

| 8.3 | Functional Description 10             | 3 |

| 8.4 | IRQ Pin                               | 6 |

| 8.5 | IRQ Module During Break Interrupts 10 | 6 |

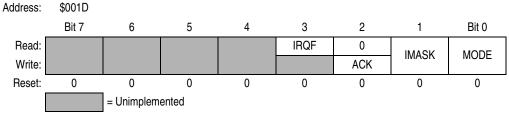

| 8.6 | IRQ Status and Control Register 10    | 7 |

## Section 9. Keyboard Interrupt Module (KBI)

| 9.1   | Introduction                            |

|-------|-----------------------------------------|

| 9.2   | Features                                |

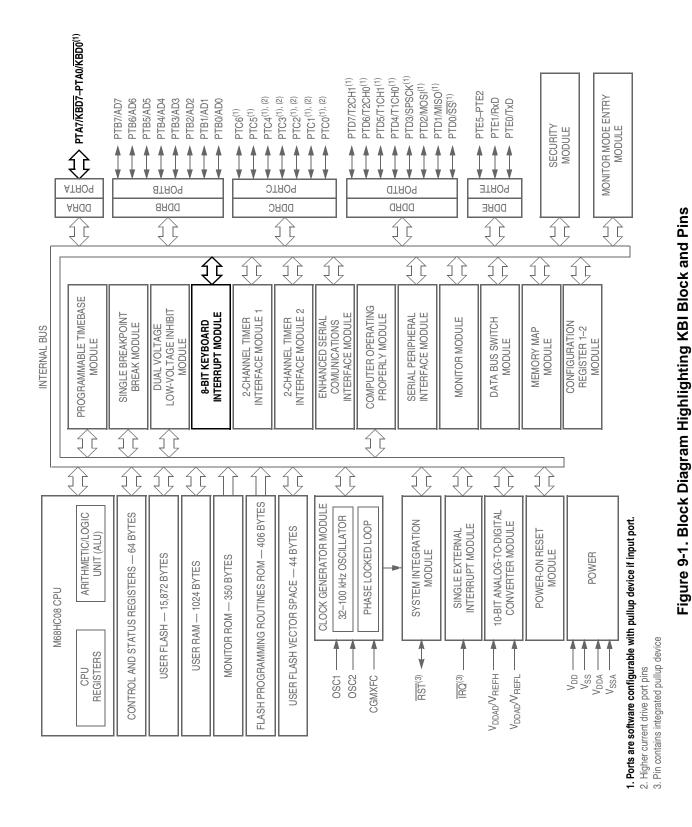

| 9.3   | Functional Description 109              |

| 9.4   | Keyboard Initialization 112             |

| 9.5   | Low-Power Modes                         |

| 9.5.1 | Wait Mode                               |

| 9.5.2 | Stop Mode                               |

| 9.6   | Keyboard Module During Break Interrupts |

Table of Contents

| 9.7     | I/O Registers                                          | 114 |

|---------|--------------------------------------------------------|-----|

| 9.7.1   | Keyboard Status and Control Register                   | 114 |

| 9.7.2   | Keyboard Interrupt Enable Register                     | 115 |

|         | Section 10. Low-Power Modes                            |     |

| 10.1    | Introduction                                           | 117 |

| 10.1.1  | Wait Mode.                                             |     |

| 10.1.2  | Stop Mode                                              |     |

| 10.2    | Analog-to-Digital Converter (ADC)                      |     |

| 10.2.1  | Wait Mode.                                             |     |

| 10.2.2  | Stop Mode                                              |     |

| 10.3    | Break Module (BRK)                                     |     |

| 10.3.1  | Wait Mode.                                             |     |

| 10.3.2  | Stop Mode                                              |     |

| 10.4    | Central Processor Unit (CPU)                           |     |

| 10.4.1  | Wait Mode.                                             |     |

| 10.4.2  | Stop Mode                                              |     |

| 10.5    | Clock Generator Module (CGM)                           |     |

| 10.5.1  | Wait Mode.                                             |     |

| 10.5.2  | Stop Mode                                              | 119 |

| 10.6    | Computer Operating Properly Module (COP)               | 119 |

| 10.6.1  | Wait Mode.                                             |     |

| 10.6.2  | Stop Mode                                              | 119 |

| 10.7    | External Interrupt Module (IRQ)                        | 119 |

| 10.7.1  | Wait Mode                                              |     |

| 10.7.2  | Stop Mode                                              |     |

| 10.8    | Keyboard Interrupt Module (KBI)                        |     |

| 10.8.1  | Wait Mode.                                             |     |

| 10.8.2  | Stop Mode                                              |     |

| 10.9    | Low-Voltage Inhibit Module (LVI)                       |     |

| 10.9.1  | Wait Mode                                              |     |

| 10.9.2  | Stop Mode                                              |     |

|         | Enhanced Serial Communications Interface Module (ESCI) |     |

| 10.10.1 |                                                        |     |

| 10.10.2 |                                                        |     |

|         | Serial Peripheral Interface Module (SPI)               |     |

| 10.11.  |                                                        |     |

| 10.11.2 |                                                        |     |

|         | Timer Interface Module (TIM1 and TIM2)                 |     |

| 10.12.  |                                                        |     |

|         | Timebase Module (TBM)                                  |     |

| 10.13   |                                                        |     |

| 10.13.  |                                                        |     |

|         |                                                        |     |

MC68HC908GR16 — Rev. 1.0

# Table of Contents

| 10.14 | Exiting Wait Mode | 122 |

|-------|-------------------|-----|

| 10.15 | Exiting Stop Mode | 123 |

## Section 11. Low-Voltage Inhibit (LVI)

| 11.1   | Introduction           | 125 |

|--------|------------------------|-----|

| 11.2   | Features               | 125 |

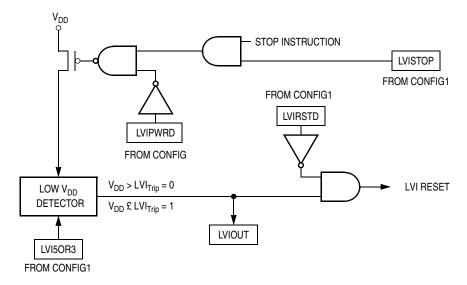

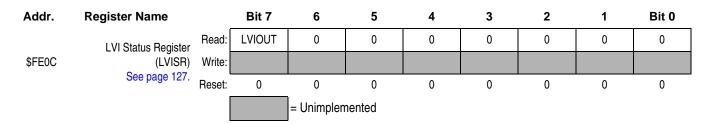

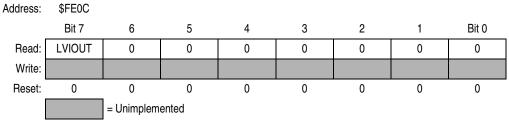

| 11.3   | Functional Description | 125 |

| 11.3.1 | Polled LVI Operation.  |     |

| 11.3.2 | Forced Reset Operation | 127 |

| 11.3.3 |                        | 127 |

| 11.3.4 | LVI Trip Selection     | 127 |

| 11.4   | LVI Status Register    | 127 |

| 11.5   | LVI Interrupts         | 128 |

| 11.6   | Low-Power Modes        | 128 |

| 11.6.1 | Wait Mode              | 128 |

| 11.6.2 | Stop Mode              | 128 |

## Section 12. Input/Output Ports (PORTS)

| 12.1   | Introduction                            |

|--------|-----------------------------------------|

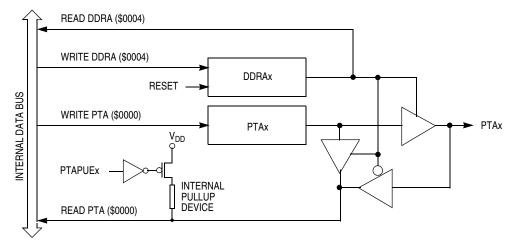

| 12.2   | Port A                                  |

| 12.2.1 | Port A Data Register 132                |

| 12.2.2 | Data Direction Register A 132           |

| 12.2.3 | Port A Input Pullup Enable Register     |

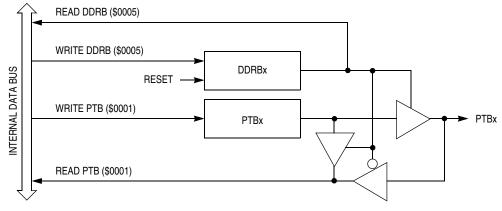

| 12.3   | Port B                                  |

| 12.3.1 | Port B Data Register 134                |

| 12.3.2 | Data Direction Register B 135           |

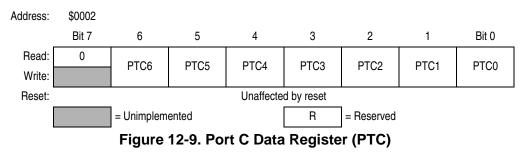

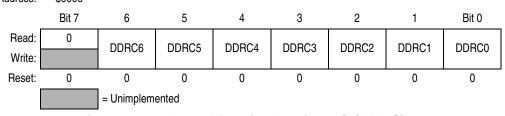

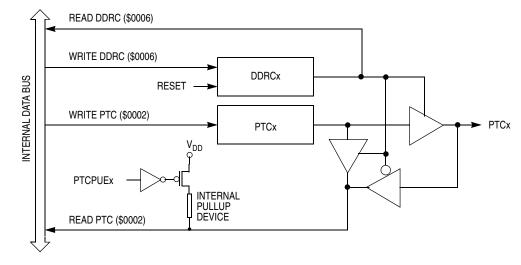

| 12.4   | Port C                                  |

| 12.4.1 | Port C Data Register 136                |

| 12.4.2 | Data Direction Register C 136           |

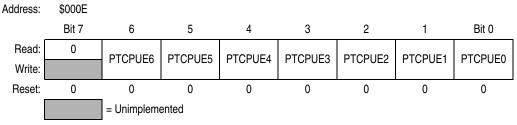

| 12.4.3 | Port C Input Pullup Enable Register     |

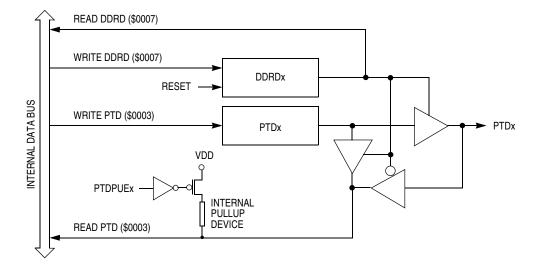

| 12.5   | Port D                                  |

| 12.5.1 | Port D Data Register 138                |

| 12.5.2 | Data Direction Register D 139           |

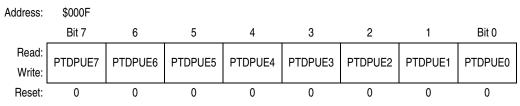

| 12.5.3 | Port D Input Pullup Enable Register 141 |

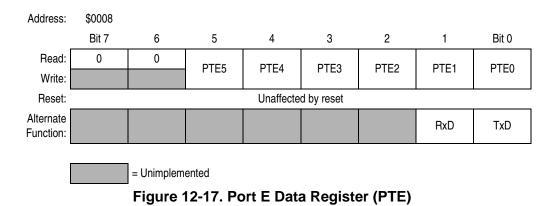

| 12.6   | Port E                                  |

| 12.6.1 | Port E Data Register 141                |

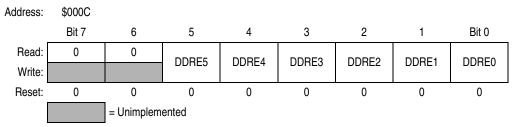

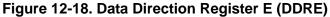

| 12.6.2 | Data Direction Register E 142           |

|        |                                         |

#### **Section 13. Resets and Interrupts**

| 13.1   |                | 145 |

|--------|----------------|-----|

| 13.2   | Resets         | 145 |

| 13.2.1 | Effects        | 145 |

| 13.2.2 | External Reset | 145 |

| 13.2.3 | Internal Reset | 145 |

|        |                |     |

Table of Contents

| 13.2.3.1  | Power-On Reset (POR) 146                                  |

|-----------|-----------------------------------------------------------|

| 13.2.3.2  | Computer Operating Properly (COP) Reset 146               |

| 13.2.3.3  | Low-Voltage Inhibit (LVI) Reset 147                       |

| 13.2.3.4  | Illegal Opcode Reset 147                                  |

| 13.2.3.5  | Illegal Address Reset 147                                 |

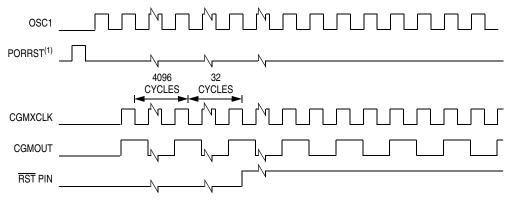

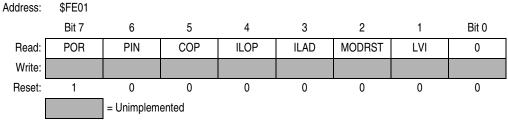

| 13.2.4    | System Integration Module (SIM) Reset Status Register 147 |

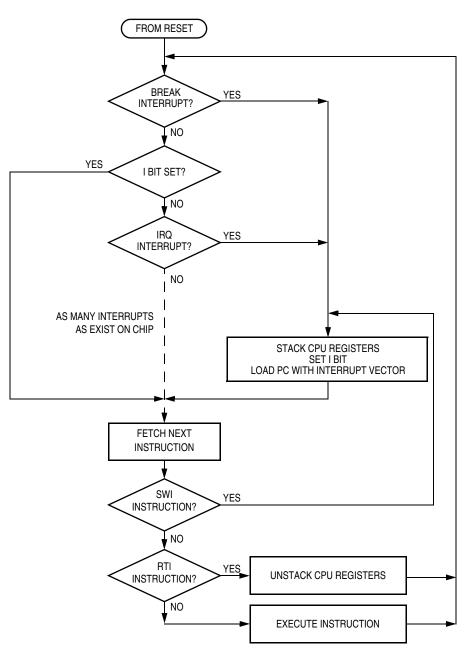

| 13.3 Int  | errupts                                                   |

| 13.3.1    | Effects                                                   |

| 13.3.2    | Sources                                                   |

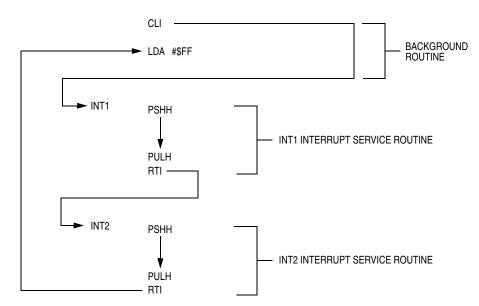

| 13.3.2.1  | Software Interrupt (SWI) Instruction 152                  |

| 13.3.2.2  | Break Interrupt 153                                       |

| 13.3.2.3  | IRQ Pin                                                   |

| 13.3.2.4  | Clock Generator (CGM) 153                                 |

| 13.3.2.5  | Timer Interface Module 1 (TIM1) 153                       |

| 13.3.2.6  | Timer Interface Module 2 (TIM2) 153                       |

| 13.3.2.7  | Serial Peripheral Interface (SPI) 154                     |

| 13.3.2.8  | Serial Communications Interface (SCI) 154                 |

| 13.3.2.9  | KBD0–KBD7 Pins 155                                        |

| 13.3.2.10 | Analog-to-Digital Converter (ADC) 155                     |

| 13.3.2.11 | Timebase Module (TBM) 155                                 |

| 13.3.3    | Interrupt Status Registers 155                            |

| 13.3.3.1  | Interrupt Status Register 1 156                           |

| 13.3.3.2  | Interrupt Status Register 2 157                           |

| 13.3.3.3  | Interrupt Status Register 3 157                           |

|           |                                                           |

#### Section 14. Enhanced Serial Communications Interface (ESCI) Module

| 14.1    | Introduction                      |

|---------|-----------------------------------|

| 14.2    | Features                          |

| 14.3    | Pin Name Conventions              |

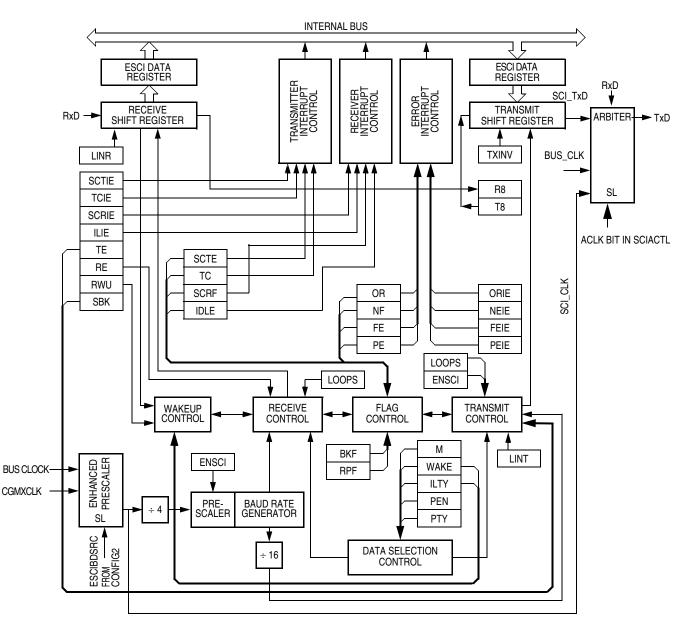

| 14.4    | Functional Description            |

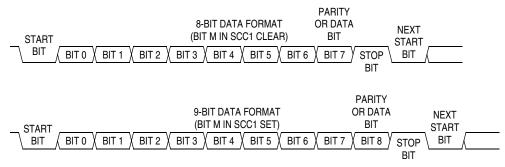

| 14.4.1  | Data Format                       |

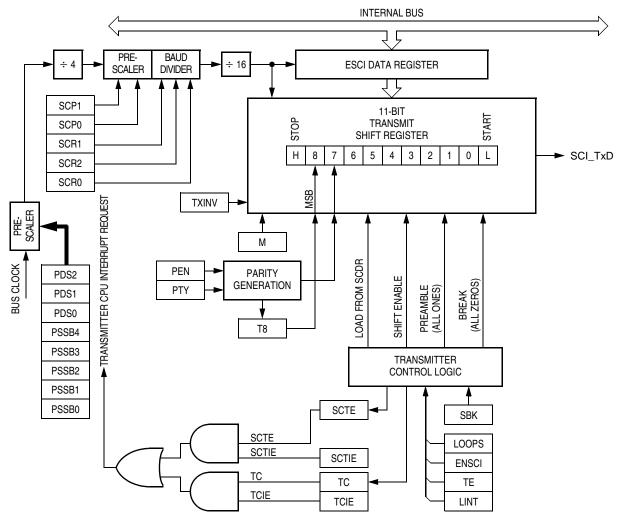

| 14.4.2  | Transmitter                       |

| 14.4.2. | 1 Character Length                |

| 14.4.2. | 2 Character Transmission          |

| 14.4.2. | 3 Break Characters 166            |

| 14.4.2. | 4 Idle Characters                 |

| 14.4.2. | 5 Inversion of Transmitted Output |

| 14.4.2. | 6 Transmitter Interrupts 167      |

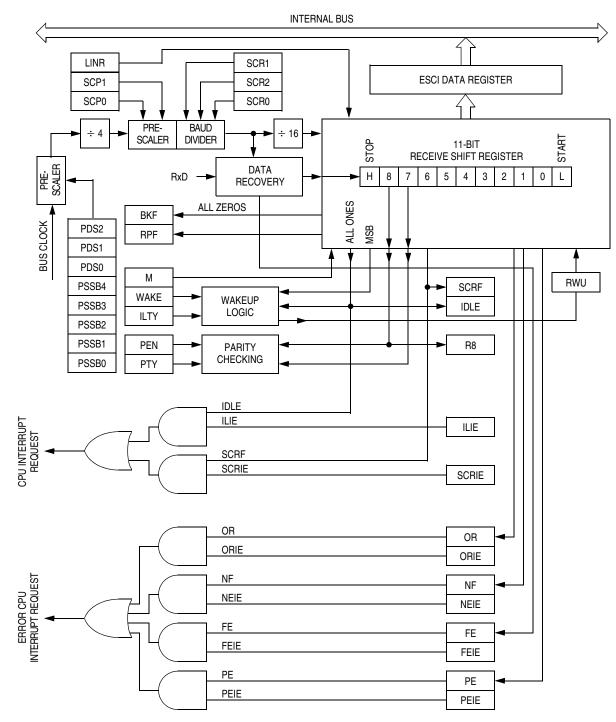

| 14.4.3  | Receiver                          |

| 14.4.3. | 1 Character Length                |

| 14.4.3. | 2 Character Reception 169         |

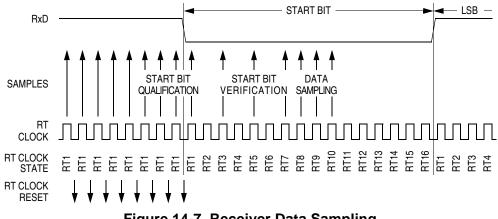

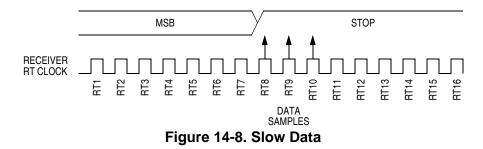

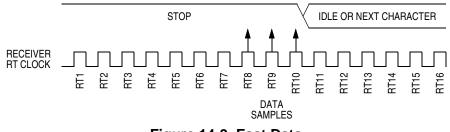

| 14.4.3. | 3 Data Sampling                   |

| 14.4.3. | 4 Framing Errors                  |

| 14.4.3. | 5 Baud Rate Tolerance 171         |

| 14.4.3. | 6 Receiver Wakeup 173             |

#### MC68HC908GR16 — Rev. 1.0

# Table of Contents

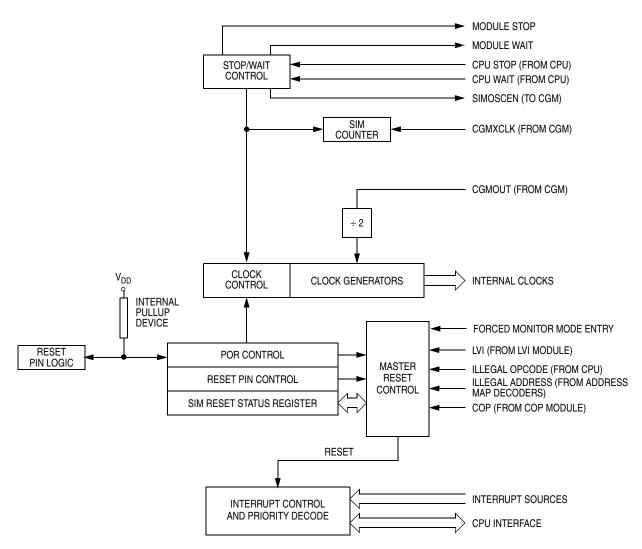

## Section 15. System Integration Module (SIM)

| 15.1    | Introduction                                   |

|---------|------------------------------------------------|

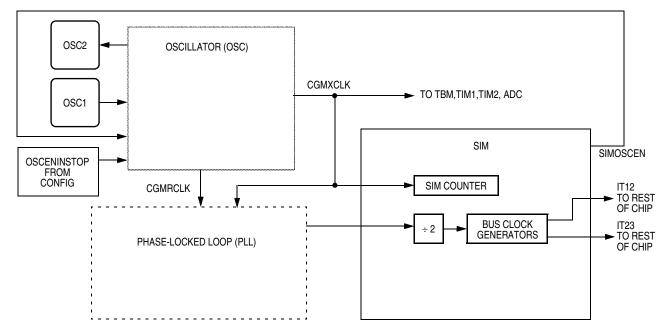

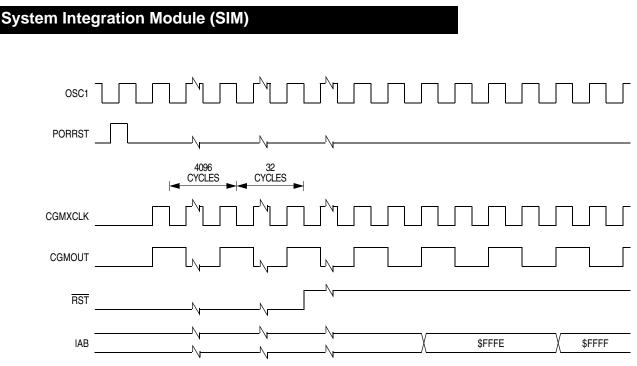

| 15.2    | SIM Bus Clock Control and Generation 198       |

| 15.2.1  | Bus Timing                                     |

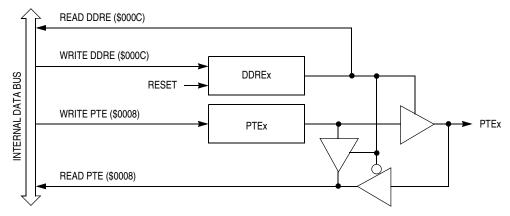

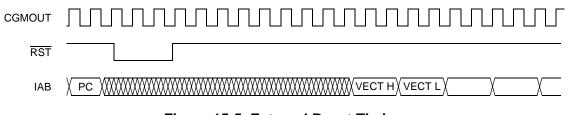

| 15.2.2  | Clock Startup from POR or LVI Reset 198        |

| 15.2.3  | Clocks in Stop Mode and Wait Mode 199          |

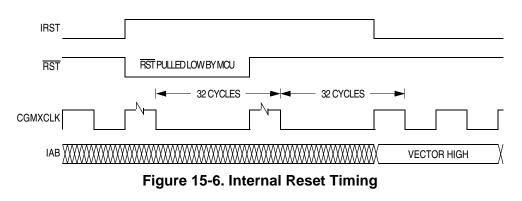

| 15.3    | Reset and System Initialization 199            |

| 15.3.1  | External Pin Reset 200                         |

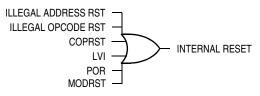

| 15.3.2  | Active Resets from Internal Sources            |

| 15.3.2. |                                                |

| 15.3.2. |                                                |

| 15.3.2. |                                                |

| 15.3.2. |                                                |

| 15.3.2. |                                                |

| 15.3.2. | 6 Monitor Mode Entry Module Reset (MODRST) 203 |

| 15.4    | SIM Counter                                    |

| 15.4.1  | SIM Counter During Power-On Reset              |

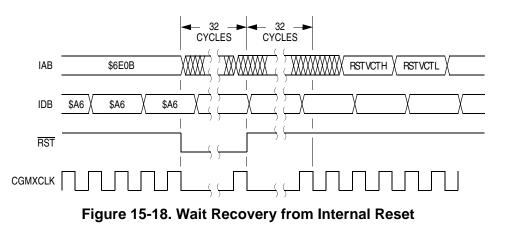

| 15.4.2  | SIM Counter During Stop Mode Recovery          |

| 15.4.3  | SIM Counter and Reset States                   |

|         |                                                |

Data Sheet

Table of Contents

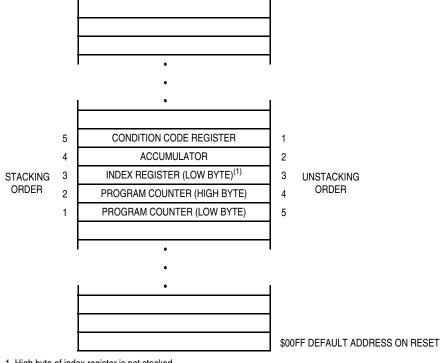

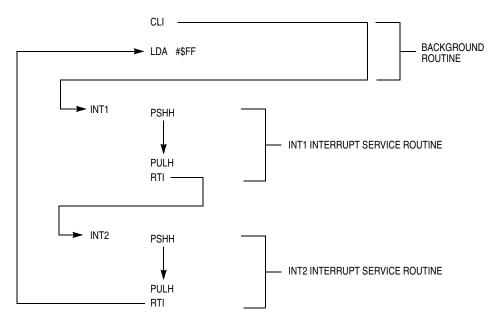

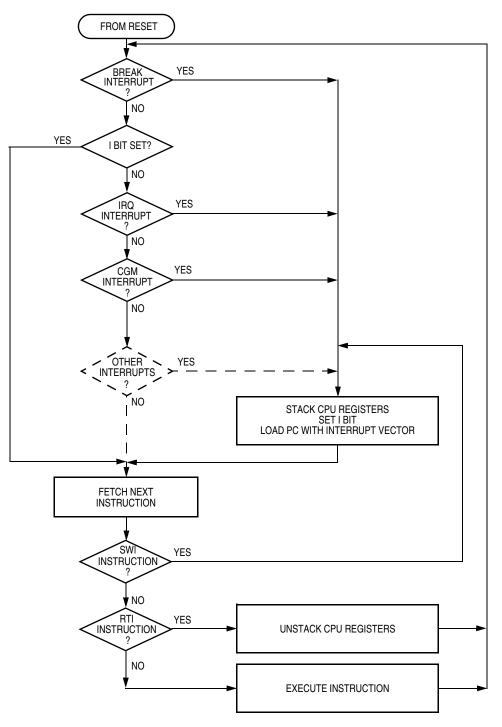

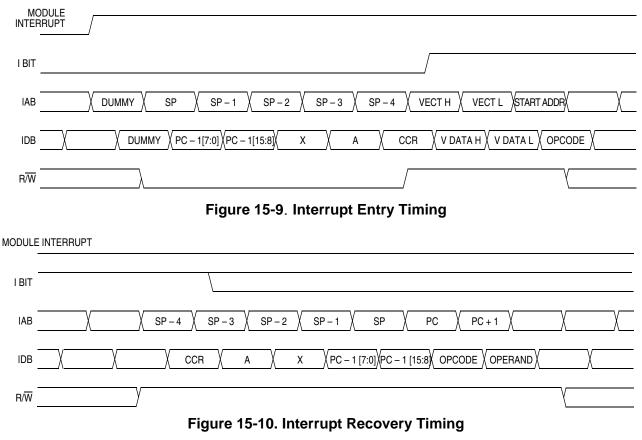

| 15.5.1       Interrupts.       204         15.5.1.1       Hardware Interrupts       206         15.5.1.2       SWI Instruction       207         15.5.1.3       Interrupt Status Registers       207         15.5.2       Reset       209         15.5.3       Break Interrupts       209 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.5.1.1         Hardware Interrupts         206           15.5.1.2         SWI Instruction         207           15.5.1.3         Interrupt Status Registers         207           15.5.2         Reset         209                                                                      |

| 15.5.1.3         Interrupt Status Registers         207           15.5.2         Reset         209                                                                                                                                                                                        |

| 15.5.2 Reset                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                           |

| 15.5.3 Break Interrupts                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                           |

| 15.5.4 Status Flag Protection in Break Mode 209                                                                                                                                                                                                                                           |

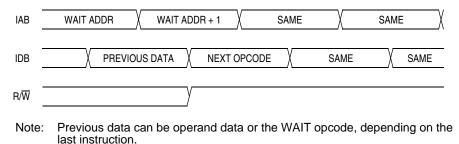

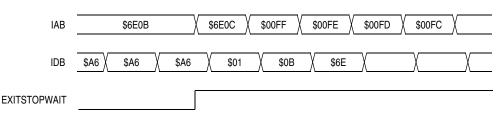

| 15.6 Low-Power Modes                                                                                                                                                                                                                                                                      |

| 15.6.1 Wait Mode 209                                                                                                                                                                                                                                                                      |

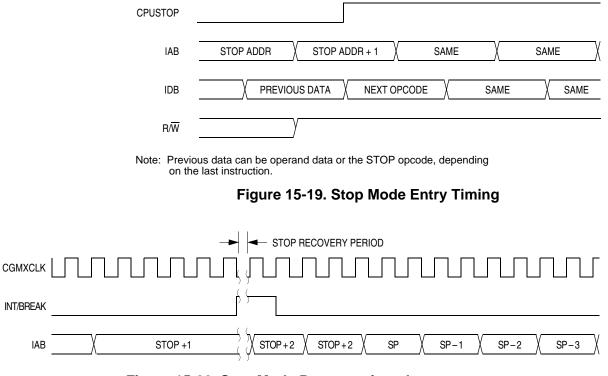

| 15.6.2 Stop Mode 211                                                                                                                                                                                                                                                                      |

| 15.7 SIM Registers                                                                                                                                                                                                                                                                        |

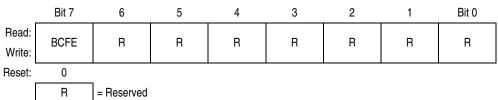

| 15.7.1 Break Status Register                                                                                                                                                                                                                                                              |

| 15.7.2 SIM Reset Status Register                                                                                                                                                                                                                                                          |

| 15.7.3 Break Flag Control Register 214                                                                                                                                                                                                                                                    |

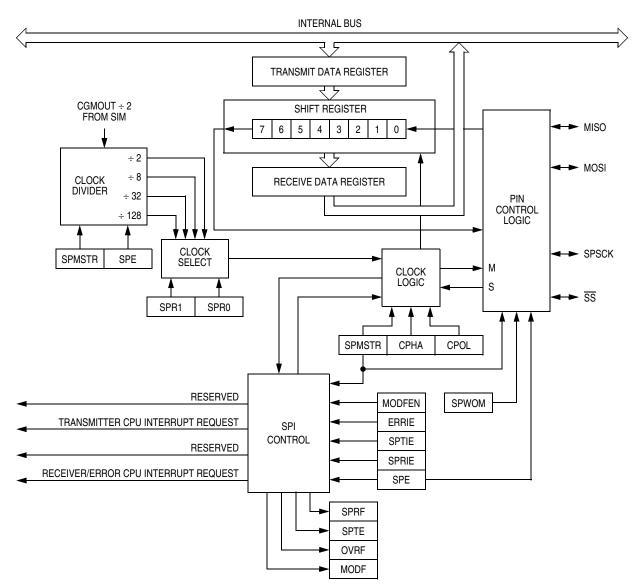

## Section 16. Serial Peripheral Interface (SPI) Module

| 16.1    | Introduction                      | 215 |

|---------|-----------------------------------|-----|

| 16.2    | Features                          | 215 |

| 16.3    | Pin Name Conventions.             | 217 |

| 16.4    | Functional Description            | 217 |

| 16.4.1  | Master Mode.                      |     |

| 16.4.2  | Slave Mode                        |     |

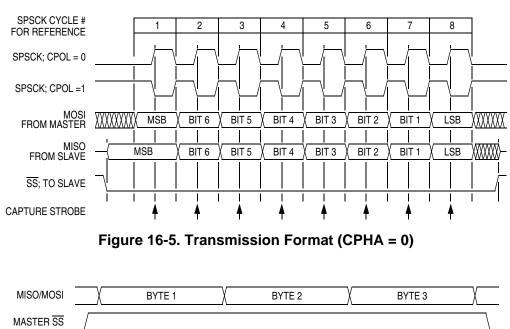

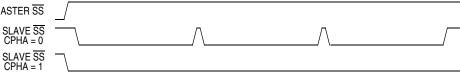

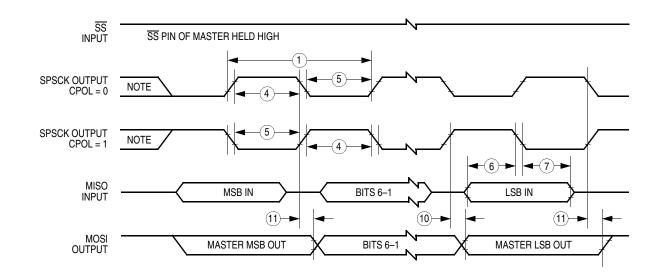

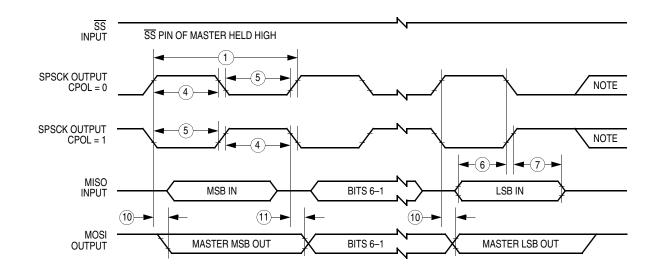

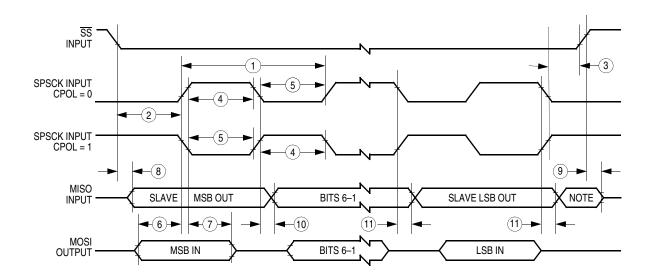

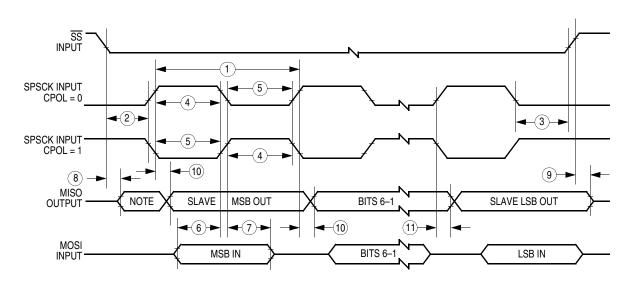

| 16.5    | Transmission Formats              | 220 |

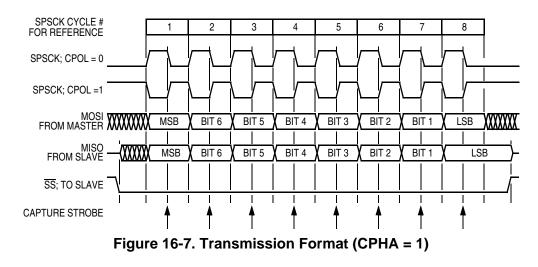

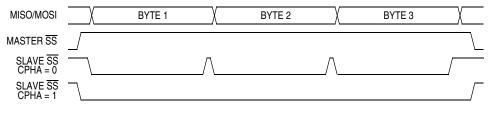

| 16.5.1  | Clock Phase and Polarity Controls | 221 |

| 16.5.2  | Transmission Format When CPHA = 0 | 221 |

| 16.5.3  | Transmission Format When CPHA = 1 | 222 |

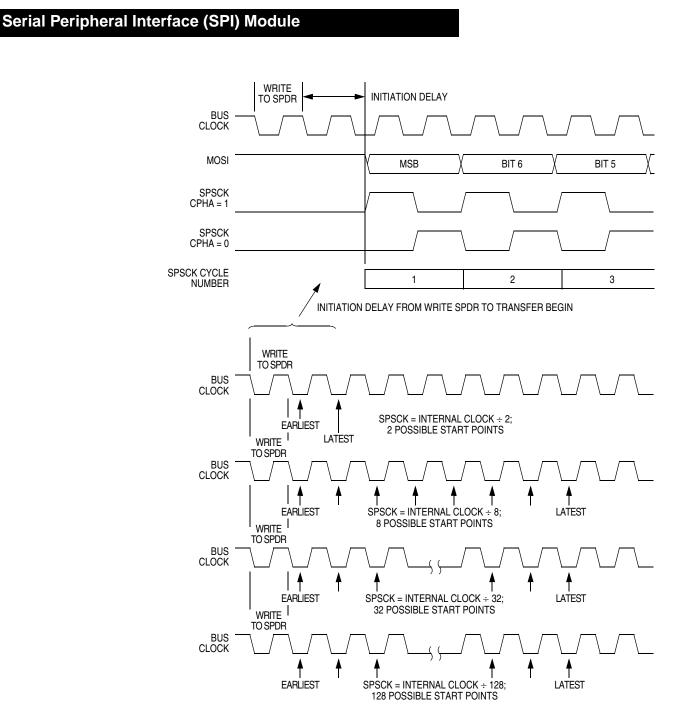

| 16.5.4  | Transmission Initiation Latency   | 223 |

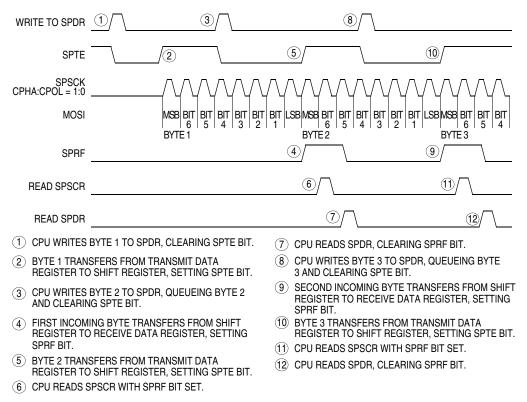

| 16.6    | Queuing Transmission Data         | 225 |

| 16.7    | Error Conditions                  | 226 |

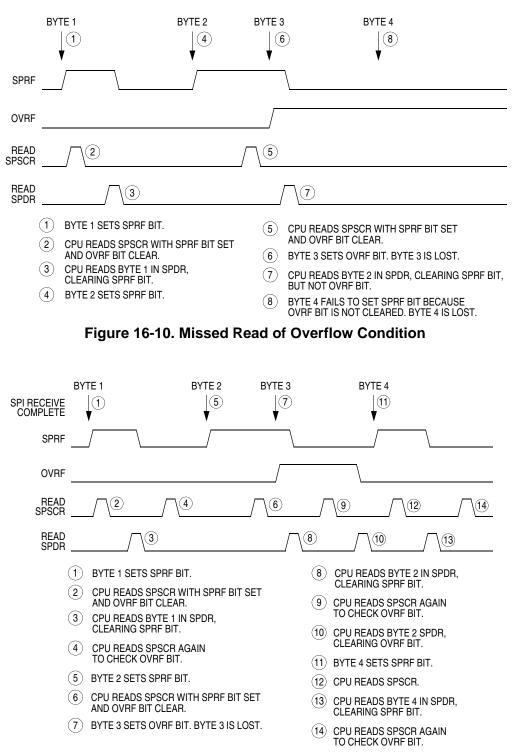

| 16.7.1  | Overflow Error.                   | 226 |

| 16.7.2  | Mode Fault Error                  | 228 |

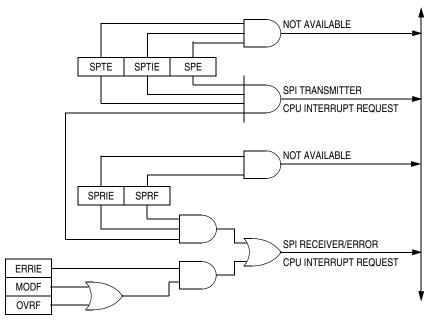

| 16.8    | Interrupts                        | 229 |

| 16.9    | Resetting the SPI                 | 230 |

| 16.10   | Low-Power Modes                   | 231 |

| 16.10.1 |                                   |     |

| 16.10.2 | 2 Stop Mode                       | 231 |

| 16.11   | SPI During Break Interrupts       | 231 |

|         | I/O Signals                       |     |

| 16.12.1 | •                                 |     |

| 16.12.2 |                                   |     |

| 16.12.3 |                                   |     |

| 16.12.4 |                                   |     |

| 16.12.  |                                   |     |

MC68HC908GR16 — Rev. 1.0

# **Table of Contents**

| 16.13 I/O | Registers                       | 234 |

|-----------|---------------------------------|-----|

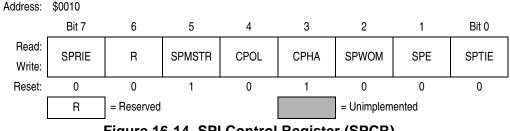

| 16.13.1   | SPI Control Register            | 234 |

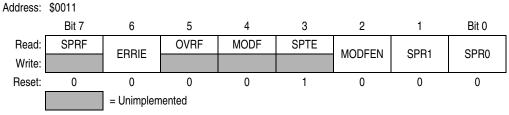

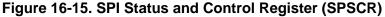

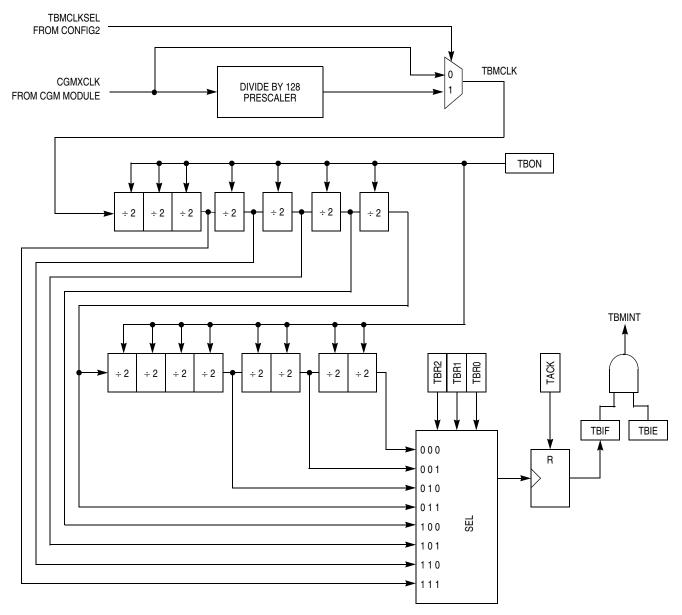

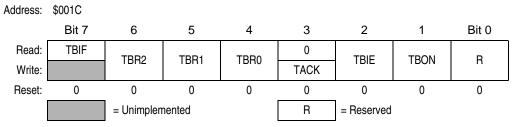

| 16.13.2   | SPI Status and Control Register | 236 |

| 16.13.3   | SPI Data Register               | 238 |

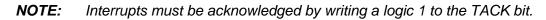

## Section 17. Timebase Module (TBM)

| 17.1   | Introduction                  |

|--------|-------------------------------|

| 17.2   | Features                      |

| 17.3   | Functional Description 239    |

| 17.4   | Interrupts 240                |

| 17.5   | TBM Interrupt Rate 241        |

|        | Low-Power Modes 241           |

| 17.6.1 | Wait Mode                     |

| 17.6.2 | Stop Mode                     |

| 17.7   | Timebase Control Register 242 |

## Section 18. Timer Interface Module (TIM)

| 18.1 Introduction                                                      |

|------------------------------------------------------------------------|

| 18.2 Features                                                          |

| 18.3 Pin Name Conventions                                              |

| 18.4 Functional Description                                            |

| 18.4.1 TIM Counter Prescaler                                           |

| 18.4.2         Input Capture         250                               |

| 18.4.3         Output Compare         250                              |

| 18.4.3.1Unbuffered Output Compare250                                   |

| 18.4.3.2   Buffered Output Compare                                     |

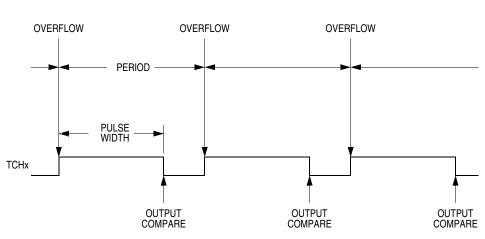

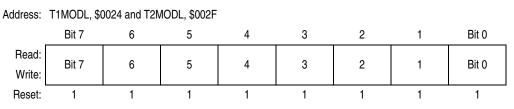

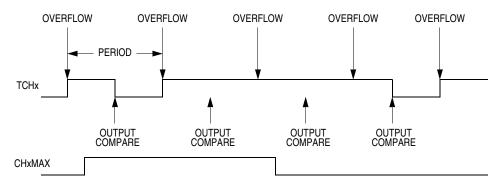

| 18.4.4 Pulse Width Modulation (PWM) 251                                |

| 18.4.4.1 Unbuffered PWM Signal Generation                              |

| 18.4.4.2Buffered PWM Signal Generation25318.4.4.3PWM Initialization253 |

|                                                                        |

| 18.5 Interrupts                                                        |

| 18.6 Low-Power Modes                                                   |

| 18.6.1 Wait Mode                                                       |

| 18.6.2 Stop Mode                                                       |

| 18.7 TIM During Break Interrupts 255                                   |

| 18.8 I/O Signals                                                       |

| 18.9 I/O Registers                                                     |

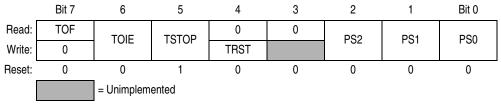

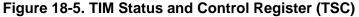

| 18.9.1 TIM Status and Control Register 256                             |

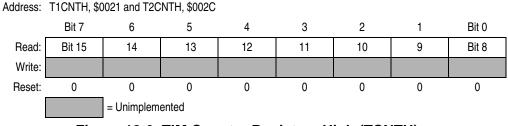

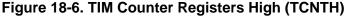

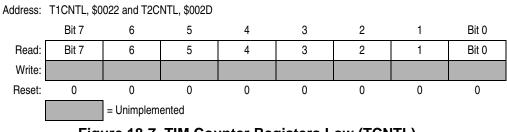

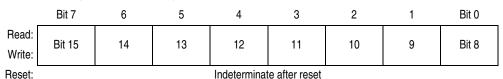

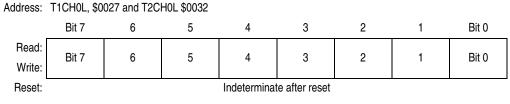

| 18.9.2 TIM Counter Registers                                           |

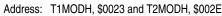

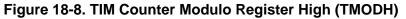

| 18.9.3 TIM Counter Modulo Registers. 258                               |

| 18.9.4 TIM Channel Status and Control Registers                        |

| 18.9.5 TIM Channel Registers                                           |

MOTOROLA

Table of Contents

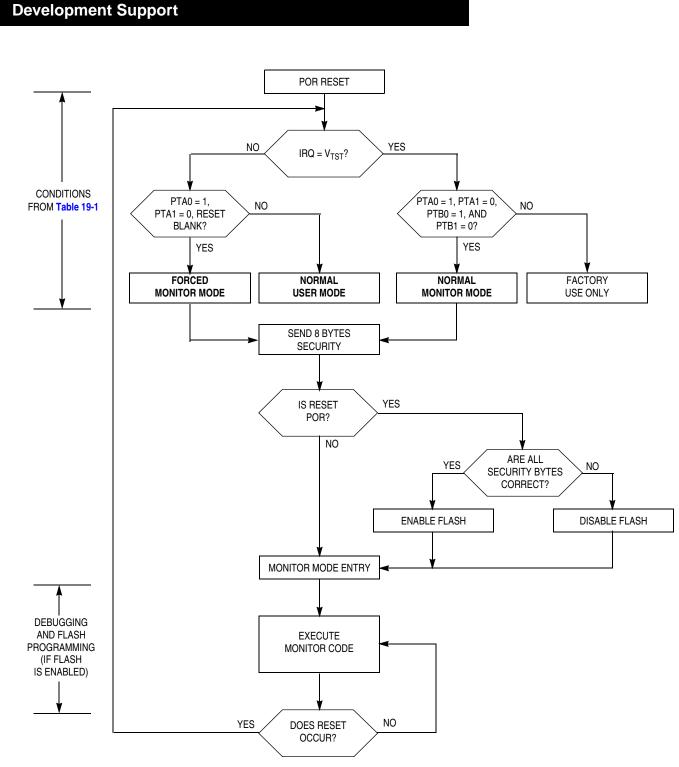

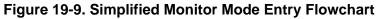

## Section 19. Development Support

| troduction                              | . 263                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

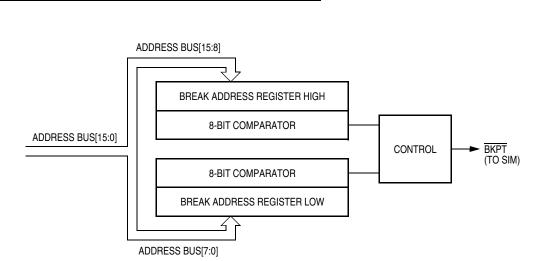

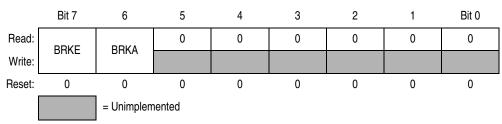

| eak Module (BRK)                        | . 263                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Functional Description                  | . 263                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Flag Protection During Break Interrupts | . 265                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| · · · · · · · · · · · · · · · · · · ·   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| •                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Security                                | . 279                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         | troduction<br>reak Module (BRK)<br>Functional Description<br>Flag Protection During Break Interrupts<br>CPU During Break Interrupts<br>TIM During Break Interrupts<br>COP During Break Interrupts<br>Break Module Registers<br>Break Address Registers<br>Break Address Register<br>Break Address Register<br>Break Status Register<br>Break Status Register<br>Dareak Flag Control Register<br>Low-Power Modes<br>onitor ROM (MON)<br>Functional Description<br>Normal Monitor Mode<br>Forced Monitor Mode<br>Monitor Vectors<br>Data Format<br>Break Signal<br>Baud Rate<br>Commands<br>Security. |

## **Section 20. Electrical Specifications**

# **Table of Contents**

| 20.16 | 5.0-Volt SPI Characteristics | 300 |

|-------|------------------------------|-----|

| 20.17 | 3.3-Volt SPI Characteristics | 301 |

| 20.18 | Memory Characteristics       | 304 |

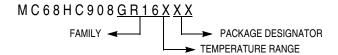

# Section 21. Ordering Information and Mechanical Specifications

| 21.1 | Introduction             | 305 |

|------|--------------------------|-----|

| 21.2 | MC Order Numbers         | 305 |

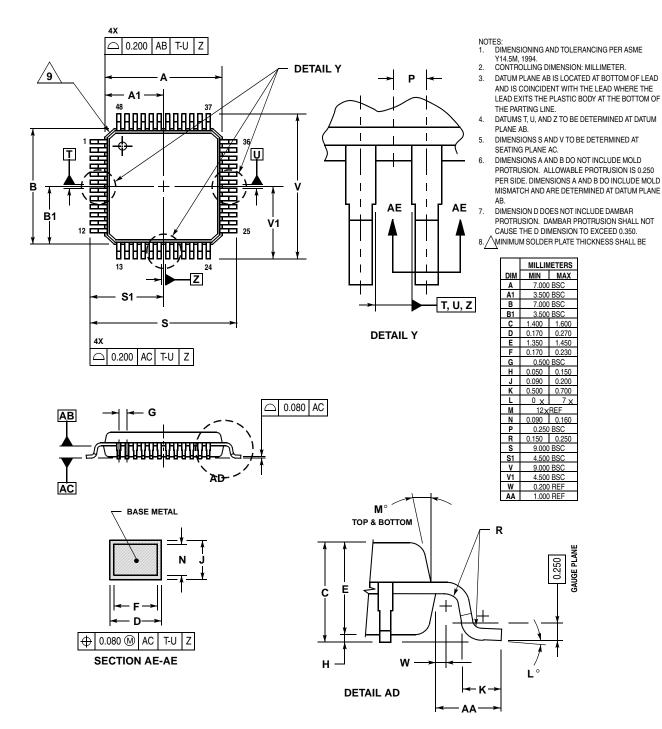

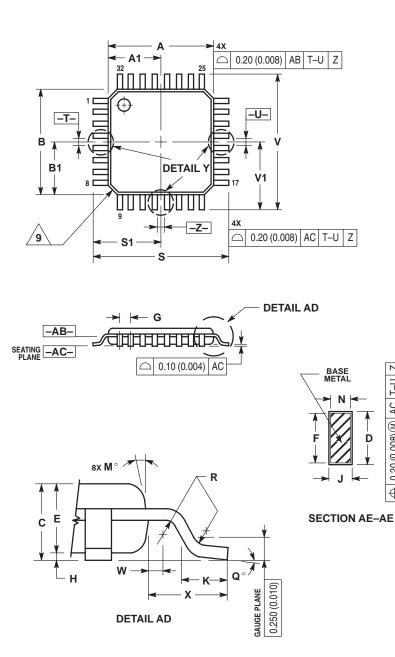

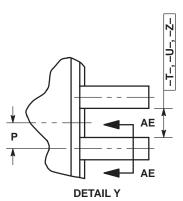

| 21.3 | 48-Pin LQFP (Case #932)  | 306 |

| 21.4 | 32-Pin LQFP (Case #873A) | 307 |

#### Data Sheet — MC68HC908GR16

## **Section 1. General Description**

#### 1.1 Introduction

The MC68HC908GR16 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

#### 1.2 Features

For convenience, features have been organized to reflect:

- Standard features of the MC68HC908GR16

- Features of the CPU08

#### 1.2.1 Standard Features of the MC68HC908GR16

Features of the MC68HC908GR16 include:

- High-performance M68HC08 architecture optimized for C-compilers

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- 8-MHz internal bus frequency

- Clock generation module supporting 32-kHz to 100-kHz crystals

- FLASH program memory security<sup>(1)</sup>

- On-chip programming firmware for use with host personal computer which does not require high voltage for entry

- In-system programming (ISP)

- System protection features:

- Optional computer operating properly (COP) reset

- Low-voltage detection with optional reset and selectable trip points for 3.3-V and 5.0-V operation

- Illegal opcode detection with reset

- Illegal address detection with reset

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### **General Description**

- · Low-power design; fully static with stop and wait modes

- Standard low-power modes of operation:

- Wait mode

- Stop mode

- Master reset pin and power-on reset (POR)

- 16 Kbytes of on-chip 100k cycle write/erase capable FLASH memory

- 1 Kbyte of on-chip random-access memory (RAM)

- 406 bytes of FLASH programming routines read-only memory (ROM)

- Serial peripheral interface (SPI) module

- Enhanced serial communications interface (ESCI) module

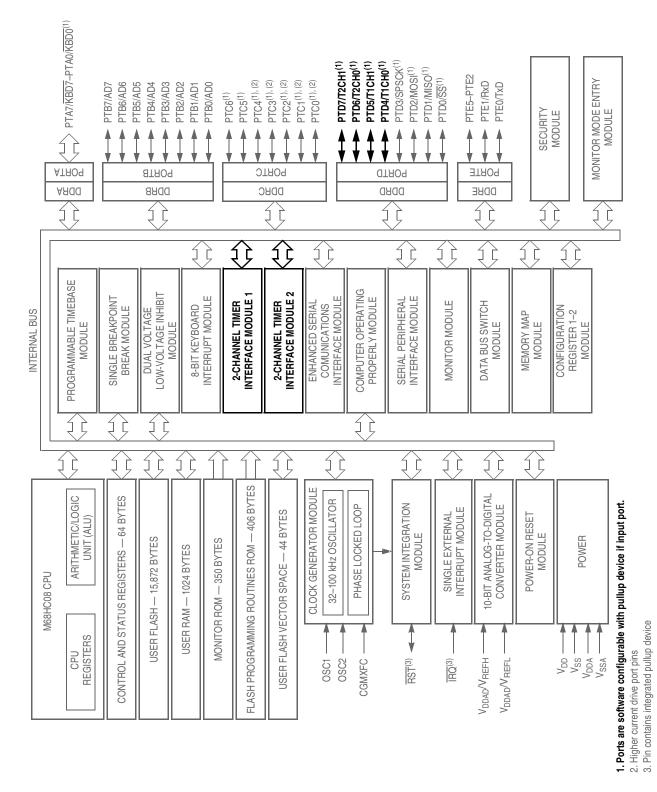

- Two 16-bit timer interface modules (2-channel TIM1 and 2-channel TIM2) with selectable input capture, output compare, and pulse-width modulation (PWM) capability on each channel

- 8-channel, 10-bit successive approximation analog-to-digital converter (ADC)

- BREAK (BRK) module to allow single breakpoint setting during in-circuit debugging

- Internal pullups on IRQ and RST to reduce customer system cost

- Up to 37 general-purpose input/output (I/O) pins, including:

- 28 shared-function I/O pins

- Up to nine dedicated I/O pins, depending on package choice

- Selectable pullups on inputs only on ports A, C, and D. Selection is on an individual port bit basis. During output mode, pullups are disengaged.

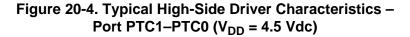

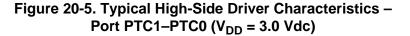

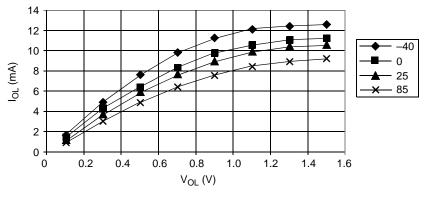

- High current 10-mA sink/source capability on all port pins

- Higher current 20-mA sink/source capability on PTC0–PTC4

- Timebase module (TBM) with clock prescaler circuitry for eight user selectable periodic real-time interrupts with optional active clock source during stop mode for periodic wakeup from stop using an external crystal

- User selection of having the oscillator enabled or disabled during stop mode

- 8-bit keyboard wakeup port

- 5 mA maximum current injection on all port pins to maintain input protection

- Available packages:

- 32-pin LQFP

- 48-pin low-profile quad flag pack (LQFP)

Data Sheet

General Description MCU Block Diagram

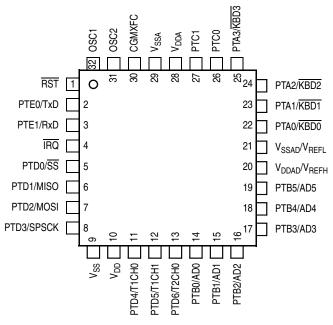

- Specific features of the MC68HC908GR16 in 32-pin LQFP are:

- Port A is only 4 bits: PTA0–PTA3; 4-pin keyboard interrupt (KBI) module

- Port B is only 6 bits: PTB0-PTB5; 6-channel ADC module

- Port C is only 2 bits: PTC0-PTC1

- Port D is only 7 bits: PTD0–PTD6; shared with SPI, TIM1, and TIM2 modules

- Port E is only 2 bits: PTE0-PTE1; shared with ESCI module

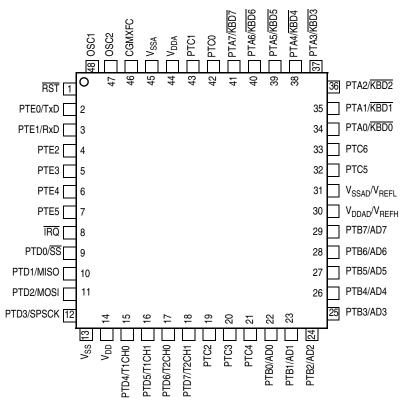

- Specific features of the MC68HC908GR16 in 48-pin LQFP are:

- Port A is 8 bits: PTA0-PTA7; 8-pin KBI module

- Port B is 8 bits: PTB0-PTB7; 8-channel ADC module

- Port C is only 7 bits: PTC0–PTC6

- Port D is 8 bits: PTD0–PTD7; shared with SPI, TIM1, and TIM2 modules

- Port E is only 6 bits: PTE0-PTE5; shared with ESCI module

#### 1.2.2 Features of the CPU08

Features of the CPU08 include:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

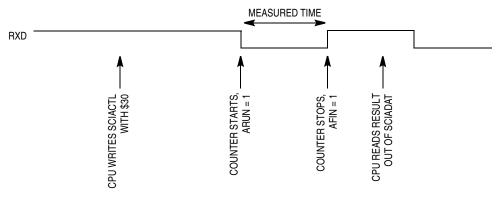

#### 1.3 MCU Block Diagram

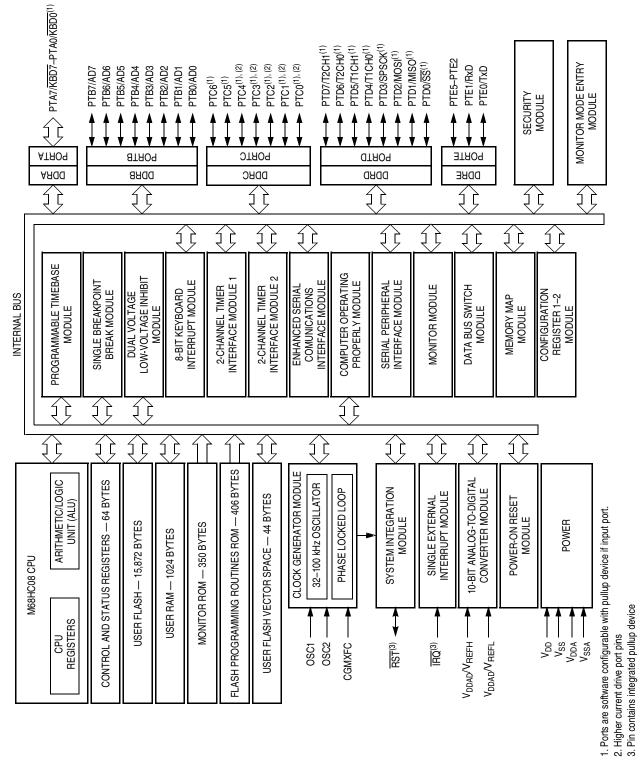

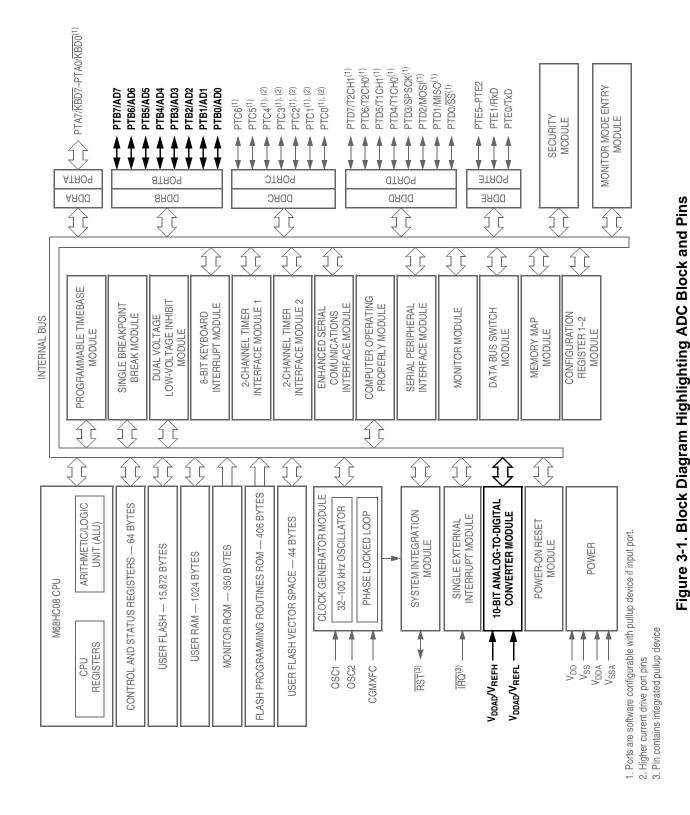

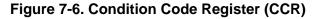

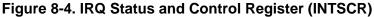

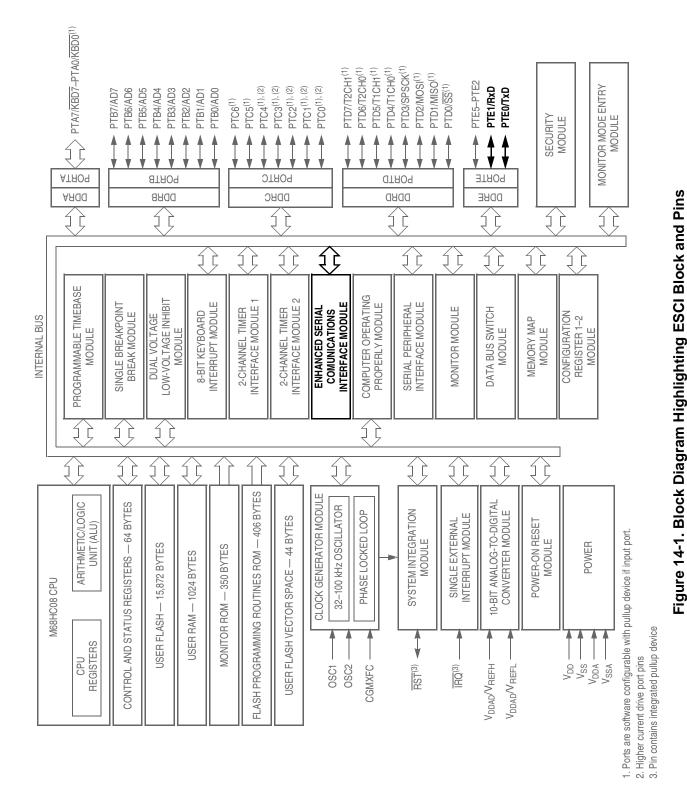

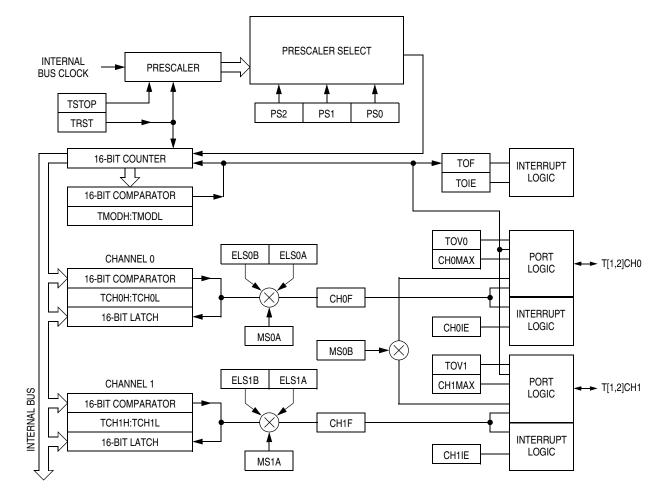

Figure 1-1 shows the structure of the MC68HC908GR16.

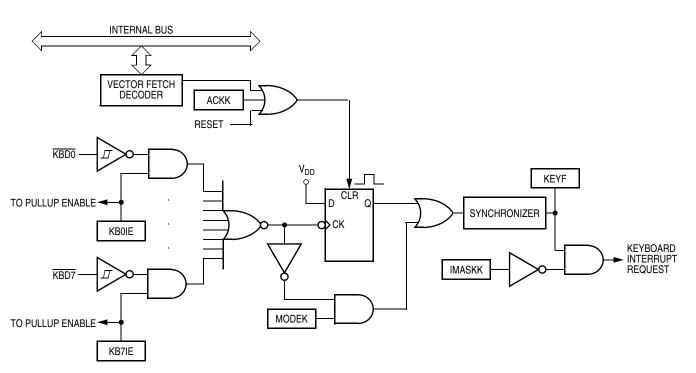

#### 1.4 Pin Assignments

**Figure 1-2** and **Figure 1-3** illustrate the pin assignments for the 32-pin LQFP and 48-pin LQFP respectively.

**General Description**

Data Sheet

MC68HC908GR16 - Rev. 1.0

MOTOROLA

Figure 1-1. MCU Block Diagram

General Description Pin Assignments

Figure 1-2. 32-Pin LQFP Pin Assignments

Figure 1-3. 48-Pin LQFP Pin Assignments

MC68HC908GR16 — Rev. 1.0

#### **General Description**

#### **1.5 Pin Functions**

Descriptions of the pin functions are provided here.

#### 1.5.1 Power Supply Pins ( $V_{DD}$ and $V_{SS}$ )

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins. The MCU operates from a single power supply.

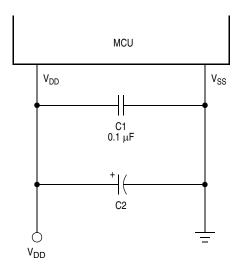

Fast signal transitions on MCU pins place high, short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as **Figure 1-4** shows. Place the C1 bypass capacitor as close to the MCU as possible. Use a high-frequency-response ceramic capacitor for C1. C2 is an optional bulk current bypass capacitor for use in applications that require the port pins to source high current levels.

Note: Component values shown represent typical applications.

Figure 1-4. Power Supply Bypassing

#### 1.5.2 Oscillator Pins (OSC1 and OSC2)

OSC1 and OSC2 are the connections for an external crystal, resonator, or clock circuit. See Section 4. Clock Generator Module (CGM).

#### 1.5.3 External Reset Pin (RST)

A logic 0 on the RST pin forces the MCU to a known startup state. RST is bidirectional, allowing a reset of the entire system. It is driven low when any internal reset source is asserted. This pin contains an internal pullup resistor. See **Section 15. System Integration Module (SIM)**.

**General Description**

#### 1.5.4 External Interrupt Pin (IRQ)

IRQ is an asynchronous external interrupt pin. This pin contains an internal pullup resistor. See Section 8. External Interrupt (IRQ).

#### 1.5.5 CGM Power Supply Pins (V<sub>DDA</sub> and V<sub>SSA</sub>)

$V_{DDA}$  and  $V_{SSA}$  are the power supply pins for the analog portion of the clock generator module (CGM). Decoupling of these pins should be as per the digital supply. See Section 4. Clock Generator Module (CGM).

#### 1.5.6 External Filter Capacitor Pin (V<sub>CGMXFC</sub>)

CGMXFC is an external filter capacitor connection for the CGM. See **Section 4. Clock Generator Module (CGM)**.

#### 1.5.7 ADC Power Supply/Reference Pins ( $V_{DDAD}/V_{REFH}$ and $V_{SSAD}/V_{REFL}$ )

$V_{DDAD}$  and  $V_{SSAD}$  are the power supply pins to the analog-to-digital converter (ADC).  $V_{REFH}$  and  $V_{REFL}$  are the reference voltage pins for the ADC.  $V_{REFH}$  is the high reference supply for the ADC, and by default the  $V_{DDAD}/V_{REFH}$  pin should be externally filtered and connected to the same voltage potential as  $V_{DD}$ .  $V_{REFL}$  is the low reference supply for the ADC, and by default the  $V_{SSAD}/V_{REFL}$  pin should be connected to the same voltage potential as  $V_{CD}$ .

#### 1.5.8 Port A Input/Output (I/O) Pins (PTA7/KBD7–PTA0/KBD0)

PTA7–PTA0 are general-purpose, bidirectional I/O port pins. Any or all of the port A pins can be programmed to serve as keyboard interrupt pins. See Section 12. Input/Output Ports (PORTS) and Section 9. Keyboard Interrupt Module (KBI).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

#### 1.5.9 Port B I/O Pins (PTB7/AD7-PTB0/AD0)

PTB7–PTB0 are general-purpose, bidirectional I/O port pins that can also be used for analog-to-digital converter (ADC) inputs. See Section 12. Input/Output Ports (PORTS) and Section 3. Analog-to-Digital Converter (ADC).

#### 1.5.10 Port C I/O Pins (PTC6-PTC0)

PTC6 and PTC5 are general-purpose, bidirectional I/O port pins. PTC4–PTC0 are general-purpose, bidirectional I/O port pins that contain higher current sink/source capability. See Section 12. Input/Output Ports (PORTS).

#### **General Description**

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

#### 1.5.11 Port D I/O Pins (PTD7/T2CH1-PTD0/SS)

PTD7–PTD0 are special-function, bidirectional I/O port pins. PTD3–PTD0 can be programmed to be serial peripheral interface (SPI) pins, while PTD7–PTD4 can be individually programmed to be timer interface module (TIM1 and TIM2) pins. See Section 18. Timer Interface Module (TIM), Section 16. Serial Peripheral Interface (SPI) Module, and Section 12. Input/Output Ports (PORTS).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

#### 1.5.12 Port E I/O Pins (PTE5-PTE2, PTE1/RxD, and PTE0/TxD)

PTE5–PTE0 are general-purpose, bidirectional I/O port pins. PTE1 and PTE0 can also be programmed to be enhanced serial communications interface (ESCI) pins. See Section 14. Enhanced Serial Communications Interface (ESCI) Module and Section 12. Input/Output Ports (PORTS).

**NOTE:** Any unused inputs and I/O ports should be tied to an appropriate logic level (either  $V_{DD}$  or  $V_{SS}$ ). Although the I/O ports of the MC68HC908GR16 do not require termination, termination is recommended to reduce the possibility of static damage.

#### Data Sheet — MC68HC908GR16

## Section 2. Memory

#### 2.1 Introduction

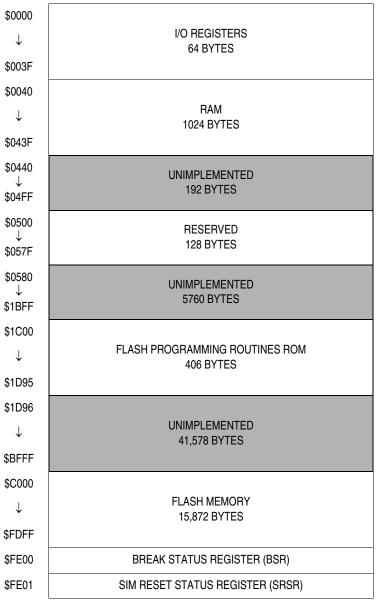

The CPU08 can address 64 Kbytes of memory space. The memory map, shown in **Figure 2-1**, includes:

- 15,872 bytes of user FLASH memory

- 1024 bytes of random-access memory (RAM)

- 406 bytes of FLASH programming routines read-only memory (ROM)

- 44 bytes of user-defined vectors

- 350 bytes of monitor ROM

#### 2.2 Unimplemented Memory Locations

Accessing an unimplemented location can cause an illegal address reset. In the memory map (Figure 2-1) and in register figures in this document, unimplemented locations are shaded.

#### 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on microcontroller (MCU) operation. In the Figure 2-1 and in register figures in this document, reserved locations are marked with the word Reserved or with the letter R.

#### 2.4 Input/Output (I/O) Section

Most of the control, status, and data registers are in the zero page area of \$0000–\$003F. Additional I/O registers have these addresses:

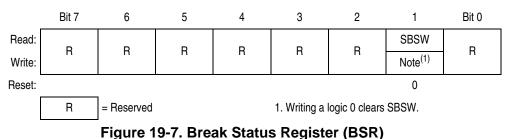

- \$FE00; break status register, BSR

- \$FE01; SIM reset status register, SRSR

- \$FE02; break auxiliary register, BRKAR

- \$FE03; break flag control register, BFCR

- \$FE04; interrupt status register 1, INT1

- \$FE05; interrupt status register 2, INT2

- \$FE06; interrupt status register 3, INT3

- \$FE07; reserved

Data Sheet

## Memory

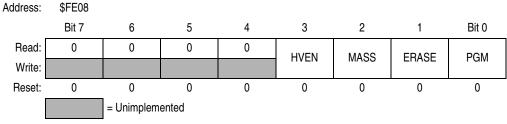

- \$FE08; FLASH control register, FLCR

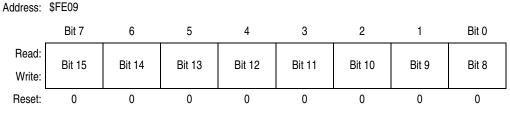

- \$FE09; break address register high, BRKH

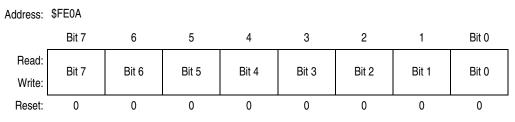

- \$FE0A; break address register low, BRKL

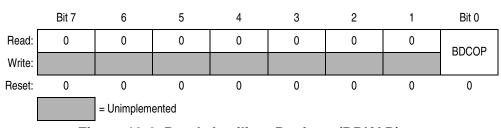

- \$FE0B; break status and control register, BRKSCR

- \$FE0C; LVI status register, LVISR

- \$FF7E; FLASH block protect register, FLBPR

Data registers are shown in Figure 2-2. Table 2-1 is a list of vector locations.

Figure 2-1. Memory Map

Data Sheet

| \$FE02                | BREAK AUXILIARY REGISTER (BRKAR)                         |

|-----------------------|----------------------------------------------------------|

| \$FE03                | BREAK FLAG CONTROL REGISTER (BFCR)                       |

| \$FE04                | INTERRUPT STATUS REGISTER 1 (INT1)                       |

| \$FE05                | INTERRUPT STATUS REGISTER 2 (INT2)                       |

| \$FE06                | INTERRUPT STATUS REGISTER 3 (INT3)                       |

| \$FE07                | RESERVED                                                 |

| \$FE08                | FLASH CONTROL REGISTER (FLCR)                            |

| \$FE09                | BREAK ADDRESS REGISTER HIGH (BRKH)                       |

| \$FE0A                | BREAK ADDRESS REGISTER LOW (BRKL)                        |

| \$FE0B                | BREAK STATUS AND CONTROL REGISTER (BRKSCR)               |

| \$FE0C                | LVI STATUS REGISTER (LVISR)                              |

| \$FE0D                |                                                          |

| $\downarrow$          | UNIMPLEMENTED<br>3 BYTES                                 |

| \$FE0F                |                                                          |

| \$FE10                | UNIMPLEMENTED                                            |

| $\downarrow$          | 16 BYTES<br>RESERVED FOR COMPATIBILITY WITH MONITOR CODE |

| \$FE1F                | FOR A-FAMILY PART                                        |

| \$FE20                |                                                          |

| $\downarrow$          | MONITOR ROM<br>350 BYTES                                 |

| \$FF7D                |                                                          |

| \$FF7E                | FLASH BLOCK PROTECT REGISTER (FLBPR)                     |

| \$FF7F                |                                                          |

| $\downarrow$          | UNIMPLEMENTED<br>85 BYTES                                |

| \$FFD3                |                                                          |

| \$FFD4                |                                                          |

| $\downarrow$          | FLASH VECTORS<br>44 BYTES                                |

| \$FFFF <sup>(1)</sup> |                                                          |

|                       |                                                          |

1. \$FFF6-\$FFFD used for eight security bytes

Figure 2-1. Memory Map (Continued)

MC68HC908GR16 — Rev. 1.0

## Memory

| Addr.  | Register Name                              |                 | Bit 7 | 6          | 5      | 4         | 3          | 2       | 1       | Bit 0    |

|--------|--------------------------------------------|-----------------|-------|------------|--------|-----------|------------|---------|---------|----------|

| \$0000 | Port A Data Register<br>(PTA)              | Read:<br>Write: | PTA7  | PTA6       | PTA5   | PTA4      | PTA3       | PTA2    | PTA1    | PTA0     |

|        | See page 132.                              | Reset:          |       |            |        | Unaffecte | d by reset |         |         | <u> </u> |

| \$0001 | Port B Data Register<br>(PTB)              | Read:<br>Write: | PTB7  | PTB6       | PTB5   | PTB4      | PTB3       | PTB2    | PTB1    | PTB0     |

|        | See page 134.                              | Reset:          |       |            | I      | Unaffecte | d by reset |         |         | <u> </u> |

| \$0002 | Port C Data Register<br>(PTC)              | Read:<br>Write: | 0     | PTC6       | PTC5   | PTC4      | PTC3       | PTC2    | PTC1    | PTC0     |

|        | See page 136.                              | Reset:          |       |            | 1      | Unaffecte | d by reset |         |         | <u> </u> |

| \$0003 | Port D Data Register<br>(PTD)              | Read:<br>Write: | PTD7  | PTD6       | PTD5   | PTD4      | PTD3       | PTD2    | PTD1    | PTD0     |

|        | See page 138.                              | Reset:          |       |            | 1      | Unaffecte | d by reset |         | 1       | L]       |

| \$0004 | Data Direction Register A<br>(DDRA)        | Read:<br>Write: | DDRA7 | DDRA6      | DDRA5  | DDRA4     | DDRA3      | DDRA2   | DDRA1   | DDRA0    |

|        | See page 132.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

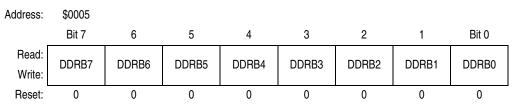

| \$0005 | Data Direction Register B<br>(DDRB)        | Read:<br>Write: | DDRB7 | DDRB6      | DDRB5  | DDRB4     | DDRB3      | DDRB2   | DDRB1   | DDRB0    |

|        | See page 135.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

| \$0006 | Data Direction Register C<br>(DDRC)        | Read:<br>Write: | 0     | DDRC6      | DDRC5  | DDRC4     | DDRC3      | DDRC2   | DDRC1   | DDRC0    |

|        | See page 136.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

| \$0007 | Data Direction Register D<br>(DDRD)        | Read:<br>Write: | DDRD7 | DDRD6      | DDRD5  | DDRD4     | DDRD3      | DDRD2   | DDRD1   | DDRD0    |

|        | See page 139.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

| \$0008 | Port E Data Register<br>(PTE)              | Read:<br>Write: | 0     | 0          | PTE5   | PTE4      | PTE3       | PTE2    | PTE1    | PTE0     |

|        | See page 141.                              | Reset:          |       |            |        | Unaffecte | d by reset |         | 1       | J        |

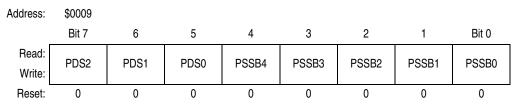

| \$0009 | ESCI Prescaler Register<br>(SCPSC)         | Read:<br>Write: | PS2   | PS1        | PS0    | PSSB4     | PSSB3      | PSSB2   | PSSB1   | PSSB0    |

|        | See page 187.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

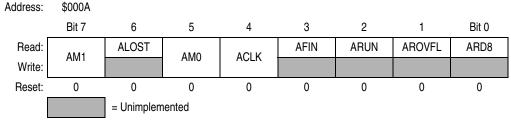

| \$000A | ESCI Arbiter Control Register<br>(SCIACTL) | Read:<br>Write: | AM1   | ALOST      | AM0    | ACLK      | AFIN       | ARUN    | AOVFL   | ARD8     |

|        | See page 191.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

| \$000B | ESCI Arbiter Data<br>Register (SCIADAT)    | Read:<br>Write: | ARD7  | ARD6       | ARD5   | ARD4      | ARD3       | ARD2    | ARD1    | ARD0     |

|        | See page 192.                              | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0       | 0        |

|        |                                            |                 |       | = Unimplem | nented | R         | = Reserved | U = Una | ffected |          |

## Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 7)

MC68HC908GR16 — Rev. 1.0

**Freescale Semiconductor, Inc.**

Memory Input/Output (I/O) Section

| Addr.  | Register Name                                   |                 | Bit 7   | 6          | 5       | 4         | 3          | 2       | 1       | Bit 0   |

|--------|-------------------------------------------------|-----------------|---------|------------|---------|-----------|------------|---------|---------|---------|

|        | Data Direction Register E                       | Read:           | 0       | 0          | DDRE5   | DDRE4     | DDRE3      | DDRE2   | DDRE1   | DDRE0   |

| \$000C | (DDRE)<br>See page 142.                         | Write:          |         |            |         |           |            |         |         |         |

|        | See page 142.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

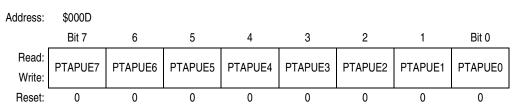

| \$000D | Port A Input Pullup Enable<br>Register (PTAPUE) | Read:<br>Write: | PTAPUE7 | PTAPUE6    | PTAPUE5 | PTAPUE4   | PTAPUE3    | PTAPUE2 | PTAPUE1 | PTAPUE0 |

|        | See page 134.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

| \$000E | Port C Input Pullup Enable<br>Register (PTCPUE) | Read:<br>Write: | 0       | PTCPUE6    | PTCPUE5 | PTCPUE4   | PTCPUE3    | PTCPUE2 | PTCPUE1 | PTCPUE0 |

|        | See page 138.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

| \$000F | Port D Input Pullup Enable<br>Register (PTDPUE) | Read:<br>Write: | PTDPUE7 | PTDPUE6    | PTDPUE5 | PTDPUE4   | PTDPUE3    | PTDPUE2 | PTDPUE1 | PTDPUE0 |

|        | See page 141.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

| \$0010 | SPI Control Register<br>(SPCR)                  | Read:<br>Write: | SPRIE   | R          | SPMSTR  | CPOL      | СРНА       | SPWOM   | SPE     | SPTIE   |

|        | See page 235.                                   | Reset:          | 0       | 0          | 1       | 0         | 1          | 0       | 0       | 0       |

| \$0011 | SPI Status and Control<br>Register (SPSCR)      | Read:<br>Write: | SPRF    | ERRIE      | OVRF    | MODF      | SPTE       | MODFEN  | SPR1    | SPR0    |

|        | See page 236.                                   | Reset:          | 0       | 0          | 0       | 0         | 1          | 0       | 0       | 0       |

|        | SPI Data Register                               | Read:           | R7      | R6         | R5      | R4        | R3         | R2      | R1      | R0      |

| \$0012 | (SPDR)                                          | Write:          | T7      | T6         | T5      | T4        | Т3         | T2      | T1      | Т0      |

|        | See page 238.                                   | Reset:          |         |            | 1       | Unaffecte | d by reset |         |         |         |

| \$0013 | ESCI Control Register 1<br>(SCC1)               | Read:<br>Write: | LOOPS   | ENSCI      | TXINV   | М         | WAKE       | ILTY    | PEN     | ΡΤΥ     |

|        | See page 176.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

| \$0014 | ESCI Control Register 2<br>(SCC2)               | Read:<br>Write: | SCTIE   | TCIE       | SCRIE   | ILIE      | TE         | RE      | RWU     | SBK     |

|        | See page 178.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

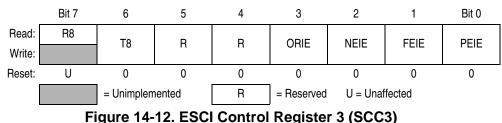

| \$0015 | ESCI Control Register 3<br>(SCC3)               | Read:<br>Write: | R8      | Т8         | R       | R         | ORIE       | NEIE    | FEIE    | PEIE    |

|        | See page 180.                                   | Reset:          | U       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

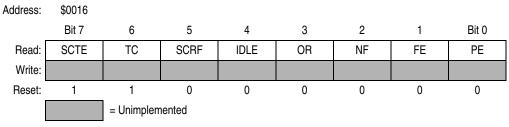

|        | ESCI Status Register 1                          | Read:           | SCTE    | TC         | SCRF    | IDLE      | OR         | NF      | FE      | PE      |

| \$0016 | (SCS1)                                          | Write:          |         |            |         |           |            |         |         |         |

|        | See page 181.                                   | Reset:          | 1       | 1          | 0       | 0         | 0          | 0       | 0       | 0       |

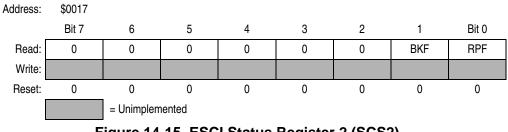

| \$0017 | ESCI Status Register 2<br>(SCS2)                | Read:<br>Write: |         |            |         |           |            |         | BKF     | RPF     |

|        | See page 184.                                   | Reset:          | 0       | 0          | 0       | 0         | 0          | 0       | 0       | 0       |

|        |                                                 |                 |         | = Unimplem | nented  | R         | = Reserved | U = Una | ffected |         |

## Memory

| Addr.  | Register Name                                        | -               | Bit 7       | 6          | 5           | 4           | 3                   | 2          | 1          | Bit 0     |

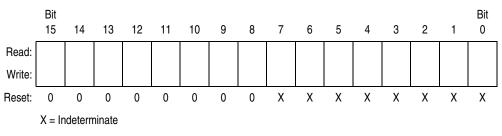

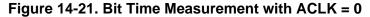

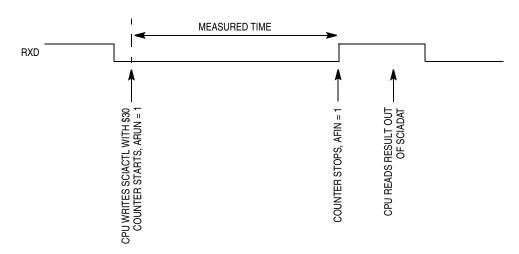

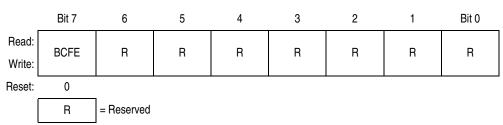

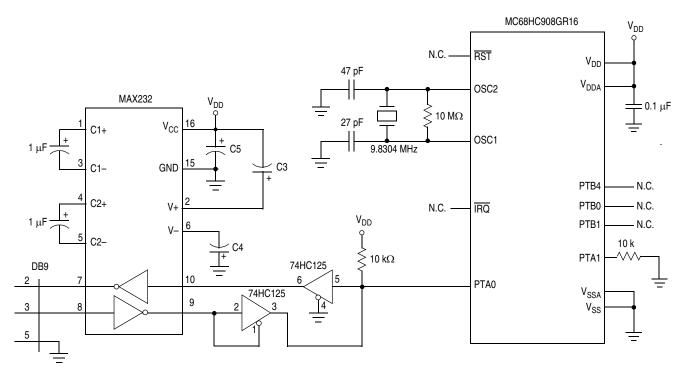

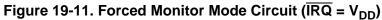

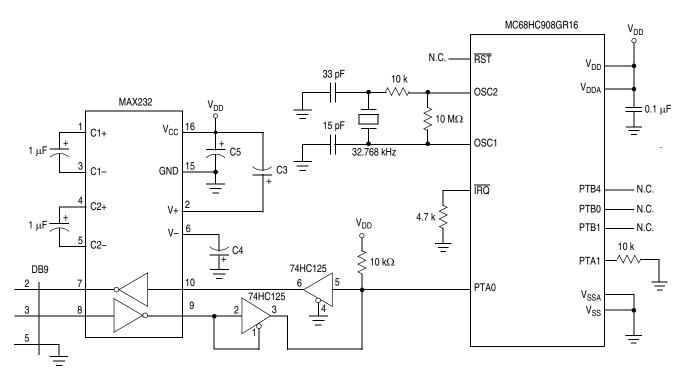

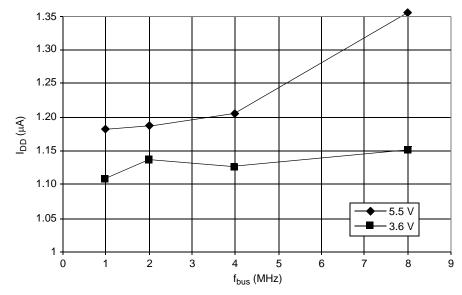

|--------|------------------------------------------------------|-----------------|-------------|------------|-------------|-------------|---------------------|------------|------------|-----------|