# 5V Linear Controller/Driver

## Description

The CS8128 contains all the necessary control circuitry to implement a 5V linear regulator. An external pass device is used to produce superior performance compared to conventional monolithic regulators. The CS8128 with a TIP42 PNP transistor typically provides a 100mV dropout voltage at 500mA, increasing to 350mV at 3A. Quiescent current at 500mA is only 5mA. Monolithic regulators cannot approach these figures because their power transistors do not provide the high beta and excellent saturation characteristics at high currents. The CS8128 is compatible with a wide variety of external transistors, allowing flexibility for thermal, space, and cost management.

The CS8128 includes thermal shutdown and externally programmable current limit and over-voltage shutdown, making it suitable for use in automotive and switching regulator post regulator applications. An optional external RC filter added to the CS8128 supply lead provides EMC hardening in addition to the on-chip EMC hardening. The SENSE

Cherry

lead allows remote sensing of the output voltage for improved regulation.

An active microprocessor RESET function is included on-chip with externally programmable delay time. During power-up, or after detection of any error in the regulated output, the RESET lead will remain in the low state for the duration of the delay. Types of errors include short circuit, low input voltage, overvoltage shutdown, thermal shutdown, or others that cause the output to become unregulated. This function is independent of the input voltage and will function correctly with an output voltage as low as 1V. Hysteresis is included in both the reset and delay comparators for noise immunity and to prevent oscillations. A latching discharge circuit is used to discharge the delay capacitor, even when triggered by a relatively short fault condition. This circuit improves upon the commonly used SCR structure by providing improved noise immunity and full capacitor discharge (0.2V typ).

### **Features**

- Externally Set Delay for Reset

- 60V Load Dump Protection

- Internal Thermal

Overload Protection

- 3% Output Accuracy

- Active RESET

- Noise Immunity

- On Chip EMC Hardening Protection Incorporated

- Externally Set Current Limit

- Externally Set

Overvoltage Shutdown

## **Package Options**

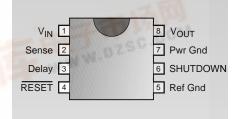

8L SO & 8L PDIP

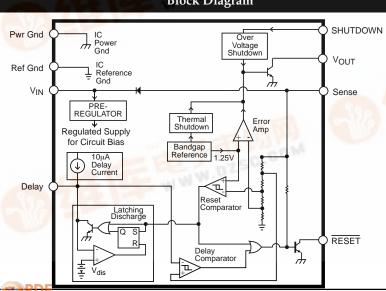

#### Block Diagram

emiconductor

#### **Absolute Maximum Ratings**

| Power DissipationInput Voltage         |                         |

|----------------------------------------|-------------------------|

| Transient Input Voltage                |                         |

| Output Current                         | Externally Limited      |

| ESD Susceptibility (Human Body Model)  |                         |

| Junction Temperature                   | -45°C to 150°C          |

| Storage Temperature                    |                         |

| Lead Temperature Soldering             |                         |

| Wave Solder (through hole styles only) | 10 sec. max, 260°C peak |

| Reflow (SMD styles only)               |                         |

Electrical Characteristics:  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $T_J = -40^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ ,  $V_{IN} = 6$  to 26V,  $I_{OUT} = 5$  to 500mA, Per Test Circuit (unless otherwise noted)

| PARAMETER                          | TEST CONDITIONS                                                                                             | MIN  | TYP          | MAX     | UNIT |

|------------------------------------|-------------------------------------------------------------------------------------------------------------|------|--------------|---------|------|

| ■ Output Stage (V <sub>OUT</sub> ) |                                                                                                             |      |              |         |      |

| Output Voltage                     |                                                                                                             | 4.85 | 5.00         | 5.15    | V    |

| Dropout Voltage                    | $I_{OUT} = 500$ mA, note 1                                                                                  |      | 0.1          | 0.6     | V    |

| Supply Current I <sub>Q</sub>      | $\begin{split} &I_{OUT} \leq 10 mA \\ &I_{OUT} \leq 500 mA \\ &I_{OUT} \leq 3A \text{, note 1} \end{split}$ |      | 4<br>5<br>30 | 8<br>15 | mA   |

| Line Regulation                    | $6V \le V_{IN} \le 26V$ , $I_{OUT} = 5mA$                                                                   |      | 12           | 50      | mV   |

| Load Regulation                    | $5V \le I_{OUT} \le 500 \text{mA}, V_{IN} = 14V$                                                            |      | 2            | 50      | mV   |

| Ripple Rejection                   | $\begin{split} f &= 120 Hz,  7V \leq V_{IN} \leq 17V, \\ I_{OUT} &= 350 mA \end{split}$                     | 60   | 70           |         | dB   |

| $V_{IN}$ Overvoltage Shutdown      |                                                                                                             | 32   |              | 40      | V    |

| Drive Current                      | $V_{SENSE} = 0V$                                                                                            | 25   | 250          |         | mA   |

#### **■** RESET and Delay Functions

| Delay Charge Current, I <sub>Charge</sub>                | $V_{\text{Delay}} = 2V$                                    | 5            | 10           | 15                                                                        | μA     |

|----------------------------------------------------------|------------------------------------------------------------|--------------|--------------|---------------------------------------------------------------------------|--------|

| $\overline{RESET}$ Threshold $V_{RTH}$ $V_{RTL}$         | V <sub>OUT</sub> Increasing<br>V <sub>OUT</sub> Decreasing | 4.65<br>4.50 | 4.90<br>4.70 | $\begin{array}{c} V_{OUT}\text{-}0.10 \\ V_{OUT}\text{-}0.15 \end{array}$ | V<br>V |

| $\overline{RESET}$ Hysteresis $V_{RH}$                   |                                                            | 150          | 200          | 250                                                                       | mV     |

| Delay Threshold $V_{DTC}$ $V_{DTD}$                      | Charge<br>Discharge                                        | 3.25<br>2.80 | 3.50<br>3.00 | 3.75<br>3.40                                                              | V<br>V |

| Delay Hysteresis, $V_{DH}$                               | $ m V_{DTC}$ - $ m V_{DTD}$                                | 200          | 400          | 800                                                                       | mV     |

| RESET Output Voltage Low                                 | $1V < V_{OUT} < V_{RTL}$ , $3k\Omega$ to $V_{OUT}$         |              |              | 0.4                                                                       | V      |

| RESET Output<br>Leakage Current                          | $V_D > V_{DTC}$ , $V_{OUT} > V_{RTH}$                      |              |              | 10                                                                        | μΑ     |

| Delay Capacitor (V <sub>dis</sub> )<br>Discharge Voltage | Discharge Latched "ON", $V_{OUT} > V_{RTH}$                |              | 0.2          | 0.5                                                                       | V      |

| Delay Time                                               | $C_{Delay} = 0.1 \mu F$ , note 2                           | 16           | 32           | 48                                                                        | ms     |

Note 1: Dependent on characteristics of external transistor.

Note 2: Delay Time =

$$\frac{C_{\text{Delay}} \times V_{\text{DTC}}}{I_{\text{Charge}}} = C_{\text{Delay}} \times 3.5 \times 10^5 \text{ (Typical)}$$

#### Typical Performance Characteristics (per Test Circuit) Temperature Performance of V<sub>OUT</sub> Dropout Voltage vs. I<sub>OUT</sub> RESET Voltage vs. Output Current 2000 I<sub>OUT</sub>=500mA 25°C $V_{in} = 5V$ 1800 350 5.01 (m) 5.00V @ 25°C 1600 £ 300 RESET OUTPUT VOLTAGE 1400 $R_{OUT} = 47\Omega$ 250 200 4.99 4.98 600 4.97 100 50 4.96 200 4.95 20 25 2.0 0.5 1.5 20 40 60 80 100120140150 I<sub>OUT</sub> (Amps) JUNCTION TEMPERATURE (°C) RESET OUTPUT CURRENT (mA) $\overline{ m V}_{ m OUT}$ vs. $m V_{ m IN}$ I<sub>Q</sub> vs. V<sub>IN</sub> I<sub>O</sub> vs. I<sub>OUT</sub> 100 00 25°C 90.00 5.00 35 I<sub>OUT</sub> = 3A 4.50 80.00 $R_{OUT} = 47\Omega$ 30 4.00 70.00 V<sub>IN</sub>=14V I<sub>OUT</sub>=0.5A 3.50 3 60.00 IQ (mA) 3.00 50.00 20 2.50 40.00 2.00 1.50 30.00 I<sub>OUT</sub> = 0.5Å 20.00 1.00 $R_{OUT} = 330\Omega$ 0.50 10.00 0.00 1.5 IOUT (Amps) Line Regulation vs. I<sub>OUT</sub> Load Regulation vs. I<sub>OUT</sub> Ripple Rejection 80 25°C 25°C 18 70 LINE REGULATION (mV) 6V≤V<sub>IN</sub> ≤- 26V IOUT=250mA LOAD REGULATION (mV) 16 60 (gp)LNO<sub>A</sub>/NI<sub>A</sub> 14 12 10 8 20 <del>IIIII | IIIIII | IIIIII | IIIIII |</del> 10K 100K 1M 10M 0.5 2.5 1.5 2.0 2.5

I<sub>OUT</sub>(Amps)

I<sub>OUT</sub>(Amps)

FREQUENCY (Hz)

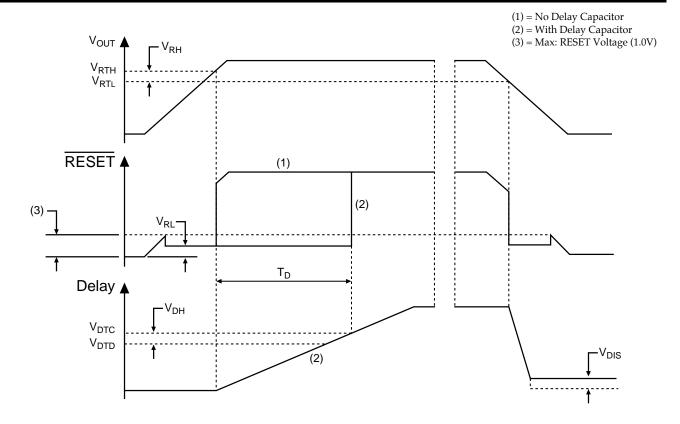

#### **RESET Circuit Waveform**

#### **RESET Circuit Functional Description**

The CS8128  $\overline{\text{RESET}}$  function is very precise, has hysteresis on both the  $\overline{\text{RESET}}$  and Delay comparators, a latching Delay capacitor discharge circuit, and operation down to 1V

The reset circuit output is an open collector type with ON and OFF parameters as specified. The reset output NPN transistor is controlled by the Low Voltage Inhibit and Reset Delay circuits (see Block Diagram).

#### Low Voltage Inhibit Circuit

This circuit monitors output voltage, and when output voltage is below  $V_{RTL}$ , causes the reset output transistor to be in the ON (saturation) state. When the output voltage is above  $V_{RTH}$ , this circuit permits the reset output transistor to go into the OFF state if allowed by the reset Delay circuit.

#### **RESET Delay Circuit**

This circuit provides a programmable (by external capacitor) delay on the  $\overline{RESET}$  output lead. The Delay lead provides source current to the external delay capacitor only when the Low Voltage Inhibit circuit indicates that output voltage is above  $V_{RTH}.$  Otherwise, the Delay lead sinks current to ground (used to discharge the Delay capacitor). The discharge current is latched ON when the output voltage falls below  $V_{RTL}.$  The Delay capacitor is fully discharged anytime the output voltage falls out of regulation, even for a short period of time. This feature ensures a controlled  $\overline{RESET}$  pulse is generated following the detection of an error condition. The circuit allows the  $\overline{RESET}$  output transistor to go to the OFF (open) state only when the voltage on the Delay lead is higher than  $V_{DTC}.$

#### **Application Information**

#### Overvoltage Shutdown

The CS8128 includes an over voltage shutdown circuit which is activated by connecting the SHUTDOWN lead to the input. Shutdown typically occurs at 36V. Grounding the SHUTDOWN lead disables this function. With the overvoltage shutdown disabled, the CS8128 will continue to regulate during an overvoltage condition.

#### Thermal Shutdown

The CS8128 includes a thermal shutdown circuit that disables the output when junction temperature exceeds approximately 180°C. This is a self-protection feature designed to protect the CS8128. The thermal shutdown circuit does not monitor the temperature of the pass transistor, which will probably be much hotter. To optimize thermal shutdown, board design should minimize the difference in temperature of the CS8128 and the pass device.

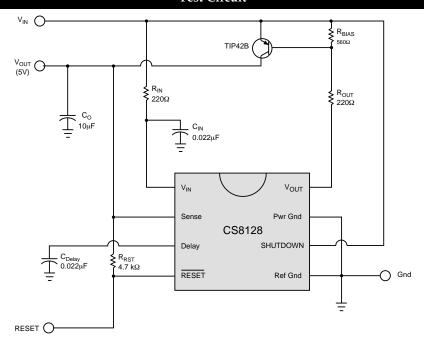

#### **External Component Selection**

**External Pass Device** - Select a pass device that will deliver the desired output current, withstand the maximum expected input voltage, and dissipate the resulting power. The CS8128 is compatible with a wide variety of Bipolar and FET pass transistors.

**Output Capacitor** - An output capacitor is required for stability in most applications. Though a  $10\mu$ F capacitor should be sufficient, regulator stability is dependent on the characteristics of the pass transistor. Capacitor effective series resistance (ESR) also factors in system stability. Some bench work may be required to determine the capacitor characteristics required for use in a particular application.

**BIAS Resistor** - This resistor provides bias current for the CS8128 output stage, and prevents the pass device from

"leaking". It also speeds the turn-off of the pass device during an overvoltage transient. For proper operation over temperature, the recommended value is  $560\Omega$ , although it may be increased or decreased for a particular application.

**R<sub>OUT</sub> Resistor** - This resistor controls the drive current available to the pass transistor. It also determines regulator start-up current and short circuit current limit. For bipolar pass transistors, it can be selected by use of the following formulae:

$$R_{OUT} = \frac{V_{IN(min)} - 1V}{I_{OUT(max)}} \times \beta_{Q1}^{***}$$

\*\*\* $\beta_{Q1}$  = Pass transistor minimum  $\beta$  @ maximum output current.

Typical start-up current and current limit can be calculated as follows:

$$I_{START} \approx \frac{4V}{R_{OUT}} + 5mA$$

$$I_{Limit} \approx \frac{V_{IN} - 1V}{R_{OUT}} \times \Re_{Q1}$$

@ Current Limit

For example, if the minimum input voltage is 6V, maximum output current is 1Amp, and minimum transistor  $\beta$  @ 1Amp is 60, then  $R_{OUT}$  can be calculated as follows:

$$R_{OUT} \approx \frac{6V - 1V}{1Amp} \times 60 = 300\Omega$$

$$I_{Start} \approx \frac{4V}{300\Omega} + 5mA = 18.3mA$$

With  $V_{\rm IN}$  = 14V, and a pass transistor  $\beta$  of 40 @ current limit:

$$I_{Limit} \approx \frac{14V - 1V}{300Q} \times 40 = 1.7 Amps$$

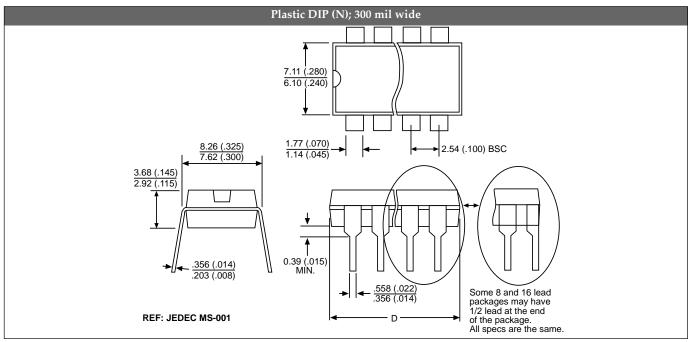

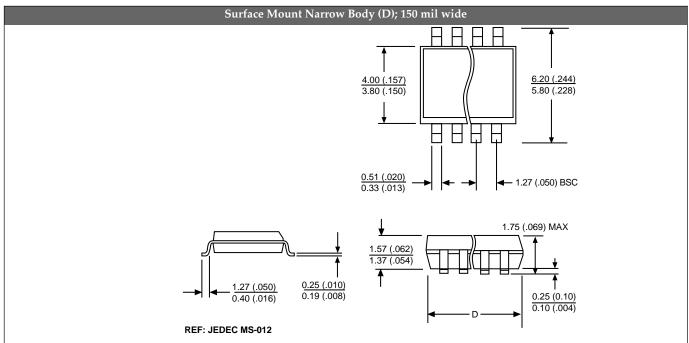

#### **Package Specification**

#### PACKAGE DIMENSIONS IN mm (INCHES)

|              |        | D    |         |      |

|--------------|--------|------|---------|------|

| Lead Count   | Metric |      | English |      |

|              | Max    | Min  | Max     | Min  |

| 8L PDIP      | 10.16  | 9.02 | .400    | .355 |

| 8L SO Narrow | 5.00   | 4.80 | .197    | .189 |

#### PACKAGE THERMAL DATA

| Thermal Data              |     | 8 Lead<br>PDIP | 8 Lead<br>SO Narrow |      |

|---------------------------|-----|----------------|---------------------|------|

| RΘ <sub>JC</sub>          | typ | 52             | 45                  | °C/W |

| $\overline{R\Theta_{JA}}$ | typ | 100            | 165                 | °C/W |

#### **Ordering Information**

| Part Number | Description                    |  |

|-------------|--------------------------------|--|

| CS8128YN8   | 8 Lead PDIP                    |  |

| CS8128YD8   | 8 Lead SO Narrow               |  |

| CS8128YDR8  | 8 Lead SO Narrow (tape & reel) |  |

Cherry Semiconductor Corporation reserves the right to make changes to the specifications without notice. Please contact Cherry Semiconductor Corporation for the latest available information.