## **PRELIMINARY**

CY7C9235

# SMPTE-259M/DVB-ASI Scrambler/Controller

#### **Features**

- Fully compatible with SMPTE-259M

- SMPTE-125M compliant for 4:2:2 component video

- SMPTE-244M compliant for 4fsc composite video

- Fully compatible with DVB-ASI

- Operates from a single +5V or -5V supply

- 44-pin PLCC package

- Encodes both 8- and 10-bit parallel digital streams for any rate from 16–40 M characters/sec (160–400 Mbits/sec serial)

- Operates with CY7B9234 SMPTE HOTLink<sup>™</sup> serializer/transmitter

- X<sup>9</sup> + X<sup>4</sup> + 1 scrambler and NRZI encoder may be bypassed for raw data output

#### **Functional Description**

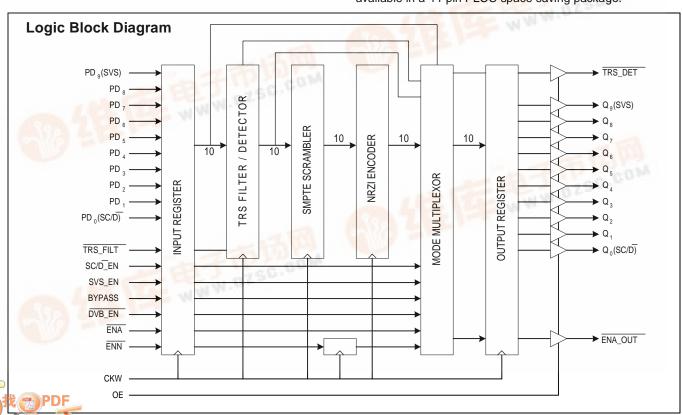

#### **SMPTE-259M Operation**

The CY7C9235 is a CMOS integrated circuit designed to encode SMPTE-125M and SMPTE-244M bit-parallel digital characters (or other data formats) using the SMPTE-259M encoding rules. Following encoding, the characters are output as bit-parallel characters ready for serialization. The encoded outputs of the CY7C9235 are designed to be directly mated to

a CY7B9234 HOTLink transmitter, which then converts the bit-parallel characters into a SMPTE-259M compatible high-speed serial data stream.

This device performs both TRS (sync) detection and filtering, data scrambling with the SMPTE-259M  $\rm X^9 + \rm X^4 + 1$  algorithm, and NRZ-to-NRZI encoding. These functions operate at any character rate from 16- to 40 MHz. For those systems operating with non-SMPTE-259M compliant video streams (or for diagnostic purposes), the scrambler and NRZI encoding functions can be disabled.

#### **DVB-ASI Operation**

The CY7C9235 also contains the necessary multiplexers, control inputs, and outputs, to sequence out a DVB-ASI compliant video stream. DVB-ASI operation is enabled through activation of a single input signal. This allows a single serial output port to support both SMPTE and DVB data streams under software or hardware control.

In DVB-ASI mode the CY7C9235 operates with two enable signals (ENA and ENN) to allow data to be presented from either synchronous (clocked) or asynchronous FIFOs. When data is not available, the CY7C9235 ensures that the proper fill character (K28.5) is generated by the attached CY7B9234 serializer.

The CY7C9235 operates from a single +5V or -5V supply. It is available in a 44-pin PLCC space saving package.

HOTLink is a trademark of Cypress Semiconductor Corporation.

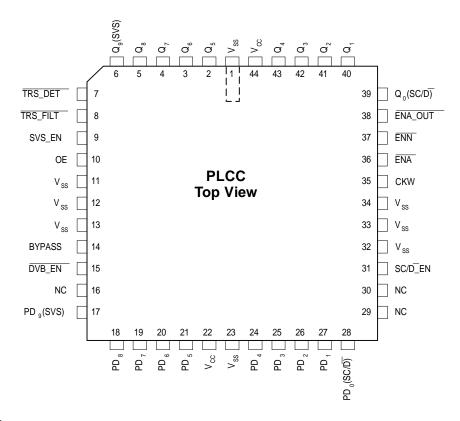

## **Pin Configuration**

## **Maximum Ratings**

| Storage Temperature                                    | 40°C to +125°C |

|--------------------------------------------------------|----------------|

| Supply Voltage to Ground Potential                     | 0.5V to +7.0V  |

| DC Voltage Applied to Outputs in High-Z State          | 0.5V to +7.0V  |

| Output Current into Outputs                            | 16 mA          |

| DC Input Voltage                                       | 0.5V to +7.0V  |

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >2001 V        |

| DC Input Current | ± 20 mA  |

|------------------|----------|

| Latch-Up Current | .>200 mA |

# **Operating Range**

| Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | 5V ± 5%         |

| Industrial | -40°C to +85°C         | 5V ± 10%        |

# **Pin Descriptions**

# CY7C9235 SMPTE-259M Encoder

| Name                    | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENA                     | Input  | Enable Parallel Data. If $\overline{\text{ENA}}$ is LOW at the rising edge of CKW, the data present on the PD <sub>0-9</sub> inputs is latched, and routed to the Q <sub>0-9</sub> outputs. This pin is only interpreted when $\overline{\text{DVB}}_{-}$ EN is active (LOW). If the CY7C9235 is only used in SMPTE-259M mode this signal should be tied to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                         |

| ENN                     | Input  | Enable Next Parallel Data. If $\overline{\text{ENN}}$ is LOW at the rising edge of CKW, the data present on the PD <sub>0-9</sub> inputs at the next rising edge of TXCLK is latched, and routed to the Q <sub>0-9</sub> outputs. This pin is only interpreted when $\overline{\text{DVB}}_{-}\overline{\text{EN}}$ is active (LOW). If the CY7C9235 is only used in SMPTE-259M mode this signal should be tied to V <sub>SS</sub> .                                                                                                                                                                                                                                                                  |

| BYPASS                  | Input  | Bypass SMPTE Encoding. BYPASS is ignored if DVB_EN is active (LOW). If BYPASS is HIGH at the rising edge of CKW (and DVB_EN is HIGH), the data latched into the input register is routed around both the SMPTE scrambler and the NRZI encoder and presented to the output register. If BYPASS is LOW at the rising edge of the CKW clock (and DVB_EN is HIGH), the data present in the input register is routed through the SMPTE scrambler and NRZI encoder.                                                                                                                                                                                                                                         |

| TRS_DET                 | Output | TRS Character Detected. This output indicates when a character used in the TRS sequence is detected in the input register. If the data contains any of the reserved characters of 000–003 or 3FC–3FF in 10-bit hex, the output will be LOW for one clock period. If the character in the input register is any other pattern (or DVB_EN is LOW) this output will remain HIGH.                                                                                                                                                                                                                                                                                                                         |

| TRS_FILT                | Input  | TRS Character Filter. This signal controls an internal filter that converts the low-order two bits of all TRS characters to same state as the upper eight bits. This allows a proper 30-bit TRS ID to be generated when the CY7C9235 is operated with 8-bit or non-standard video streams. When this signal is LOW, all characters from 000–003 are converted to 000, and all characters from 3FC–3FF are converted to 3FF. When TRS_FILT is disabled (HIGH), all characters are passed to the scrambler without modification. This signal has no effect when DVB_EN is active (LOW).                                                                                                                 |

| SVS_EN                  | Input  | Send Violation Symbol Enable. This input is only valid when $\overline{DVB\_EN}$ is active (LOW). If SVS_EN is HIGH and a HIGH input is present on PD $_9$ , Q $_9$ will also be high on a following clock cycle, forcing the CY7B9234 serializer to generate an invalid 8B/10B character. If SVS_EN is LOW, the level present on PD $_9$ is ignored and Q $_9$ is forced to a LOW state.                                                                                                                                                                                                                                                                                                             |

| SC/D_EN                 | Input  | Special Character/Data Select Enable. This input is only valid when $\overline{\text{DVB}_{=}\text{EN}}$ is active (LOW). If SC/D_EN is HIGH and a HIGH input is present on PD <sub>0</sub> , Q <sub>0</sub> will also be high on a following clock cycle, forcing the CY7B9234 serializer to generate an 8B/10B control character as selected by the character present on the PD <sub>8-1</sub> inputs. If SC/D_EN is LOW, the level present on PD <sub>0</sub> is ignored and Q <sub>0</sub> is forced to a LOW (data only) state.                                                                                                                                                                  |

| PD <sub>9</sub> (SVS)   | Input  | Parallel Data 9 or Send Violation Symbol. This is the MSB of the input data field. It is latched in the input register at the rising edge of CKW. When $\overline{\text{DVB}}_{-}\overline{\text{EN}}$ is active (LOW) and SVS_EN is HIGH, this latched input is routed to the output register bit Q <sub>9</sub> (SVS). When $\overline{\text{DVB}}_{-}\overline{\text{EN}}$ is active (LOW) and SVS_EN is LOW, output register bit Q <sub>9</sub> (SVS) is forced to a LOW (zero) level. When DVB_EN is inactive (HIGH), this latched input is routed to the scrambler and NRZI encoder.                                                                                                            |

| PD <sub>8-1</sub>       | Input  | Parallel Data 8 through 1. The signals present at the PD <sub>8-1</sub> inputs are latched in the input register at the rising edge of CKW. When DVB_EN is HIGH, these signals are the middle eight bits of the SMPTE 10-bit data field, and are then routed to the scrambler and NRZI encoder. When DVB_EN is active (LOW), these signals are full DVB-ASI data bus, and are then routed to the Q <sub>8-1</sub> outputs.                                                                                                                                                                                                                                                                            |

| $PD_0(SC/\overline{D})$ | Input  | Parallel Data 0 or Special Code/Data Select. This is the LSB of the input data field. It is latched in the input register at the rising edge of CKW. When $\overline{\text{DVB}}_{-}\text{EN}$ is active (LOW) and SC/ $\overline{\text{D}}_{-}$ EN is HIGH, this input is routed to output register bit Q <sub>0</sub> (SVS). When $\overline{\text{DVB}}_{-}\text{EN}$ is active (LOW) and SC/ $\overline{\text{D}}_{-}$ EN is LOW, output register bit Q <sub>0</sub> (SC/ $\overline{\text{D}}_{-}$ ) is forced to a LOW (zero) level. When $\overline{\text{DVB}}_{-}\text{EN}$ is inactive (HIGH), this input data bit is routed through the input register and the scrambler and NRZI encoder. |

| Q <sub>9</sub> (SVS)    | Output | Output Bit 9. This is the MSB of the output register. It should be connected directly to the CY7B9234 serializer input signal SVS(Dj).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Q <sub>8-1</sub>        | Output | Output Bits 8 through 1. These signals should be connected directly to the CY7B9234 serializer input signals $D_{7-0}$ respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Pin Descriptions (continued)

#### CY7C9235 SMPTE-259M Encoder

| Name                   | I/O    | Description                                                                                                                                                                                                                                                                                                                                        |

|------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Q_0(SC/\overline{D})$ | Output | Output Bit 0. This is the LSB of the output register. It should be connected directly to the CY7B9234 serializer input signal SC/D(Da).                                                                                                                                                                                                            |

| DVB_EN                 | Input  | DVB Mode Enable. This signal is sampled by the rising edge of the CKW clock. If $\overline{\text{DVB\_EN}}$ is active (LOW), the data present on the PD <sub>0-9</sub> , $\overline{\text{ENA}}$ , and $\overline{\text{ENN}}$ inputs are latched and routed to the Q <sub>0-9</sub> and $\overline{\text{ENA\_OUT}}$ outputs.                     |

| CKW                    | Input  | Clock Write. This clock controls all synchronous operations of the CY7C9235. It operates at the character rate which is equivalent to one tenth the serialized bit-rate. This clock also connects directly to the CKW input of the CY7B9234 serializer.                                                                                            |

| ENA_OUT                | Output | Enable Parallel Data Out. This output attached directly to the CY7B9234 $\overline{\text{ENA}}$ input, and identifies when valid data is available at the CY7C9235 outputs. If used only for SMPTE-259M data streams, this output may be left open, with the $\overline{\text{ENA}}$ input to the CY7B9234 directly connected to V <sub>SS</sub> . |

| OE                     | Input  | Output Enable. When this signal is HIGH all outputs are driven to their normal logic levels. When LOW, all outputs are placed in a High-Z state.                                                                                                                                                                                                   |

| V <sub>CC</sub>        |        | Power.                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SS</sub>        |        | Ground.                                                                                                                                                                                                                                                                                                                                            |

### **CY7C9235 Description**

#### **Input Register**

The input register is clocked by the rising edge of CKW. This register captures the data present at the  $PD_{0-9}$  inputs on every clock cycle. In addition to the data inputs, all control inputs except OE are also captured at each rising edge of CKW. This includes BYPASS,  $\overline{DVB\_EN}$ , SVS\_EN, SC/ $\overline{D}$ \_EN,  $\overline{TRS\_DET}$ ,  $\overline{TRS\_FILT}$ ,  $\overline{ENN}$ , and  $\overline{ENA}$ .

#### **TRS Filter**

The TRS Filter is used to convert all 8-bit TRS characters (000–003 and 3FC–3FF in 10-bit hex) to their full 10-bit value. If TRS\_FILT is active (LOW) and any of these values are detected in the input register, the lower two bits are forced to either zeros or ones respectively. This allows the encoder to be used with both 8- and 10-bit SMPTE character streams.

If TRS\_FILT is HIGH, the filter function is disabled and all characters are passed from the input register to the SMPTE scrambler unmodified.

#### **TRS Detector**

When operated in SMPTE mode (DVB\_EN is HIGH), the TRS detector looks for the most significant eight bits of the input register to be either all ones or all zeros. If either of these values are detected, the TRS\_DET output will go LOW following the rising edge of CKW, and remain LOW until a character is detected in the input register that is not all zeros or ones, or DVB\_EN is latched LOW.

#### **SMPTE Scrambler**

The SMPTE scrambler implements a parallel encoded version of a linear-feedback shift register. It encodes the data present in the input register using the  $X^9 + X^4 + 1$  polynomial to increase the transition density of the serial data stream and to decrease the DC-content of the transmitted serial bit stream.

#### NRZI Encoder

The scrambled data is also fed through an NRZ-to-NRZI encoder. This also increases the transition density of the serial data stream, decreases the DC-content of the transmitted serial bit stream, and makes the serial stream insensitive to polarity inversions.

#### **DVB-ASI Operation**

The CY7C9235 is designed to operate in both SMPTE-259M and DVB-ASI environments. When operated in SMPTE-only environments, the DVB control inputs may be tied to either  $V_{CC}$  or  $V_{SS}$  as needed to place them in a known state. When not used for DVB operation, the  $\overline{\text{ENA}}, \ \overline{\text{ENN}}, \ \text{SVS}_{\underline{\text{EN}}}, \ \text{and}$  SC/ $\overline{\text{D}}_{\underline{\text{EN}}}$  inputs many be tied to either  $V_{CC}$  or  $V_{SS}$ .  $\overline{\text{DVB}}_{\underline{\text{EN}}}$  must be tied or driven HIGH.

DVB-ASI operation is enabled by asserting DVB\_EN LOW. This signal is latched by the rising edge of the CKW clock. When the CY7C9235 is placed in DVB mode, the SMPTE and NRZI encoders are bypassed, and the data latched into the input register is routed directly to the output register.

#### Error Propagation

For those DVB-ASI implementations that do not require propagation of detected errors, the  $Q_9$  output may be forced to a zero by setting SVS\_EN LOW. When SVS\_EN is HIGH (and the encoder is in DVB mode) the PD $_9$  data latched into the input register is routed to the output register and to the CY7B9234 SVS input.

#### Command Code Generation

The DVB-ASI interface does not normally transmit any command characters other than the K28.5 code that is used both for synchronization and as a fill character when data is not being transmitted. These K28.5 characters may be generated by two methods; by controlling when the CY7C9235 is enabled

PRELIMINARY

CY7C9235

using the ENA and ENN inputs, or by placing a C5.0 character on the PD<sub>9-0</sub> inputs when one of the two enables is active.

If the gen<u>eration of K28.5 fill characters</u> is to be controlled using the  $\overline{\text{ENA}}$  or  $\overline{\text{ENN}}$  inputs, the SC/ $\overline{\text{D}}$ \_EN input should be driven LOW or connected to V<sub>SS</sub>. This will insure that the PD $_0$  data bit is not routed to the output register by forcing the Q<sub>0</sub> output to always be LOW.

If the generation of a K28.5 characters is controlled by transmission of a C5.0 character, the  $SC/\overline{D}_{-}EN$  input must be HIGH to allow the  $PD_0$  input to be propagated to the  $Q_0$  output.

## **Electrical Characteristics** Over the Operating Range

| Parameter       | Description                                   | Test Conditions                                                        | Min. | Max. | Unit |

|-----------------|-----------------------------------------------|------------------------------------------------------------------------|------|------|------|

| V <sub>OH</sub> | Output HIGH Voltage                           | $V_{CC}$ =Min., $I_{OH}$ = $-3.2$ mA                                   | 2.4  |      | V    |

| V <sub>OL</sub> | Output LOW Voltage                            | V <sub>CC</sub> =Min., I <sub>OL</sub> = 16.0 mA                       |      | 0.5  | V    |

| V <sub>IH</sub> | Input HIGH Voltage                            | Guaranteed Input Logical HIGH<br>Voltage for all Inputs <sup>[1]</sup> | 2.0  | 7.0  | V    |

| V <sub>IL</sub> | Input LOW Voltage                             | Guaranteed Input Logical HIGH Voltage for all Inputs <sup>[1]</sup>    | -0.5 | 0.8  | V    |

| I <sub>IX</sub> | Input Load Current                            | $V_I = V_{CC}$ or $V_{SS}$                                             | -10  | +10  | μΑ   |

| I <sub>OZ</sub> | Output Leakage Current                        | $V_O = V_{CC}$ or $V_{SS}$                                             | -50  | +50  | μΑ   |

| I <sub>OS</sub> | Output Short Circuit Current <sup>[2,3]</sup> | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.5V                        | -10  | -80  | mA   |

| I <sub>CC</sub> | Power Supply Current                          | $V_{IN}$ , $V_{I/O} = V_{CC}$ or $V_{SS}$                              |      |      | mA   |

# Capacitance<sup>[3]</sup>

| Parameter        | Description        | Test Conditions                      | Max. | Unit |

|------------------|--------------------|--------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 5.0V at f = 1 MHz  | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 5.0V at f = 1 MHz | 12   | pF   |

#### Notes:

- These are absolute values with respect to device ground. All overshoots due to system or tester noise are included. Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second.  $V_{OUT} = 0.5V$  has been chosen to avoid test 1. 2. problems caused by tester ground degradation.

Tested initially and after any design or process changes that may affect these parameters.

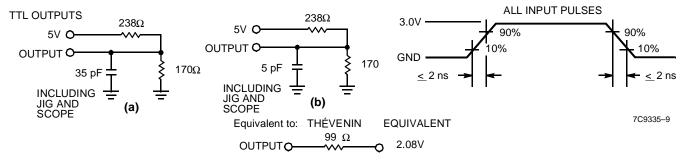

## **AC Test Loads and Waveforms**

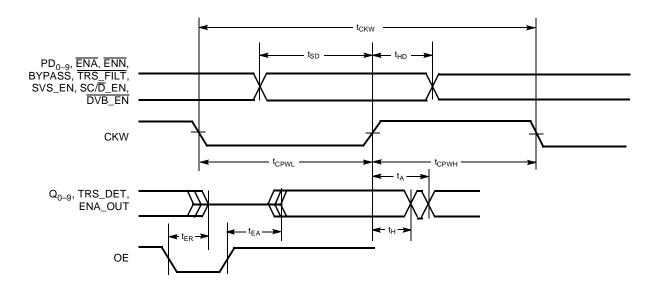

## Switching Characteristics Over the Operating Range<sup>[4]</sup>

|                   |                                        | CY7C9 | CY7C9235-27 CY |      | CY7C9235-40 |      |

|-------------------|----------------------------------------|-------|----------------|------|-------------|------|

| Parameter         | Description                            | Min.  | Max.           | Min. | Max.        | Unit |

| t <sub>SD</sub>   | Data Set-Up Time                       | 10    |                | 8    |             | ns   |

| t <sub>HD</sub>   | Data Hold Time                         | 0     |                | 0    |             | ns   |

| t <sub>CPWH</sub> | CKW Pulse Width HIGH                   | 6.5   |                | 6.5  |             | ns   |

| t <sub>CPWL</sub> | CPW Pulse Width LOW                    | 6.5   |                | 6.5  |             | ns   |

| t <sub>CKW</sub>  | Write Clock Period                     | 30    | 62.5           | 25   | 62.5        | ns   |

| t <sub>A</sub>    | Access Time                            |       | 10             |      | 8           | ns   |

| t <sub>H</sub>    | Data Output Hold Time From CKW Rise    | 4     |                | 3    |             | ns   |

| t <sub>EA</sub>   | Input to Output Enable                 |       | 23             |      | 20          | ns   |

| t <sub>ER</sub>   | Input to Output Disable <sup>[5]</sup> |       | 23             |      | 20          | ns   |

#### Notes:

- All AC parameters are with all outputs switching.

Test load (b) used for this parameter. Test load (a) used for all other AC parameters.

# **Switching Waveform**

# **Ordering Information**

| Ordering Code  | Package<br>Name | Package Type                       | Operating<br>Range |

|----------------|-----------------|------------------------------------|--------------------|

| CY7C9235-270JC | J67             | 44-pin Plastic Leaded Chip Carrier | Commercial         |

| CY7C9235-400JC | J67             | 44-pin Plastic Leaded Chip Carrier | Commercial         |

Document #: 38-00571-A

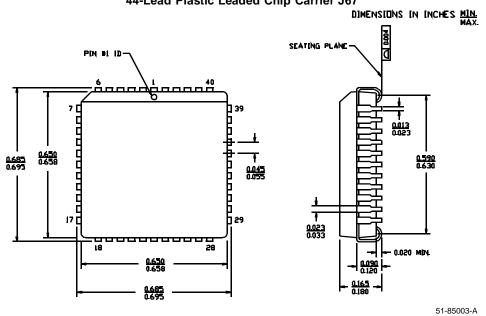

# Package Diagram

## 44-Lead Plastic Leaded Chip Carrier J67