CONNECTION DIAGRAM PINOUT A

LOGIC SYMBOL

X4 1

Cn 2

X3 3

X2 4

X1 5

**X**0 6

So 8

81 9

S2 10 S<sub>3</sub> 11 24 Vcc

23 Y\_1 22 Yo

21 Yı

20 P

19 Ko

18 Kı

17 K2

15 S<sub>5</sub>

14 S4 13 Cn.

16 K<sub>2</sub>

## 93543

## 4-BIT BY 2-BIT TWOS COMPLEMENT MULTIPLIER

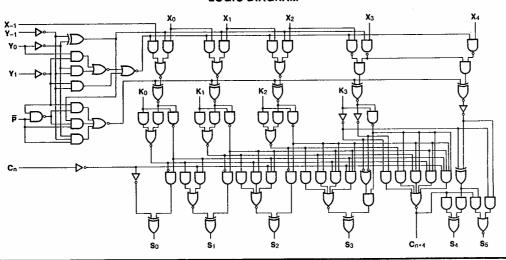

**DESCRIPTION** — The '43 is a high speed twos complement multiplier. The device is a 4-bit by 2-bit building block that can be connected in an iterative array to perform multiplication of two binary numbers of variable lengths. The device can generate the twos complement product, without correction, of two binary numbers presented in twos complement notation.

- VERY HIGH SPEED MULTIPLICATION TWO 12-BIT NUMBERS IN 125 ns (TYP)

- PROVIDES TWOS COMPLEMENT PRODUCT WITHOUT CORRECTION

- EXPANDS TO ANY SIZE ARRAY WITHOUT ADDITIONAL COMPONENTS

- ACCEPTS ACTIVE HIGH OR ACTIVE LOW OPERANDS

- EASILY CORRECTABLE FOR UNSIGNED, SIGN-MAGNITUDE OR

|                    |     | E: See Section 9                                                                        | N                                                                                                       |      | 23    |   | 7 6 | 5<br>X1 | 4 3<br>1 1<br>X <sub>2</sub> X <sub>3</sub> |                | L           | 17 16<br>k <sub>2</sub> k <sub>3</sub> | W |

|--------------------|-----|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-------|---|-----|---------|---------------------------------------------|----------------|-------------|----------------------------------------|---|

| PKGS               | PIN | COMMERCIAL GRADE                                                                        | MILITARY GRADE                                                                                          | PKG  | 22    |   |     |         |                                             |                |             | Cn ·                                   |   |

|                    | OUT | $V_{CC} = +5.0 \text{ V} \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C} \text{ to } +125^{\circ} \text{ C}$ | TYPE | 20 —0 | Р | So  | Ş:      | Sz                                          | S <sub>3</sub> | <b>\$</b> 4 | <b>S</b> 5                             |   |

| Plastic<br>DIP (P) | Α   | 93S43PC                                                                                 | W. GZSG. COM                                                                                            | 9N   |       |   | 8   | 9       | 10                                          | 11             | 14          | 15                                     |   |

| Ceramic<br>DIP (D) | А   | 93S43DC                                                                                 | 93S43DM                                                                                                 | 6N   |       |   |     |         | ; = I<br>D =                                |                |             |                                        |   |

| Flatpak            | A   | 93S43FC                                                                                 | 93S43FM                                                                                                 | 4M   |       |   |     |         |                                             |                |             |                                        |   |

## INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                       | DESCRIPTION                                           | 93S (U.L.)<br>HIGH/LOW |  |

|---------------------------------|-------------------------------------------------------|------------------------|--|

| X-1, X3, X4                     | Multiplicand Inputs                                   | 1.0/1.0                |  |

| X0, X1, X2                      | Multiplicand Inputs                                   | 2.0/2.0                |  |

| Y <sub>0</sub>                  | Multiplier Input                                      | 2.0/2.0                |  |

| y_1, y1                         | Multiplier Inputs                                     | 1.0/1.0                |  |

| k <sub>0</sub> — k <sub>3</sub> | Constant Inputs                                       | 2.0/2.0                |  |

|                                 | Carry Input                                           | 1.0/1.0                |  |

| Cn<br>₱                         | Polarity Control Input (Active LOW for HIGH Operands) | 3.0/3.0                |  |

| S <sub>0</sub> — S <sub>5</sub> | Product Outputs                                       | 25/12.5                |  |

| Cn + 4                          | Carry Output                                          | 25/12.5                |  |

(F)

**FUNCTIONAL DESCRIPTION** — The '43 is a super fast hardware multiplier employing Schottky technology and twos complement arithmetic. It multiplies a multiplicand of four bits by a multiplier of two bits and forms a basic iterative logic cell. It can also multiply in active HIGH (positive logic) or active LOW (negative logic) representations by reinterpreting the active levels of the inputs, outputs and the Polarity Control ( $\overline{P}$ ). The binary number with 1 as the most significant bit is treated as a negative number represented in twos complement form. These '43 iterative logic cells can be connected to implement multiplication of an X-bit number by a Y-bit number. This application requires  $X \bullet Y \div 4 \bullet 2$  packages and the resulting product has X + Y bits. At the beginning of the array, a constant can be presented at the K inputs that will be added to the least significant part of the product. The packages can be connected in parallel, triangular or split-array scheme depending on the speed requirement. The '41 ALU can be used with these multipliers in the split-array scheme to obtain high speed multiplication.

TABLE I SWITCHING TEST CONDITIONS

| INPUT                                               | OUTPUTS                                                                                                                                                                                                                                                                 | INPUTS AT 0 V (Remaining Inputs at 4.5 V)                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cn                                                  | Cn + 4, S0 - S3, S4, S5                                                                                                                                                                                                                                                 | P, y−1, y1, All x                                                                                                                                                                                                                                                                                                                  |

| ko<br>k1<br>k2<br>k3<br>k3                          | Cn + 4, S0 — S3, S4, S5<br>Cn + 4, S1 — S3, S4, S5<br>Cn + 4, S2, S3, S4, S5<br>S3<br>S4, S5                                                                                                                                                                            | 戸, y-1, y1, All x   戸, y-1, y1, All x, Cn                                                                                                                                                                                                          |

| X-1<br>X0<br>X1<br>X2<br>X3, X4<br>X3, X4<br>X3, X4 | Cn + 4, S0 — S3, S4, S5<br>Cn + 4, S0 — S3, S4, S5<br>Cn + 4, S1 — S3, S4, S5<br>Cn + 4, S2, S3, S4, S5<br>S3<br>S4, S5<br>S4, S5                                                                                                                                       | P, y <sub>1</sub> , All k<br>P, y <sub>-</sub> 1, y <sub>1</sub> , All k, C <sub>n</sub><br>P, y <sub>-</sub> 1, All k, C <sub>n</sub> |

| У–1<br>У0<br>У1                                     | C <sub>n</sub> + 4, S <sub>0</sub> — S <sub>3</sub> , S <sub>4</sub> , S <sub>5</sub><br>C <sub>n</sub> + 4, S <sub>0</sub> — S <sub>3</sub> , S <sub>4</sub> , S <sub>5</sub><br>C <sub>n</sub> + 4, S <sub>0</sub> — S <sub>3</sub> , S <sub>4</sub> , S <sub>5</sub> | F, x1, x2, x3, x4, All k   F, x1, x2, x3, x4, All k   x0, x1, x2, x3, x4, All k                                                                                                                                                                                                                                                    |

## LOGIC DIAGRAM

| DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified) |                      |     |     |       |                       |  |  |

|----------------------------------------------------------------------------------|----------------------|-----|-----|-------|-----------------------|--|--|

| SYMBOL                                                                           | PARAMETER            | 9   | 38  | UNITS | CONDITIONS            |  |  |

| 31 MDOL                                                                          | I VIONE I and        | Min | Max | ]     |                       |  |  |

| lcc                                                                              | Power Supply Current |     | 149 | mA    | V <sub>CC</sub> = Max |  |  |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C (See Section 3 for waveforms and load configurations)

|                | PARAMETER                                                              | 9                | 93S<br>C <sub>L</sub> = 15 pF |    | CONDITIONS     |

|----------------|------------------------------------------------------------------------|------------------|-------------------------------|----|----------------|

| SYMBOL         |                                                                        | C <sub>L</sub> = |                               |    |                |

|                |                                                                        | Min              | Max                           | 1  |                |

| tplH<br>tpHL   | Propagation Delay<br>C <sub>n</sub> to C <sub>n</sub> + 4              |                  | 9.0<br>9.0                    | ns | Figs. 3-1, 3-5 |

| tplH ,<br>tpHL | Propagation Delay<br>Cn to So — S3                                     |                  | 13<br>11                      | ns | Figs. 3-1, 3-4 |

| tpLH<br>tpHL   | Propagation Delay<br>C <sub>n</sub> to S <sub>4</sub> , S <sub>5</sub> |                  | 16<br>15                      | ns | Figs. 3-1, 3'4 |

| tplH<br>tpHL   | Propagation Delay<br>k <sub>n</sub> to C <sub>n</sub> + 4              |                  | 12<br>13                      | ns | Figs. 3-1, 3-5 |

| tpLH<br>tpHL   | Propagation Delay<br>k <sub>n</sub> to S <sub>0</sub> — S <sub>3</sub> |                  | 14<br>12                      | ns | Figs. 3-1, 3-5 |

| tpLH<br>tpHL   | Propagation Delay<br>k <sub>n</sub> to S <sub>4</sub> , S <sub>5</sub> |                  | 19<br>17                      | ns | Figs. 3-1, 3-4 |

| tplH<br>tpHL   | Propagation Delay<br>x <sub>n</sub> to C <sub>n</sub> + 4              |                  | 15<br>24                      | ns | Figs. 3-1, 3-5 |

| tpLH<br>tpHL   | Propagation Delay<br>x <sub>n</sub> to S <sub>0</sub> — S <sub>3</sub> |                  | 25<br>25                      | ns | Figs. 3-1, 3-4 |

| tplH<br>tpHL   | Propagation Delay<br>x <sub>n</sub> to S <sub>4</sub> , S <sub>5</sub> |                  | 30<br>21                      | ns | Figs. 3-1, 3-4 |

| tplH<br>tpHL   | Propagation Delay<br>y <sub>n</sub> to C <sub>n</sub> + 4              |                  | 25<br>27                      | ns | Figs. 3-1, 3-5 |

| tplH<br>tpHL   | Propagation Delay<br>y <sub>n</sub> to S <sub>0</sub> — S <sub>3</sub> |                  | 28<br>27                      | ns | Figs. 3-1, 3-4 |

| tPLH<br>tPHL   | Propagation Delay<br>y <sub>n</sub> to S <sub>4</sub> , S <sub>5</sub> |                  | 32<br>30                      | ns | Figs. 3-1, 3-4 |