# L4975A

# **5A SWITCHING REGULATOR**

**MULTIPOWER BCD TECHNOLOGY**

- 5A OUTPUT CURRENT

- 5.1V TO 40V OUTPUT VOLTAGE RANGE

- 0 TO 90% DUTY CYCLE RANGE

- INTERNAL FEED-FORWARD LINE REGULA-TION

W.OZSC.COM

- INTERNAL CURRENT LIMITING

- PRECISE 5.1V ± 2% ON CHIP REFERENCE

- RESET AND POWER FAIL FUNCTIONS

- SOFT START

- INPUT/OUTPUT SYNC PIN

- UNDER VOLTAGE LOCK OUT WITH HYS-TERETIC TURN-ON

- PWM LATCH FOR SINGLE PULSE PER PERIOD

- VERY HIGH EFFICIENCY

- SWITCHING FREQUENCY UP TO 500KHz

- THERMAL SHUTDOWN

- CONTINUOUS MODE OPERATION

#### DESCRIPTION

The L4975A is a stepdown monolithic power switching regulator delivering 5A at a voltage variable from 5.1 to 40V.

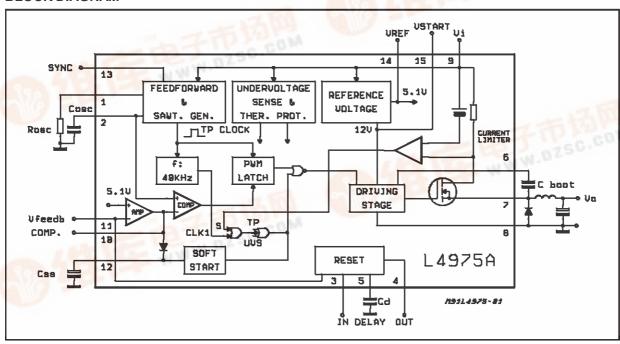

#### **BLOCK DIAGRAM**

Realized with BCD mixed technology, the device uses a DMOS output transistor to obtain very high efficiency and very fast switching times. Features of the L4975A include reset and power fail for microprocessors, feed forward line regulation, soft start, limiting current and thermal protection. The device is mounted in a 15-lead multiwatt plastic power package and requires few external components. Efficient operation at switching frequencies up to 500KHz allows reduction in the size and cost of external filter components.

June 2000

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                               | Parameter                                                     | Value                     | Unit |

|----------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|------|

| V <sub>9</sub>                                                       | Input Voltage                                                 | 55                        | V    |

| V <sub>9</sub>                                                       | Input Operating Voltage                                       | 50                        | V    |

| V <sub>7</sub>                                                       | Output DC Voltage Output Peak Voltage at t = 0.1µs f = 200KHz | -1<br>-7                  | V    |

| l <sub>7</sub>                                                       | Maximum Output Current                                        | Internally Limited        |      |

| $V_6$                                                                | Bootstrap Voltage Bootstrap Operating Voltage                 | 65<br>V <sub>9</sub> + 15 | V    |

| V <sub>3</sub> , V <sub>12</sub>                                     | Input Voltage at Pins 3, 12                                   | 12                        | V    |

| $V_4$                                                                | Reset Output Voltage                                          | 50                        | V    |

| l <sub>4</sub>                                                       | Reset Output Sink Current                                     | 50                        | mA   |

| V <sub>5</sub> , V <sub>10</sub> , V <sub>11</sub> , V <sub>13</sub> | Input Voltage at Pin 5, 10, 11, 13                            | 7                         | V    |

| l <sub>5</sub>                                                       | Reset Delay Sink Current                                      | 30                        | mA   |

| I <sub>10</sub>                                                      | Error Amplifier Output Sink Current                           | 1                         | Α    |

| I <sub>12</sub>                                                      | Soft Start Sink Current                                       | 30                        | mA   |

| P <sub>tot</sub>                                                     | Total Power Dissipation at T <sub>case</sub> < 120°C          | 30                        | W    |

| T <sub>j</sub> , T <sub>stg</sub>                                    | Junction and Storage Temperature                              | -40 to 150                | °C   |

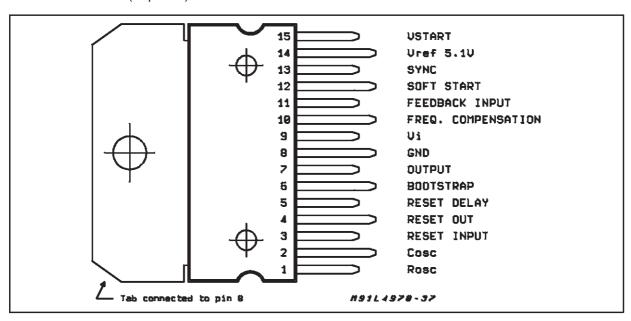

# PIN CONNECTION (Top view)

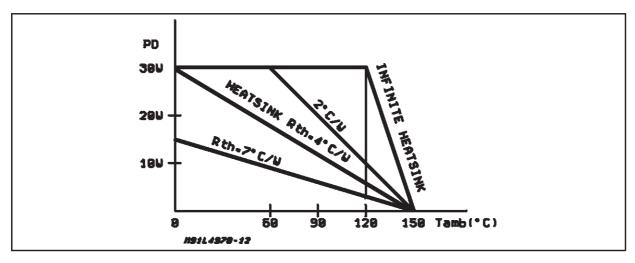

#### THERMAL DATA

| Symbol                 | Parameter                           |     | Value | Unit |

|------------------------|-------------------------------------|-----|-------|------|

| R <sub>th i-case</sub> | Thermal Resistance Junction-case    | max | 1     | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient | max | 35    | °C/W |

#### **PIN FUNCTIONS**

| N° | Name                      | Function                                                                                                                                                                                                                                  |

|----|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

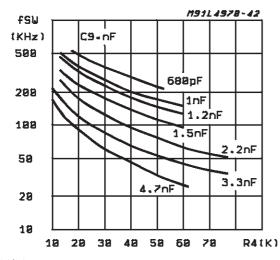

| 1  | OSCILLATOR                | $R_{\text{osc}}$ . External resistor connected to ground determines the constant charging current of $C_{\text{osc}}$ .                                                                                                                   |

| 2  | OSCILLATOR                | $C_{\text{osc}}$ . External capacitor connected to ground determines (with $R_{\text{osc}}$ ) the switching frequency.                                                                                                                    |

| 3  | RESET INPUT               | Input of Power Fail Circuit. The threshold is $5.1V$ . It may be connected via a divider to the input for power fail function. It must be connected to the pin $14$ an external $30K\Omega$ resistor when power fail signal not required. |

| 4  | RESET OUT                 | Open Collector Reset/power Fail Signal Output. This output is high when the supply and the output voltages are safe.                                                                                                                      |

| 5  | RESET DELAY               | A $C_{\text{d}}$ capacitor connected between this terminal and ground determines the reset signal delay time.                                                                                                                             |

| 6  | BOOTSTRAP                 | A C <sub>boot</sub> capacitor connected between this terminal and the output allows to drive properly the internal D-MOS transistor.                                                                                                      |

| 7  | OUTPUT                    | Regulator Output.                                                                                                                                                                                                                         |

| 8  | GROUND                    | Common Ground Terminal                                                                                                                                                                                                                    |

| 9  | SUPPLY VOLTAGE            | Unregulated Input Voltage.                                                                                                                                                                                                                |

| 10 | FREQUENCY<br>COMPENSATION | A series RC network connected between this terminal and ground determines the regulation loop gain characteristics.                                                                                                                       |

| 11 | FEEDBACK INPUT            | The Feedback Terminal of the Regulation Loop. The output is connected directly to this terminal for 5.1V operation; It is connected via a divider for higher voltages.                                                                    |

| 12 | SOFT START                | Soft Start Time Constant. A capacitor is connected between thi sterminal and ground to define the soft start time constant.                                                                                                               |

| 13 | SYNC INPUT                | Multiple L4975A are synchronized by connecting pin 13 inputs together or via an external syncr. pulse.                                                                                                                                    |

| 14 | V <sub>ref</sub>          | 5.1V V <sub>ref</sub> Device Reference Voltage.                                                                                                                                                                                           |

| 15 | V <sub>start</sub>        | Internal Start-up Circuit to Drive the Power Stage.                                                                                                                                                                                       |

# **CIRCUIT OPERATION** (refer to the block diagram)

The L4975A is a 5A monolithic stepdown switching regulator working in continuous mode realized in the new BCD Technology. This technology allows the integration of isolated vertical DMOS power transistors plus mixed CMOS/Bipolar transistors.

The device can deliver 5A at an output voltage adjustable from 5.1V to 40V, and contains diagnostic and control functions that make it particularly suitable for microprocessor based systems.

#### **BLOCK DIAGRAM**

The block diagram shows the DMOS power transistor and the PWM control loop. Integrated functions include a reference voltage trimmed to  $5.1V\pm2\%$ , soft start, undervoltage lockout, oscillator with feedforward control, pulse by pulse current limit, thermal shutdown and finally the reset and power fail circuit. The reset and power fail circuit provides an output signal for a microprocessor indicating the status of the system.

Device turn on is around 11V with a typical 1V hysteresis, this threshold provides a correct voltage for the driving stage of the DMOS gate and the hysteresis prevents instabilities.

An external bootstrap capacitor charged to 12V by an internal voltage reference is needed to provide correct gate drive to the power DMOS. The driving circuit is able to source and sink peak currents of around 0.5A to the gate of the DMOS transistor. A typical switching time of the current in the DMOS transistor is 50ns. Due to the fast commutation switching frequencies up to 500kHz are possible.

The PWM control loop consists of a sawtooth oscillator, error amplifier, comparator, latch and the output stage. An error signal is produced by comparing the output voltage with the precise  $5.1V\pm2\%$  on chip reference. This error signal is then compared with the sawtooth oscillator, in order to generate a fixed frequency pulse width modulated drive for the output stage. A PWM latch is included to eliminate multiple pulsing within a period even in noisy environments. The gain and

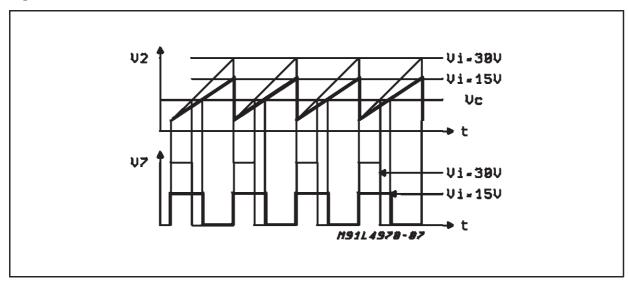

Figure 1: Feedforward Waveform

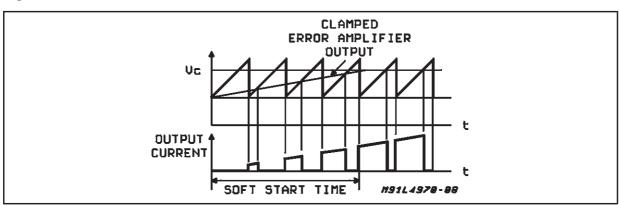

Figure 2: Soft Start Function

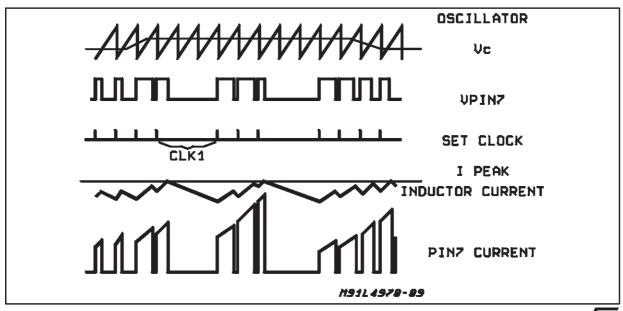

Figure 3: Limiting Current Function

stability of the loop can be adjusted by an external RC network connected to the output of the error amplifier. A voltage feedforward control has been added to the oscillator, this maintains superior line regulation over a wide input voltage range. Closing the loop directly gives an output voltage of 5.1V, higher voltages are obtained by inserting a voltage divider.

At turn on output overcurrents are prevented by the soft start function (fig. 2). The error amplifier is initially clamped by an external capacitor Css and allowed to rise linearly under the charge of an internal constant current source.

Output overload protection is provided by a current limit circuit (fig. 3). The load current is sensed by an internal metal resistor connected to a comparator. When the load current exceeds a preset threshold the output of the comparator sets a flip flop which turns off the power DMOS. The next clock pulse, from an internal 40kHz oscillator will reset the flip flop and the power DMOS will again conduct. This current protection method, ensures

a constant current output when the system is overloaded or short circuited and limits the switching frequency, in this condition, to 40kHz.

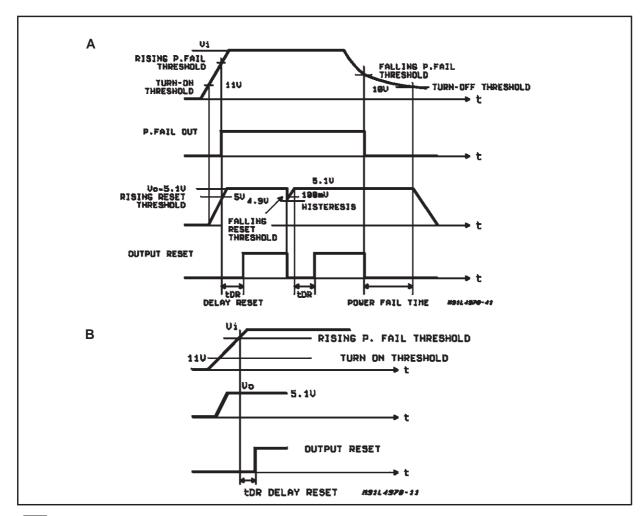

The Reset and Power fail circuitry (fig 4) generates an output signal when the supply voltage exceeds a threshold programmed by an external voltage divider. The reset signal, is generated with a delay time programmed by an external capacitor on the delay pin. When the supply voltage falls below the threshold or the output voltage goes below 5V the reset output goes low immediately. The reset output is an open collector-drain.

Fig 4A shows the case when the supply voltage is higher than the threshold, but the output voltage is not yet 5V.

Fig 4B shows the case when the output is 5.1V but the supply voltage is not yet higher than the fixed threshold.

The thermal protection disables circuit operation when the junction temperature reaches about 150°C and has an hysterysis to prevent unstable conditions.

Figure 4: Reset and Power Fail Functions.

**ELECTRICAL CHARACTERISTICS** (Refer to the test circuit,  $T_j = 25^{\circ}C$ ,  $V_i = 35V$ ,  $R_4 = 16K\Omega$ ,  $C_9 = 2.2nF$ ,  $f_{SW} = 200KHz$  typ, unless otherwise specified) DYNAMIC CHARACTERISTICS

| Symbol                        | Parameter                                      | Test Condition                                                            | Min. | Тур.        | Max.       | Unit     | Fig. |

|-------------------------------|------------------------------------------------|---------------------------------------------------------------------------|------|-------------|------------|----------|------|

| Vi                            | input Voltage Range (pin 9)                    | $V_o = V_{ref}$ to 40V<br>$I_o = 5A$                                      | 15   |             | 50         | V        | 5    |

| Vo                            | Output Votage                                  | $V_i = 15V \text{ to } 50V$<br>$I_0 = 3A; V_0 = V_{re}f$                  | 5    | 5.1         | 5.2        | V        | 5    |

| $\Delta V_{o}$                | Line Regulation                                | $V_i = 15V \text{ to } 50V$<br>$I_0 = 2A; V_0 = V_{re}f$                  |      | 12          | 30         | mV       | 5    |

| $\Delta V_{o}$                | Load Regulation                                | $V_o = V_{ref}$<br>$I_o = 2A \text{ to } 4A$<br>$I_o = 1A \text{ to } 5A$ |      | 10<br>20    | 30<br>50   | mV<br>mV | 5    |

| $V_d$                         | Dropout Voltage Between<br>Pin 9 and 7         | I <sub>o</sub> = 3A<br>I <sub>o</sub> = 5A                                |      | 0.4<br>0.55 | 0.6<br>0.8 | V<br>V   | 5    |

| I <sub>7L</sub>               | Max. Limiting Current                          | $V_i = 15 \text{ to } 50V$<br>$V_0 = V_{\text{ref}} \text{ to } 40V$      | 5.5  | 6.5         | 7.5        | А        | 5    |

| η                             | Efficiency                                     | $I_{o} = 3A$ $V_{o} = V_{ref}$ $V_{o} = 12V$                              | 70   | 75<br>80    |            | %<br>%   | 5    |

|                               |                                                | $I_o = 5A$ $V_o = V_{ref}$ $V_o = 12V$                                    | 80   | 85<br>92    |            | %<br>%   | 5    |

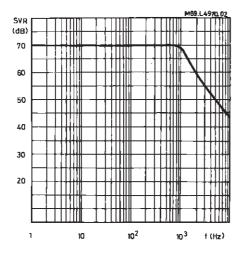

| SVR                           | Supply Voltage Ripple Reject.                  | $V_i = 2VRMS$ ; $I_o = 3A$<br>$f = 100Hz$ ; $V_o = V_{ref}$               | 56   | 60          |            | dB       | 5    |

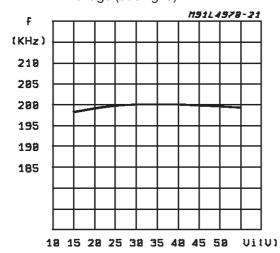

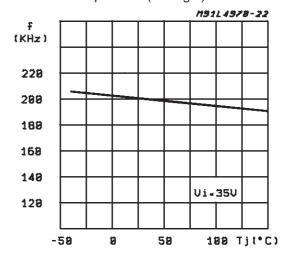

| f                             | Switching Frequency                            |                                                                           | 180  | 200         | 220        | KHz      | 5    |

| $\frac{\Delta f}{\Delta V_i}$ | Voltage Stability of<br>Swiching Frequency     | $V_i = 15V$ to $45V$                                                      |      | 2           | 6          | %        | 5    |

| $\frac{\Delta f}{T_j}$        | Temperature Stability of<br>Swiching Frequency | $T_j = 0 \text{ to } 125^{\circ}\text{C}$                                 |      | 1           |            | %        | 5    |

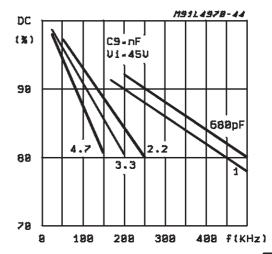

| f <sub>max</sub>              | Maximum Operating<br>Switching Frequency       | $V_{o} = V_{ref}; R_{4} = 10K\Omega$<br>$I_{o} = 5A; C_{9} = 1nF$         | 500  |             |            | KHz      | 5    |

# V<sub>ref</sub> SECTION (pin 14)

| Symbol                           | Parameter                                               | Test Condition              | Min. | Тур. | Max. | Unit  | Fig. |

|----------------------------------|---------------------------------------------------------|-----------------------------|------|------|------|-------|------|

| V <sub>14</sub>                  | Reference Voltage                                       |                             | 5    | 5.1  | 5.2  | V     | 7    |

| $\Delta V_{14}$                  | Line Regulation                                         | V <sub>i</sub> = 15V to 50V |      | 10   | 25   | mV    | 7    |

| $\Delta V_{14}$                  | Load Regulation                                         | I <sub>14</sub> = 0 to 1mA  |      | 20   | 40   | mV    | 7    |

| $\frac{\Delta V_{14}}{\Delta T}$ | Average Temperature<br>Coefficient Reference<br>Voltage | $T_j = 0$ °C to 125°C       |      | 0.4  |      | mV/°C | 7    |

| I <sub>14 short</sub>            | Short Circuit Current Limit                             | $V_{14} = 0$                |      | 70   |      | mA    | 7    |

# V<sub>START</sub> SECTION (pin 15)

| Symbol                | Parameter                   | Test Condition             | Min. | Тур. | Max. | Unit | Fig. |

|-----------------------|-----------------------------|----------------------------|------|------|------|------|------|

| V <sub>15</sub>       | Reference Voltage           |                            | 11.4 | 12   | 12.6 | V    | 7    |

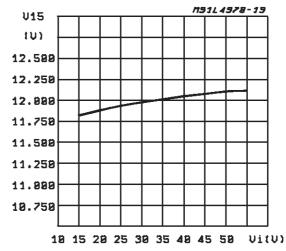

| $\Delta V_{15}$       | Line Regulation             | V <sub>i</sub> = 15 to 50V |      | 0.6  | 1.4  | V    | 7    |

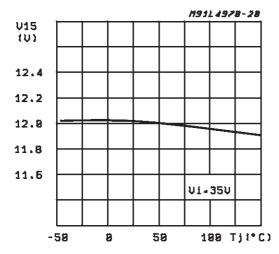

| $\Delta V_{15}$       | Load Regulation             | I <sub>15</sub> = 0 to 1mA |      | 50   | 200  | mV   | 7    |

| I <sub>15 short</sub> | Short Circuit Current Limit | V <sub>15</sub> = 0V       |      | 80   |      | mA   | 7    |

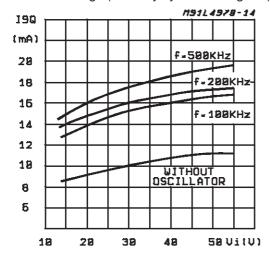

# **ELECTRICAL CHARACTERISTICS** (continued)

# DC CHARACTERISTICS

| Symbol              | Parameter                | Test Condition                        | Min. | Тур. | Max. | Unit | Fig. |

|---------------------|--------------------------|---------------------------------------|------|------|------|------|------|

| V <sub>9on</sub>    | Turn-on Threshold        |                                       | 10   | 11   | 12   | V    | 7A   |

| V <sub>9 Hyst</sub> | Turn-off Hysteresys      |                                       |      | 1    |      | V    | 7A   |

| I <sub>9Q</sub>     | Quiescent Current        | $V_{12} = 0$ ; $S1 = D$               |      | 13   | 19   | mA   | 7A   |

| I <sub>9OQ</sub>    | Operating Supply Current | V <sub>12</sub> = 0; S1 = C; S2 = B   |      | 16   | 23   | mA   | 7A   |

| I <sub>7L</sub>     | Out Leak Current         | $V_i = 55V$ ; $S3 = A$ ; $V_{12} = 0$ |      |      | 2    | mA   | 7A   |

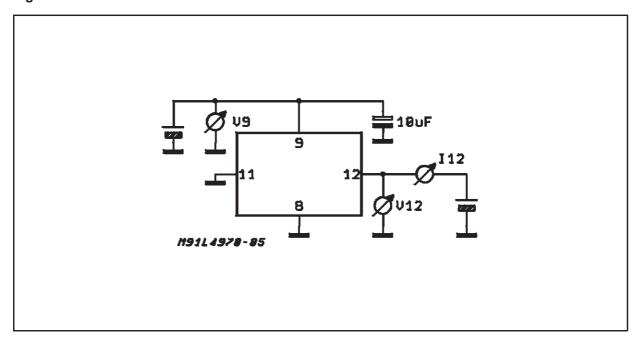

### SOFT START

| Symbol          | Parameter                 | Test Condition                             | Min. | Тур. | Max. | Unit | Fig. |

|-----------------|---------------------------|--------------------------------------------|------|------|------|------|------|

| I <sub>12</sub> | Soft Start Source Current | $V_{12} = 3V; V_{11} = 0V$                 | 70   | 100  | 130  | μΑ   | 7B   |

| V <sub>12</sub> | Output Saturation Voltage | $I_{12} = 20 \text{mA}; V_9 = 10 \text{V}$ |      |      | 1    | V    | 7B   |

|                 |                           | $I_{12} = 200 \mu A; V_9 = 10 V$           |      |      | 0.7  | V    | 7B   |

### **ERROR AMPLIFIER**

| Symbol           | Parameter                | Test Condition                                         | Min. | Тур. | Max. | Unit | Fig. |

|------------------|--------------------------|--------------------------------------------------------|------|------|------|------|------|

| V <sub>10H</sub> | High Level Out Voltage   | $I_{10} = -100\mu A; S1 = C$<br>$V_{11} = 4.7V$        | 6    |      |      | V    | 7C   |

| V <sub>10L</sub> | Low Level Out Voltage    | $I_{10} = +100\mu A; S1 = C$<br>$V_{11} = 5.3V;$       |      |      | 1.2  | V    | 7C   |

| I <sub>10H</sub> | Source Output Current    | $V_{10} = 1V; S1 = E$<br>$V_{11} = 4.7V$               | 100  | 150  |      | μΑ   | 7C   |

| I <sub>10L</sub> | Sink Output Current      | V <sub>10</sub> = 6V; S1 = D<br>V <sub>11</sub> = 5.3V | 100  | 150  |      | μΑ   | 7C   |

| I <sub>11</sub>  | Input Bias Current       | $R_S = 10K\Omega$                                      |      | 0.4  | 3    | μΑ   | _    |

| G <sub>V</sub>   | DC Open Loop Gain        | $V_{VCM} = 4V;$<br>$R_S = 10\Omega$                    | 60   |      |      | dB   | -    |

| SVR              | Supply Voltage Rejection | $15 < V_i < 50V;$<br>$R_S = 10\Omega$                  | 60   | 80   |      | dB   | _    |

| Vos              | Input Offset Voltage     | $R_S = 50\Omega$                                       |      | 2    | 10   | mV   | _    |

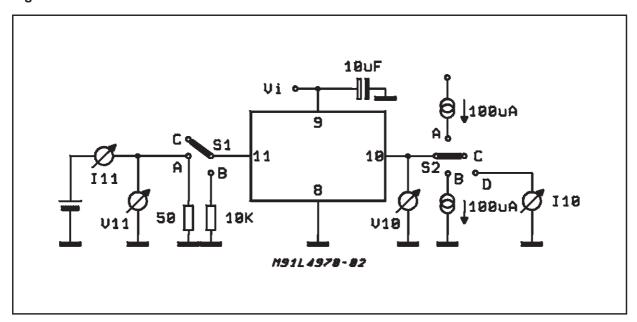

# RAMP GENERATOR (pin 2)

| Symbol         | Parameter         | Test Condition                 |             | Min. | Тур. | Max. | Unit | Fig. |

|----------------|-------------------|--------------------------------|-------------|------|------|------|------|------|

| $V_2$          | Ramp Valley       | S1 = C; S2 = B                 |             | 1.2  | 1.5  |      | V    | 7A   |

| V <sub>2</sub> | Ramp Peak         | S1 = C                         | Vi = 15V    |      | 2.5  |      | V    | 7A   |

|                |                   | S2 = B                         | $V_i = 45V$ |      | 5.5  |      | V    | 7A   |

| l <sub>2</sub> | Min. Ramp Current | S1 = A; I <sub>1</sub> = 100μA |             |      | 270  | 300  | μΑ   | 7A   |

| l <sub>2</sub> | Max. Ramp Current | S1 = A; I1 = 1                 | mA          | 2.4  | 2.7  |      | mA   | 7A   |

# SYNC FUNCTION (pin 13)

| Symbol           | Parameter                                    | Test Condition                                                     | Min. | Тур. | Max. | Unit | Fig. |

|------------------|----------------------------------------------|--------------------------------------------------------------------|------|------|------|------|------|

| V <sub>13</sub>  | Low Input Voltage                            | $V_i = 15V \text{ to } 50V; V_{12} = 0;$<br>S1 = C; S2 = B; S4 = B | -0.3 |      | 0.9  | V    | 7A   |

| V <sub>13</sub>  | High Input voltage                           | V <sub>12</sub> = 0;<br>S1 = C; S2 = B; S4 = B                     | 3.5  |      | 5.5  | V    | 7A   |

| I <sub>13L</sub> | Sync Input Current with<br>Low Input Voltage | $V_2 = V_{13} = 0.9V;$ S4 = A;<br>S1 = C; S2 = B                   |      |      | 0.4  | mA   | 7A   |

| I <sub>13H</sub> | Input Current with High Input Voltage        | V <sub>13</sub> = 3.5V; S4 = A;<br>S1 = C; S2 = B                  |      |      | 2    | mA   | 7A   |

| V <sub>13</sub>  | Output Amplitude                             |                                                                    | 4    | 5    |      | V    | _    |

| t <sub>W</sub>   | Output Pulse Width                           | $V_{thr} = 2.5V$                                                   | 0.3  | 0.5  | 0.8  | μs   | -    |

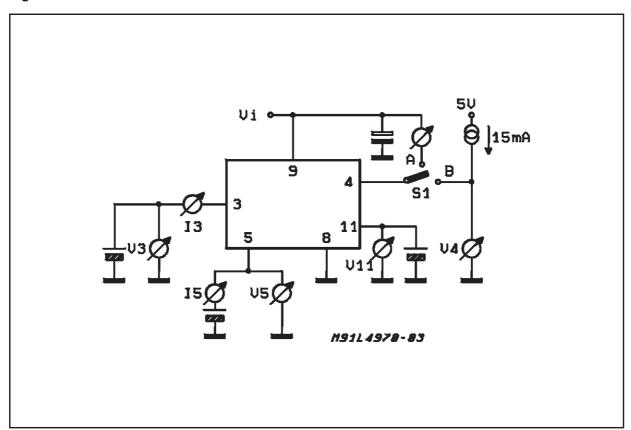

#### **ELECTRICAL CHARACTERISTICS** (continued)

**RESET AND POWER FAIL FUNCTIONS**

| Symbol            | Parameter                          | Test Condition                                     | Min.                     | Тур.                     | Max.                     | Unit    | Fig. |

|-------------------|------------------------------------|----------------------------------------------------|--------------------------|--------------------------|--------------------------|---------|------|

| V <sub>11R</sub>  | Rising Threshold Voltage (pin 11)  | $V_i = 15 \text{ to } 50V$<br>$V_3 = 5.3V$         | V <sub>ref</sub><br>-120 | V <sub>ref</sub><br>-100 | V <sub>ref</sub><br>-80  | V<br>mV | 7D   |

| V <sub>11F</sub>  | Falling Threshold Voltage (pin 11) | Vi = 15  to  50V<br>$V_3 = 5.3V$                   | 4.77                     | V <sub>ref</sub><br>-200 | V <sub>ref</sub><br>-160 | V<br>mV | 7D   |

| V <sub>5H</sub>   | Delay High Threshold<br>Voltage    | $V_i = 15 \text{ to } 50V$<br>$V_{11} = V_{14}$    | 4.95                     | 5.1                      | 5.25                     | V       | 7D   |

| V <sub>5L</sub>   | Delay Low Threshold<br>Voltage     | Vi = 15  to  50V<br>$V_{11} = V_{14}$ $V_3 = 5.3V$ | 1                        | 1.1                      | 1.2                      | V       | 7D   |

| -l <sub>5SO</sub> | Delay Source Current               | $V_3 = 5.3V$ ; $V_5 = 3V$                          | 40                       | 60                       | 80                       | μΑ      | 7D   |

| I <sub>5SI</sub>  | Delay Sink Current                 | $V_3 = 4.7V$ ; $V_5 = 3V$                          | 10                       |                          |                          | mA      | 7D   |

| V <sub>4S</sub>   | Out Saturation Voltage             | $I_4 = 15mA; S1 = B$<br>$V_3 = 4.7V$               |                          |                          | 0.4                      | V       | 7D   |

| 14                | Output Leak Current                | $V_4 = 50V$ ; S1 = A<br>$V_3 = 5.3V$               |                          |                          | 100                      | μΑ      | 7D   |

| V <sub>3R</sub>   | Rising Threshold Voltage           | $V_{11} = V_{14}$                                  | 4.95                     | 5.1                      | 5.25                     | V       | 7D   |

| V <sub>3H</sub>   | Hysteresys                         |                                                    | 0.4                      | 0.5                      | 0.6                      | V       | 7D   |

| l <sub>3</sub>    | Input Bias Current                 |                                                    |                          | 1                        | 3                        | μΑ      | 7D   |

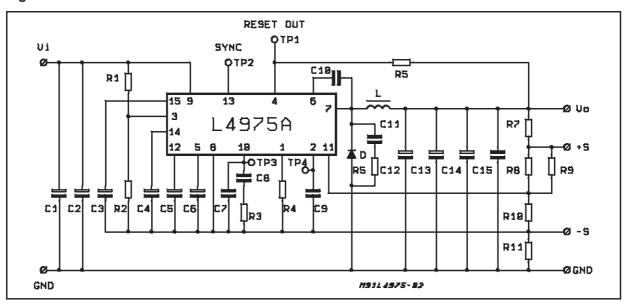

Figure 5: Test and Evaluation Board Circuit

TYPICAL PERFORMANCES (using evaluation board):

$n = 83\% (V_i = 35V; V_o = V_{REF}; I_o = 5A; f_{SW} = 200KHz)$

$V_{\text{0 RIPPLE}}$  = 30mV (at 5A) with output filter capacitor ESR  $\leq 60 \text{m}\Omega$

Line regulation = 5mV ( $V_i = 15 to 50V$ )

Load regulation =  $15mV (I_0 = 2 \text{ to } 5A)$

For component values, refer to test circuit part list.

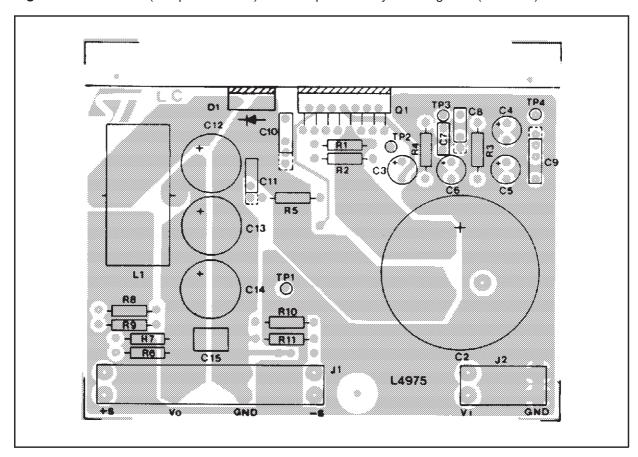

Figure 6a: P.C. Board (components side) and Components Layout of Figure 5 (1:1 scale).

#### **PARTS LIST**

| $R_1 = 30K\Omega$                          | $C_1$ , $C_2 = 3300 \mu F 63 V_L EYF (ROE)$                        |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| $R_2 = 10K\Omega$                          | $C_3$ , $C_4$ , $C_5$ , $C_6 = 2.2 \mu F$                          |  |  |  |  |

| $R_3 = 15K\Omega$                          | C <sub>7</sub> = 390pF Film                                        |  |  |  |  |

| $R_4 = 16K\Omega$                          | C <sub>8</sub> = 22nF MKT 1817 (ERO)                               |  |  |  |  |

| $R_5 = 22\Omega \ 0.5W$                    |                                                                    |  |  |  |  |

| $R_6 = 4K7$                                | C <sub>9</sub> = 2.2nF KP1830                                      |  |  |  |  |

| $R_7 = 10\Omega$                           | C <sub>10</sub> = 220nF MKT                                        |  |  |  |  |

| R <sub>8</sub> = see tab. A                | C <sub>11</sub> = 2.2nF MP1830                                     |  |  |  |  |

| R <sub>9</sub> = OPTION                    | ** $C_{12}$ , $C_{13}$ , $C_{14} = 220 \mu F 40 V_L EKR$           |  |  |  |  |

| $R_{10} = 4K7$                             | $C_{15} = 1\mu F$ Film                                             |  |  |  |  |

| $R_{11} = 10\Omega$                        |                                                                    |  |  |  |  |

| D1 = MBR 760CT (or 7.5A/60V or equivalent) |                                                                    |  |  |  |  |

| L1 = 80μH                                  | core 58930 MAGNETICS<br>24 TURNS Ø 1.1mm (AWG 17)<br>COGEMA 949178 |  |  |  |  |

<sup>2</sup> capacitors in parallel to increase input RMS current capability

3 capacitors in parallel to reduce total output ESR

Table A

| $\mathbf{V}_0$ | $R_9$            | <b>R</b> <sub>7</sub> |

|----------------|------------------|-----------------------|

| 12V            | 4.7kΩ            | 6.2kW                 |

| 15V            | 4.7kΩ            | 9.1kΩ                 |

| 18V            | 4.7kΩ            | 12kΩ                  |

| 24V            | $4.7$ k $\Omega$ | 18kΩ                  |

**Table B** SUGGESTED BOOTSTRAP CAPACITORS

| Operating Frequency | Bootstrap Cap.c10 |  |  |

|---------------------|-------------------|--|--|

| f = 20KHz           | ≥680nF            |  |  |

| f = 50KHz           | ≥470nF            |  |  |

| f = 100KHz          | ≥330nF            |  |  |

| f = 200KHz          | ≥220nF            |  |  |

| f = 500KHz          | ≥100nF            |  |  |

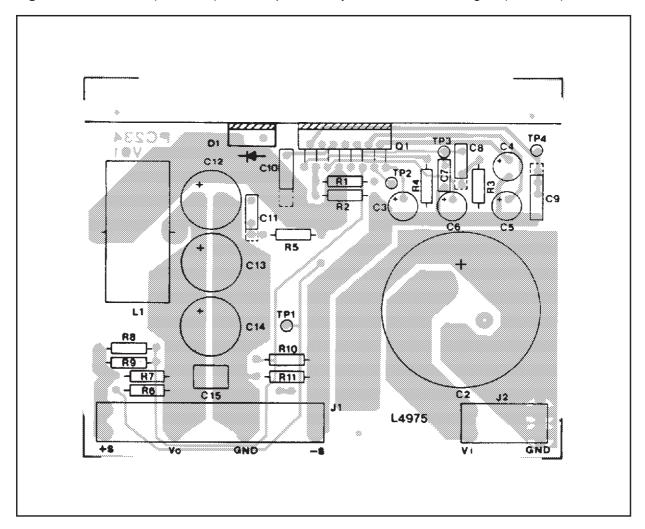

Figure 6b: P.C. Board (Back side) and Components Layout of the Circuit of Fig. 5. (1:1 scale)

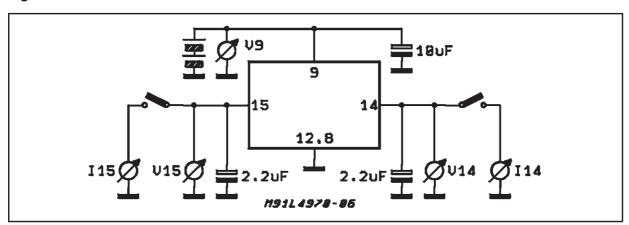

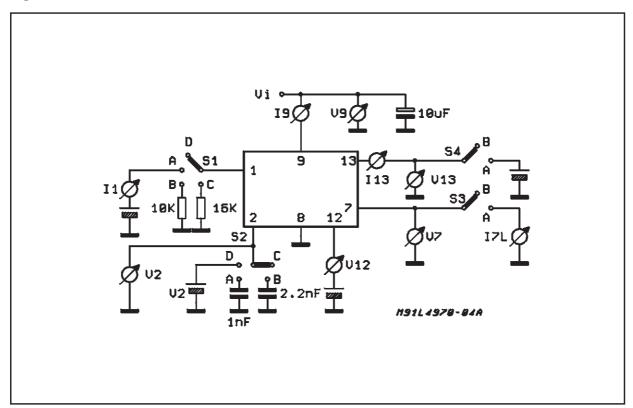

Figure 7: DC Test Circuits

Figure 7A

Figure 7B

Figure 7D

Figure 7C

Figure 8: Quiescent Drain Current vs. Supply Voltage (0% duty cycle - see fig. 7A).

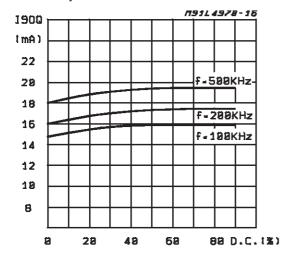

Figure 10: Quiescent Drain Current vs. Duty Cycle

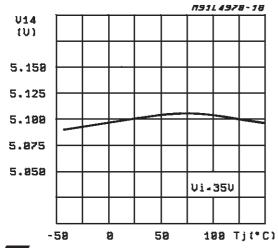

**Figure 12:** Reference Voltage (pin 14) vs. Junction Temperature (see fig. 7)

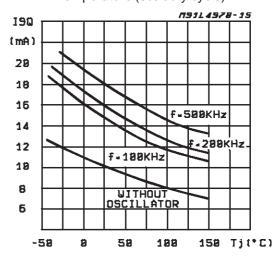

Figure 9: Quiescent Drain Current vs. Junction Temperature (0% duty cycle).

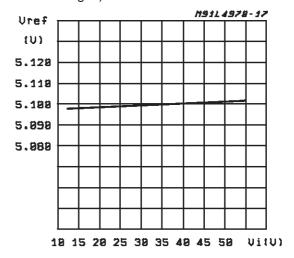

**Figure 11:** Reference Voltage (pin14) vs. V<sub>i</sub> (see fig. 7)

**Figure 13:** Reference Voltage (pin15) vs. V<sub>i</sub> (see fig. 7)

**Figure 14:** Reference Voltage (pin 15) vs. Junction Temperature (see fig. 7)

**Figure 16:** Switching Frequency vs. Input Voltage (see fig. 5)

Figure 18: Switching Frequency vs. R4 (see fig. 5)

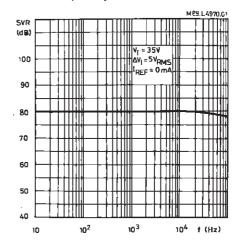

Figure 15: Reference Voltage 5.1V (pin 14) Supply Voltage Ripple Rejection vs. Frequency

**Figure 17:** Switching Frequency vs. Junction Temperature (see fig 5)

Figure 19: Max. Duty Cycle vs. Frequency

5

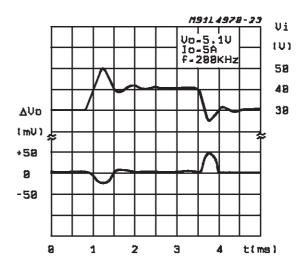

**Figure 20:** Supply Voltage Ripple Rejection vs. Frequency (see fig. 5)

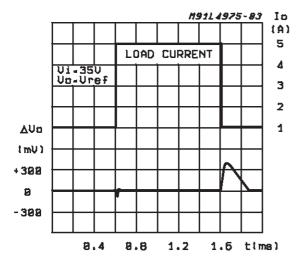

Figure 22: Load Transient Response (see fig. 5)

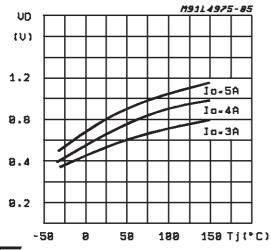

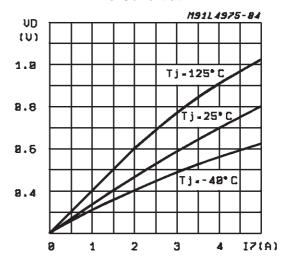

**Figure 24:** Dropout Voltage Between Pin 9 and Pin 7 vs. Junction Temperature

Figure 21: Line Transient Response (see fig. 5)

**Figure 23:** Dropout Voltage Between Pin 9 and Pin 7 vs. Current at Pin 7

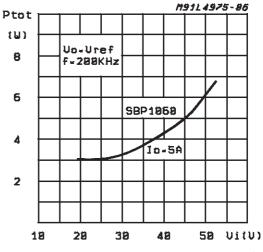

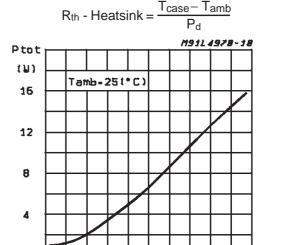

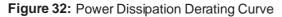

**Figure 25:** Power Dissipation (device only) vs. Input Voltage

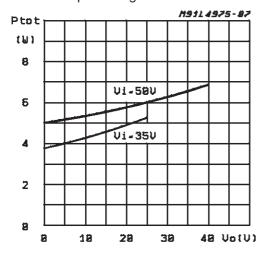

**Figure 26:** Power Dissipation (device only) vs. Output Voltage

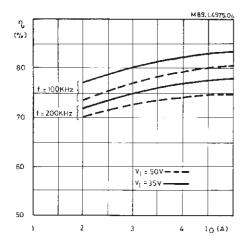

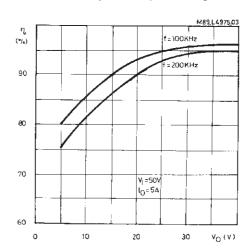

Figure 28: Efficiency vs. Output Current

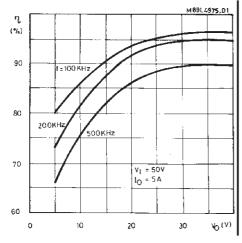

Figure 30: Efficiency vs. Output Voltage

Figure 27: Heatsink Used to Derive the Device's Power Dissipation

59

60 Trase(°C)

Figure 29: Efficiency vs. Output Voltage

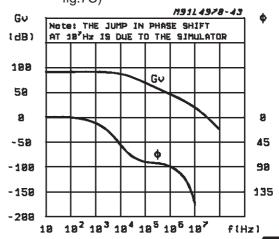

**Figure 31:** Open Loop Frequency and Phase Response of Error Amplifier (see fig.7C)

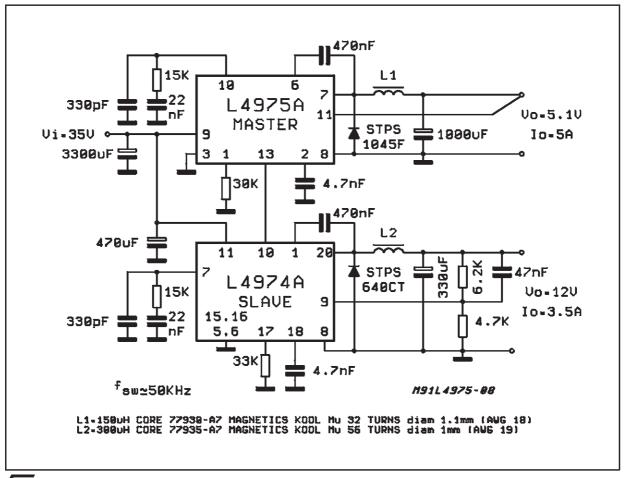

Figure 33: 5.1V/12V Multiple Supply. Note the Synchronization between the L4975A and the L4974A

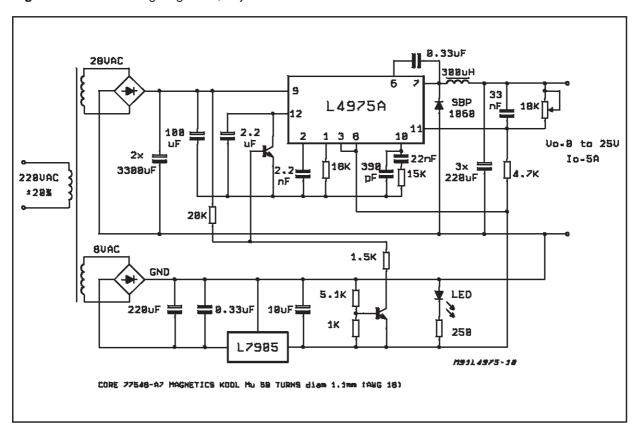

Figure 34: 5.1V / 5A Low Cost Application

Figure 35: 5A Switching Regulator, Adjustable from 0V to 25V.

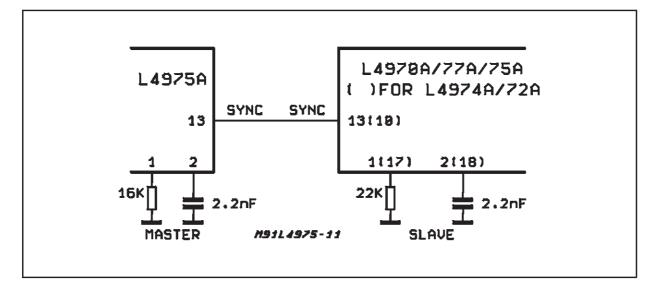

Figure 36: L4975A's Sync. Example

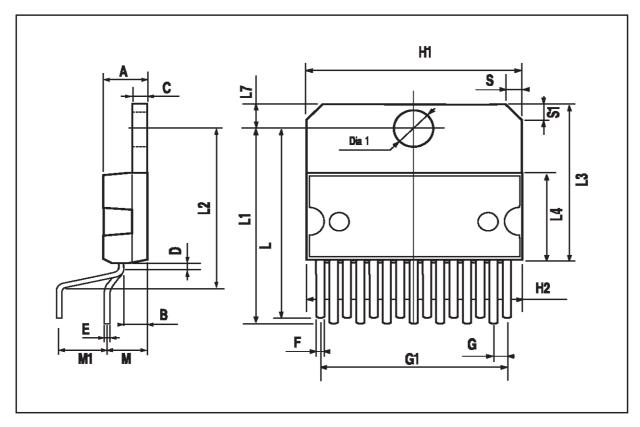

| DIM. | mm    |       |       | inch  |       |       |

|------|-------|-------|-------|-------|-------|-------|

|      | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α    |       |       | 5     |       |       | 0.197 |

| В    |       |       | 2.65  |       |       | 0.104 |

| С    |       |       | 1.6   |       |       | 0.063 |

| D    |       | 1     |       |       | 0.039 |       |

| E    | 0.49  |       | 0.55  | 0.019 |       | 0.022 |

| F    | 0.66  |       | 0.75  | 0.026 |       | 0.030 |

| G    | 1.02  | 1.27  | 1.52  | 0.040 | 0.050 | 0.060 |

| G1   | 17.53 | 17.78 | 18.03 | 0.690 | 0.700 | 0.710 |

| H1   | 19.6  |       |       | 0.772 |       |       |

| H2   |       |       | 20.2  |       |       | 0.795 |

| L    | 21.9  | 22.2  | 22.5  | 0.862 | 0.874 | 0.886 |

| L1   | 21.7  | 22.1  | 22.5  | 0.854 | 0.870 | 0.886 |

| L2   | 17.65 |       | 18.1  | 0.695 |       | 0.713 |

| L3   | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |

| L4   | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |

| L7   | 2.65  |       | 2.9   | 0.104 |       | 0.114 |

| М    | 4.25  | 4.55  | 4.85  | 0.167 | 0.179 | 0.191 |

| M1   | 4.63  | 5.08  | 5.53  | 0.182 | 0.200 | 0.218 |

| S    | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| S1   | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| Dia1 | 3.65  |       | 3.85  | 0.144 |       | 0.152 |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com