A plus make your production A-plus

# **Data Sheet**

## aIVR8511 – 85 sec

### **APLUS INTEGRATED CIRCUITS INC.**

#### Address:

3 F-10, No. 32, Sec. 1, Chenggung Rd., Taipei, Taiwan 115, R.O.C. (115)台北市南港區成功路一段 32號 3 樓之 10.

TEL: 886-2-2782-9266

FAX: 886-2-2782-9255

**WEBSITE :** <u>http://www.aplusinc.com.tw</u>

Sales E-mail: sales@aplusinc.com.tw

Support E-mail: service@aplusinc.com.tw

#### FEATURES

- I Standard CMOS process.

- Embedded EPROM.

- Embedded 8-bit MCU.

- 85sec voice duration at 6 KHz sampling with 4-bit ADPCM compression.

- Combination of voice building blocks to extend playback duration.

- **I** Table entries are available for voice block combinations.

- User selectable PCM or ADPCM data compress.

- Voice Group Trigger Options: Edge / Level; Hold / Un-hold; Retrigger / Non-retrigger.

- Programmable I/Os, Timer Interrupt and Watch Dog Timer.

- Built-in oscillator with fixed Rosc, software control sampling frequency

- $1 \quad 2.2V 3.6V$  single power supply and < 5uA low stand-by current.

- PWM Vout1 and Vout2 drive speaker directly with two levels of volume selection.

- D/A COUT with ramp-up ramp-down option to drive speaker through an external BJT.

#### DESCRIPTION

Aplus' aIVR8511 is a 8-bit MCU based Voice chip. It is fabricated with Standard CMOS process with embedded voice storage memory. It can store 85sec voice message with 4-bit ADPCM compression at 6KHz sampling rate. 8-bit PCM is also available as user selectable option to improve sound quality. There are eleven programmable I/O pins. Key trigger and Parallel CPU trigger mode can be configured according to different application requirement. User selectable triggering and output signal options provide maximum flexibility to various applications. Built-in resistor controlled oscillator, 8-bit current mode D/A output and PWM direct speaker driving output minimize the number of external components. Two levels volume control for PWM speaker direct drive is available.

#### PIN CONFIGURATION

| aIVR 8511 |            |  |  |  |  |  |

|-----------|------------|--|--|--|--|--|

|           |            |  |  |  |  |  |

| PD0 🛛 1   | ✓ 20 ] PC3 |  |  |  |  |  |

| PD1 2     | 19 🛛 PC2   |  |  |  |  |  |

| PD2 3     | 18 🛛 PC1   |  |  |  |  |  |

| NC 4      | 17 🛛 PC0   |  |  |  |  |  |

| VDD 5     | 16 🛛 VDDA  |  |  |  |  |  |

| VOUT2 6   | 15 🛛 OSC   |  |  |  |  |  |

| VOUT1 7   | 14 RSTB    |  |  |  |  |  |

| NC 8      | 13 PB0     |  |  |  |  |  |

| VSS 🛛 🤊   | 12 PB1     |  |  |  |  |  |

| PB3 10    | 11 PB2     |  |  |  |  |  |

|           |            |  |  |  |  |  |

|           | DIP / SOP  |  |  |  |  |  |

|           |            |  |  |  |  |  |

|           |            |  |  |  |  |  |

#### **PIN DESCRIPTIONS**

| Pin Names  | Description                                                 |  |

|------------|-------------------------------------------------------------|--|

| VOUT1      | PWM output to drive speaker directly                        |  |

| VOUT2_COUT | PWM output or COUT DAC output select by programmable option |  |

| VSS        | Power Ground                                                |  |

| OSC        | Oscillator input                                            |  |

| VDDA       | Positive Power Supply                                       |  |

| VDD        | Positive Power Supply                                       |  |

| PB0~PB3    | Programmable I/O port B                                     |  |

| PC0~PC3    | Programmable I/O port C                                     |  |

| PD0~PD2    | Programmable I/O port D                                     |  |

| RSTB       | Reset pin, Low active                                       |  |

Note:

- PB, PC and PD ports are software programmable I/O pins that can be set to different configurations such as pure input, input with pull-up, input with pull-down and output. The programmable I/O pins set up will take effect immediately after chip RESET is applied.

- Pins for memory programming are: VDD, VDDA, VSS, PB0, PB1, OSC, VOUT2 and RSTB.

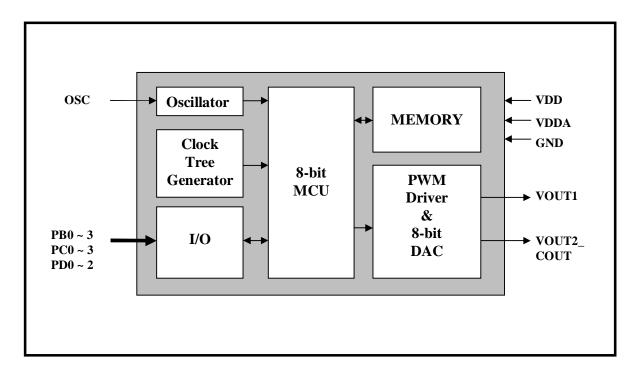

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol Rating                     |                                                     | Unit |

|-----------------------------------|-----------------------------------------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | -0.5 ~ +4.0                                         | V    |

| V <sub>IN</sub>                   | $V_{SS} - 0.3 < V_{IN} < V_{DD} + 0.3$              | V    |

| V <sub>OUT</sub>                  | V <sub>SS</sub> <v<sub>OUT<v<sub>DD</v<sub></v<sub> | V    |

| T (Operating):                    | -40 ~ +85                                           | °C   |

| T (Junction)                      | -40 ~ +125                                          | °C   |

| T (Storage)                       | -55 ~ +125                                          | °C   |

### **DC CHARACTERISTICS** ( $T_A = 0$ to 70°C, $V_{DD} = 3.0V$ , $V_{SS} = 0V$ )

| Symbol               | Parameter                                            | Min. | Typ.       | Max. | Unit | Conditions                              |

|----------------------|------------------------------------------------------|------|------------|------|------|-----------------------------------------|

| V <sub>DD</sub>      | Operating Voltage                                    | 2.2  | 3.0        | 3.6  | V    |                                         |

| I <sub>SB</sub>      | Standby current                                      |      | 1          | 5    | μA   | I/O properly terminated                 |

| I <sub>OP</sub>      | Operating current                                    |      | 7          |      | mA   | I/O properly terminated                 |

| V <sub>IH</sub>      | "H" Input Voltage                                    | 2.5  | 3.0        | 3.5  | V    | V <sub>DD</sub> =3.0V                   |

| V <sub>IL</sub>      | "L" Input Voltage                                    | -0.3 | 0          | 0.5  | V    | V <sub>DD</sub> =3.0V                   |

| I <sub>VOUTL_N</sub> | V <sub>OUT</sub> low O/P Current<br>(Normal Volume)  | —    | 130        | —    | mA   | Vout=1.0V                               |

| I <sub>VOUTL_H</sub> | V <sub>OUT</sub> low O/P Current<br>(High Volume)    |      | 200        |      | mA   | Vout=1.0V                               |

| I <sub>VOUTH_N</sub> | V <sub>OUT</sub> high O/P Current<br>(Normal Volume) |      | -130       |      | mA   | Vout=2.0V                               |

| I <sub>vouth_h</sub> | V <sub>OUT</sub> high O/P Current<br>(High Volume)   | _    | -200       |      | mA   | Vout=2.0V                               |

| ICO                  | C <sub>OUT</sub> O/P Current                         |      | -2         |      | mA   | Data = 80h                              |

| IOH                  | O/P High Current                                     |      | -10        |      | mA   | V <sub>OH</sub> =2.5V                   |

| I <sub>OL</sub>      | O/P Low Current                                      |      | 17         |      | mA   | V <sub>OL</sub> =0.3V                   |

| RN <sub>VOUT</sub>   | VOUT pull-down resistance                            |      | 100K       |      | Ω    | VOUT pin set to internal pull-down      |

| RN <sub>PIO</sub>    | Programmable IO pin pull-down resistance             |      | 1 <b>M</b> |      | Ω    | PBx, PCx, PDx set to internal pull-down |

| RU <sub>PIO</sub>    | Programmable IO pin pull-up resistance               | 3.3K | 4.7K       | _    | Ω    | PBx, PCx, PDx set to internal pull-up   |

| ΔFs/Fs               | Frequency stability                                  | -3   |            | +3   | %    | $V_{DD} = 3V + 0.4V$                    |

| ΔFc/Fc               | Chip to chip Frequency<br>Variation                  | -5   |            | +5   | %    | Also apply to lot to lot variation      |

#### **TYPICAL APPLICATIONS**

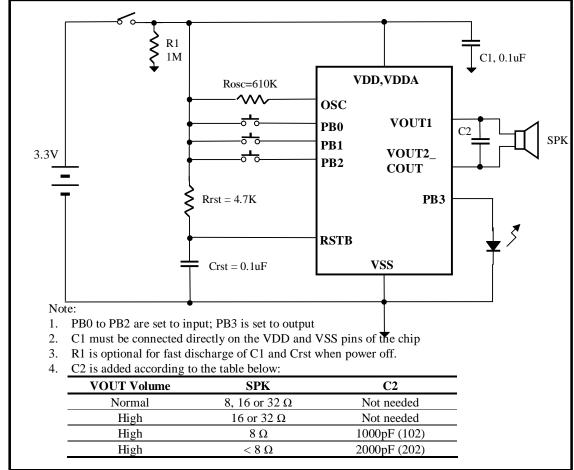

Using 3.3V Battery Direct Drive Speaker

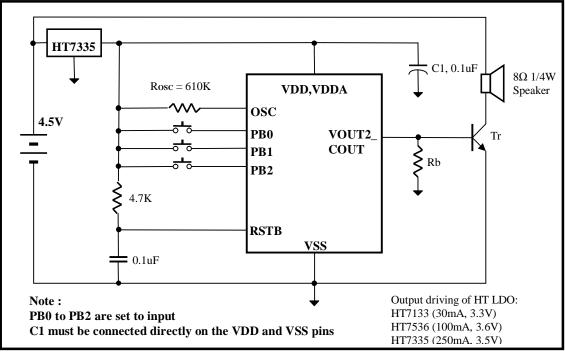

Using 4.5V Battery with COUT speaker drive

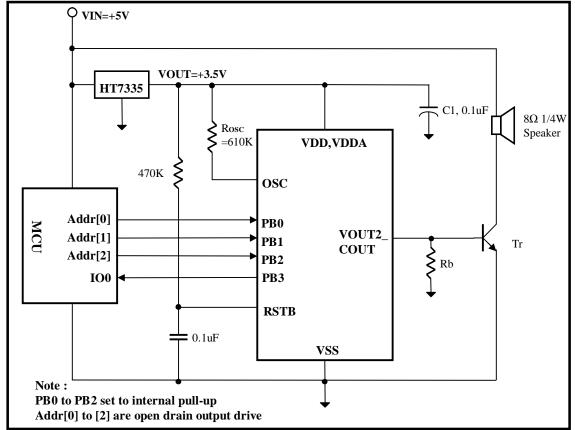

5V CPU Control with COUT

Note for COUT speaker drive:

- 1. C1 must be connected as close to the chips VDD and VSS pins as possible.

- 2. Rb is base resistor from 120 Ohm to 390 Ohm depends on value of VDD and transistor gain.

- 3. Tr is an NPN transistor with beta larger than 150, e.g. 8050D.

- 4. Rosc = 610K Ohm with Vdd=3.0V can support sampling rate up to 14KHz.

- 5. For sampling rate higher than 14KHz, smaller value of Rosc should be used.

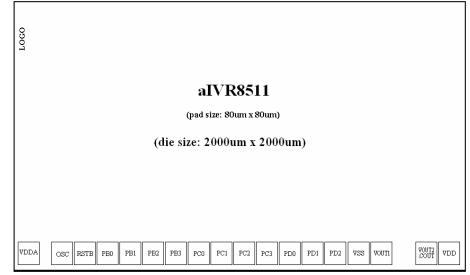

#### **Bonding Diagrams**

Note: Substrate must be connected to VSS