www.fairchildsemi.com

# TMC2249A Digital Mixer 12 x 12 Bit, 60 MHz

#### **Features**

- 60 MHz input and computation rate

- Two 12-bit multipliers

- Separate data and coefficient inputs

- Independent, user-selectable pipeline delays of 1 to 16 clocks on all input ports

- Separate 16-bit input port allows cascading or addition of a constant

- · User-selectable rounded output

- Internal 1/2 LSB rounding of products

- · Fully registered, pipelined architecture

- Available in 120-Pin CPGA, PPGA, MPGA or MQFP

# **Applications**

- Video switching

- Image mixing

- · Digital signal modulation

- · Complex frequency synthesis

- Digital filtering

- · Complex arithmetic functions

# Description

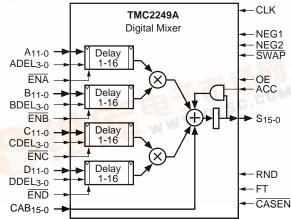

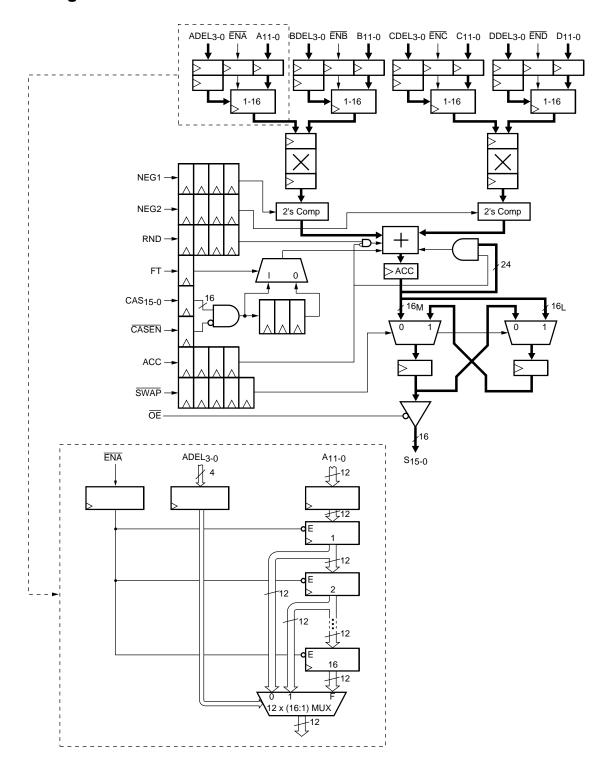

The TMC2249A is a high-speed digital arithmetic circuit consisting of two 12-bit multipliers, an adder and a cascadeable accumulator. All four multiplier inputs are simultaneously accessible to the user, and each includes a user-programmable pipeline delay of up to 16 clocks in length. The 24-bit adder/subtractor is followed by an accumulator and 16-bit input port which allows the user to cascade multiple TMC2249As. A new 16-bit accumulated output is available every clock, up to the maximum rate of 60 MHz. All inputs and outputs are registered except the three-state output enable, and all are TTL compatible.

offering significant flexibility. Input register clock enables and programmable input data pipeline delays on each port offer an adaptable input structure for high-speed digital systems. Following the multipliers, the user may perform addition or subtraction of either product, arithmetic rounding to 16 bits, and accumulation and summation of products with a cascading input. The output port allows access to all 24 bits of the internal accumulator by switching between overlapping least and most-significant 16-bit words, and a three-state output enable simplifies connection to an external system bus.

The TMC2249A utilizes a pipelined, bus-oriented structure

The TMC2249A has numerous applications in digital processing algorithms, from executing simple image mixing and switching, to performing complex arithmetic functions and complex waveform synthesis. FIR filters, digital quadrature mixers and modulators, and vector arithmetic functions may also be implemented with this device.

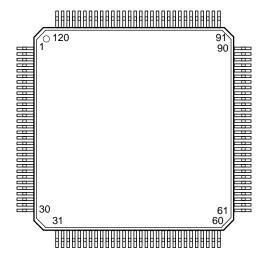

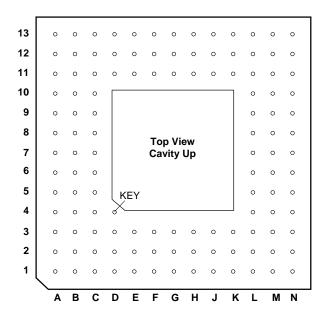

Fabricated in a submicron CMOS process, the TMC2249A operates at guaranteed clock rates of up to 60 MHz over the full temperature and supply voltage ranges. It is pin- and function-compatible with Fairchild's TMC2249, while providing higher speed operation and lower power dissipation. It is available in a 120 pin Ceramic Pin Grid Array (CPGA), 120 pin Plastic Pin Grid Array (PPGA), 120 lead MQFP to PPGA package (MPGA), and a 120 lead Metric Quad Flat-Pack (MQFP).

# Logic Symbol

# **Block Diagram**

# **Functional Description**

The TMC2249A performs the summation of products described by the formula:

$$\begin{split} S(N+5) = & A(N\text{-}ADEL) \times B(N\text{-}BDEL) \times (\text{-}1^{NEG1(N)}) + \\ & C(N\text{-}CDEL) \times D(N\text{-}DDEL) \times (\text{-}1^{NEG2(N)}) + \\ & CAS(N+3 \times FT) \end{split}$$

where ADEL through DDEL range from 1 to 16 pipe delays.

All inputs and controls utilize pipeline delay registers to maintain synchronicity with the data input during that clock,

except when the Cascade data input is routed directly to the accumulator by use of the Feedthrough control. One-half LSB rounding to 16 bits may be performed on the sum of products while summing with the cascade input data.

The user may access either the upper or lower 16 bits of the 24-bit accumulator by swapping overlapping registers. The output bus has an asynchronous high-impedance enable, to simplify interfacing to complex systems.

# **Pin Assignments**

#### 120 Pin Metric Quad Flat Pack, KE Package

| Pin | Name              | Pin | Name              | Pin | Name              | Pin | Name              |

|-----|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|

| 1   | CLK               | 31  | BDEL <sub>2</sub> | 61  | ADEL <sub>3</sub> | 91  | C <sub>1</sub>    |

| 2   | ACC               | 32  | BDEL3             | 62  | ADEL <sub>2</sub> | 92  | C <sub>2</sub>    |

| _ 3 | NEG1              | 33  | ENB               | 63  | ADEL <sub>1</sub> | 93  | C3                |

| _ 4 | NEG2              | 34  | B <sub>0</sub>    | 64  | ADEL <sub>0</sub> | 94  | C4                |

| _ 5 | RND               | 35  | B <sub>1</sub>    | 65  | NC                | 95  | C <sub>5</sub>    |

| _6  | S <sub>15</sub>   | 36  | B <sub>2</sub>    | 66  | CAS <sub>15</sub> | 96  | C <sub>6</sub>    |

| _ 7 | S <sub>14</sub>   | 37  | Вз                | 67  | CAS <sub>14</sub> | 97  | C <sub>7</sub>    |

| 8   | GND               | 38  | В4                | 68  | CAS <sub>13</sub> | 98  | C <sub>8</sub>    |

| 9   | S <sub>13</sub>   | 39  | B5                | 69  | CAS <sub>12</sub> | 99  | C9                |

| 10  | S <sub>12</sub>   | 40  | В6                | 70  | CAS <sub>11</sub> | 100 | C <sub>10</sub>   |

| 11  | S <sub>11</sub>   | 41  | В7                | 71  | CAS <sub>10</sub> | 101 | C <sub>11</sub>   |

| 12  | VDD               | 42  | GND               | 72  | GND               | 102 | VDD               |

| 13  | S <sub>10</sub>   | 43  | B8                | 73  | CAS <sub>9</sub>  | 103 | D11               |

| 14  | S <sub>9</sub>    | 44  | В9                | 74  | CAS <sub>8</sub>  | 104 | D <sub>10</sub>   |

| 15  | S <sub>8</sub>    | 45  | B <sub>10</sub>   | 75  | CAS <sub>7</sub>  | 105 | Dg                |

| 16  | GND               | 46  | V <sub>DD</sub>   | 76  | CAS <sub>6</sub>  | 106 | GND               |

| 17  | S <sub>7</sub>    | 47  | B11               | 77  | CAS <sub>5</sub>  | 107 | D8                |

| 18  | S <sub>8</sub>    | 48  | A11               | 78  | CAS <sub>4</sub>  | 108 | D <sub>7</sub>    |

| 19  | S <sub>5</sub>    | 49  | A10               | 79  | CAS <sub>3</sub>  | 109 | D <sub>6</sub>    |

| _20 | VDD               | 50  | A9                | 80  | CAS <sub>2</sub>  | 110 | D <sub>5</sub>    |

| 21  | S <sub>4</sub>    | 51  | A <sub>8</sub>    | 81  | CAS <sub>1</sub>  | 111 | D <sub>4</sub>    |

| 22  | S <sub>3</sub>    | 52  | A <sub>7</sub>    | 82  | CAS <sub>0</sub>  | 112 | D <sub>3</sub>    |

| 23  | S <sub>2</sub>    | 53  | A <sub>6</sub>    | 83  | CASEN             | 113 | D <sub>2</sub>    |

| 24  | GND               | 54  | A5                | 84  | FT                | 114 | D <sub>1</sub>    |

| 25  | S <sub>1</sub>    | 55  | A4                | 85  | CDEL <sub>0</sub> | 115 | D <sub>0</sub>    |

| 26  | S <sub>0</sub>    | 56  | Аз                | 86  | CDEL <sub>1</sub> | 116 | END               |

| 27  | ŌE                | 57  | A <sub>2</sub>    | 87  | CDEL <sub>2</sub> | 117 | DDEL3             |

| 28  | SWAP              | 58  | A <sub>1</sub>    | 88  | CDEL3             | 118 | DDEL <sub>2</sub> |

| 29  | BDEL <sub>0</sub> | 59  | A <sub>0</sub>    | 89  | ENC               | 119 | DDEL <sub>1</sub> |

| 30  | BDEL <sub>1</sub> | 60  | ENA               | 90  | C <sub>0</sub>    | 120 | DDEL <sub>0</sub> |

# **Pin Assignments**

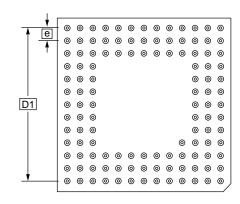

120 Pin Plastic Pin Grid Array, H5 Package, 120 Pin Ceramic Pin Grid Array, G1 Package, and 120 Pin Metric Quad FlatPack to 120 Pin Plastic Pin Array, H6 Package

| Pin | Name              | Pin | Name              | Pin | Name              | Pin | Name              |

|-----|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|

| A1  | DDEL <sub>0</sub> | C5  | D1                | G11 | CAS <sub>6</sub>  | L10 | A <sub>1</sub>    |

| A2  | DDEL3             | C6  | D <sub>5</sub>    | G12 | CAS <sub>7</sub>  | L11 | ADEL3             |

| АЗ  | END               | C7  | GND               | G13 | CAS <sub>5</sub>  | L12 | NC                |

| A4  | D <sub>2</sub>    | C8  | VDD               | H1  | S <sub>6</sub>    | L13 | CAS <sub>15</sub> |

| A5  | D4                | C9  | C <sub>8</sub>    | H2  | S <sub>5</sub>    | M1  | ŌE                |

| A6  | D <sub>7</sub>    | C10 | C4                | Н3  | VDD               | M2  | BDEL3             |

| A7  | D8                | C11 | C <sub>1</sub>    | H11 | GND               | МЗ  | B <sub>1</sub>    |

| A8  | D10               | C12 | ENC               | H12 | CAS9              | M4  | Вз                |

| A9  | C11               | C13 | CDEL <sub>1</sub> | H13 | CAS <sub>8</sub>  | M5  | B <sub>6</sub>    |

| A10 | C9                | D1  | S <sub>13</sub>   | J1  | S <sub>4</sub>    | M6  | B <sub>8</sub>    |

| A11 | C <sub>6</sub>    | D2  | S <sub>14</sub>   | J2  | S <sub>3</sub>    | M7  | B <sub>10</sub>   |

| A12 | С3                | D3  | GND               | J3  | GND               | M8  | A <sub>10</sub>   |

| A13 | C <sub>0</sub>    | D11 | CDEL3             | J11 | CAS <sub>13</sub> | M9  | A7                |

| B1  | NEG1              | D12 | CDEL <sub>0</sub> | J12 | CAS <sub>11</sub> | M10 | A4                |

| B2  | ACC               | D13 | CASEN             | J13 | CAS <sub>10</sub> | M11 | A <sub>0</sub>    |

| В3  | DDEL1             | E1  | S <sub>11</sub>   | K1  | S <sub>2</sub>    | M12 | ADEL <sub>2</sub> |

| B4  | D <sub>0</sub>    | E2  | S <sub>12</sub>   | K2  | S <sub>1</sub>    | M13 | ADEL <sub>1</sub> |

| B5  | D <sub>3</sub>    | E3  | GND               | K3  | SWAP              | N1  | BDEL <sub>1</sub> |

| B6  | D <sub>6</sub>    | E11 | FT                | K11 | ADEL <sub>0</sub> | N2  | ENB               |

| B7  | D9                | E12 | CAS <sub>0</sub>  | K12 | CAS <sub>14</sub> | N3  | B <sub>2</sub>    |

| B8  | D11               | E13 | CAS <sub>1</sub>  | K13 | CAS <sub>12</sub> | N4  | B5                |

| B9  | C10               | F1  | S9                | L1  | S <sub>0</sub>    | N5  | B <sub>7</sub>    |

| B10 | C7                | F2  | S <sub>10</sub>   | L2  | BDEL <sub>0</sub> | N6  | B9                |

| B11 | C5                | F3  | VDD               | L3  | BDEL <sub>2</sub> | N7  | B11               |

| B12 | C <sub>2</sub>    | F11 | CAS <sub>2</sub>  | L4  | В0                | N8  | A11               |

| B13 | CDEL <sub>2</sub> | F12 | CAS <sub>3</sub>  | L5  | B4                | N9  | A <sub>8</sub>    |

| C1  | S <sub>15</sub>   | F13 | CAS <sub>4</sub>  | L6  | GND               | N10 | A <sub>6</sub>    |

| C2  | RND               | G1  | S <sub>7</sub>    | L7  | VDD               | N11 | Аз                |

| C3  | CLK               | G2  | S <sub>8</sub>    | L8  | A9                | N12 | A <sub>2</sub>    |

| C4  | DDEL2             | G3  | GND               | L9  | A5                | N13 | ENA               |

# **Pin Descriptions**

|                     | Pin N                                                                                         | umber                                                                   |                                                                                                                                                                                                                                                                                            |

|---------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name            | CPGA/PPGA/<br>MPGA                                                                            | MQFP                                                                    | Pin Function Description                                                                                                                                                                                                                                                                   |

| Power               |                                                                                               |                                                                         |                                                                                                                                                                                                                                                                                            |

| V <sub>DD</sub>     | F3, H3, L7, C8                                                                                | 12, 20, 46, 102                                                         | <b>Supply Voltage.</b> The TMC2249A operates from a single +5V supply. All power and ground pins must be connected.                                                                                                                                                                        |

| GND                 | E3, G3, J3, L6,<br>H11, C7                                                                    | 8, 16, 24, 42,<br>72, 106                                               | <b>Ground.</b> The TMC2249A operates from a single +5V supply. All power and ground pins must be connected.                                                                                                                                                                                |

| Clock               | •                                                                                             |                                                                         |                                                                                                                                                                                                                                                                                            |

| CLK                 | C3                                                                                            | 1                                                                       | System Clock. The TMC2249A operates from a single master clock input. The rising edge of clock strobes all enabled registers. All timing specifications are referenced to the rising edge of CLK.                                                                                          |

| Inputs              |                                                                                               |                                                                         |                                                                                                                                                                                                                                                                                            |

| A <sub>11-0</sub>   | N8, M8, L8,<br>N9, M9, N10,<br>L9, M10, N11,<br>N12, L10, M11                                 | 48, 49, 50, 51, 52, 53, 54, 55, 56, 57, 58, 59                          | <b>A-D Input.</b> A through D are the four 12-bit registered data input ports. $A_0$ - $D_0$ are the LSBs (see Table 1). Data presented to the input ports is clocked in to the top of the 16-stage delay pipeline on the next clock when enabled, "pushing" data down the register stack. |

| B <sub>11-0</sub>   | N7, M7, N6,<br>M6, N5, M5,<br>N4, L5, M4,<br>N3, M3, L4                                       | 47, 45, 44, 43,<br>41, 40, 39, 38,<br>37, 36, 35, 34                    |                                                                                                                                                                                                                                                                                            |

| C <sub>11-0</sub>   | A9, B9, A10,<br>C9, B10, A11,<br>B11, C10, A12,<br>B12, C11, A13                              | 101, 100, 99,<br>98, 97, 96, 95,<br>94, 93, 92, 91,<br>90               |                                                                                                                                                                                                                                                                                            |

| D <sub>11-0</sub>   | B8, A8, B7, A7,<br>A6, B6, C6, A5,<br>B5, A4, C5, B4                                          | 103, 104, 105,<br>107, 108, 109,<br>110, 111, 112<br>113, 114, 115      |                                                                                                                                                                                                                                                                                            |

| ADEL <sub>3-0</sub> | L11, M12,<br>M13, K11                                                                         | 61, 62, 63, 64                                                          | <b>A-D Delay.</b> ADEL through DDEL are the four-bit registered input data pipe delay select word inputs. Data to be presented to the                                                                                                                                                      |

| BDEL <sub>3-0</sub> | M2, L3, N1, L2                                                                                | 32, 31, 30, 29                                                          | multipliers is selected from one of sixteen stages in the input data delay pipe registers, as indicated by the delay select word                                                                                                                                                           |

| CDEL <sub>3-0</sub> | D11, B13,<br>C13, D12                                                                         | 88, 87, 86, 85                                                          | presented to the respective input port during that clock. The minimum delay is one clock (select word=0000), and the maximum                                                                                                                                                               |

| DDEL <sub>3-0</sub> | A2, C4, B3, A1                                                                                | 117, 118, 119,<br>120                                                   | delay is 16 clocks (select word=1111). Following powerup these values are indeterminate and must be initialized by the user.                                                                                                                                                               |

| CAS <sub>15-0</sub> | L13, K12, J11,<br>K13, J12, J13,<br>H12, H13,<br>G12, G11,<br>G13, F13, F12,<br>F11, E13, E12 | 66, 67, 68, 69,<br>70, 71, 73, 74,<br>75, 76, 77, 78,<br>79, 80, 81, 82 | Cascade Input. CAS is the 16-bit Cascade data input port. CAS <sub>0</sub> is the LSB. See Table 1.                                                                                                                                                                                        |

| Controls            |                                                                                               |                                                                         |                                                                                                                                                                                                                                                                                            |

| S <sub>15-0</sub>   | C1, D2, D1,<br>E2, E1, F2, F1,<br>G2, G1, H1,<br>H2, J1, J2, K1,<br>K2, L1                    | 6, 7, 9, 10, 11,<br>13, 14, 15, 17,<br>18, 19, 21, 22,<br>23, 25, 26    | <b>Sum Output.</b> The current 16-bit result is available at the Sum output. The output may be the most or least significant 16 bits of the current accumulator output, as determined by $\overline{\text{SWAP}}$ . $S_0$ is the LSB. See Table 1.                                         |

# Pin Descriptions (continued)

|          | Pin N               | umber           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | CPGA/PPGA/<br>MPGA  | MQFP            | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Controls | 1                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENA-END  | N13, N2, C12,<br>A3 | 60, 33, 89, 116 | Input Enables. Input data presented to port i11-0 (i=A,B,C, or D) are latched into delay pipeline i, and data already in pipeline i advance by one register position, on each rising edge of CLK for which ENi is LOW. When ENi is HIGH, the data in pipeline i do not move and the value at the input port i will be lost before it reaches the multiplier.                                                                                                                                                                                                                                         |

| NEG1,2   | B1, D3              | 3, 4            | <b>Negate.</b> The products of the multipliers are negated causing a subtraction to be performed during the internal summation of products, when the NEGate controls are HIGH, NEG1 negates the product A x B, while NEG2 acts on the output of the multiplier which generates the product C x D. When the length controls ADEL—DDEL are set to zero, these controls indicate the operation to be performed on data input during the same clock. As nonzero values for ADEL—DDEL do not affect the pipelining of these controls, their effect is not synchronous with the data input in these cases. |

| RND      | C2                  | 5               | <b>Round.</b> When the rounding control is HIGH, the 24-bit sum of products resulting from data input during that clock is rounded to 16 bits. When enabled rounding is automatically performed only during the first cycle of each accumulation sequence, to avoid the accumulation of roundoff errors.                                                                                                                                                                                                                                                                                             |

| FT       | E11                 | 84              | <b>Feedthrough.</b> When the Feedthrough control is HIGH, the pipeline delay through the cascade data path is minimized to simplify the cascading of multiple devices. When FT is LOW and ADEL through DDEL are all set to 0, the data inputs are aligned, such that $S(n+6) = CAS(n) + A(n)B(n) + C(n)D(n)$ . See Table 2.                                                                                                                                                                                                                                                                          |

| CASEN    | D13                 | 83              | Cascade Enable. Data presented at the cascade data input port are latched and accumulated internally when the input enable CASEN during that clock is LOW. When CASEN is HIGH, the cascade input port is ignored.                                                                                                                                                                                                                                                                                                                                                                                    |

| ACC      | B2                  | 2               | <b>Accumulate.</b> When the registered ACCumulator control is LOW, no internal accumulation will be performed on the data input during the current clock, effectively clearing the prior accumulated sum. When ACC is HIGH, the internal accumulator adds the emerging product to the sum of the previous products and RND is disabled.                                                                                                                                                                                                                                                              |

| SWAP     | К3                  | 28              | Swap Output Words. The user may access both the most and least-significant 16 bits of the 24-bit accumulator by utilizing SWAP. Normal operation of the device, with SWAP = HIGH, outputs the most significant word. Setting SWAP = LOW puts a double-register structure into "toggle" mode, allowing the user to examine the LSW on alternate clocks. New output data will not be clocked into the output registers until SWAP returns HIGH.                                                                                                                                                        |

| ŌĒ       | M1                  | 27              | <b>Output Enable.</b> Data currently in the output registers is available at the output bus $S_{15-0}$ when the asynchronous Output Enable is LOW. When $\overline{\text{OE}}$ is HIGH, the outputs are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                 |

| No Conne |                     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | L12                 | 65              | Do Not Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | D4                  |                 | Index Pin (optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 1. | Data | <b>Formats</b> | and | Bit | Weighting |

|----------|------|----------------|-----|-----|-----------|

|          |      |                |     |     |           |

| 15               | 14              | 13              | 12              | 11               | 10              | 9               | 8               | 7               | 6               | 5               | 4               | 3               | 2               | 1              | 0                     | BIT                                          |

|------------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------------|----------------------------------------------|

|                  |                 |                 |                 | -2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup>  | 2 <sup>8</sup>  | 2 <sup>7</sup>  | 2 <sup>6</sup>  | 2 <sup>5</sup>  | 2 <sup>4</sup>  | 2 <sup>3</sup>  | 2 <sup>2</sup>  | 2 <sup>1</sup> | 2 <sup>0</sup>        | DATA (A <sub>11-0</sub> -D <sub>11-0</sub> ) |

| -2 <sup>23</sup> | 2 <sup>22</sup> | 2 <sup>21</sup> | 2 <sup>20</sup> | 2 <sup>19</sup>  | 2 <sup>18</sup> | 2 <sup>17</sup> | 2 <sup>16</sup> | 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup>        | CASCADE INPUT (CAS <sub>15-0</sub> )         |

|                  |                 |                 |                 |                  |                 |                 |                 |                 |                 | -               |                 |                 |                 |                | SUN                   | И (S <sub>15-0</sub> )                       |

| 2 <sup>15</sup>  | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup>  | 2 <sup>10</sup> | 2 <sup>9</sup>  | 2 <sup>8</sup>  | 2 <sup>7</sup>  | 2 <sup>6</sup>  | 2 <sup>5</sup>  | 2 <sup>4</sup>  | 2 <sup>3</sup>  | 2 <sup>2</sup>  | 2 <sup>1</sup> | <b>2</b> <sup>0</sup> | LSW                                          |

| -2 <sup>23</sup> | 2 <sup>22</sup> | 2 <sup>21</sup> | 2 <sup>20</sup> | 2 <sup>19</sup>  | 2 <sup>18</sup> | 2 <sup>17</sup> | 2 <sup>16</sup> | 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup>        | MSW                                          |

#### Notes:

A minus sign indicates the two's complement sign bit.

RND adds 1 to the 2<sup>7</sup> position if ACC is low.

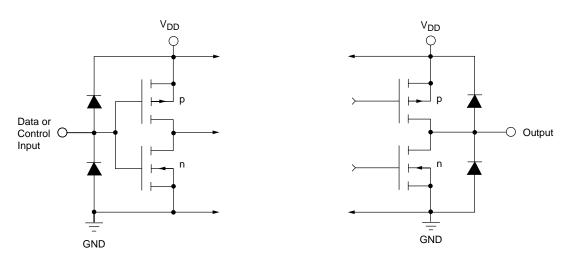

# **Equivalent Circuits and Threshold Levels**

Figure 1. Equivalent Digital Input Circuit

Figure 2. Equivalent Digital Output Circuit

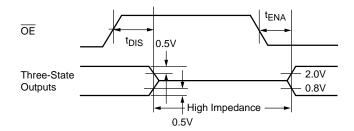

Figure 3. Threshold Levels for Three-State Measurement

# Absolute Maximum Ratings (beyond which the device may be damaged)1

| Parameter                                                             | Min  | Max                   | Unit |

|-----------------------------------------------------------------------|------|-----------------------|------|

| Supply Voltage                                                        | -0.5 | 7.0                   | V    |

| Input Voltage                                                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Applied Voltage (Output) <sup>2</sup>                                 | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Externally Forced Current (Output) 3,4                                | -3.0 | 6.0                   | mA   |

| Output Short Circuit Duration (single output in HIGH state to ground) |      | 1                     | sec  |

| Operating, Ambient Temperature                                        | -20  | 110                   | °C   |

| Operating, Junction Temperature                                       |      | 140                   | °C   |

| Storage Temperature                                                   | -65  | 150                   | °C   |

| Lead, Soldering (10 seconds)                                          |      | 300                   | °C   |

#### Notes:

- Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

# **Operating Conditions**

| Paran            | neter                          |             | Min  | Nom | Max  | Units |

|------------------|--------------------------------|-------------|------|-----|------|-------|

| $V_{DD}$         | Power Supply Voltage           |             | 4.75 | 5.0 | 5.25 | V     |

| f <sub>CLK</sub> | Clock frequency                | TMC2249A    |      |     | 25   | MHz   |

|                  |                                | TMC2249A-1  |      |     | 40   | MHz   |

|                  |                                | TMC2249A-2  |      |     | 60   | MHz   |

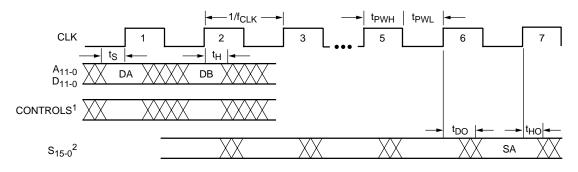

| t <sub>PWH</sub> | CLK pulse width, HIGH          |             | 6    |     |      | ns    |

| t <sub>PWL</sub> | CLK pulse width, LOW           |             | 7    |     |      | ns    |

| t <sub>S</sub>   | Input Data Set-up Time         |             | 6    |     |      | ns    |

| t <sub>H</sub>   | Input Data Hold Time           |             | 1.5  |     |      | ns    |

| V <sub>IH</sub>  | Input Voltage, Logic HIGH      | Data Inputs | 2.0  |     |      | V     |

|                  |                                | CLK Input   | 2.2  |     |      | V     |

| V <sub>IL</sub>  | Input Voltage, Logic LOW       |             |      |     | 0.8  | V     |

| I <sub>OH</sub>  | Output Current, Logic HIGH     |             |      |     | -2.0 | mA    |

| I <sub>OL</sub>  | Output Current, Logic LOW      |             |      |     | 4.0  | mA    |

| T <sub>A</sub>   | Ambient Temperature, Still Air |             | 0    |     | 70   | °C    |

# **Electrical Characteristics**

| Param            | neter                                       | Conditions                                          | Min | Тур | Max | Units |

|------------------|---------------------------------------------|-----------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub>  | Total Power Supply                          | $V_{DD} = Max, C_{LOAD} = 25pF, f_{CLK} = Max$      |     |     |     |       |

|                  | Current                                     | TMC2249A                                            |     |     | 75  | mA    |

|                  |                                             | TMC2249A-1                                          |     |     | 105 | mA    |

|                  |                                             | TMC2249A-2                                          |     |     | 145 | mA    |

| I <sub>DDU</sub> | Power Supply Current,                       | $V_{DD} = Max, \overline{OE} = HIGH, f_{CLK} = Max$ |     |     |     |       |

|                  | Unloaded                                    | TMC2249A                                            |     |     | 68  | mA    |

|                  |                                             | TMC2249A-1                                          |     |     | 92  | mA    |

|                  |                                             | TMC2249A-2                                          |     |     | 124 | mA    |

| I <sub>DDQ</sub> | Power Supply Current,<br>Quiescent          | V <sub>DD</sub> = Max, CLK = LOW                    |     |     | 5   | mA    |

| C <sub>PIN</sub> | I/O Pin Capacitance                         |                                                     |     | 5   |     | pF    |

| I <sub>IH</sub>  | Input Current, HIGH                         | $V_{DD} = Max, V_{IN} = V_{DD}$                     |     |     | ±10 | μΑ    |

| I <sub>IL</sub>  | Input Current, LOW                          | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0 V        |     |     | ±10 | μΑ    |

| l <sub>OZH</sub> | Hi-Z Output Leakage<br>Current, Output HIGH | $V_{DD} = Max, V_{IN} = V_{DD}$                     |     |     | ±10 | μA    |

| I <sub>OZL</sub> | Hi-Z Output Leakage<br>Current, Output LOW  | $V_{DD} = Max, V_{IN} = 0 V$                        |     |     | ±10 | μA    |

| los              | Short-Circuit Current                       |                                                     | -20 |     | -80 | mA    |

| V <sub>OH</sub>  | Output Voltage, HIGH                        | S <sub>15-0</sub> , I <sub>OH</sub> = Max           | 2.4 |     |     | V     |

| V <sub>OL</sub>  | Output Voltage, LOW                         | S <sub>15-0</sub> , I <sub>OL</sub> = Max           |     |     | 0.4 | V     |

# **Switching Characteristics**

| Param            | eter                             | Conditions <sup>1</sup>   | Min | Тур | Max | Units |

|------------------|----------------------------------|---------------------------|-----|-----|-----|-------|

| t <sub>DO</sub>  | Output Delay Time                | C <sub>LOAD</sub> = 25 pF |     |     | 14  | ns    |

| t <sub>HO</sub>  | Output Hold Time                 | C <sub>LOAD</sub> = 25 pF | 2.5 |     |     | ns    |

| t <sub>ENA</sub> | Three-State Output Enable Delay  | C <sub>LOAD</sub> = 0 pF  |     |     | 12  | ns    |

| t <sub>DIS</sub> | Three-State Output Disable Delay | C <sub>LOAD</sub> = 0 pF  |     |     | 12  | ns    |

#### Note:

1. All transitions are measured at a 1.5V level except for  $t_{\text{ENA}}$  and  $t_{\text{DIS}}$ .

Figure 4. Timing Diagram

$<sup>^{1}\</sup>text{Except}\ \overline{\text{OE}}.$   $^{2}\text{Assumes}\ \overline{\text{OE}}$  = LOW and ADEL-DDEL set to 0.

### **Application Notes**

The TMC2249A is a flexible signal and image processing building block with numerous user-selectable functions which expand its usefulness. Table 2 clarifies the operation of the device, demonstrating the various feature available to the user and the timing delays incurred.

**Table 2. TMC2249A Operation Sequence**

| CLK | ADEL | A <sub>11-0</sub> | BDEL | B <sub>11-0</sub> | CDEL | C <sub>11-0</sub> | DDEL | D <sub>11-0</sub> | NEG1 | NEG2 | CAS <sub>15-0</sub> | FT | ACC | RND | SWAP | S <sub>15-0</sub>                                     |

|-----|------|-------------------|------|-------------------|------|-------------------|------|-------------------|------|------|---------------------|----|-----|-----|------|-------------------------------------------------------|

| 1   | 0    | A(1)              | 0    | B(1)              | 0    | C(1)              | 0    | D(1)              | L    | L    | 0                   | L  | L   | Н   | Н    | _                                                     |

| 2   | 0    | A(2)              | 0    | B(2)              | 0    | C(2)              | 0    | D(2)              | L    | Н    | 0                   | L  | L   | Н   | Н    | _                                                     |

| 3   | 0    | A(3)              | 0    | B(3)              | 0    | C(3)              | 0    | D(3)              | Н    | L    | 0                   | L  | L   | L   | Н    | _                                                     |

| 4   | 0    | A(4)              | 0    | B(4)              | 0    | C(4)              | 0    | D(4)              | L    | L    | CAS(4)              | L  | L   | L   | Н    | _                                                     |

| 5   | 0    | A(5)              | 0    | B(5)              | 0    | C(5)              | 0    | D(5)              | L    | L    | 0                   | L  | L   | L   | Н    | _                                                     |

| 6   | 0    | A(6)              | 0    | B(6)              | 0    | C(6)              | 0    | D(6)              | L    | L    | 0                   | L  | L   | Н   | Н    | $(A(1) \times B(1) + C(1) \times D(1) + 2^{7})_{ms}$  |

| 7   | 0    | A(7)              | 0    | B(7)              | 0    | C(7)              | 0    | D(7)              | L    | L    | 0                   | L  | Н   | Х   | Н    | $(A(2) \times B(2)-C(2) \times D(2)+2^{7})_{MS}$      |

| 8   | 0    | A(8)              | 0    | B(8)              | 0    | C(8)              | 0    | D(8)              | L    | L    | CAS(8)              | Н  | L   | L   | L    | $(-A(3) \times B(3) + C(3) \times D(3))_{mS}$         |

| 9   | 0    | A(9)              | 0    | B(9)              | 0    | C(9)              | 0    | D(9)              | L    | L    | 0                   | L  | L   | Н   | Н    | $(A(4) \times B(4) + C(4) \times D(4) + CAS(4))_{MS}$ |

| 10  |      |                   |      |                   |      |                   |      |                   |      |      |                     |    |     |     |      | $(A(5) \times B(5) + C(5) \times D(5) + CAS(8))_{ms}$ |

| 11  |      |                   |      |                   |      |                   |      |                   |      |      |                     |    |     |     |      | $(A(6) \times B(6) + C(6) \times D(6) + 2^{7})_{ms}$  |

| 12  |      |                   |      |                   |      |                   |      |                   |      |      |                     |    |     |     |      | $(A(7) \times B(7) + C(7) \times D(7) + S(11))_{ms}$  |

| 13  |      |                   |      |                   |      |                   |      |                   |      |      |                     |    |     |     |      | (S(12)) <sub> s</sub>                                 |

| 14  |      |                   |      |                   |      |                   |      |                   |      |      |                     |    |     |     |      | $(A(9) \times B(8) + C(7) \times D(6) + 2^{7})_{ms}$  |

CASEN = 0, H=HIGH, L=LOW, "ms" indicates most significant output word (bits 23-8), "ls" indicates least significant word (bits 15-0). The appropriate enables for the indicated data are assumed, otherwise '-' indicates that port not enabled. Note that the output data summations including A(8)-D(8) is lost, since the output on cycle 13 is swapped to the LSW of S(12) on cycle 8. In general, RND may be left high unless the ls output is to be used, as on line 8 above.

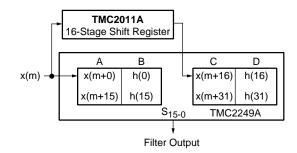

#### **Digital Filtering**

The input structure of the TMC2249A demonstrates great versatility when all four multiplier inputs and the programmable delay registers are utilized.

Table 3 and Table 4 illlustrate how a direct-form symmetric FIR filter of up to 32 taps can be implemented. By utilizing

the four input delay registers as pipelined storage banks, the user can store up to 32 coefficient-data word pairs, split into alternate "even" and "odd" halves. Two taps of the filter are calculated on each clock, and the user then increments/decrements the delay words (ADEL-DDEL). The sums of products are successively added to the global sum in the internal accumulator.

Table 3. FIR Filtering with the TMC2249A—Initial Data Loading

| Register Position (Hex) | Even Data<br>A | Odd Data<br>C | Coefficient<br>B | Storage<br>D |

|-------------------------|----------------|---------------|------------------|--------------|

| 0                       | x(31)          | x(30)         | h(0)             | h(1)         |

| 1                       | x(29)          | x(28)         | h(2)             | h(3)         |

| 2                       | x(27)          | x(26)         | h(4)             | h(5)         |

| 3                       | x(25)          | x(24)         | h(6)             | h(7)         |

| 4                       | x(23)          | x(22)         | h(8)             | h(9)         |

| 5                       | x(21)          | x(20)         | h(10)            | h(11)        |

| 6                       | x(19)          | x(18)         | h(12)            | h(13)        |

| 7                       | x(17)          | x(16)         | h(14)            | h(15)        |

| 8                       | x(15)          | x(14)         | h(15)            | h(14)        |

| 9                       | x(13)          | x(12)         | h(13)            | h(12)        |

| A                       | x(11)          | x(10)         | h(11)            | h(10)        |

| В                       | x(9)           | x(8)          | h(9)             | h(8)         |

| С                       | x(7)           | x(6)          | h(7)             | h(6)         |

| D                       | x(5)           | x(4)          | h(5)             | h(4)         |

| E                       | x(3)           | x(2)          | h(3)             | h(2)         |

| F                       | x(1)           | x(0)          | h(1)             | h(0)         |

Once all of the products of the desired taps have been summed, the result is available at the output. The user then "pushes" a new time-data sample on to the appropriate even or odd data register "stack" and reiterates the summation. Note that the coefficient bank "pointers", the BDEL and DDEL delay words, are alternately incremented and decremented on successive filter passes to maintain alignment between the incoming data samples and their respective coefficients.

The effective filter speed is calculated by dividing the clock rate by one-half the number of taps implemented.

Alternatively, non-symmetric FIR filters can be implemented using the TMC2249A in a similar fashion. Here, a shift register is used to delay the incoming data fed to the A input by an amount equal to one-half the length of the filter (the length of the A delay register).

As shown in Figure 5, the data is then sent to the C input, thus "stacking" the A and C delay registers to create a single N-tap FIR filter. The incremented delay words (ADEL-DDEL) for all four inputs are identical. Again, the filter throughput is equal to the clock speed divided by one-half the number of taps implemented.

Figure 5. Non-Symmetric 32-Tap FIR Filtering Using the TMC2249A

Table 4. FIR Filtering - Operation Sequence

| Cycle | Push<br>A | В | Push<br>C | D | ADEL | CDEL | BDEL | DDEL | ACC | ENA | ENB | ENC | END | Convolutional Sum        | Resultant<br>Output |

|-------|-----------|---|-----------|---|------|------|------|------|-----|-----|-----|-----|-----|--------------------------|---------------------|

| 1     | -         | - | -         | - | 0    | 0    | 0    | 0    | L   | Н   | Н   | Н   | Н   | x(31)•h(0)+x(30)•h(1)    | See Note 2          |

| 2     | -         | - | -         | - | 1    | 1    | 1    | 1    | Н   | Н   | Н   | Н   | Н   | +x(29)•h(2)+x(28)•h(3)   |                     |

| 3     | -         | - | -         | _ | 2    | 2    | 2    | 2    | Н   | Н   | Н   | Н   | Н   | +x(27)•h(4)+x(26)•h(5)   |                     |

| 4     | _         | - | -         | - | 3    | 3    | 3    | 3    | Н   | Н   | Н   | Н   | Н   | +x(25)•h(6)+x(24)•h(7)   |                     |

| 5     | _         | - | -         | - | 4    | 4    | 4    | 4    | Н   | Н   | Н   | Н   | Н   | +x(23)•h(8)+x(22)•h(9)   |                     |

| 6     | -         | - | -         | - | 5    | 5    | 5    | 5    | Н   | Н   | Н   | Н   | Н   | +x(21)•h(10)+x(20)•h(11) |                     |

| 7     | _         | - | -         | - | 6    | 6    | 6    | 6    | Н   | Н   | Н   | Н   | Н   | +x(19)•h(12)+x(18)•h(13) |                     |

| 8     | -         | - | -         | - | 7    | 7    | 7    | 7    | Н   | Н   | Н   | Н   | Н   | +x(17)•h(14)+x(16)•h(15) |                     |

| 9     | -         | - | -         | - | 8    | 8    | 8    | 8    | Н   | Н   | Н   | Н   | Н   | +x(15)•h(15)+x(14)•h(14) |                     |

| 10    | -         | - | -         | - | 9    | 9    | 9    | 9    | Н   | Н   | Н   | Н   | Н   | +x(13)•h(13)+x(12)•h(12) |                     |

| 11    | -         | - | -         | - | Α    | Α    | Α    | Α    | Н   | Н   | Н   | Н   | Н   | +x(11)•h(11)+x(10)•h(10) |                     |

| 12    | -         | - | -         | - | В    | В    | В    | В    | Н   | Н   | Н   | Н   | Н   | +x(9)•h(9)+x(8)•h(8)     |                     |

| 13    | -         | - | -         | - | С    | С    | С    | С    | Н   | Н   | Н   | Н   | Н   | +x(7)•h(7)+x(6)•h(6)     |                     |

| 14    | -         | - | -         | - | D    | D    | D    | D    | Н   | Н   | Н   | Н   | Н   | +x(5)•h(5)+x(4)•h(4)     |                     |

| 15    | -         | - | -         | - | E    | E    | E    | E    | Н   | Н   | Н   | Н   | Н   | +x(3)•h(3)+x(2)•h(2)     |                     |

| 16    | -         | - | x(32)     | - | F    | F    | F    | F    | Н   | Н   | Н   | L   | Н   | +x(1)•h(1)+x(0)•h(0)     |                     |

| 17    | -         | - | -         | - | 0    | 0    | F    | F    | Н   | Н   | Н   | Н   | Н   | +x(31)•h(1)+x(32)•h(0)   |                     |

| 18    | -         | - | -         | - | 1    | 1    | E    | E    | Н   | Н   | Н   | Н   | Н   | +x(29)•h(3)+x(30)•h(2)   |                     |

| 19    | -         | - | -         | - | 2    | 2    | D    | D    | Н   | Н   | Н   | Н   | Н   | +x(27)•h(5)+x(28)•h(4)   |                     |

| 20    | -         | - | -         | - | 3    | 3    | С    | С    | Н   | Н   | Н   | Н   | Н   | +x(25)•h(7)+x(26)•h(6)   |                     |

| 21    | -         | - | -         | - | 4    | 4    | В    | В    | Н   | Н   | Н   | Н   | Н   | +x(23)•h(9)+x(24)•h(8)   |                     |

|       |           |   |           |   |      |      |      |      |     |     |     |     |     |                          |                     |

|       |           |   |           |   |      |      |      |      |     |     |     |     |     |                          |                     |

#### Notes:

1. If only the 16 MSBs of the result are used, the user may leave RND HIGH and SWAP low. If the 16 LSBs or all 24 bits of the result are used, then RND should be set low.

2.

$$s = \sum_{k=0}^{15} (x(k)h(k) + x(k+16)h(k))$$

#### **Complex Arithmetic Functions**

The TMC2249A can also be used to perform complex arithmetic functions. The basic function performed by the device, ignoring the delay controls,

$$SUM = (\pm A \bullet B) + (\pm C \bullet D)$$

can realize in two steps the familiar summation:

$$(P+jR)(S+jT)=(PS-RT)+j(PT+SR)$$

$$(1) (2)$$

by loading the TMC2249A as follows:

|      |   | T | Resultant |   |      |      |         |

|------|---|---|-----------|---|------|------|---------|

| Step | Α | В | С         | D | NEG1 | NEG2 | Output  |

| 1    | Р | S | R         | Т | L    | Н    | (PS-RT) |

| 2    | Р | Т | R         | S | L    | L    | (PT+SR) |

where H and L indicate a logic HIGH and LOW.

Thus we can perform a complex multiplication in two clock cycles. Notice that the user must switch the two components of the second input vector between the B and D inputs to obtain the second complex summation.

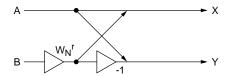

#### Calculating a Butterfly

Taking advantage of the complex multiply which we implemented above using the TMC2249A, we can expand slightly to calculate a Radix-2 Butterfly, the core of the Fast Fourier Transform algorithm. To review, the Butterfly is calculated as shown in Figure 6.

Figure 6. Signal Flow of Radix-2 Butterfly

Where

$$X=A+B(W_N^r)$$

$$Y=A-B(W_N^r),$$

and  $W_N^{\ r}$  is the complex phase coefficient, or "twiddle factor" for the N-point transform, which is:

$$\begin{array}{lll} W_N^{\ r} & = & e^{j(2\pi/N)} \\ & = & \cos(2\pi/N) + j(\sin(2\pi/N)) \\ & = & Re(W) + jIm(W) \end{array}$$

with Re and Im indicating the real and imaginary parts of the vector.

Expanding the complex vectors A and B to calculate X and Y, we get:

$$X = (Re(A)+jlm(A))+(Re(B)Re(W)-lm(B)lm(W)+j(Re(B)lm(W)+lm(B)Re(W)))$$

$$= (Re(A)+Re(B)Re(W)-lm(B)lm(W))+j(lm(A)+Re(B)lm(W)+lm(B)Re(W))$$

$$=$$

Re(X)+ $i$ lm(X)

and,

$$Y = (Re(A)+jlm(A))-(Re(B)Re(W)-lm(B)lm(W)+j(Re(B)lm(W)+lm(B)Re(W)))$$

$$=$$

Re(Y)+ $j$ lm(Y)

The butterfly is then neatly implemented in four clocks, as follows:

|      |       | Result- |       |       |              |      |      |               |

|------|-------|---------|-------|-------|--------------|------|------|---------------|

| Step | Α     | В       | С     | D     | CAS<br>Input | NEG1 | NEG2 | ant<br>Output |

| 1    | Re(B) | Re(W)   | Im(B) | Im(W) | Re(A)        | L    | Н    | Re(X)         |

| 2    | Re(B) | Re(W)   | Im(B) | Im(W) | Re(A)        | Н    | L    | Re(Y)         |

| 3    | Re(B) | Im(W)   | Im(B) | Re(W) | Im(A)        | L    | L    | Im(X)         |

| 4    | Re(B) | Im(W)   | Im(B) | Re(W) | Im(A)        | Н    | Н    | Im(Y)         |

Notice again that the components of the second vector must be switched by the user on the second half of the computation, as well as the parts of the vector presented to the cascade input.

#### **Quadrature Modulation**

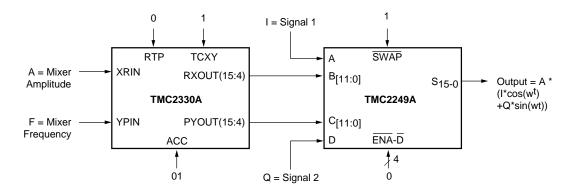

The TMC2249A can also be used to advantage as a digital-domain complex frequency synthesizer, as demonstrated in Figure 7.

Here, orthogonal sinusoidal waveforms are generated digitally in the TMC2330A Coordinate Transformer. These quadrature phase coefficients are then multiplied with two input signals, such as digitized analog data.

The TMC2249A then adds these products, which can be output directly to a high-speed digital-to-analog converter such as the Fairchild TDC1012 for direct waveform synthesis. This 12-bit, 20MHz DAC is ideally suited to waveform generation, featuring extremely low glitch energy for low spurious harmonics and distortion.

Figure 7. Direct Quadrature Waveform Synthesizer using the TMC2249A and TMC2330A

#### **Related Products**

- TMC2301 Image Resampling Sequencer

- TMC2302A Image Manipulation Sequencer

- TMC2246A Image Filter

- TMC2242B Half-Band Filter

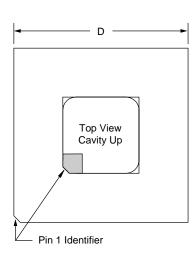

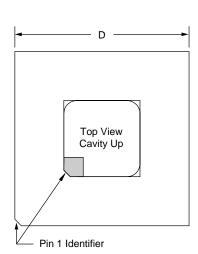

# **Mechanical Dimensions**

#### 120-Lead CPGA Package

| Cumbal | Inc            | hes   | Millin | Notes |       |

|--------|----------------|-------|--------|-------|-------|

| Symbol | Min.           | Max.  | Min.   | Max.  | Notes |

| А      | .080 .160      |       | 2.03   | 4.06  |       |

| A1     | .040           | .060  | 1.01   | 1.53  |       |

| A2     | .125 .215 3.17 |       | 3.17   | 5.46  |       |

| øΒ     | .016           | .020  | 0.40   | 0.51  | 2     |

| øB2    | .050 ا         | NOM.  | 1.27   | 2     |       |

| D      | 1.340          | 1.380 | 33.27  | 35.05 | SQ    |

| D1     | 1.200          | BSC   | 30.48  |       |       |

| е      | .100           | BSC   | 2.54   |       |       |

| L      | .110           | .145  | 2.79   | 3.68  |       |

| L1     | .170           | .190  | 4.31   | 4.83  |       |

| М      | 1              | 3     | 1      | 3     |       |

| N      | 12             | 20    | 12     | 4     |       |

| Р      | .003           | _     | .076   | _     |       |

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Pin diameter excludes solder dip finish.

- 3. Dimension "M" defines matrix size.

- 4. Dimension "N" defines the maximum possible number of pins.

- 5. Orientation pin is at supplier's option.

- 6. Controlling dimension: inch.

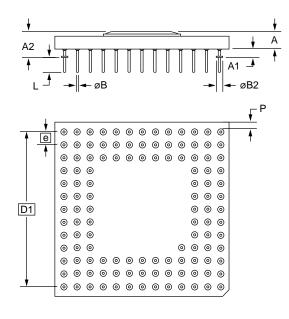

# **Mechanical Dimensions**

#### 120-Lead PPGA Package

| Symbol | Inc            | hes   | Millin    | Notes |       |

|--------|----------------|-------|-----------|-------|-------|

| Symbol | Min.           | Max.  | Min.      | Max.  | Notes |

| Α      | .080 .160      |       | 2.03      | 4.06  |       |

| A1     | .040           | .060  | 1.01      | 1.53  |       |

| A2     | .125 .215 3.17 |       | 3.17      | 5.46  |       |

| øΒ     | .016           | .020  | 0.40 0.51 |       | 2     |

| øB2    | .050 ا         | NOM.  | 1.27      | 2     |       |

| D      | 1.340          | 1.380 | 33.27     | 35.05 | SQ    |

| D1     | 1.200          | BSC   | 30.48     |       |       |

| е      | .100           | BSC   | 2.54      |       |       |

| L      | .110           | .145  | 2.79      | 3.68  |       |

| L1     | .170           | .190  | 4.31      | 4.83  |       |

| М      | 1              | 3     | 1         | 3     |       |

| N      | 12             | 20    | 12        | 4     |       |

| Р      | .003           | _     | .076      | _     |       |

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Pin diameter excludes solder dip finish.

- 3. Dimension "M" defines matrix size.

- 4. Dimension "N" defines the maximum possible number of pins.

- 5. Orientation pin is at supplier's option.

- 6. Controlling dimension: inch.

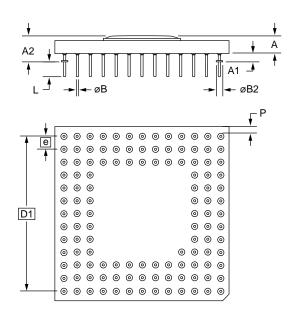

#### **Mechanical Dimensions**

## 120-Lead Metric Quad Flat Package to Pin Grid Array Package (MPGA)

| Symbol | Inc    | hes       | Millin    | Notes     |       |  |

|--------|--------|-----------|-----------|-----------|-------|--|

| Зушьог | Min.   | Max.      | Min.      | Max.      | Notes |  |

| Α      | .309   | .311      | 7.85      | 7.90      |       |  |

| A1     | .145   | .155      | 3.68      | 3.94      |       |  |

| A2     | .080   | .090      | 2.03      | 2.29      |       |  |

| A3     | .050   | .050 TYP. |           | 1.27 TYP. |       |  |

| øΒ     | B .016 |           | 0.40      | 0.51      | 2     |  |

| øB2    | .050 I | NOM.      | 1.27      | 2         |       |  |

| D      | 1.355  | 1.365     | 34.42     | 34.67     | SQ    |  |

| D1     | 1.200  | BSC       | 30.48 BSC |           |       |  |

| е      | .100   | BSC       | 2.54      |           |       |  |

| L      | .175   | .185      | 4.45      | 4.70      |       |  |

| М      | 1      | 3         | 1         | 3         |       |  |

| N      | 120    |           |           | 120       |       |  |

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Pin diameter excludes solder dip finish.

- 3. Dimension "M" defines matrix size.

- 4. Dimension "N" defines the maximum possible number of pins.

- 5. Orientation pin is at supplier's option.

- 6. Controlling dimension: inch.

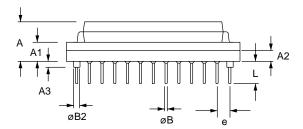

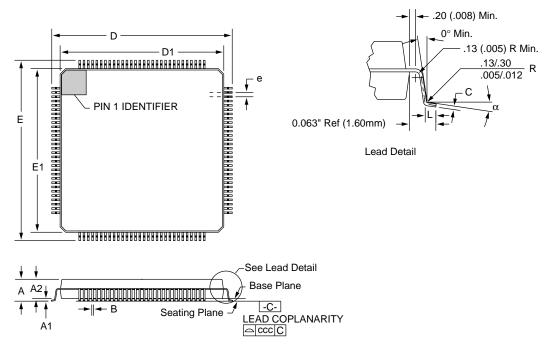

#### **Mechanical Dimensions**

#### 120-Lead MQFP Package

| Symbol | Inc   | hes   | Millin | Notes |       |

|--------|-------|-------|--------|-------|-------|

| Symbol | Min.  | Max.  | Min.   | Max.  | Notes |

| Α      | _     | .154  | _      | 3.92  |       |

| A1     | .010  | _     | .25    |       |       |

| A2     | .125  | .144  | 3.17   | 3.67  |       |

| В      | .012  | .018  | .30    | .45   | 3, 5  |

| _C     | .005  | .009  | .13    | .23   | 5     |

| D/E    | 1.219 | 1.238 | 30.95  | 31.45 |       |

| D1/E1  | 1.098 | 1.106 | 27.90  | 28.10 |       |

| е      | .0315 | BSC   | .80 I  | BSC   |       |

| L      | .026  | .037  | .65    | .95   | 4     |

| N      | 12    | 20    | 12     |       |       |

| ND     | 3     | 0     | 3      |       |       |

| α      | 0°    | 7°    | 0°     | 7°    |       |

| ccc    | _     | .004  | _      | .10   |       |

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Controlling dimension is millimeters.

- 3. Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be .08mm (.003in.) maximum in excess of the "B" dimension. Dambar cannot be located on the lower radius or the foot.

- 4. "L" is the length of terminal for soldering to a substrate.

- 5. "B" & "C" includes lead finish thickness.

# **Ordering Information**

| Product<br>Number | Temperature<br>Range | Speed<br>Grade | Screening  | Package                                             | Package<br>Marking |

|-------------------|----------------------|----------------|------------|-----------------------------------------------------|--------------------|

| TMC2249AG1C       | 0°C to 70°C          | 25 MHz         | Commercial | 120 Pin Ceramic Pin Grid Array                      | 2249AG1C           |

| TMC2249AG1C1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Pin Ceramic Pin Grid Array                      | 2249AG1C1          |

| TMC2249AG1C2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Pin Ceramic Pin Grid Array                      | 2249AG1C2          |

| TMC2249AH5C       | 0°C to 70°C          | 25 MHz         | Commercial | 120 Pin Plastic Pin Grid Array                      | 2249AH5C           |

| TMC2249AH5C1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Pin Plastic Pin Grid Array                      | 2249AH5C1          |

| TMC2249AH5C2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Pin Plastic Pin Grid Array                      | 2249AH5C2          |

| TMC2249AH6C       | 0°C to 70°C          | 25 MHz         | Commercial | 120 Lead Metric Quad Flat Pack<br>to Pin Grid Array | N/A                |

| TMC2249AH6C1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Lead Metric Quad Flat Pack<br>to Pin Grid Array | N/A                |

| TMC2249AH6C2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Lead Metric Quad Flat Pack<br>to Pin Grid Array | N/A                |

| TMC2249AKEC       | 0°C to 70°C          | 25 MHz         | Commercial | 120 Lead Metric Quad Flat Pack                      | 2249AKEC           |

| TMC2249AKEC1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Lead Metric Quad Flat Pack                      | 2249AKEC1          |

| TMC2249AKEC2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Lead Metric Quad Flat Pack                      | 2249AKEC2          |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.