HIGH-SPEED 3.3V 128K x 36 SYNCHRONOUS BANK-SWITCHABLE DUAL-PORT STATIC RAM WITH 3.3V OR 2.5V INTERFACE

IDT70V7599S

#### Features:

- 128K x 36 Synchronous Bank-Switchable Dual-ported SRAM Architecture

- 64 independent 2K x 36 banks

- 4 megabits of memory on chip

- Bank access controlled via bank address pins

- High-speed data access

- Commercial: 3.4ns (200MHz)/3.6ns (166MHz)/ 4.2ns (133MHz) (max.)

- Industrial: 3.6ns (166MHz)/4.2ns (133MHz) (max.)

- Selectable Pipelined or Flow-Through output mode

- Counter enable and repeat features

- Dual chip enables allow for depth expansion without additional logic

- Full synchronous operation on both ports

- 5ns cycle time, 200MHz operation (14Gbps bandwidth)

- Fast 3.4ns clock to data out

- 1.5ns setup to clock and 0.5ns hold on all control, data, and address inputs @ 200MHz

- Data input, address, byte enable and control registers

- Self-timed write allows fast cycle time

- Separate byte controls for multiplexed bus and bus matching compatibility

- LVTTL- compatible, 3.3V (±150mV) power supply for core

- LVTTL compatible, selectable 3.3V (±150mV) or 2.5V (±100mV) power supply for I/Os and control signals on each port

- Industrial temperature range (-40°C to +85°C) is available at 166MHz and 133MHz

- Available in a 208-pin Plastic Quad Flatpack (PQFP), 208-pin fine pitch Ball Grid Array (fpBGA), and 256-pin Ball Grid Array (BGA)

- Supports JTAG features compliant with IEEE 1149.1

### **Description:**

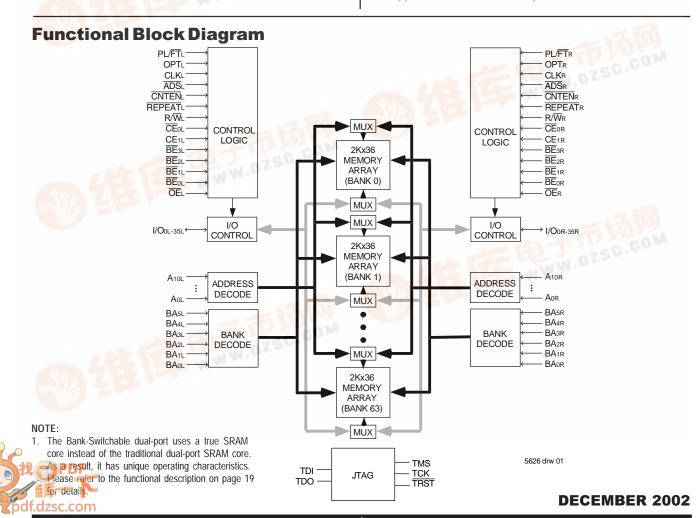

The IDT70V7599 is a high-speed 128Kx36 (4Mbit) synchronous Bank-Switchable Dual-Ported SRAM organized into 64 independent 2Kx36 banks. The device has two independent ports with separate control, address, and I/O pins for each port, allowing each port to access any 2Kx36 memory block not already accessed by the other port. Accesses by the ports into specific banks are controlled via the bank address pins under the user's direct control.

Registers on control, data, and address inputs provide minimal setup and hold times. The timing latitude provided by this approach allows systems to be designed with very short cycle times. With an input data register, the IDT70V7599 has been optimized for applications having unidirectional or bidirectional data flow in bursts. An automatic power down feature, controlled by CEo and CE1, permits the on-chip circuitry of each port to enter a very low standby power mode. The dual chip enables also facilitate depth expansion.

The 70V7599 can support an operating voltage of either 3.3V or 2.5V on one or both ports, controllable by the OPT pins. The power supply for the core of the device(VDD) remains at 3.3V. Please refer also to the functional description on page 19.

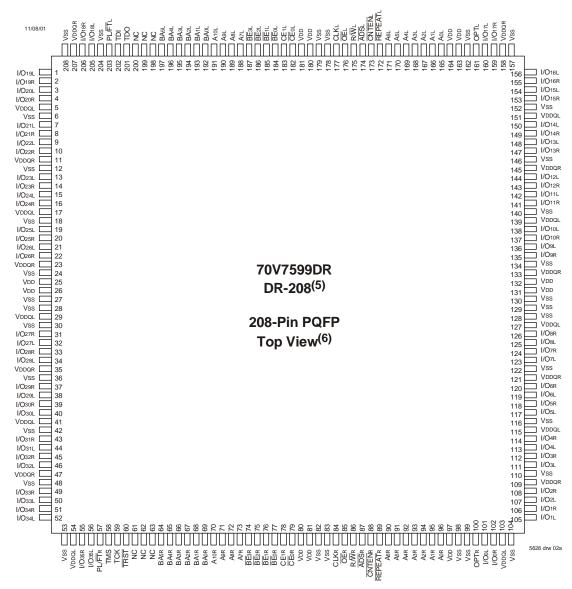

### Pin Configuration(1,2,3,4)

11/08/01

| A1<br>IO19L               | A2<br>IO18L           | A3<br>Vss    | A4<br>TDO    | A5<br>NC   | A6<br>BA5L | A7<br>BA1L        | A8<br>A8L               | A9<br>BE1L              | A10<br>VDD             | A11<br>CLKL    | A12<br>CNTENL             | A13<br>A4L | A14<br>A0L            | A15<br>OPTL   | A16<br>I/O17L         | A17<br>Vss    |

|---------------------------|-----------------------|--------------|--------------|------------|------------|-------------------|-------------------------|-------------------------|------------------------|----------------|---------------------------|------------|-----------------------|---------------|-----------------------|---------------|

| B1<br>I/O <sub>20</sub> R | B2<br>Vss             | B3<br>I/O18R | B4<br>TDI    | B5<br>NC   | B6<br>BA2L | B7<br>A9L         | B8<br>BE2L              | B9<br>CE <sub>0</sub> L | B10<br>Vss             | B11<br>ADSL    | B12<br>A5L                | B13<br>A1L | B14<br>Vss            | B15<br>VDDQR  | B16<br>I/O16L         | B17<br>I/O15R |

| C1<br>VDDQL               | C2<br>I/O19R          | C3<br>Vddqr  | C4<br>PL/FTL | C5<br>NC   | C6<br>BA3L | C7<br>A10L        | C8<br>BE3L              | C9<br>CE1L              | C10<br>Vss             | C11<br>R/WL    | C12<br>A6L                | C13<br>A2L | C14<br>VDD            | C15<br>I/O16R | C16<br>I/O15L         | C17<br>VSS    |

| D1<br>I/O22L              | D2<br>Vss             | D3<br>I/O21L | D4<br>I/O20L | D5<br>BA4L | D6<br>BA0L | D7<br>A7L         | D8<br>BE <sub>0</sub> L | D9<br>Vdd               | D10<br>OEL             | D11<br>REPEATL | D12<br>A3L                | D13<br>VDD | D14<br>I/O17R         | D15<br>VDDQL  | D16<br>I/O14L         | D17<br>I/O14R |

| E1<br>I/O23L              | E2<br>I/O22R          | E3<br>Vddqr  | E4<br>I/O21R |            |            |                   |                         |                         |                        |                |                           |            | E14<br>I/O12L         | E15<br>I/O13R | E16<br>Vss            | E17<br>I/O13L |

| F1<br>VDDQL               | F2<br>I/O23R          | F3<br>I/O24L | F4<br>Vss    |            |            |                   |                         |                         |                        |                |                           |            | F14<br>VSS            | F15<br>I/O12R | F16<br>I/O11L         | F17<br>VDDQR  |

| G1<br>I/O26L              | G2<br>Vss             | G3<br>I/O25L | G4<br>I/O24R |            |            |                   |                         |                         |                        |                |                           |            | G14<br>I/ <b>O</b> 9L | G15<br>Vddql  | G16<br>I/O10L         | G17<br>I/O11R |

| H1<br>VDD                 | H2<br>I/O26R          | H3<br>Vddqr  | H4<br>I/O25R |            |            |                   | _                       | /7599<br>208            |                        |                |                           |            | H14<br>VDD            | H15<br>IO9R   | H16<br>Vss            | H17<br>I/O10R |

| J1<br>VDDQL               | J2<br>Vdd             | J3<br>Vss    | J4<br>Vss    |            |            |                   |                         |                         |                        |                |                           |            | J14<br>Vss            | J15<br>Vdd    | J16<br>Vss            | J17<br>Vddqr  |

| K1<br>I/O28R              | K2<br>VSS             | K3<br>I/O27R | K4<br>Vss    |            |            |                   | 208-F<br>Top            | Vie                     |                        | <b>L</b>       |                           |            | K14<br>I/O7R          | K15<br>VDDQL  | K16<br>I/ <b>O</b> 8R | K17<br>Vss    |

| L1<br>I/O29R              | L2<br>I/ <b>O</b> 28L | L3<br>Vddqr  | L4<br>I/O27L |            |            |                   |                         |                         |                        |                |                           |            | L14<br>I/O6R          | L15<br>I/O7L  | L16<br>Vss            | L17<br>I/O8L  |

| M1<br>VDDQL               | M2<br>I/ <b>O</b> 29L | M3<br>I/O30R | M4<br>Vss    |            |            |                   |                         |                         |                        |                |                           |            | M14<br>Vss            | M15<br>I/O6L  | M16<br>I/O5R          | M17<br>VDDQR  |

| N1<br>I/O31L              | N2<br>Vss             | N3<br>I/O31R | N4<br>I/O30L |            |            |                   |                         |                         |                        |                |                           |            | N14<br>I/O3R          | N15<br>VDDQL  | N16<br>I/O4R          | N17<br>I/O5L  |

| P1<br>I/O32R              | P2<br>I/O32L          | P3<br>Vddqr  | P4<br>I/O35R | P5<br>TRST | P6<br>BA5R | P7<br>BA1R        | P8<br>A8R               | P9<br>BE1R              | P10<br>VDD             | P11<br>CLKR    | P12<br>CNTEN <sub>R</sub> | P13<br>A4R | P14<br>I/O2L          | P15<br>I/O3L  | P16<br>Vss            | P17<br>I/O4L  |

| R1<br>Vss                 | R2<br>I/O33L          | R3<br>I/O34R | R4<br>TCK    | R5<br>NC   | R6<br>BA2R | R7<br><b>A</b> 9R | R8<br>BE2R              | R9<br>CE0R              | R10<br>VSS             | R11<br>ADSR    | R12<br>A5R                | R13<br>A1R | R14<br>VSS            | R15<br>VDDQL  | R16<br>I/O1R          | R17<br>VDDQR  |

| T1<br>I/O33R              | T2<br>I/O34L          | T3<br>Vddql  | T4<br>TMS    | T5<br>NC   | T6<br>BA3R | T7<br>A10R        | т8<br><u>ВЕ</u> зк      | T9<br>CE1R              | T10<br>VSS             | T11<br>R/WR    | T12<br>A6R                | T13<br>A2R | T14<br>Vss            | T15<br>I/O0R  | T16<br>VSS            | T17<br>I/O2R  |

| U1<br>Vss                 | U2<br>I/O35L          | uз<br>PL/FTR | U4<br>NC     | U5<br>BA4R | U6<br>BAor | U7<br>A7R         | U8<br>BEOR              | U9<br>VDD               | U10<br><del>OE</del> R | U11<br>REPEATR | U12<br>A3R                | U13<br>Aor | U14<br>VDD            | U15<br>OPTR   | U16<br>I/Ool          | U17<br>I/O1L  |

#### NOTES

- 1. All VDD pins must be connected to 3.3V power supply.

- 2. All VDDQ pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to VIH (3.3V), and 2.5V if OPT pin for that port is set to VIL (0V).

- 3. All Vss pins must be connected to ground supply.

- 4. Package body is approximately 15mm x 15mm x 1.4mm with 0.8mm ball pitch.

- 5. This package code is used to reference the package diagram.

- 6. This text does not indicate orientation of the actual part-marking.

5626 drw 02c

# Pin Configuration<sup>(1,2,3,4)</sup> (con't.)

70V7599BC BC-256<sup>(5)</sup>

256-Pin BGA Top View<sup>(6)</sup>

11/08/01

| A1                 | A2                 | A3                  | A4     | A5    | A6    | A7          | A8                | A9                | A10          | A11     | A12         | A13             | A14                | A15            | A16                |

|--------------------|--------------------|---------------------|--------|-------|-------|-------------|-------------------|-------------------|--------------|---------|-------------|-----------------|--------------------|----------------|--------------------|

| NC                 | TDI                | NC                  | NC     | BA3L  | BA0L  | A8L         | BE <sub>2</sub> L | CE1L              | OEL          | CNTENL  | <b>A</b> 5L | A2L             | A0L                | NC             | NC                 |

| B1                 | B2                 | B3                  | B4     | B5    | B6    | B7          | B8                | B9                | B10          | B11     | B12         | B13             | B14                | B15            | B16                |

| I/O <sub>18L</sub> | NC                 | TDO                 | NC     | BA4L  | BA1L  | A9L         | BE3L              | CEol              | R/WL         | REPEATL | A4L         | A1L             | VDD                | I/O17L         | NC                 |

| C1                 | C2                 | C3                  | C4     | C5    | C6    | C7          | C8                | C9                | C10          | C11     | C12         | C13             | C14                | C15            | C16                |

| I/O18R             | I/O19L             | Vss                 | BA5L   | BA2L  | A10L  | A7L         | BE <sub>1</sub> L | BE <sub>0</sub> L | CLKL         | ADSL    | A6L         | <b>A</b> 3L     | OPTL               | I/O17R         | I/O16L             |

| D1                 | D2                 | D3                  | D4     | D5    | D6    | d7          | d8                | D9                | d10          | D11     | d12         | D13             | D14                | D15            | D16                |

| I/ <b>O</b> 20R    | I/O19R             | I/O <sub>20L</sub>  | PL/FTL | Vddql | VDDQL | Vddqr       | Vddqr             | VDDQL             | Vddql        | VDDQR   | Vddqr       | Vdd             | I/O <sub>15R</sub> | I/O15L         | I/O16R             |

| E1                 |                    | E3                  | E4     | E5    | E6    | E7          | E8                | E9                | E10          | E11     | E12         | E13             | E14                | E15            | E16                |

| I/O21R             |                    | I/O22L              | VddQl  | Vdd   | Vdd   | Vss         | Vss               | Vss               | Vss          | VDD     | VDD         | Vddqr           | I/O13L             | I/O14L         | I/O14R             |

| F1                 | F2                 | F3                  | F4     | F5    | F6    | F7          | F8                | F9                | F10          | F11     | F12         | F13             | F14                | F15            | F16                |

| I/O23L             | I/O22R             | I/ <b>O</b> 23R     | Vddql  | Vdd   | Vss   | Vss         | Vss               | Vss               | Vss          | Vss     | Vdd         | Vddqr           | I/O12R             | I/O13R         | I/O12L             |

| G1                 | G2                 | G3                  | g4     | G5    | G6    | G7          | G8                | <sub>G9</sub>     | G10          | G11     | G12         | G13             | G14                | G15            | G16                |

| I/O24R             | I/O <sub>24L</sub> | I/ <b>O</b> 25L     | Vddqr  | Vss   | Vss   | Vss         | Vss               | Vss               | Vss          | Vss     | Vss         | Vddql           | I/O10L             | I/O11L         | I/O11R             |

| H1                 | H2                 | H3                  | H4     | H5    | H6    | H7          | н8                | H9                | H10          | H11     | H12         | H13             | H14                | H15            | H16                |

| I/O26L             | I/O25R             | I/O26R              | Vddqr  | Vss   | Vss   | Vss         | Vss               | Vss               | Vss          | Vss     | Vss         | Vddql           | I/O9R              | <b>IO</b> 9L   | I/O <sub>10R</sub> |

| J1                 | J2                 | J3                  | J4     | J5    | J6    | J7          | <sub>J8</sub>     | <sup>J9</sup>     | J10          | J11     | J12         | J13             | J14                | J15            | J16                |

| I/O27L             | I/O28R             | I/ <b>O</b> 27R     | Vddql  | Vss   | Vss   | Vss         | Vss               | Vss               | Vss          | Vss     | Vss         | Vddqr           | I/O <sub>8R</sub>  | I/ <b>O</b> 7R | I/O8L              |

| K1                 | K2                 | K3                  | K4     | K5    | K6    | K7          | K8                | к9                | K10          | K11     | K12         | K13             | K14                | K15            | K16                |

| I/O29R             | I/O29L             | I/O28L              | Vddql  | Vss   | Vss   | Vss         | Vss               | Vss               | Vss          | Vss     | Vss         | Vddqr           | I/O6R              | I/O6L          | I/O7L              |

| L1                 | L2                 | L3                  | L4     | L5    | L6    | L7          | L8                | L9                | L10          | L11     | L12         | L13             | L14                | L15            | L16                |

| I/O30L             | I/O31R             | I/O30R              | Vddqr  | Vdd   | Vss   | Vss         | Vss               | Vss               | Vss          | Vss     | Vdd         | Vddql           | I/O5L              | I/O4R          | I/O5R              |

| M1                 | M2                 | M3                  | m4     | M5    | M6    | M7          | M8                | M9                | M10          | M11     | M12         | M13             | M14                | M15            | M16                |

| I/O <sub>32R</sub> | I/O <sub>32L</sub> | I/O <sub>31</sub> L | Vddqr  | Vdd   | Vdd   | Vss         | Vss               | Vss               | Vss          | Vdd     | Vdd         | VDDQL           | I/O3R              | I/ОзL          | I/O4L              |

| N1                 | N2                 | N3                  | N4     | n5    | n6    | n7          | N8                | n9                | n10          |         | N12         | N13             | N14                | N15            | N16                |

| I/O33L             | I/O34R             | I/O33R              | PL/FTR | Vddqr | Vddqr | Vddql       | Vddql             | Vddqr             | Vddqr        |         | Vddql       | V <sub>DD</sub> | I/O2L              | I/O1R          | I/O <sub>2R</sub>  |

| P1                 | P2                 | P3                  | P4     | P5    | P6    | P7          | P8                | P9                | P10          | P11     | P12         | P13             | P14                | P15            | P16                |

| I/O35R             | I/O34L             | TMS                 | BA5R   | BA2R  | A10R  | A7R         | BE1R              | BE0R              | CLKR         | ADSR    | A6R         | A3R             | I/OoL              | I/ <b>O</b> 0R | I/O1L              |

| R1                 | R2                 | R3                  | R4     | R5    | R6    | R7          | R8                | R9                | R10          | R11     | R12         | R13             | R14                | R15            | R16                |

| I/O35L             | NC                 | TRST                | NC     | BA4R  | BA1R  | <b>A</b> 9R | BE3R              | CE0R              | <b>R/W</b> R | REPEATR | <b>A</b> 4R | <b>A</b> 1R     | OPTR               | NC             | NC                 |

| T1                 | T2                 | T3                  | T4     | т5    | T6    | T7          | T8                | T9                | T10          | T11     | T12         | T13             | T14                | T15            | T16                |

| NC                 | TCK                | NC                  | NC     | ВАзк  | BAor  | A8R         | BE2R              | CE1R              | OEr          | CNTENR  | <b>A</b> 5R | <b>A</b> 2R     | Aor                | NC             | NC                 |

#### NOTES

- 1. All VDD pins must be connected to 3.3V power supply.

- 2. All VDDQ pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to VIH (3.3V), and 2.5V if OPT pin for that port is set to VIL (0V).

- 3. All Vss pins must be connected to ground supply.

- 4. Package body is approximately 17mm x 17mm x 1.4mm, with 1.0mm ball-pitch.

- 5. This package code is used to reference the package diagram.

- 6. This text does not indicate orientation of the actual part-marking.

5626 drw 02d

# Pin Configuration<sup>(1,2,3,4)</sup> (con't.)

- 1. All VDD pins must be connected to 3.3V power supply.

- 2. All VDDQ pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to VIH (3.3V), and 2.5V if OPT pin for that port is set to VIH (0V).

- 3. All Vss pins must be connected to ground supply.

- 4. Package body is approximately 28mm x 28mm x 3.5mm.

- 5. This package code is used to reference the package diagram.

- 6. This text does not indicate orientation of the actual part-marking.

### **Pin Names**

| <u>Pin Name</u>     | S                  |                                               |

|---------------------|--------------------|-----------------------------------------------|

| Left Port           | Right Port         | Names                                         |

| CEOL, CE1L          | CEOR, CE1R         | Chip Enables                                  |

| R/WL                | R/WR               | Read/Write Enable                             |

| ŌĒL                 | <del>OE</del> R    | Output Enable                                 |

| BAOL - BA5L         | BAOR - BA5R        | Bank Address <sup>(4)</sup>                   |

| AOL - A10L          | Aor - A10r         | Address                                       |

| 1/O0L - 1/O35L      | I/Oor - I/O35R     | Data Input/Output                             |

| CLKL                | CLKr               | Clock                                         |

| PL/ <del>FT</del> L | PL/FT <sub>R</sub> | Pipeline/Flow-Through                         |

| <del>ADS</del> L    | <del>ADS</del> R   | Address Strobe Enable                         |

| CNTENL              | <u>CNTEN</u> R     | Counter Enable                                |

| REPEATL             | REPEATR            | Counter Repeat <sup>(3)</sup>                 |

| BEOL - BE3L         | BEOR - BE3R        | Byte Enables (9-bit bytes)                    |

| VDDQL               | VDDQR              | Power (I/O Bus) (3.3V or 2.5V) <sup>(1)</sup> |

| OPTL                | OPTr               | Option for selecting VDDQx <sup>(1,2)</sup>   |

| V                   | DD                 | Power (3.3V) <sup>(1)</sup>                   |

| V                   | ss                 | Ground (0V)                                   |

| T                   | DI                 | Test Data Input                               |

| П                   | 00                 | Test Data Output                              |

| T                   | CK                 | Test Logic Clock (10MHz)                      |

| T                   | MS                 | Test Mode Select                              |

| TF                  | RST                | Reset (Initialize TAP Controller)             |

#### 5626 tbl 01

- VDD, OPTx, and VDDOx must be set to appropriate operating levels prior to applying inputs on the I/Os and controls for that port.

- 2. OPTx selects the operating voltage levels for the I/Os and controls on that port. If OPTx is set to VIH (3.3V), then that port's I/Os and controls will operate at 3.3V levels and VDDOX must be supplied at 3.3V. If OPTx is set to VIL (0V), then that port's I/Os and address controls will operate at 2.5V levels and VDDOX must be supplied at 2.5V. The OPT pins are independent of one another—both ports can operate at 3.3V levels, both can operate at 2.5V levels, or either can operate at 3.3V with the other at 2.5V.

- 3. When REPEATx is asserted, the counter will reset to the last valid address loaded via ADSx

- 4. Accesses by the ports into specific banks are controlled by the bank address pins under the user's direct control: each port can access any bank of memory with the shared array that is not currently being accessed by the opposite port (i.e., BAoL BA5L ≠ BAOR BA5R). In the event that both ports try to access the same bank at the same time, neither access will be valid, and data at the two specific addresses targeted by the ports within that bank may be corrupted (in the case that either or both ports are writing) or may result in invalid output (in the case that both ports are trying to read).

# Truth Table I—Read/Write and Enable Control (1,2,3,4)

| ŌE³ | CLK | Œ0 | CE <sub>1</sub> | <u>B</u> E₃ | <b>BE</b> ₂ | BE <sub>1</sub> | BE <sub>0</sub> | R/W | Byte 3<br>I/O <sub>27-35</sub> | Byte 2<br>I/O <sub>18-26</sub> | Byte 1<br>I/O <sub>9-17</sub> | Byte 0<br>I/O <sub>0-8</sub> | MODE                        |

|-----|-----|----|-----------------|-------------|-------------|-----------------|-----------------|-----|--------------------------------|--------------------------------|-------------------------------|------------------------------|-----------------------------|

| Х   | 1   | Н  | Χ               | Χ           | Χ           | Х               | Χ               | Χ   | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Deselected-Power Down       |

| Х   | 1   | Χ  | L               | Χ           | Χ           | Χ               | Χ               | Χ   | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Deselected-Power Down       |

| Х   | 1   | L  | Н               | Н           | Н           | Н               | Н               | Χ   | High-Z                         | High-Z                         | High-Z                        | High-Z                       | All Bytes Deselected        |

| Х   | 1   | L  | Н               | Н           | Н           | Н               | L               | L   | High-Z                         | High-Z                         | High-Z                        | Din                          | Write to Byte 0 Only        |

| Х   | 1   | L  | Н               | Н           | Н           | L               | Н               | L   | High-Z                         | High-Z                         | Din                           | High-Z                       | Write to Byte 1 Only        |

| Х   | 1   | L  | Н               | Н           | L           | Н               | Н               | L   | High-Z                         | Din                            | High-Z                        | High-Z                       | Write to Byte 2 Only        |

| Х   | 1   | L  | Н               | L           | Н           | Н               | Н               | L   | Din                            | High-Z                         | High-Z                        | High-Z                       | Write to Byte 3 Only        |

| Х   | 1   | L  | Н               | Н           | Н           | L               | L               | L   | High-Z                         | High-Z                         | Din                           | Din                          | Write to Lower 2 Bytes Only |

| Х   | 1   | L  | Н               | L           | L           | Н               | Н               | L   | Din                            | Din                            | High-Z                        | High-Z                       | Write to Upper 2 bytes Only |

| Х   | 1   | L  | Н               | L           | L           | L               | L               | L   | Din                            | Din                            | Din                           | Din                          | Write to All Bytes          |

| L   | 1   | L  | Н               | Н           | Н           | Н               | L               | Н   | High-Z                         | High-Z                         | High-Z                        | <b>D</b> оит                 | Read Byte 0 Only            |

| L   | 1   | L  | Н               | Н           | Н           | L               | Н               | Н   | High-Z                         | High-Z                         | <b>D</b> оит                  | High-Z                       | Read Byte 1 Only            |

| L   | 1   | L  | Н               | Н           | L           | Н               | Н               | Н   | High-Z                         | Douт                           | High-Z                        | High-Z                       | Read Byte 2 Only            |

| L   | 1   | L  | Н               | L           | Н           | Н               | Н               | Н   | Dout                           | High-Z                         | High-Z                        | High-Z                       | Read Byte 3 Only            |

| L   | 1   | L  | Н               | Н           | Н           | L               | L               | Н   | High-Z                         | High-Z                         | <b>D</b> оит                  | <b>D</b> оит                 | Read Lower 2 Bytes Only     |

| L   | 1   | L  | Н               | L           | L           | Н               | Н               | Н   | <b>D</b> оит                   | <b>D</b> оит                   | High-Z                        | High-Z                       | Read Upper 2 Bytes Only     |

| L   | 1   | L  | Н               | L           | L           | L               | L               | Н   | <b>D</b> оит                   | <b>D</b> оит                   | <b>D</b> оит                  | <b>D</b> оит                 | Read All Bytes              |

| Н   | Χ   | Х  | Х               | Χ           | Х           | Х               | Х               | Χ   | High-Z                         | High-Z                         | High-Z                        | High-Z                       | Outputs Disabled            |

#### NOTES:

5626 tbl 02

- 1. "H" = VIH, "L" = VIL, "X" = Don't Care.

- 2. ADS, CNTEN, REPEAT are set as appropriate for address access. Refers to Truth Table II for details.

- 3.  $\overline{\text{OE}}$  is an asynchronous input signal.

- 4. It is possible to read or write any combination of bytes during a given access. A few representative samples have been illustrated here.

# Truth Table II—Address and Address Counter Control (1,2,7)

| Address | Previous<br>Address | Addr<br>Used | CLK      | ĀDS              | CNTEN            | REPEAT <sup>(6)</sup> | I/O <sup>(3)</sup> | MODE                                                      |

|---------|---------------------|--------------|----------|------------------|------------------|-----------------------|--------------------|-----------------------------------------------------------|

| An      | Х                   | An           | 1        | L <sup>(4)</sup> | Х                | Н                     | Dvo (n)            | External Address Used                                     |

| Х       | An                  | An + 1       | 1        | Н                | L <sup>(5)</sup> | Н                     | Dvo(n+1)           | Counter Enabled—Internal Address generation               |

| Х       | An + 1              | An + 1       | <b>↑</b> | Н                | Н                | Н                     | Dvo(n+1)           | External Address Blocked—Counter disabled (An + 1 reused) |

| Х       | Х                   | An           | 1        | Х                | Х                | L <sup>(4)</sup>      | Dvo(0)             | Counter Set to last valid ADS load                        |

#### NOTES:

5626 tbl 03

- 1. "H" = VIH. "L" = VIL. "X" = Don't Care.

- 2. Read and write operations are controlled by the appropriate setting of R/W, CEo, CE1, BEn and OE.

- 3. Outputs configured in flow-through output mode: if outputs are in pipelined mode the data out will be delayed by one cycle.

- 4. ADS and REPEAT are independent of all other memory control signals including CEo, CE1 and BEn

- 5. The address counter advances if CNTEN = VIL on the rising edge of CLK, regardless of all other memory control signals including CEo, CE1, BEn.

- 6. When REPEAT is asserted, the counter will reset to the last valid address loaded via ADS. This value is not set at power-up: a known location should be loaded via  $\overline{\text{ADS}}$  during initialization if desired. Any subsequent  $\overline{\text{ADS}}$  access during operations will update the  $\overline{\text{REPEAT}}$  address location.

- 7. The counter includes bank address and internal address. The counter will advance across bank boundaries. For example, if the counter is in Bank 0, at address FFFh, and is advanced one location, it will move to address 0h in Bank 1. By the same token, the counter at FFFh in Bank 63 will advance to 0h in Bank 0. Refer to Timing Waveform of Counter Repeat, page 18. Care should be taken during operation to avoid having both counters point to the same bank (i.e., ensure BAoL - BA<sub>5</sub>L ≠ BA<sub>9</sub>R - BA<sub>5</sub>R), as this condition will invalidate the access for both ports. Please refer to the functional description on page 19 for details.

# Recommended Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient<br>Temperature | GND | VDD                 |  |  |

|------------|------------------------|-----|---------------------|--|--|

| Commercial | 0°C to +70°C           | 0V  | 3.3V <u>+</u> 150mV |  |  |

| Industrial | -40°C to +85°C         | 0V  | 3.3V <u>+</u> 150mV |  |  |

#### NOTE:

1. This is the parameter Ta. This is the "instant on" case temperature.

### **Absolute Maximum Ratings**(1)

| Symbol               | Rating                               | Commercial<br>& Industrial | Unit |

|----------------------|--------------------------------------|----------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND | -0.5 to +4.6               | ٧    |

| TBIAS                | Temperature<br>Under Bias            | -55 to +125                | °C   |

| Tstg                 | Storage<br>Temperature               | -65 to +150                | °C   |

| ЮИТ                  | DC Output Current                    | 50                         | mA   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- VTERM must not exceed VDD + 150mV for more than 25% of the cycle time or 4ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ VDD + 150mV.

# Recommended DC Operating Conditions with VDDQ at 2.5V

| Symbol | Parameter                                        | Min.                | Тур. | Мах.                        | Unit |

|--------|--------------------------------------------------|---------------------|------|-----------------------------|------|

| VDD    | Core Supply Voltage                              | 3.15                | 3.3  | 3.45                        | ٧    |

| VDDQ   | I/O Supply Voltage <sup>(3)</sup>                | 2.4                 | 2.5  | 2.6                         | ٧    |

| Vss    | Ground                                           | 0                   | 0    | 0                           | ٧    |

| VIH    | Input High Voltage<br>(Address & Control Inputs) | 1.7                 | _    | VDDQ + 100mV <sup>(2)</sup> | V    |

| VIH    | Input High Voltage - I/O <sup>(3)</sup>          | 1.7                 |      | VDDQ + 100mV <sup>(2)</sup> | ٧    |

| VIL    | Input Low Voltage                                | -0.3 <sup>(1)</sup> |      | 0.7                         | ٧    |

#### NOTES

5626 tbl 04

5626 tb1 05a

- 1. Undershoot of  $Vil \ge -1.5V$  for pulse width less than 10ns is allowed.

- 2. VTERM must not exceed VDDQ + 100mV.

- 3. To select operation at 2.5V levels on the I/Os and controls of a given port, the OPT pin for that port must be set to VIL (0V), and VDDOX for that port must be supplied as indicated above.

# Recommended DC Operating Conditions with VDDQ at 3.3V

| Symbol | Parameter                                                       | Min.    | Тур. | Max.                        | Unit |

|--------|-----------------------------------------------------------------|---------|------|-----------------------------|------|

| VDD    | Core Supply Voltage                                             | 3.15    | 3.3  | 3.45                        | ٧    |

| VDDQ   | I/O Supply Voltage <sup>(3)</sup>                               | 3.15    | 3.3  | 3.45                        | ٧    |

| Vss    | Ground                                                          | 0       | 0    | 0                           | ٧    |

| VIH    | Input High Voltage<br>(Address & Control Inputs) <sup>(3)</sup> | 2.0     |      | VDDQ + 150mV <sup>(2)</sup> | V    |

| VIH    | Input High Voltage - I/O <sup>(3)</sup>                         | 2.0     | -    | VDDQ + 150mV <sup>(2)</sup> | ٧    |

| VIL    | Input Low Voltage                                               | -0.3(1) | _    | 0.8                         | V    |

#### NOTES

5626 tbl 05b

- 1. Undershoot of  $V_{IL \ge}$  -1.5V for pulse width less than 10ns is allowed.

- 2. VTERM must not exceed VDDQ + 150 mV.

- To select operation at 3.3V levels on the I/Os and controls of a given port, the OPT pin for that port must be set to ViH (3.3V), and VDDOX for that port must be supplied as indicated above.

## Capacitance<sup>(1)</sup>

### (Ta = +25°C, F = 1.0MHz) PQFP ONLY

| Symbol              | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit |

|---------------------|--------------------|---------------------------|------|------|

| CIN                 | Input Capacitance  | V <sub>IN</sub> = 3dV     | 8    | pF   |

| Соит <sup>(3)</sup> | Output Capacitance | Vout = 3dV                | 10.5 | pF   |

5626 tbl 07

#### NOTES:

- 1. These parameters are determined by device characterization, but are not

- 2. 3dV references the interpolated capacitance when the input and output switch from 0V to 3V or from 3V to 0V.

- 3. Cout also references Ci/o.

### **DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 3.3V ± 150mV)**

|            |                                       |                                                                                       | 70V7 | ′599S |      |

|------------|---------------------------------------|---------------------------------------------------------------------------------------|------|-------|------|

| Symbol     | Parameter                             | Test Conditions                                                                       | Min. | Max.  | Unit |

| Li         | Input Leakage Current <sup>(1)</sup>  | VDDQ = Max., VIN = 0V to VDDQ                                                         |      | 10    | μΑ   |

| ILO        | Output Leakage Current <sup>(1)</sup> | $\overline{CE}_0 = V_{IH} \text{ or CE}_1 = V_{IL}, V_{OUT} = 0V \text{ to } V_{DDQ}$ |      | 10    | μΑ   |

| Vol (3.3V) | Output Low Voltage <sup>(2)</sup>     | IOL = +4mA, $VDDQ = Min$ .                                                            |      | 0.4   | V    |

| Vон (3.3V) | Output High Voltage <sup>(2)</sup>    | IOH = -4mA, VDDQ = Min.                                                               | 2.4  |       | V    |

| Vol (2.5V) | Output Low Voltage <sup>(2)</sup>     | IOL = +2mA, $VDDQ = Min$ .                                                            |      | 0.4   | V    |

| Vон (2.5V) | Output High Voltage <sup>(2)</sup>    | IOH = -2mA, VDDQ = Min.                                                               | 2.0  | _     | V    |

#### NOTES:

5626 tbl 08

- 1. At  $VDD \le 2.0V$  leakages are undefined.

- 2. VDDQ is selectable (3.3V/2.5V) via OPT pins. Refer to p.5 for details.

DC Electrical Characteristics Over the Operating

Temperature and Supply Voltage Range<sup>(5)</sup> (VDD = 3.3V ± 150mV)

|        |                                     | d supply tollage italig                                                                                     |        |    | 70V7599S200 <sup>(7)</sup><br>Com'l Only |      | 70V7599S166 <sup>(6)</sup><br>Com'l<br>& Ind |      | 70V7599S133<br>Com'l<br>& Ind |      |      |

|--------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|----|------------------------------------------|------|----------------------------------------------|------|-------------------------------|------|------|

| Symbol | Parameter                           | Test Condition                                                                                              | Versio | on | Typ. <sup>(4)</sup>                      | Max. | Typ. <sup>(4)</sup>                          | Max. | Typ. <sup>(4)</sup>           | Max. | Unit |

| IDD    | Dynamic Operating                   | CEL and CER= VIL,                                                                                           | COM'L  | S  | 815                                      | 950  | 675                                          | 790  | 550                           | 645  | m A  |

|        | Current (Both<br>Ports Active)      | Outputs Disabled,<br>f = fmax <sup>(1)</sup>                                                                | IND    | S  | _                                        | _    | 675                                          | 830  | 550                           | 675  |      |

| IS B1  | Standby Current                     | CEL = CER = VIH                                                                                             | COM'L  | S  | 340                                      | 410  | 275                                          | 340  | 250                           | 295  | m A  |

|        | (Both Ports - TTL<br>Level Inputs)  | f = fMAX <sup>(1)</sup>                                                                                     | IND    | S  | _                                        |      | 275                                          | 355  | 250                           | 310  |      |

| IS B2  | Standby Current<br>(One Port - TTL  | CE'A" = VIL and CE'B" = VIH(3)                                                                              | COM'L  | S  | 690                                      | 770  | 515                                          | 640  | 460                           | 520  | m A  |

|        | Level Inputs)                       | Active Port Outputs Disabled,<br>f=fMAX <sup>(1)</sup>                                                      | IND    | S  | _                                        | _    | 515                                          | 660  | 460                           | 545  |      |

| IS B3  | Full Standby Current                | Both Ports CEL and                                                                                          | COM'L  | S  | 10                                       | 30   | 10                                           | 30   | 10                            | 30   | m A  |

|        | (Both Ports - CMOS<br>Level Inputs) | $\overline{\text{CE}}$ R $\geq$ VDD - 0.2V, VN $\geq$ VDD - 0.2V<br>or VN $\leq$ 0.2V, f = 0 <sup>(2)</sup> | IND    | S  | _                                        | _    | 10                                           | 40   | 10                            | 40   |      |

| IS B4  | Full Standby Current                | $\overline{CE}$ 'A" $\leq 0.2V$ and $\overline{CE}$ 'B" $\geq VDD - 0.2V^{(3)}$                             | COM'L  | S  | 690                                      | 770  | 515                                          | 640  | 460                           | 520  | m A  |

|        | (One Port - CMOS<br>Level Inputs)   | VIN $\geq$ VDD - 0.2V or VIN $\leq$ 0.2V<br>Active Port, Outputs Disabled, f = fMax <sup>(1)</sup>          | IND    | S  | _                                        | _    | 515                                          | 660  | 460                           | 545  |      |

- 1. At f = fmax, address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of 1/tcyc, using "AC TEST CONDITIONS" at input levels of GND to 3V.

- 2. f = 0 means no address, clock, or control lines change. Applies only to input at CMOS level standby.

- 3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- 4. VDD = 3.3V,  $TA = 25^{\circ}C$  for Typ, and are not production tested. IDD DC(f=0) = 120mA (Typ).

- 5.  $\overline{CE}x = V_{IL} \text{ means } \overline{CE}ox = V_{IL} \text{ and } CE_{1X} = V_{IH}$  $\overline{CE}x = V_{IH} \text{ means } \overline{CE}ox = V_{IH} \text{ or } CE_{1X} = V_{IL}$

- "X" represents "L" for left port or "R" for right port.

- 6. 166MHz Industrial Temperature not available in BF-208 package.

- 7. This speed grade available when VDDQ = 3.3.V for a specific port (i.e., OPTx = VIH). This speed grade available in BC-256 package only.

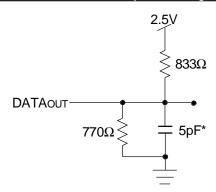

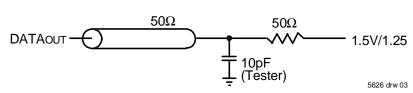

### AC Test Conditions (Vppg - 3.3V/2.5V)

| Ad 1031 dollaritions                    | 4DDQ - 3134/2134)       |

|-----------------------------------------|-------------------------|

| Input Pulse Levels (Address & Controls) | GND to 3.0V/GND to 2.4V |

| Input Pulse Levels (I/Os)               | GND to 3.0V/GND to 2.4V |

| Input Rise/Fall Times                   | 2ns                     |

| Input Timing Reference Levels           | 1.5V/1.25V              |

| Output Reference Levels                 | 1.5V/1.25V              |

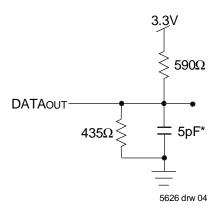

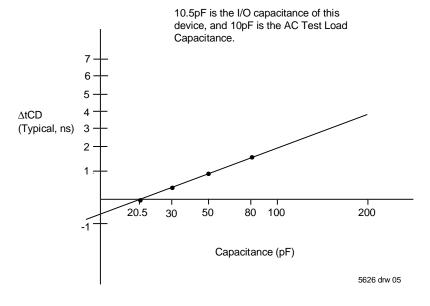

| Output Load                             | Figures 1 and 2         |

5626 tbl 10

Figure 1. AC Output Test load.

Figure 2. Output Test Load (For tcklz, tckhz, tolz, and tohz). \*Including scope and jig.

Figure 3. Typical Output Derating (Lumped Capacitive Load).

### **AC Electrical Characteristics Over the Operating Temperature Range** (Read and Write Cycle Timing)<sup>(2)</sup> (VDD = 3.3V ± 150mV, TA = 0°C to +70°C)

|                | and write cycle i ining) (VDD = 3                 | 70V75' Com | 99\$200 <sup>(5)</sup><br>'I Only | 70V7599 | 9S166 <sup>(3,4)</sup><br>om'l<br>Ind | 70V759<br>Co | 9\$133 <sup>(3)</sup><br>om'l<br>Ind |      |

|----------------|---------------------------------------------------|------------|-----------------------------------|---------|---------------------------------------|--------------|--------------------------------------|------|

| Symbol         | Parameter                                         | Min.       | Max.                              | Min.    | Max.                                  | Min.         | Max.                                 | Unit |

| tcYC1          | Clock Cycle Time (Flow-Through) <sup>(1)</sup>    | 15         |                                   | 20      |                                       | 25           |                                      | ns   |

| tcyc2          | Clock Cycle Time (Pipelined) <sup>(1)</sup>       | 5          |                                   | 6       |                                       | 7.5          |                                      | ns   |

| tcн1           | Clock High Time (Flow-Through) <sup>(1)</sup>     | 5          |                                   | 6       |                                       | 7            |                                      | ns   |

| tcl1           | Clock Low Time (Flow-Through) <sup>(1)</sup>      | 5          |                                   | 6       |                                       | 7            |                                      | ns   |

| tcH2           | Clock High Time (Pipelined) $^{(2)}$              | 2.0        |                                   | 2.1     |                                       | 2.6          |                                      | ns   |

| tCL2           | Clock Low Time (Pipelined) <sup>(1)</sup>         | 2.0        |                                   | 2.1     |                                       | 2.6          |                                      | ns   |

| t <sub>R</sub> | Clock Rise Time                                   | ***        | 1.5                               |         | 1.5                                   |              | 1.5                                  | ns   |

| tF             | Clock Fall Time                                   | ***        | 1.5                               |         | 1.5                                   |              | 1.5                                  | ns   |

| ts a           | Address Setup Time                                | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| tha            | Address Hold Time                                 | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| tsc            | Chip Enable Setup Time                            | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| thc            | Chip Enable Hold Time                             | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| tsw            | R/W Setup Time                                    | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| thw            | R/W Hold Time                                     | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| tsp            | Input Data Setup Time                             | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| thd            | Input Data Hold Time                              | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| tsad           | ADS Setup Time                                    | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| thad           | ADS Hold Time                                     | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| tscn           | CNTEN Setup Time                                  | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| then           | CNTEN Hold Time                                   | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| tsrpt          | REPEAT Setup Time                                 | 1.5        |                                   | 1.7     |                                       | 1.8          |                                      | ns   |

| thrpt          | REPEAT Hold Time                                  | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| toe            | Output Enable to Data Valid                       |            | 4.0                               |         | 4.0                                   |              | 4.2                                  | ns   |

| tolz           | Output Enable to Output Low-Z                     | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| to HZ          | Output Enable to Output High-Z                    | 1          | 3.4                               | 1       | 3.6                                   | 1            | 4.2                                  | ns   |

| tcD1           | Clock to Data Valid (Flow-Through) <sup>(1)</sup> |            | 10                                |         | 12                                    |              | 15                                   | ns   |

| tcD2           | Clock to Data Valid (Pipelined) <sup>(1)</sup>    | ***        | 3.4                               |         | 3.6                                   |              | 4.2                                  | ns   |

| toc            | Data Output Hold After Clock High                 | 1          |                                   | 1       |                                       | 1            |                                      | ns   |

| tckHZ          | Clock High to Output High-Z                       | 1          | 3.4                               | 1       | 3.6                                   | 1            | 4.2                                  | ns   |

| tcklz          | Clock High to Output Low-Z                        | 0.5        |                                   | 0.5     |                                       | 0.5          |                                      | ns   |

| Port-to-Port I | Port-to-Port Delay                                |            |                                   |         |                                       |              |                                      |      |

| tco            | Clock-to-Clock Offset                             | 5.0        |                                   | 6.0     |                                       | 7.5          |                                      | ns   |

|                |                                                   |            |                                   |         |                                       |              |                                      |      |

<sup>1.</sup> The Pipelined output parameters (tcyc2, tcp2) apply to either or both left and right ports when  $\overline{FT}/PIPEx = VIH$ . Flow-through parameters (tcyc1, tcp1) apply when  $\overline{FT}/PIPEx = VIL for that port.$

<sup>2.</sup> All input signals are synchronous with respect to the clock except for the asynchronous Output Enable  $(\overline{OE})$  and  $\overline{FT}/PIPE$ .  $\overline{FT}/PIPE$  should be treated as a DC signal, i.e. steady state during operation.

<sup>3.</sup> These values are valid for either level of VDDQ (3.3V/2.5V). See page 5 for details on selecting the desired operating voltage levels for each port.

<sup>4. 166</sup>MHz Industrial Temperature not available in BF-208 package.

<sup>5.</sup> This speed grade available when VDDQ = 3.3.V for a specific port (i.e., OPTx = VIH). This speed grade available in BC-256 package only.

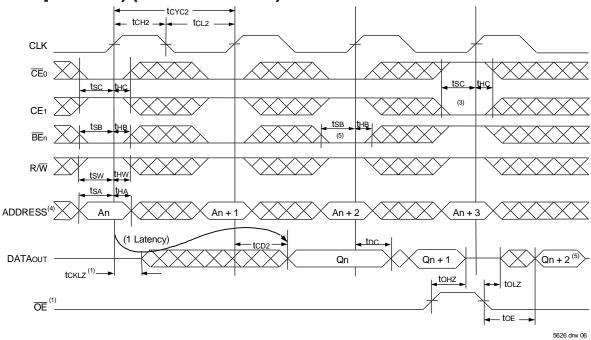

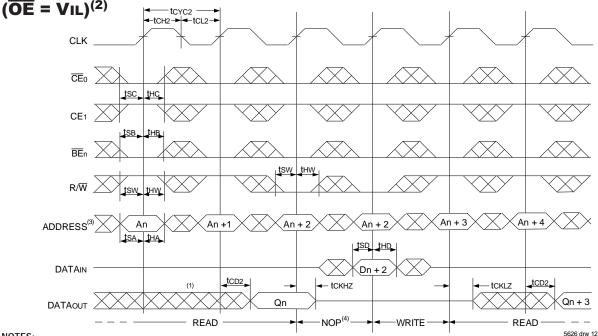

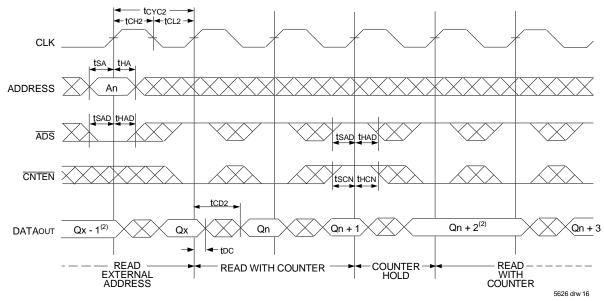

# Timing Waveform of Read Cycle for Pipelined Operation (ADS Operation) (FT/PIPE'x' = VIH)(2)

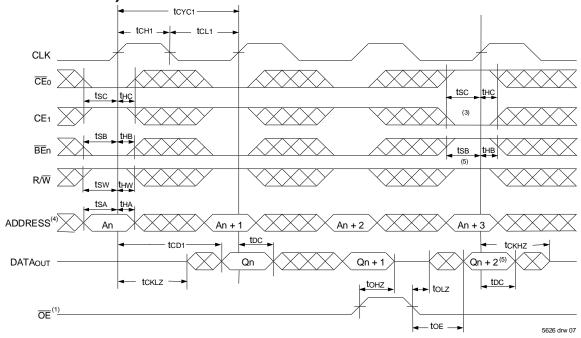

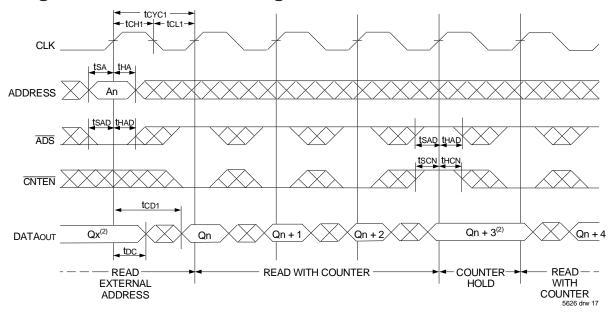

# Timing Waveform of Read Cycle for Flow-through Output $(\overline{FT}/PIPE"x" = VIL)^{(2,6)}$

- 1.  $\overline{\text{OE}}$  is asynchronously controlled; all other inputs are synchronous to the rising clock edge.

- 2. ADS = VIL, CNTEN and REPEAT = VIH.

- 3. The output is disabled (High-Impedance state) by  $\overline{\text{CE}}_0 = \text{V}_{\text{IH}}$ ,  $\text{CE}_1 = \text{V}_{\text{IL}}$ ,  $\overline{\text{BE}}_{\text{n}} = \text{V}_{\text{IH}}$  following the next rising edge of the clock. Refer to Truth Table 1.

- Addresses do not have to be accessed sequentially since ADS = VIL constantly loads the address on the rising edge of the CLK; numbers

are for reference use only.

- 5. If  $\overline{BE}_n$  was HIGH, then the appropriate Byte of DATAout for Qn + 2 would be disabled (High-Impedance state).

- 6. "x" denotes Left or Right port. The diagram is with respect to that port.

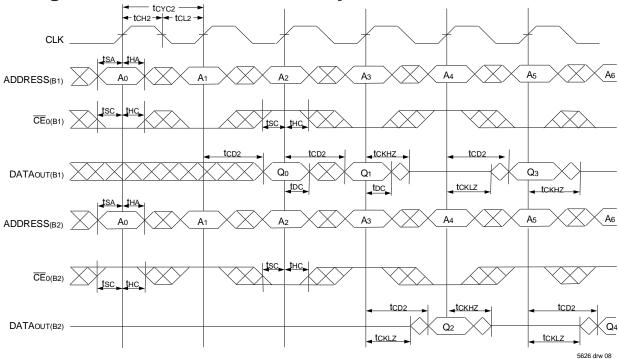

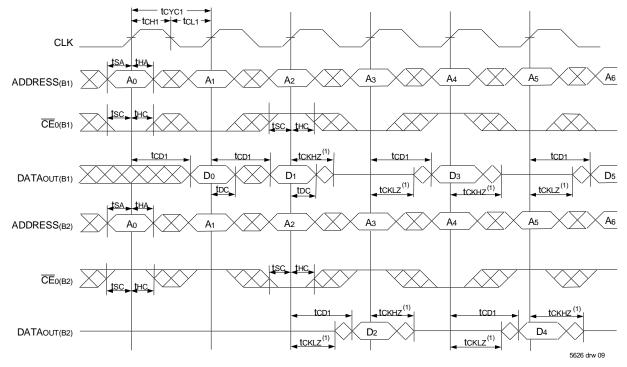

# Timing Waveform of a Multi-Device Pipelined Read<sup>(1,2)</sup>

# Timing Waveform of a Multi-Device Flow-Through Read<sup>(1,2)</sup>

- 1. B1 Represents Device #1; B2 Represents Device #2. Each Device consists of one IDT70V7599 for this waveform, and are setup for depth expansion in this example. ADDRESS(B1) = ADDRESS(B2) in this situation.

- 2.  $\overline{BEn}$ ,  $\overline{OE}$ , and  $\overline{ADS}$  = VIL;  $\overline{CE1(B1)}$ ,  $\overline{CE1(B2)}$ ,  $\overline{R/W}$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT}$  = VIH.

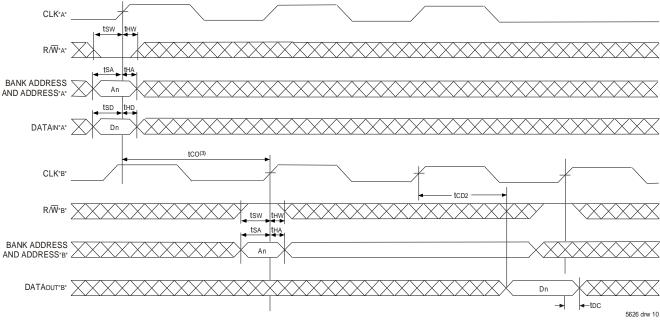

# Timing Waveform of Port A Write to Pipelined Port B Read<sup>(1,2,4)</sup>

#### NOTES:

- 1.  $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{ADS} = VIL$ ;  $CE_1$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT} = VIH$ .

- 2.  $\overline{OE} = VIL$  for Port "B", which is being read from.  $\overline{OE} = VIH$  for Port "A", which is being written to.

- 3. If tco < minimum specified, then operations from both ports are INVALID. If tco ≥ minimum, then data from Port "B" read is available on first Port "B" clock cycle (ie, time from write to valid read on opposite port will be tco + tcyc2 + tcp2).

- 4. All timing is the same for Left and Right ports. Port "A" may be either Left or Right port. Port "B" is the opposite of Port "A"

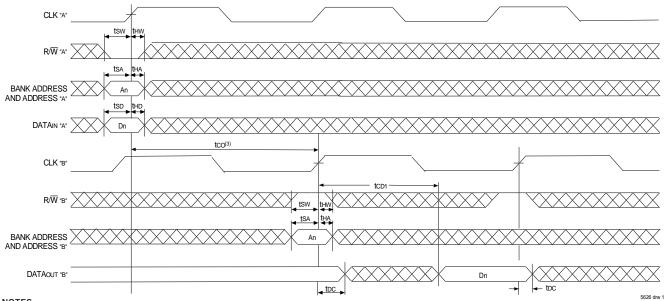

# Timing Waveform with Port-to-Port Flow-Through Read (1,2,4)

- 1.  $\overline{CE_0}$ ,  $\overline{BE}$ n, and  $\overline{ADS}$  = VIL;  $\overline{CE_1}$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT}$  = VIH.

- 2.  $\overline{OE} = V_{IL}$  for the Right Port, which is being read from.  $\overline{OE} = V_{IH}$  for the Left Port, which is being written to.

- 3. If tco < minimum specified, then operations from both ports are INVALID. If tco ≥ minimum, then data from Port "B" read is available on first Port "B" clock cycle (i.e., time from write to valid read on opposite port will be tco + tcp1).

- 4. All timing is the same for both left and right ports. Port "A" may be either left or right port. Port "B" is the opposite of Port "A".

# Timing Waveform of Pipelined Read-to-Write-to-Read

- 1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

- 2.  $\overline{CE}_0$ ,  $\overline{BE}_n$ , and  $\overline{ADS} = VIL$ ;  $\overline{CE}_1$ ,  $\overline{CNTEN}$ , and  $\overline{REPEAT} = VIH$ . "NOP" is "No Operation".

- 3. Addresses do not have to be accessed sequentially since ADS = VIL constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

- 4. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

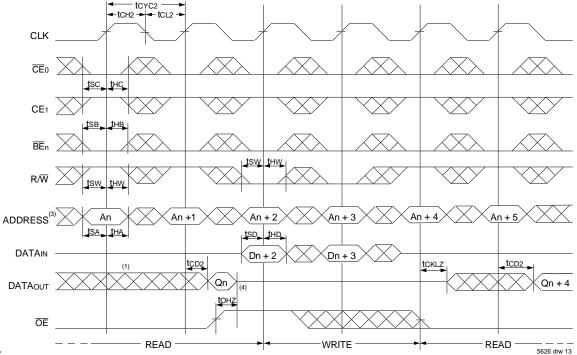

## Timing Waveform of Pipelined Read-to-Write-to-Read (OE Controlled)(2)

- Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK; numbers are for reference

- 4. This timing does not meet requirements for fastest speed grade. This waveform indicates how logically it could be done if timing so allows.

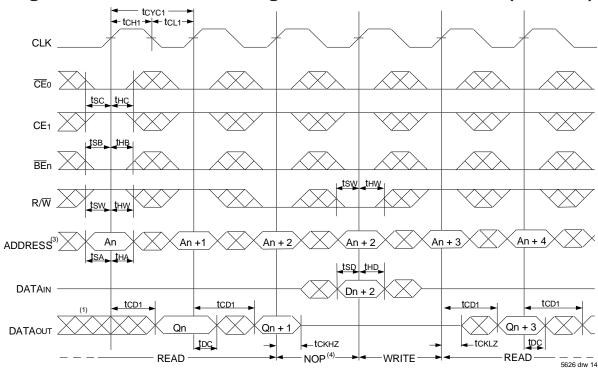

# Timing Waveform of Flow-Through Read-to-Write-to-Read ( $\overline{OE} = V_{IL}$ )<sup>(2)</sup>

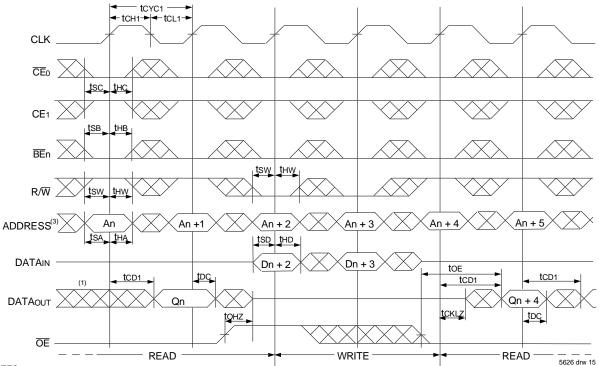

## Timing Waveform of Flow-Through Read-to-Write-to-Read (OE Controlled)(2)

- Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

- CEO, BEn, and ADS = VIL; CE1, CNTEN, and REPEAT = VIH.

- 3. Addresses do not have to be accessed sequentially since ADS = VIL constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

- 4. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

# Timing Waveform of Pipelined Read with Address Counter Advance<sup>(1)</sup>

## Timing Waveform of Flow-Through Read with Address Counter Advance<sup>(1)</sup>

- 1.  $\overline{CE}_0$ ,  $\overline{OE}$ ,  $\overline{BE}_0$  = VIL; CE1, R/ $\overline{W}$ , and  $\overline{REPEAT}$  = VIH.

- 2. If there is no address change via  $\overline{ADS} = VIL$  (loading a new address) or  $\overline{CNTEN} = VIL$  (advancing the address), i.e.  $\overline{ADS} = VIH$  and  $\overline{CNTEN} = VIH$ , then the data output remains constant for subsequent clocks.

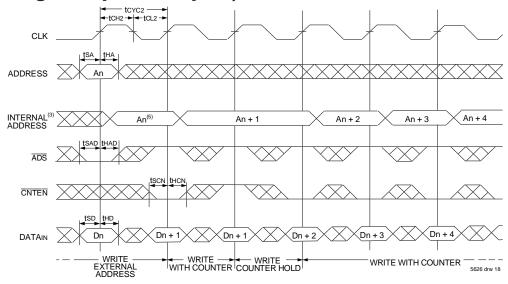

# Timing Waveform of Write with Address Counter Advance (Flow-through or Pipelined Inputs)<sup>(1,6)</sup>

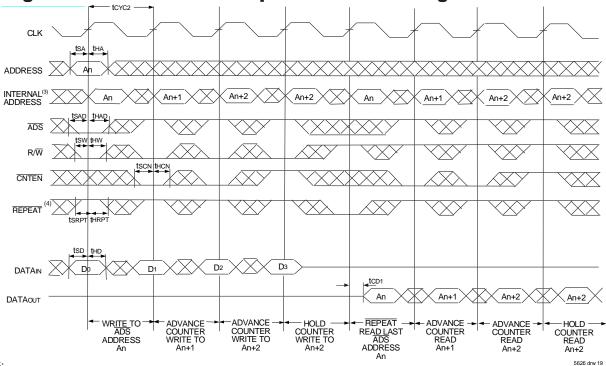

# Timing Waveform of Counter Repeat for Flow Through Mode<sup>(2,6,7)</sup>

- 1.  $\overline{CE_0}$ ,  $\overline{BE_n}$ , and  $R/\overline{W} = V_{IL}$ ;  $CE_1$  and  $\overline{REPEAT} = V_{IH}$ .

- 2.  $\overline{CE}_0$ ,  $\overline{BE}_n = VIL$ ;  $CE_1 = VIH$ .

- 3. The "Internal Address" is equal to the "External Address" when  $\overline{ADS} = VIL$  and equals the counter output when  $\overline{ADS} = VIH$ .

- 4. No dead cycle exists during REPEAT operation. A READ or WRITE cycle may be coincidental with the counter REPEAT cycle: Address loaded by last valid ADS load will be accessed. For more information on REPEAT function refer to Truth Table II.

- 5. CNTEN = VIL advances Internal Address from 'An' to 'An +1'. The transition shown indicates the time required for the counter to advance. The 'An +1'Address is written to during this cycle.

- 6. The counter includes bank address and internal address. The counter will advance across bank boundaries. For example, if the counter is in Bank 0, at address FFFh, and is advanced one location, it will move to address 0h in Bank 1. By the same token, the counter at FFFh in Bank 63 will advance to 0h in Bank 0.

- 7. For Pipelined Mode user should add 1 cycle latency for outputs as per timing waveform of read cycle for pipelined operations.

### **Functional Description**

The IDT70V7599 is a high-speed 128Kx36 (4 Mbit) synchronous Bank-Switchable Dual-Ported SRAM organized into 64 independent 2Kx36 banks. Based on a standard SRAM core instead of a traditional true dual-port memory core, this bank-switchable device offers the benefits of increased density and lower cost-per-bit while retaining many of the features of true dual-ports. These features include simultaneous, random access to the shared array, separate clocks per port, 166 MHz operating speed, full-boundary counters, and pinouts compatible with the IDT70V3599 (128Kx36) dual-port family.

The two ports are permitted independent, simultaneous access into separate banks within the shared array. Access by the ports into specific banks are controlled by the bank address pins under the user's direct control: each port can access any bank of memory with the shared array that is not currently being accessed by the opposite port (i.e., BAOL - BA5L  $\pm$  BAOR - BA5R). In the event that both ports try to access the same bank at the same time, neither access will be valid, and data at the two specific addresses targeted by the ports within that bank may be corrupted (in the case that either or both ports are writing) or may result in invalid output (in the case that both ports are trying to read).

The IDT70V7599 provides a true synchronous Dual-Port Static RAM

interface. Registered inputs provide minimal setup and hold times on address, data and all critical control inputs.

An asynchronous output enable is provided to ease asynchronous bus interfacing. Counter enable inputs are also provided to stall the operation of the address counters for fast interleaved memory applications.

A HIGH on  $\overline{\text{CE}}$ 0 or a LOW on CE1 for one clock cycle will power down the internal circuitry on each port (individually controlled) to reduce static power consumption. Dual chip enables allow easier banking of multiple IDT70V7599S for depth expansion configurations. Two cycles are required with  $\overline{\text{CE}}$ 0 LOW and CE1 HIGH to read valid data on the outputs.

### **Depth and Width Expansion**

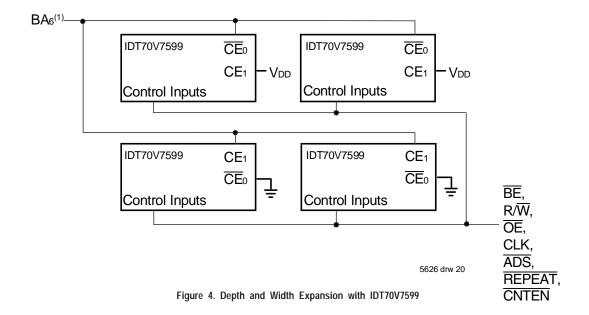

The IDT70V7599 features dual chip enables (refer to Truth Table I) in order to facilitate rapid and simple depth expansion with no requirements for external logic. Figure 4 illustrates how to control the various chip enables in order to expand two devices in depth.

The IDT70V7599 can also be used in applications requiring expanded width, as indicated in Figure 4. Through combining the control signals, the devices can be grouped as necessary to accommodate applications needing 72-bits or wider.

#### NOTE:

1. In the case of depth expansion, the additional address pin logically serves as an extension of the bank address. Accesses by the ports into specific banks are controlled by the bank address pins under the user's direct control: each port can access any bank of memory within the shared array that is not currently being accessed by the opposite port (i.e., BAOL - BAOL - BAOL). In the event that both ports try to access the same bank at the same time, neither access will be valid, and data at the two specific addresses targeted by the parts within that bank may be corrupted (in the case that either or both parts are writing) or may result in invalid output (in the case that both ports are trying to read).

### **JTAG Timing Specifications**

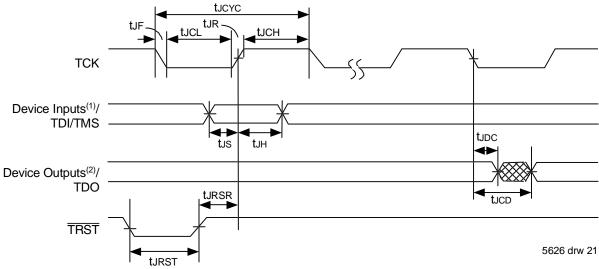

Figure 5. Standard JTAG Timing

#### NOTES:

- 1. Device inputs = All device inputs except TDI, TMS, TRST, and TCK.

- 2. Device outputs = All device outputs except TDO.

### **JTAG AC Electrical** Characteristics(1,2,3,4)

|        |                         | 70V7599 |                  |       |

|--------|-------------------------|---------|------------------|-------|

| Symbol | Parameter               | Min.    | Max.             | Units |

| tucyc  | JTAG Clock Input Period | 100     | _                | ns    |

| tлсн   | JTAG Clock HIGH         | 40      | _                | ns    |

| tucı   | JTAG Clock Low          | 40      | _                | ns    |

| tur    | JTAG Clock Rise Time    | _       | 3 <sup>(1)</sup> | ns    |

| ₩F     | JTAG Clock Fall Time    | _       | 3 <sup>(1)</sup> | ns    |

| turst  | JTAG Reset              | 50      | _                | ns    |

| tursr  | JTAG Reset Recovery     | 50      | _                | ns    |

| tico   | JTAG Data Output        | _       | 25               | ns    |

| tudo   | JTAG Data Output Hold   | 0       | _                | ns    |

| tus    | JTAG Setup              | 15      | _                | ns    |

| ţлн    | JTAG Hold               | 15      |                  | ns    |

- 1. Guaranteed by design.

- 2. 30pF loading on external output signals.

- 3. Refer to AC Electrical Test Conditions stated earlier in this document.

- 4. JTAG operations occur at one speed (10MHz). The base device may run at any speed specified in this datasheet.

5626 tbl 12

### **Identification Register Definitions**

| Instruction Field                 | Value | Description                                          |

|-----------------------------------|-------|------------------------------------------------------|

| Revision Number (31:28)           | 0x0   | Reserved for version number                          |

| IDT Device ID (27:12)             | 0x308 | Defines IDT part number                              |

| IDT JEDEC ID (11:1)               | 0x33  | Allows unique identification of device vendor as IDT |

| ID Register Indicator Bit (Bit 0) | 1     | Indicates the presence of an ID register             |

5626 tbl 13

### **Scan Register Sizes**

| Register Name        | Bit Size |  |  |  |

|----------------------|----------|--|--|--|

| Instruction (IR)     | 4        |  |  |  |

| Bypass (BYR)         | 1        |  |  |  |

| Identification (IDR) | 32       |  |  |  |

| Boundary Scan (BSR)  | Note (3) |  |  |  |

5626 tbl 14

### **System Interface Parameters**

| Instruction    | Code            | Description                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 0000            | Forces contents of the boundary scan cells onto the device outputs <sup>(1)</sup> . Places the boundary scan register (BSR) between TDI and TDO.                                                                                                                                                            |

| BYPASS         | 1111            | Places the bypass register (BYR) between TDI and TDO.                                                                                                                                                                                                                                                       |

| IDCODE         | 0010            | Loads the ID register (IDR) with the vendor ID code and places the register between TDI and TDO.                                                                                                                                                                                                            |

| HIGHZ          | 0100            | Places the bypass register (BYR) between TDI and TDO. Forces all device output drivers to a High-Z state.                                                                                                                                                                                                   |

| CLAMP          | 0011            | Uses BYR. Forces contents of the boundary scan cells onto the device outputs. Places the bypass register (BYR) between TDI and TDO.                                                                                                                                                                         |

| SAMPLE/PRELOAD | 0001            | Places the boundary scan register (BSR) between TDI and TDO. SAMPLE allows data from device inputs <sup>(2)</sup> and outputs <sup>(1)</sup> to be captured in the boundary scan cells and shifted serially through TDO. PRELOAD allows data to be input serially into the boundary scan cells via the TDI. |

| RESERVED       | All other codes | Several combinations are reserved. Do not use codes other than those identified above.                                                                                                                                                                                                                      |

NOTES: 5626 tbl 15

- 1. Device outputs = All device outputs except TDO.

- 2. Device inputs = All device inputs except TDI, TMS, TRST, and TCK.

- 3. The Boundary Scan Descriptive Language (BSDL) file for this device is available on the IDT website (www.idt.com), or by contacting your local IDT sales representative.

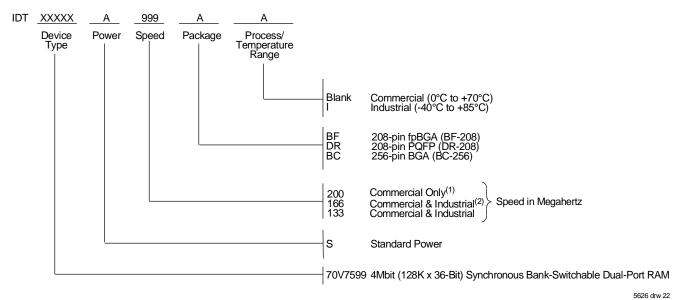

### **Ordering Information**

NOTES:

- 1. Available in BC-256 package only.

- 2. Industrial Temperature at 166Mhz not available in BF-208 package.

## **Datasheet Document History:**

1/5/00: Initial Public Offering

10/19/01: Page 2, 3 & 4 Added date revision for pin configurations

Page 9 Changed Isb3 values for commercial and industrial DC Electrical Characteristics

Page 11 Changed to Evalue in AC Electrical Characteristics, please refer to Errata #SMEN-01-05

Page 20 Increased tuco from 20ns to 25ns, please refer to Errata #SMEN-01-04

Page 1 & 22 Replaced TM logo with ® logo

03/18/02: Page 1, 9, 11 & 22 Added 200MHz specification

Page 9 Tightened power numbers in DC Electrical Characteristics

Page 14 Changed waveforms to show INVALID operation if too < minimum specified

Page 1 - 22 Removed "Preliminary" status

12/4/02: Page 9, 11 & 22 Designated 200 Mhz speed grade available in BC-256 package only.

CORPORATE HEADQUARTERS

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-5166

for Tech Support:

DualPortHelp@idt.com

831-754-4613

fax: 408-492-8674

www.idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.