# CS5376A

# Low Power Multi-Channel Decimation Filter

## Features

- 1 to 4 Channel Digital Decimation Filter

- Multiple On-Chip FIR and IIR Coefficient Sets

- Programmable Coefficients for Custom Filters

- Synchronous Operation

- Selectable Output Word Rate

- 4000, 2000, 1000, 500, 333, 250 SPS

- 200, 125, 100, 50, 40, 25, 20, 10, 5, 1 SPS

- Digital Gain and Offset Corrections

- Test DAC Bit Stream Generator

- · Sine Wave or Impulse Output Mode

- Time Break Controller, General Purpose I/O

- Secondary SPI Port, Boundary Scan JTAG

- Microcontroller or EEPROM Configuration

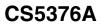

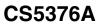

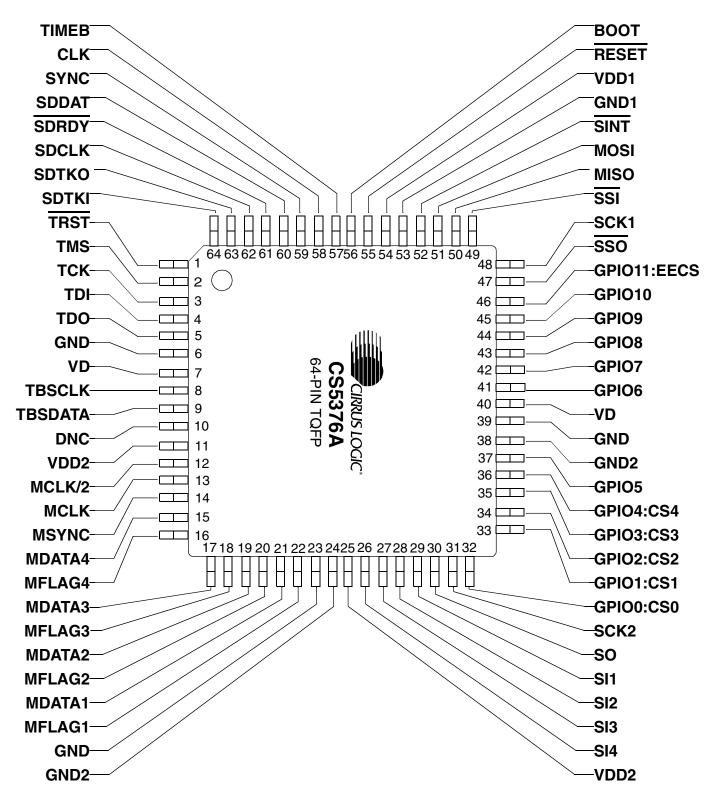

- Small Footprint 64-pin TQFP Package

- Low Power Consumption

- 9 mW per Channel at 500 SPS

- Flexible Power Supplies

- + I/O Interface: 3.3 V or 5.0 V

- Digital Logic Core: 3.0 V, 3.3 V or 5.0 V

## Description

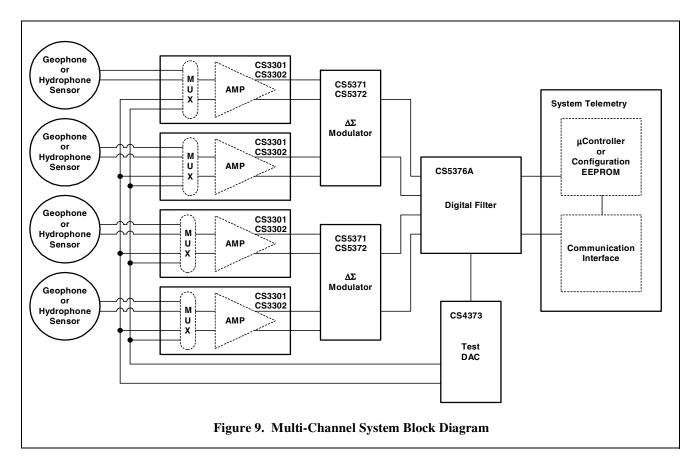

The CS5376A is a multi-function digital filter utilizing a low-power signal processing architecture to achieve efficient filtering for up to four  $\Delta\Sigma$  modulators. By combining the CS5376A with CS3301/02 differential amplifiers, CS5371/72  $\Delta\Sigma$  modulators, and the CS4373  $\Delta\Sigma$  test DAC a synchronous high resolution multi-channel measurement system can be designed quickly and easily.

Digital filter coefficients for the CS5376A FIR and IIR filters are included on-chip for a simple setup, or they can be programmed for custom applications. Selectable digital filter decimation ratios produce output word rates from 4000 SPS to 1 SPS, resulting in measurement bandwidths ranging from 1600 Hz down to 400 mHz when using the on-chip coefficient sets.

The CS5376A includes integrated peripherals to simplify system design: offset and gain corrections, a test DAC bit stream generator, a time break controller, 12 general purpose I/O pins, a secondary SPI port, and a boundary scan JTAG port.

#### ORDERING INFORMATION

CS5376A-IQ -40 to +85 °C

64-pin TQFP

CIRRUS LOGIC®

Copyright © Cirrus Logic, Inc. 2004 (All Rights Reserved)

## TABLE OF CONTENTS

| 1. | General Description                  | 7    |

|----|--------------------------------------|------|

|    | 1.1. Digital Filter Features         |      |

|    | 1.2. Integrated Peripheral Features  | 8    |

|    | 1.3. System Level Features           | 8    |

|    | 1.4. Configuration Interface         |      |

| 2. | Characteristics and Specifications.  | . 13 |

|    | Specified Operating Conditions       |      |

|    | Absolute Maximum Ratings             |      |

|    | Thermal Characteristics              | .14  |

|    | Digital Characteristics              | .14  |

|    | Power Consumption                    | .14  |

|    | Switching Characteristics            |      |

| 3. | System Design with CS5376A.          | . 19 |

|    | 3.1. Power Supplies                  | .19  |

|    | 3.2. Reset Control                   |      |

|    | 3.3. Clock Generation                | .20  |

|    | 3.4. Synchronization                 |      |

|    | 3.5. System Configuration            | .20  |

|    | 3.6. Digital Filter Operation        | .20  |

|    | 3.7. Data Collection                 | .20  |

|    | 3.8. Integrated peripherals          | .20  |

| 4. | Power Supplies                       | . 21 |

|    | 4.1. Pin Descriptions                | .21  |

|    | 4.2. Bypass Capacitors               |      |

|    | 4.3. Power Consumption               |      |

| 5. | Reset Control.                       |      |

|    | 5.1. Pin Descriptions                |      |

|    | 5.2. Reset Self-Tests                |      |

|    | 5.3. Boot Configurations             |      |

| 6. | Clock Generation.                    | . 24 |

|    | 6.1. Pin Description                 |      |

|    | 6.2. Synchronous Clocking            |      |

|    | 6.3. Master Clock Jitter and Skew    |      |

| 7. | Synchronization                      |      |

|    | 7.1. Pin Description                 |      |

|    | 7.2. MSYNC Generation                |      |

|    | 7.3. Digital Filter Synchronization  |      |

|    | 7.4. Modulator Synchronization       |      |

|    | 7.5. Test Bit Stream Synchronization |      |

| 8. | Configuration By EEPROM              |      |

|    | 8.1. Pin Descriptions                | .26  |

|    | 8.2. EEPROM Hardware Interface       |      |

|    | 8.3. EEPROM Organization             |      |

|    | 8.4. EEPROM Configuration Commands   |      |

|    | 8.5. Example EEPROM Configuration    |      |

| 9. | Configuration By Microcontroller     | . 32 |

## CS5376A

| 9.1. Pin Descriptions                       |      |

|---------------------------------------------|------|

| 9.2. Microcontroller Hardware Interface     |      |

| 9.3. Microcontroller Serial Transactions    |      |

| 9.4. Microcontroller Configuration Commands |      |

| 9.5. Example Microcontroller Configuration  | 37   |

| 10. Modulator Interface                     |      |

| 10.1. Pin Descriptions                      |      |

| 10.2. Modulator Clock Generation            |      |

| 10.2. Modulator Synchronization             |      |

| •                                           |      |

| 10.4. Modulator Data Inputs                 |      |

| 10.5. Modulator Flag Inputs                 |      |

| 11. Digital Filter Initialization           |      |

| 11.1. Filter Coefficient Selection          |      |

| 11.2. Filter Configuration Options          |      |

| 12. SINC Filter                             |      |

| 12.1. SINC1 Filter                          |      |

| 12.2. SINC2 Filter                          |      |

| 12.3. SINC3 Filter                          |      |

| 12.4. SINC Filter Synchronization           |      |

| 13. FIR Filter                              | . 47 |

| 13.1. FIR1 Filter                           | 47   |

| 13.2. FIR2 Filter                           | 47   |

| 13.3. On-Chip FIR Coefficients              | 47   |

| 13.4. Programmable FIR Coefficients         | 48   |

| 13.5. FIR Filter Synchronization            | 48   |

| 14. IIR Filter                              | . 55 |

| 14.1. IIR Architecture                      |      |

| 14.2. IIR1 Filter                           |      |

| 14.3. IIR2 Filter                           |      |

| 14.4. IIR3 Filter                           |      |

| 14.5. On-Chip IIR Coefficients              |      |

| 14.6. Programmable IIR Coefficients         |      |

| 14.7. IIR Filter Synchronization            |      |

| 15. Gain and Offset Correction              |      |

| 15.1. Gain Correction                       |      |

| 15.2. Offset Correction                     |      |

| 15.3. Offset Calibration                    |      |

| 16. Serial Data Port                        |      |

| 16.1. Pin Descriptions                      |      |

| 16.2. SD Port Data Format                   |      |

| 16.3. SD Port Transactions                  |      |

| 17. Test Bit Stream Generator.              |      |

|                                             |      |

| 17.1. Pin Descriptions                      |      |

| 17.2. TBS Architecture                      |      |

| 17.3. TBS Configuration                     |      |

| 17.4. TBS Data Source                       |      |

| 17.5. TBS Sine Wave Output                  |      |

| 17.6. TBS Impulse Output                    | 66   |

## CS5376A

| 17.7. TBS Loopback Testing                       |

|--------------------------------------------------|

| 17.8. TBS Synchronization                        |

| 18. Time Break Controller                        |

| 18.1. Pin Description                            |

| 18.2. Time Break Operation                       |

| 18.3. Time Break Delay                           |

| 19. General Purpose I/O                          |

| 19.1. Pin Descriptions                           |

| 19.2. GPIO Architecture                          |

| 19.3. GPIO Registers                             |

| 19.4. GPIO Input Mode                            |

| 19.5. GPIO Output Mode                           |

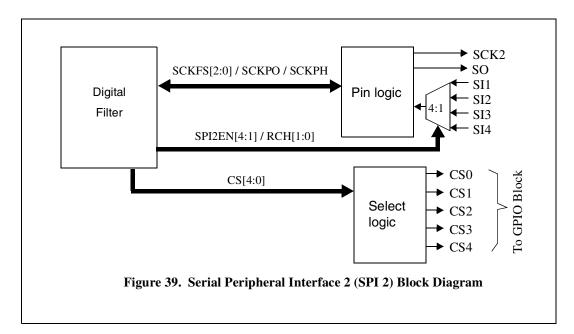

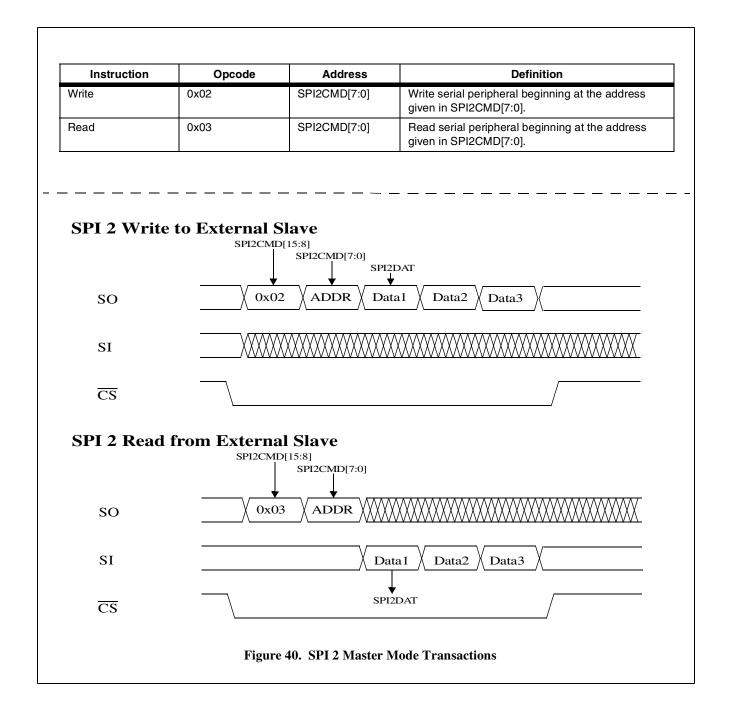

| 20. Serial Peripheral Interface 2                |

| 20.1. Pin Descriptions                           |

| 20.2. SPI 2 Architecture                         |

| 20.3. SPI 2 Registers                            |

| 20.4. SPI 2 Transactions73                       |

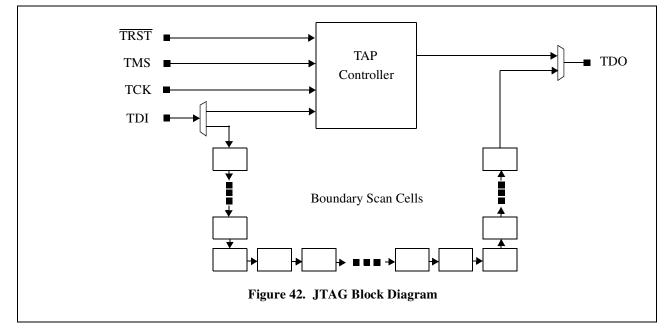

| 21. Boundary Scan JTAG                           |

| 21.1. Pin Descriptions                           |

| 21.2. JTAG Architecture                          |

| 22. Revision History                             |

| 22.1. Changes from CS5376 rev A to CS5376 rev B  |

| 22.2. Changes from CS5376 rev B to CS5376A rev A |

| 23. Register Summary                             |

| 23.1. SPI 1 Registers                            |

| 23.2. Digital Filter Registers                   |

| 24. Pin Descriptions                             |

| 25. Package Dimensions                           |

| 26. Document Revisions                           |

## **LIST OF FIGURES**

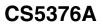

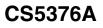

| Figure 1. CS5376A Block Diagram                        |

|--------------------------------------------------------|

| Figure 2. Digital Filtering Stages                     |

| Figure 3. FIR and IIR Coefficient Set Selection Word11 |

| Figure 4. MOSI Write Timing in SPI Slave Mode15        |

| Figure 5. MISO Read Timing in SPI Slave Mode15         |

| Figure 6. SD Port Read Timing16                        |

| Figure 7. SYNC, MCLK, MSYNC, MDATA Interface Timing17  |

| Figure 8. TBS Output Clock and Data Timing             |

| Figure 9. Multi-Channel System Block Diagram           |

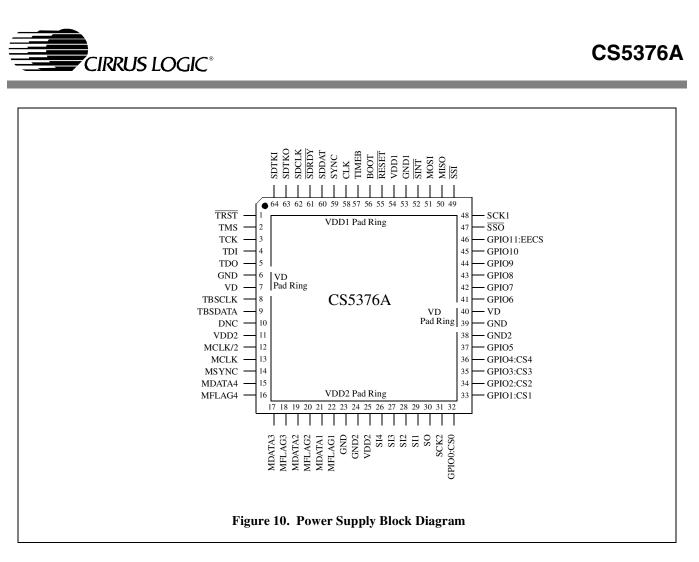

| Figure 10. Power Supply Block Diagram                  |

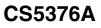

| Figure 11. Reset Control Block Diagram                 |

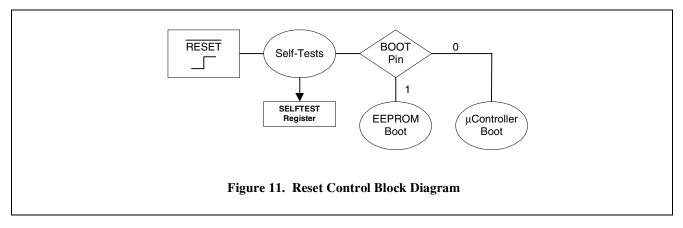

| Figure 12. Clock Generation Block Diagram              |

| Figure 13. Synchronization Block Diagram               |

| Figure 14. EEPROM Configuration Block Diagram          |

| Figure 15. | SPI 1 EEPROM Read Transactions                      | 27   |

|------------|-----------------------------------------------------|------|

| Figure 16. | 8 Kbyte EEPROM Memory Organization.                 | 28   |

| Figure 17. | Serial Peripheral Interface 1 (SPI 1) Block Diagram | 32   |

|            | Microcontroller Serial Transactions                 |      |

|            | SPI 1 Registers                                     |      |

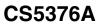

| Figure 20. | Modulator Data Interface                            | 39   |

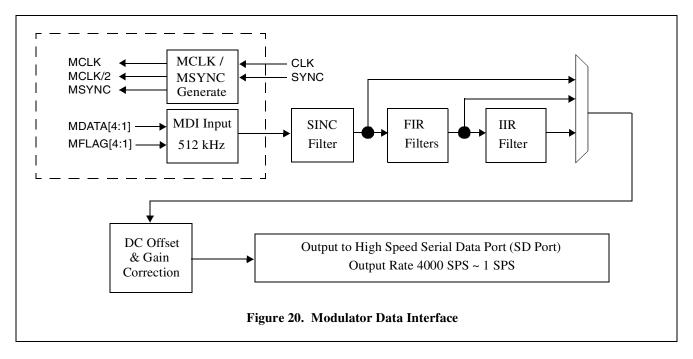

| Figure 21. | Digital Filter Stages                               | 41   |

| Figure 22. | FIR and IIR Coefficient Set Selection Word          | 42   |

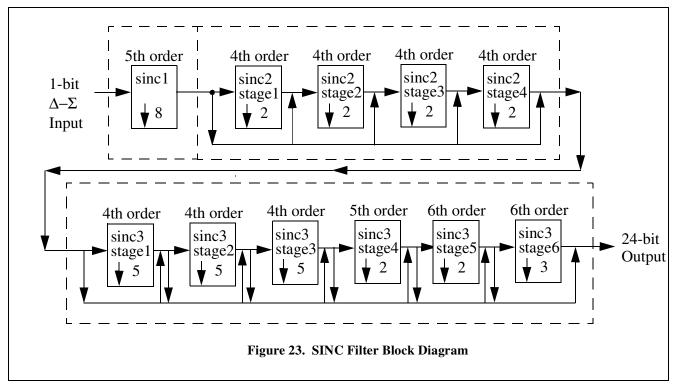

| Figure 23. | SINC Filter Block Diagram                           | 43   |

| Figure 24. | SINC Filter Stages                                  | 44   |

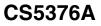

|            | FIR Filter Block Diagram                            |      |

|            | FIR Filter Stages                                   |      |

|            | FIR1 Coefficients                                   |      |

|            | FIR2 Linear Phase Coefficients                      |      |

| •          | FIR2 Minimum Phase Coefficients                     |      |

| •          | IIR Filter Block Diagram                            |      |

| •          | IIR Filter Stages                                   |      |

|            | Gain and Offset Correction                          |      |

|            | Serial Data Port Block Diagram                      |      |

| •          | SD Port Data Format                                 |      |

| •          | SD Port Transaction                                 |      |

| •          | Test Bit Stream Generator Block Diagram             |      |

|            | Time Break Block Diagram                            |      |

| -          | GPIO Bi-directional Structure                       |      |

|            | Serial Peripheral Interface 2 (SPI 2) Block Diagram |      |

|            | SPI 2 Master Mode Transactions                      |      |

| •          | JTAG Block Diagram                                  |      |

|            | SPI 1 Control Register SPI1CTRL.                    |      |

|            | SPI 1 Command Register SPI1CMD                      |      |

| Figure 45  | SPI 1 Data Register SPI1DAT1                        | 85   |

|            | SPI 1 Data Register SPI1DAT2                        |      |

|            | Hardware Configuration Register CONFIG              |      |

|            | GPIO Configuration Register GPCFG0                  |      |

| •          | GPIO Configuration Register GPCFG1                  |      |

| •          | SPI 2 Control Register SPI2CTRL.                    |      |

|            | SPI 2 Command Register SPI2CMD                      |      |

|            | SPI 2 Data Register SPI2DAT                         |      |

| Figure 53. | Filter Configuration Register FILTCFG               | 94   |

|            | Gain Correction Register GAIN1                      |      |

|            | Offset Correction Register OFFSET1                  |      |

|            | Time Break Counter Register TIMEBRK                 |      |

|            | Test Bit Stream Configuration Register TBSCFG       |      |

|            | Test Bit Stream Gain Register TBSGAIN               |      |

| -          | User Defined System Register SYSTEM1                |      |

|            | Hardware Version ID Register VERSION                |      |

| Figure 61  | Self Test Result Register SELFTEST                  | .102 |

| riguie or. |                                                     |      |

## LIST OF TABLES

## 1. GENERAL DESCRIPTION

The CS5376A is a multi-channel digital filter with integrated system peripherals. Figure 1 illustrates a simplified block diagram of the CS5376A.

## **1.1 Digital Filter Features**

- Multi-channel decimation filter for CS5371/72  $\Delta\Sigma$  modulators.

- 1, 2, 3, or 4 channel concurrent operation.

- Synchronous operation for simultaneous sampling in multi-sensor systems.

- Internal synchronization of digital filter phase to an external SYNC signal.

- Multiple output word rates, including low bandwidth rates.

- Standard output rates: 4000, 2000, 1000, 500, 333, 250 SPS.

- Low bandwidth rates: 200, 125, 100, 50, 40, 25, 20, 10, 5, 1 SPS.

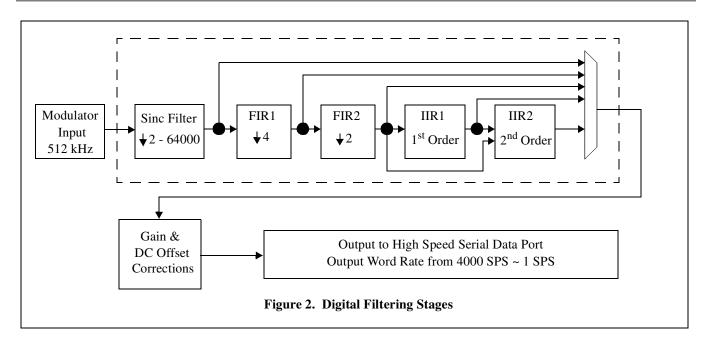

- Flexible digital filter configuration. (See Figure 2)

- Cascaded SINC, FIR, and IIR filters with selectable output stage.

- Linear and minimum phase FIR low-pass filter coefficients included.

- 3 Hz Butterworth IIR high-pass filter coefficients included.

- FIR and IIR coefficients are programmable to create a custom filter response.

- Digital gain correction.

- Individual channel gain correction to normalize signal amplitudes.

- Digital offset correction and calibration.

- Individual channel offset correction to remove measurement offsets.

- Calibration engine for automatic calculation of offset correction factors.

### **1.2 Integrated Peripheral Features**

- Synchronous operation for simultaneous sampling in multi-sensor systems.

- MCLK / MSYNC output signals to synchronize external components.

- High speed serial data output port (SD port).

- Asynchronous operation to 4 MHz for direct connection to system telemetry.

- Internal 8-deep data FIFO for flexible output timing.

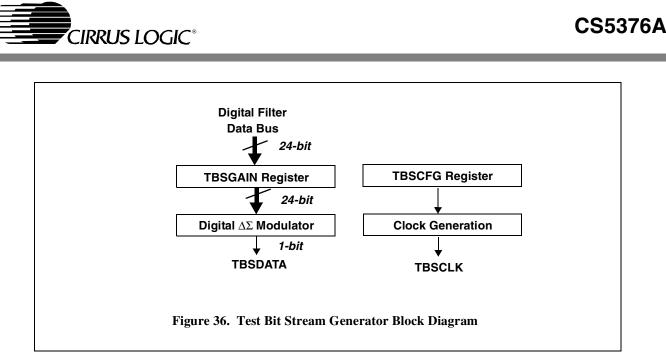

- Digital test bit stream signal generator suitable for CS4373  $\Delta\Sigma$  test DAC.

- Sine wave output mode for testing total harmonic distortion.

- Impulse output mode for transfer function characterization.

- Programmable waveform data for custom test signal generation.

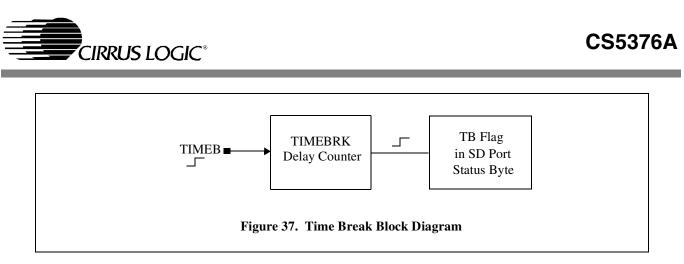

- Time break controller to record system timing information.

- Dedicated TB status bit in the output data stream.

- Programmable output delay to match system group delay.

- Additional hardware peripherals simplify system design.

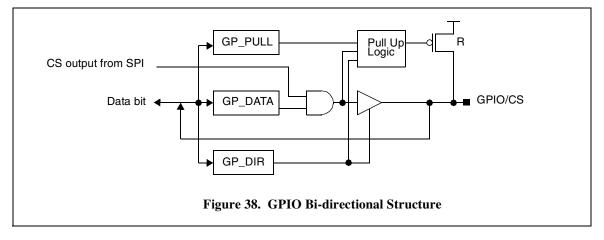

- 12 General Purpose I/O (GPIO) pins for local hardware control.

- Secondary SPI 2 serial port to control local serial peripherals.

- JTAG port for boundary scan (IEEE 1149.1 compliant).

### **1.3** System Level Features

- Flexible configuration options.

- Configuration 'on-the-fly' via microcontroller or system telemetry.

- Fixed configuration via stand-alone boot

#### EEPROM.

- Low power consumption.

- 37 mW for 4-channel operation at 500 SPS (9.25 mW/channel).

- $40 \,\mu\text{W}$  standby mode.

- Flexible power supply configurations.

- Separate digital logic core, telemetry I/O, and modulator I/O power supplies.

- Telemetry I/O and modulator I/O interfaces operate from 3.3 V or 5 V.

- Digital logic core operates from 3.0 V, 3.3 V or 5 V.

- Small 64-pin TQFP package.

- Total footprint 12 mm x 12 mm plus five bypass capacitors.

### **1.4 Configuration Interface**

- Configuration from microcontroller or standalone boot EEPROM.

- Microcontroller boot permits reconfiguration during operation.

- EEPROM boot sets a fixed operational configuration.

- Configuration commands written through Serial Peripheral Interface 1. (See Table 1)

- Standardized microcontroller interface using SPI 1 registers. (See Table 3)

- Commands write digital filter registers, filter coefficients, and test bit stream data.

- Digital filter registers set hardware configuration options.

## Microcontroller Boot Configuration Commands

| Name                   | CMD<br>24-bit | DAT1<br>24-bit           | DAT2<br>24-bit           | Description                       |

|------------------------|---------------|--------------------------|--------------------------|-----------------------------------|

| NOP                    | 000000        | -                        | -                        | No Operation                      |

| WRITE DF REGISTER      | 000001        | REG                      | DATA                     | Write Digital Filter Register     |

| READ DF REGISTER       | 000002        | REG<br>[DATA]            | -                        | Read Digital Filter Register      |

| WRITE FIR COEFFICIENTS | 000003        | NUM FIR1<br>(FIR COEF)   | NUM FIR2<br>(FIR COEF)   | Write Custom FIR Coefficients     |

| WRITE IIR COEFFICIENTS | 000004        | a11<br>b11<br>a22<br>b21 | b10<br>a21<br>b20<br>b22 | Write Custom IIR Coefficients     |

| WRITE ROM COEFFICIENTS | 000005        | COEF SEL                 | -                        | Use On-Chip Coefficients          |

| WRITE TBS DATA         | 000006        | NUM TBS<br>(TBS DATA)    | -<br>(TBS DATA)          | Write Custom Test Bit Stream Data |

| WRITE ROM TBS          | 000007        | -                        | -                        | Use On-Chip TBS Data              |

| FILTER START           | 000008        | -                        | -                        | Start Digital Filter Operation    |

| FILTER STOP            | 000009        | -                        | -                        | Stop Digital Filter Operation     |

#### **EEPROM Boot Configuration Commands**

| Name                   | CMD<br>8-bit | DATA<br>24-bit                                       | Description                       |

|------------------------|--------------|------------------------------------------------------|-----------------------------------|

| NOP                    | 00           | -                                                    | No Operation                      |

| WRITE DF REGISTER      | 01           | REG<br>DATA                                          | Write Digital Filter Register     |

| WRITE FIR COEFFICIENTS | 02           | NUM FIR1<br>NUM FIR2<br>(FIR COEF)                   | Write Custom FIR Coefficients     |

| WRITE IIR COEFFICIENTS | 03           | a11<br>b10<br>b11<br>a21<br>a22<br>b20<br>b21<br>b22 | Write Custom IIR Coefficients     |

| WRITE ROM COEFFICIENTS | 04           | COEF SEL                                             | Use On-Chip Coefficients          |

| WRITE TBS DATA         | 05           | NUM TBS<br>(TBS DATA)                                | Write Custom Test Bit Stream Data |

| WRITE ROM TBS          | 06           | -                                                    | Use On-Chip TBS Data              |

| FILTER START           | 07           | -                                                    | Start Digital Filter Operation    |

[DATA] indicates data word returned from digital filter.

(DATA) indicates multiple words of this type are to be written.

#### Table 1. Microcontroller and EEPROM Configuration Commands

| Bits      | 23:20 | 19:16 | 15:12 | 11:8 | 7:4  | 3:0  |

|-----------|-------|-------|-------|------|------|------|

| Selection | 0000  | 0000  | IIR2  | IIR1 | FIR2 | FIR1 |

| Bits 15:12 | IIR2 Coefficients |

|------------|-------------------|

| 0000       | 3 Hz @ 2000 SPS   |

| 0001       | 3 Hz @ 1000 SPS   |

| 0010       | 3 Hz @ 500 SPS    |

| 0011       | 3 Hz @ 333 SPS    |

| 0100       | 3 Hz @ 250 SPS    |

| Bits 11:8 | IIR1 Coefficients |

|-----------|-------------------|

| 0000      | 3 Hz @ 2000 SPS   |

| 0001      | 3 Hz @ 1000 SPS   |

| 0010      | 3 Hz @ 500 SPS    |

| 0011      | 3 Hz @ 333 SPS    |

| 0100      | 3 Hz @ 250 SPS    |

| Bits 3:0 | FIR1 Coefficients |

|----------|-------------------|

| 0000     | Linear Phase      |

| 0001     | Minimum Phase     |

|          |                   |

|          |                   |

| Bits 7:4 | FIR2 Coefficients |

Minimum Phase

Г

0001

Figure 3. FIR and IIR Coefficient Set Selection Word

### **Test Bit Stream Characteristic Equation:**

(Signal Freq) \* (# TBS Data) \* (Interpolation + 1) = Output Rate Example: (31.25 Hz) \* (1024) \* (0x07 + 1) = 256 kHz

| Signal<br>Frequency<br>(TBSDATA) | Output<br>Rate<br>(TBSCLK) | Output Rate<br>Selection<br>(RATE) | Interpolation<br>Selection<br>(INTP) |

|----------------------------------|----------------------------|------------------------------------|--------------------------------------|

| 10.00 Hz                         | 256 kHz                    | 0x4                                | 0x18                                 |

| 10.00 Hz                         | 512 kHz                    | 0x5                                | 0x31                                 |

| 25.00 Hz                         | 256 kHz                    | 0x4                                | 0x09                                 |

| 25.00 Hz                         | 512 kHz                    | 0x5                                | 0x13                                 |

| 31.25 Hz                         | 256 kHz                    | 0x4                                | 0x07                                 |

| 31.25 Hz                         | 512 kHz                    | 0x5                                | 0x0F                                 |

| 50.00 Hz                         | 256 kHz                    | 0x4                                | 0x04                                 |

| 50.00 Hz                         | 512 kHz                    | 0x5                                | 0x09                                 |

| 125.00 Hz                        | 256 kHz                    | 0x4                                | 0x01                                 |

| 125.00 Hz                        | 512 kHz                    | 0x5                                | 0x03                                 |

Table 2. TBS Configurations Using On-Chip Data

## SPI 1 Registers

| Name     | Addr.   | Туре | # Bits  | Description   |

|----------|---------|------|---------|---------------|

| SPI1CTRL | 00 - 02 | R/W  | 8, 8, 8 | SPI 1 Control |

| SPI1CMD  | 03 - 05 | R/W  | 8, 8, 8 | SPI 1 Command |

| SPI1DAT1 | 06 - 08 | R/W  | 8, 8, 8 | SPI 1 Data 1  |

| SPI1DAT2 | 09 - 0B | R/W  | 8, 8, 8 | SPI 1 Data 2  |

## Digital Filter Registers

| Name     | Addr. | Туре | # Bits | Description                                    |

|----------|-------|------|--------|------------------------------------------------|

| CONFIG   | 00    | R/W  | 24     | Hardware Configuration                         |

| RESERVED | 01-0D | R/W  | 24     | Reserved                                       |

| GPCFG0   | 0E    | R/W  | 24     | GPIO[7:0] Direction, Pull-up Enable, and Data  |

| GPCFG1   | 0F    | R/W  | 24     | GPIO[11:8] Direction, Pull-up Enable, and Data |

| SPI2CTRL | 10    | R/W  | 24     | SPI 2 Control                                  |

| SPI2CMD  | 11    | R/W  | 16     | SPI 2 Command                                  |

| SPI2DAT  | 12    | R/W  | 24     | SPI 2 Data                                     |

| RESERVED | 13-1F | R/W  | 24     | Reserved                                       |

| FILTCFG  | 20    | R/W  | 24     | Digital Filter Configuration                   |

| GAIN1    | 21    | R/W  | 24     | Gain Correction Channel 1                      |

| GAIN2    | 22    | R/W  | 24     | Gain Correction Channel 2                      |

| GAIN3    | 23    | R/W  | 24     | Gain Correction Channel 3                      |

| GAIN4    | 24    | R/W  | 24     | Gain Correction Channel 4                      |

| OFFSET1  | 25    | R/W  | 24     | Offset Correction Channel 1                    |

| OFFSET2  | 26    | R/W  | 24     | Offset Correction Channel 2                    |

| OFFSET3  | 27    | R/W  | 24     | Offset Correction Channel 3                    |

| OFFSET4  | 28    | R/W  | 24     | Offset Correction Channel 4                    |

| TIMEBRK  | 29    | R/W  | 24     | Time Break Delay                               |

| TBSCFG   | 2A    | R/W  | 24     | Test Bit Stream Configuration                  |

| TBSGAIN  | 2B    | R/W  | 24     | Test Bit Stream Gain                           |

| SYSTEM1  | 2C    | R/W  | 24     | User Defined System Register 1                 |

| SYSTEM2  | 2D    | R/W  | 24     | User Defined System Register 2                 |

| VERSION  | 2E    | R/W  | 24     | Hardware Version ID                            |

| SELFTEST | 2F    | R/W  | 24     | Self-Test Result Code                          |

Table 3. SPI 1 and Digital Filter Registers

### 2. CHARACTERISTICS AND SPECIFICATIONS

- Min / Max characteristics and specifications are guaranteed over the Specified Operating Conditions.

- Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and  $T_A = 25^{\circ}C$ .

- GND, GND1, GND2 = 0 V, all voltages with respect to 0 V.

## SPECIFIED OPERATING CONDITIONS

| Parameter                              |                  | Symbol         | Min   | Nom | Max  | Unit |

|----------------------------------------|------------------|----------------|-------|-----|------|------|

| Logic Core Power Supply                |                  | VD             | 2.85  | 3.0 | 5.25 | V    |

| Microcontroller Interface Power Supply |                  | VDD1           | 3.135 | 3.3 | 5.25 | V    |

| Modulator Interface Power Supply       |                  | VDD2           | 3.135 | 3.3 | 5.25 | V    |

| Ambient Operating Temperature          | Industrial (-IQ) | Τ <sub>Α</sub> | -40   | -   | 85   | °C   |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                              | Symbol                       | Min              | Max  | Units   |    |

|----------------------------------------|------------------------------|------------------|------|---------|----|

| DC Power Supplies                      | DC Power Supplies Logic Core |                  | -0.3 | 6.0     | V  |

|                                        | Microcontroller Interface    | VDD1             | -0.3 | 6.0     | V  |

|                                        | Modulator Interface          | VDD2             | -0.3 | 6.0     | V  |

| Input Current, Any Pin Except Supplies | (Note 1)                     | I <sub>IN</sub>  | -    | ±10     | mA |

| Input Current, Power Supplies          | (Note 1)                     | I <sub>IN</sub>  | -    | ±50     | mA |

| Output Current                         | (Note 1)                     | I <sub>OUT</sub> | -    | ±25     | mA |

| Power Dissipation                      |                              | P <sub>DN</sub>  | -    | 500     | mW |

| Digital Input Voltages                 |                              | V <sub>IND</sub> | -0.3 | VDD+0.3 | V  |

| Ambient Operating Temperature (Powe    | er Applied)                  | T <sub>A</sub>   | -40  | 85      | °C |

| Storage Temperature Range              |                              | T <sub>STG</sub> | -65  | 150     | ٥° |

1. Transient currents up to 100 mA will not cause SCR latch-up.

## **THERMAL CHARACTERISTICS**

| Parameter                                     | Symbol         | Min | Тур | Max | Unit   |

|-----------------------------------------------|----------------|-----|-----|-----|--------|

| Allowable Junction Temperature                | Т <sub>Ј</sub> | -   | -   | 135 | °C     |

| Junction to Ambient Thermal Impedance         | $\Theta_{JA}$  | -   | 65  |     | °C / W |

| Ambient Operating Temperature (Power Applied) | T <sub>A</sub> | -40 | -   | +85 | °C     |

## **DIGITAL CHARACTERISTICS**

| Parameter                                           | Symbol             | Min       | Тур | Max  | Unit |

|-----------------------------------------------------|--------------------|-----------|-----|------|------|

| High-Level Input Drive Voltage                      | V <sub>IH</sub>    | 0.6 * VDD | -   | VDD  | V    |

| Low-Level Input Drive Voltage                       | V <sub>IL</sub>    | 0.0       | -   | 0.8  | V    |

| High-Level Output Drive Voltage $I_{out} = -40 \mu$ | A V <sub>OH</sub>  | VDD - 0.3 | -   | VDD  | V    |

| Low-Level Output Drive Voltage $I_{out} = +40 \mu$  | A V <sub>OL</sub>  | 0.0       | -   | 0.3  | V    |

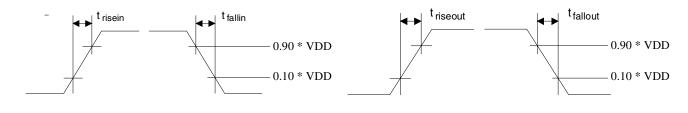

| Rise Times, Digital Inputs                          | t <sub>RISE</sub>  | -         | -   | 100  | ns   |

| Fall Times, Digital Inputs                          | t <sub>FALL</sub>  | -         | -   | 100  | ns   |

| Rise Times, Digital Outputs                         | t <sub>RISE</sub>  | -         | -   | 100  | ns   |

| Fall Times, Digital Outputs                         | t <sub>FALL</sub>  | -         | -   | 100  | ns   |

| Input Leakage Current (Note 2                       | l) I <sub>IN</sub> | -         | ± 1 | ± 10 | μA   |

| 3-State Leakage Current                             | I <sub>OZ</sub>    | -         | -   | ± 10 | μA   |

| Digital Input Capacitance                           | C <sub>IN</sub>    | -         | 9   | -    | pF   |

| Digital Output Pin Capacitance                      | C <sub>OUT</sub>   | -         | 9   | -    | pF   |

Notes: 2. Max leakage for pins with pull-up resistors (TRST, TMS, TDI,  $\overline{SSI}$ , GPIO, MOSI, SCK1) is ±250  $\mu$ A.

## **POWER CONSUMPTION**

| Parameter                                   | Symbol            | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------|-----|-----|-----|------|

| Operational Power Consumption               |                   |     |     |     | •    |

| 1.024 MHz Digital Filter Clock              | PWR <sub>1</sub>  | -   | 21  | -   | mW   |

| 2.048 MHz Digital Filter Clock              | PWR <sub>2</sub>  | -   | 26  | -   | mW   |

| 4.096 MHz Digital Filter Clock              | PWR <sub>4</sub>  | -   | 37  | -   | mW   |

| 8.192 MHz Digital Filter Clock              | PWR <sub>8</sub>  | -   | 57  | -   | mW   |

| 16.384 MHz Digital Filter Clock             | PWR <sub>16</sub> | -   | 85  | -   | mW   |

| Standby Power Consumption                   |                   | -   | •   | •   | •    |

| 32 kHz Digital Filter Clock, Filter Stopped | PWR <sub>S</sub>  | -   | 40  | -   | μW   |

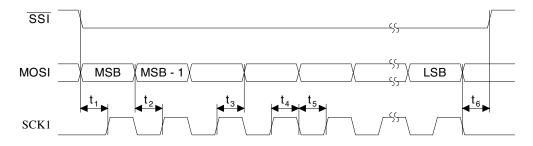

#### SPI 1 Interface Timing (External Master)

Figure 4. MOSI Write Timing in SPI Slave Mode

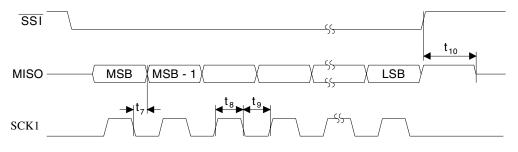

Figure 5. MISO Read Timing in SPI Slave Mode

| Parameter                             | Symbol          | Min | Тур | Мах | Unit |

|---------------------------------------|-----------------|-----|-----|-----|------|

| MOSI Write Timing                     |                 |     |     |     |      |

| SSI Enable to Valid Latch Clock       | t <sub>1</sub>  | 60  | -   | -   | ns   |

| Data Set-up Time Prior to SCK1 Rising | t <sub>2</sub>  | 60  | -   | -   | ns   |

| Data Hold Time After SCK1 Rising      | t <sub>3</sub>  | 120 | -   | -   | ns   |

| SCK1 High Time                        | t <sub>4</sub>  | 120 | -   | -   | ns   |

| SCK1 Low Time                         | t <sub>5</sub>  | 120 | -   | -   | ns   |

| SCK1 Falling Prior to SSI Disable     | t <sub>6</sub>  | 60  | -   | -   | ns   |

| MISO Read Timing                      |                 |     |     |     |      |

| SCK1 Falling to New Data Bit          | t <sub>7</sub>  | -   | -   | 200 | ns   |

| SCK1 High Time                        | t <sub>8</sub>  | 120 | -   | -   | ns   |

| SCK1 Low Time                         | t <sub>9</sub>  | 120 | -   | -   | ns   |

| SSI Rising to MISO Hi-Z               | t <sub>10</sub> | -   | -   | 150 | ns   |

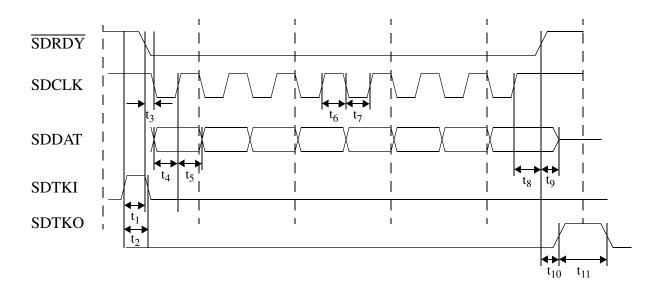

#### Serial Data Port (SD Port)

| Parameter                                | Symbol          | Min | Тур | Max  | Unit |

|------------------------------------------|-----------------|-----|-----|------|------|

| SDTKI to SDRDY Falling Edge              | t <sub>1</sub>  | 60  | -   | -    | ns   |

| SDTKI High Time Width                    | t <sub>2</sub>  | 60  | -   | 1000 | ns   |

| SDRDY Falling Edge to SDCLK Falling Edge | t <sub>3</sub>  | 50  | -   | -    | ns   |

| Data Setup Time Prior to SDCLK Rising    | t <sub>4</sub>  | 60  | -   | -    | ns   |

| Data Hold Time After SDCLK Rising        | t <sub>5</sub>  | 60  | -   | -    | ns   |

| SDCLK High Time                          | t <sub>6</sub>  | 120 | -   | -    | ns   |

| SDCLK Low Time                           | t <sub>7</sub>  | 120 | -   | -    | ns   |

| SDCLK Rising to SDRDY Rising             | t <sub>8</sub>  | 60  | -   | -    | ns   |

| Data Hold Time After SDRDY Rising        | t <sub>9</sub>  | -   | -   | 150  | ns   |

| SDRDY High to SDTKO Rising Edge          | t <sub>10</sub> | -   | -   | 60   | ns   |

| SDTKO High Time                          | t <sub>11</sub> | 90  | -   | -    | ns   |

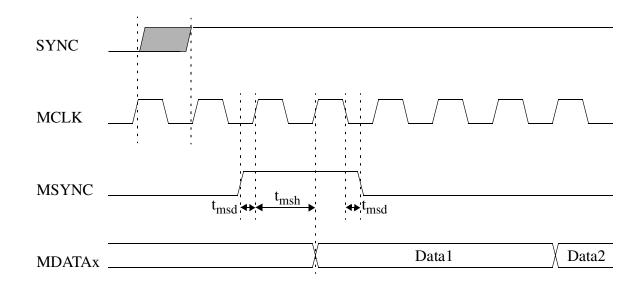

#### CLK, SYNC, MCLK, MSYNC, and MDATAx

Note: SYNC input latched on MCLK rising edge. MSYNC output triggered by MCLK falling edge.

| f <sub>MCLK</sub>        | 2.048 MHz                  | 1.024 MHz                  |

|--------------------------|----------------------------|----------------------------|

| $t_{msd} = T_{MCLK} / 4$ | $t_{msd} = 122 \text{ ns}$ | $t_{msd} = 244 \text{ ns}$ |

| $t_{msh} = T_{MCLK}$     | $t_{msh} = 488 \text{ ns}$ | t <sub>msh</sub> = 976 ns  |

| Figure 7. | SYNC. MCLK | , MSYNC, MDATA | Interface Timing |

|-----------|------------|----------------|------------------|

|           |            | ,              |                  |

| Parameter                                  | Symbol            | Min | Тур    | Max | Unit |

|--------------------------------------------|-------------------|-----|--------|-----|------|

| Master Clock Frequency (Note 3)            | CLK               | 32  | 32.768 | 33  | MHz  |

| Master Clock Duty Cycle                    | DTY               | 40  | -      | 60  | %    |

| Master Clock Rise Time                     | t <sub>RISE</sub> | -   | -      | 20  | ns   |

| Master Clock Fall Time                     | t <sub>FALL</sub> | -   | -      | 20  | ns   |

| Master Clock Jitter                        | JTR               | -   | -      | 300 | ps   |

| Synchronization after SYNC rising (Note 4) | SYNC              | -2  | -      | 2   | μs   |

| MSYNC Setup Time to MCLK rising            | t <sub>msr</sub>  | 20  | -      | -   | ns   |

| MCLK rising to Valid MDATA                 | t <sub>mdv</sub>  | -   | -      | 75  | ns   |

| MSYNC falling to MCLK rising               | t <sub>msf</sub>  | 20  | -      | -   | ns   |

Notes: 3. Master clock frequencies above or below 32.768 MHz will affect generated clock frequencies.

4. Sampling synchronization between multiple CS5376A devices receiving identical SYNC signals.

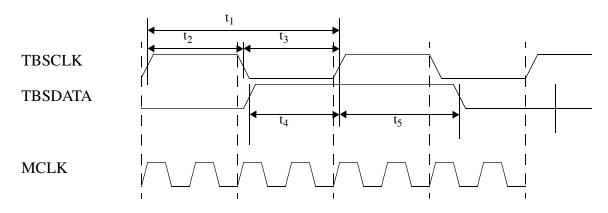

#### Test Bit Stream (TBS)

Note: Example timing shown for a 256 kHz output rate and no programmable delays.

#### Figure 8. TBS Output Clock and Data Timing

| Parameter                                               | Symbol         | Min | Тур   | Мах | Unit |

|---------------------------------------------------------|----------------|-----|-------|-----|------|

| TBS Clock Timing                                        |                |     |       |     |      |

| TBS Clock Period                                        | t <sub>1</sub> | -   | 3.906 | -   | μs   |

| TBS Clock High Time (Note 5)                            | t <sub>2</sub> | 40  | -     | 60  | %    |

| TBS Clock Low Time                                      | t <sub>3</sub> | 40  | -     | 60  | %    |

| TBS Data Output Timing                                  |                |     |       |     |      |

| TBS Data Bit Rate                                       |                | -   | 256   | -   | kbps |

| TBS Data Rising to TBS Clock Rising Setup Time          | t <sub>4</sub> | 60  | -     | -   | ns   |

| TBS Clock Rising to TBS Data Falling Hold Time (Note 6) | t <sub>5</sub> | 60  | -     | -   | ns   |

5. TBSCLK phase can be delayed in 1/8 increments. The timing diagram shows no TBSCLK delay.

6. TBSDATA can be delayed from 0 to 63 full bit periods. The timing diagram shows no TBSDATA delay.

### 3. SYSTEM DESIGN WITH CS5376A

Figure 9 illustrates a simplified block diagram of the CS5376A in a multi-channel measurement system.

Up to four differential sensors are connected through CS3301/02 differential amplifiers to the CS5371/72  $\Delta\Sigma$  modulators, where analog to digital conversion occurs. Each modulators 1-bit output connects to a CS5376A MDATA input, where the oversampled  $\Delta\Sigma$  data is decimated and filtered to 24-bit output samples at a programmed output rate. These output samples are buffered in an 8-deep data FIFO and passed to the system telemetry on command.

System self tests are performed by connecting the CS5376A test bit stream (TBS) generator to the CS4373 test DAC. Analog tests drive differential signals from the CS4373 test DAC into the multiplexed inputs of the CS3301/02 amplifiers or di-

rectly to the sensors through external analog switches. Digital loopback tests internally connect the TBS digital output directly to the CS5376A modulator inputs.

### 3.1 Power Supplies

The multi-channel system shown in Figure 9 typically operates from a  $\pm 2.5$  V or 5 V analog power supply and a 3.3 V digital power supply. The CS5376A logic core can be powered from 3 V to minimize power consumption, if required.

### 3.2 Reset Control

System reset is required only for the CS5376A device, and is a standard active low signal that can be generated by a power supply monitor or microcontroller. Other system devices default to a power-down state when the CS5376A is reset.

## 3.3 Clock Generation

A single 32.768 MHz low-jitter clock input, which can be generated from a VCXO based PLL, is required to drive the CS5376A device. Clock inputs for other system devices are driven by clock outputs from the CS5376A.

## 3.4 Synchronization

Digital filter phase and analog sample timing of the four  $\Delta\Sigma$  modulators connected to the CS5376A are synchronized by a rising edge on the SYNC pin. If a synchronization signal is received identically by all CS5376A devices in a measurement network, synchronous sampling across the network is guaranteed.

### 3.5 System Configuration

Through the SPI 1 serial port, filter coefficients and digital filter register settings can either be programmed by a microcontroller or automatically loaded from an external EEPROM after reset. System configuration is only required for the CS5376A device, as other devices are configured via the CS5376A General Purpose I/O pins.

Two registers in the digital filter, SYSTEM1 and SYSTEM2 (0x2C, 0x2D), are provided for user defined system information. These are general purpose registers that will hold any 24-bit data values written to them.

## 3.6 Digital Filter Operation

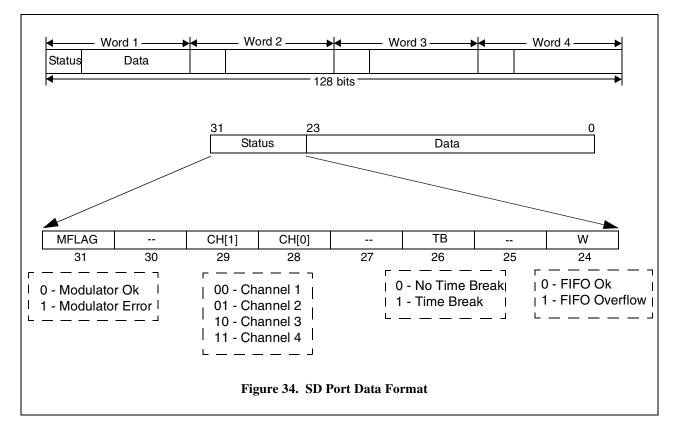

After analog to digital conversion occurs in the modulators, the oversampled 1-bit  $\Delta\Sigma$  data is read into the CS5376A through the MDATA pins. The digital filter then processes data through the enabled filter stages, decimating it to 24-bit words at a programmed output word rate. The final 24-bit samples are concatenated with 8-bit status words and placed into an output FIFO.

#### 3.7 Data Collection

Data is collected from the CS5376A through the Serial Data port (SD port). Automatically or upon request, depending how the SDTKI pin is connected, the SD port initiates serial transactions to transfer 32-bit data from the output FIFO to the system telemetry. The output FIFO has eight data locations to permit latency in data collection.

## 3.8 Integrated peripherals

## Test Bit Stream (TBS)

A digital signal generator built into the CS5376A produces a 1-bit  $\Delta\Sigma$  sine wave or impulse function. This digital test bit stream can be connected to the CS4373 test DAC to create high quality analog test signals or it can be internally looped back to the CS5376A MDATA inputs to test the digital filter and data collection circuitry.

## Time Break

Timing information is recorded during data collection by strobing the TIMEB pin. A dedicated flag in the sample status bits, TB, is set high to indicate over which measurement the timing event occurred.

## General Purpose I/O (GPIO)

Twelve general purpose pins are available on the CS5376A for system control. Each pin can be set as input or output, high or low, with an internal pullup enabled or disabled. The CS3301/02, CS5371/72 and CS4373 devices in Figure 9 are configured by simple pin settings controlled through the CS5376A GPIO pins.

## Serial Peripheral Interface 2 (SPI 2)

A secondary master mode serial port to communicate with external serial peripherals.

## JTAG Port

Boundary scan JTAG is IEEE 1149.1 compliant.

### 4. POWER SUPPLIES

The CS5376A has three sets of power supply inputs. Two sets supply power to the I/O pins of the device (VDD1, VDD2), and the third supplies power to the logic core (VD). The I/O pin power supplies determine the maximum input and output voltages when interfacing to peripherals, and the logic core power supply largely determines the power consumption of the CS5376A.

## 4.1 Pin Descriptions

### VDD1, GND1 - Pins 54,53

Sets the interface voltage to a microcontroller and system telemetry. Can be driven with voltages from 3.3 V to 5 V.

VDD1 powers pins 1-5 and 41-64:

TRST, TMS, TCK, TDI, TDO

GPIO6 - GPIO11:EECS SSO, SCK1, SSI, MISO, MOSI, SINT, RESET, BOOT, TIMEB, CLK, SYNC SDDAT, SDRDY, SDCLK, SDTKO, SDTKI

## VDD2, GND2 - Pins 11, 25, 24, 38

Sets the interface voltage to the modulators, test DAC, and serial peripherals. Can be driven with voltages from 3.3 V to 5 V.

VDD2 powers pins 8-37:

TBSCLK, TBSDATA MCLK/2, MCLK, MSYNC MDATA1 - MDATA4 MFLAG1 - MFLAG4 SI1 - SI4, SO, SCK2 GPIO0:CS0 - GPIO5

### VD, GND - Pins 7, 40, 6, 23, 39

Sets the operational voltage of the CS5376A logic core. Can be driven with voltages from 3 V to 5 V. A 3 V supply minimizes total power consumption.

### 4.2 Bypass Capacitors

Each power supply pin should be bypassed with parallel  $1 \mu F$  and  $0.01 \mu F$  caps, or by a single  $0.1 \mu F$  cap, placed as close as possible to the CS5376A. Bypass capacitors should be ceramic

(X7R, C0G), tantalum, or other good quality dielectric type.

#### 4.3 Power Consumption

Power consumption of the CS5376A depends primarily on the power supply voltage of the logic core (VD) and the programmed digital filter clock rate. Digital filter clock rates are selected based on the required output word rate as explained in "Digital Filter Initialization" on page 41.

### 5. RESET CONTROL

The CS5376A reset signal is active low. When released, a series of self-tests are performed and the device either actively boots from an external EE-PROM or enters an idle state waiting for microcontroller configuration.

#### 5.1 Pin Descriptions

#### **RESET** - Pin 55

Reset input, active low.

### BOOT - Pin 56

Boot mode select, latched following a **RESET** rising edge.

BOOT = 1 = EEPROM boot

BOOT = 0 = Microcontroller boot

#### 5.2 Reset Self-Tests

After  $\overline{\text{RESET}}$  is released but before booting, a series of digital filter self-tests are run. Results are

| Self-Test<br>Type | Pass<br>Code | Fail<br>Code |

|-------------------|--------------|--------------|

| Program ROM       | 0x00000A     | 0x00000F     |

| Data ROM          | 0x0000A0     | 0x0000F0     |

| Program RAM       | 0x000A00     | 0x000F00     |

| Data RAM          | 0x00A000     | 0x00F000     |

| Execution Unit    | 0x0A0000     | 0x0F0000     |

combined into the SELFTEST register (0x2F), with 0x0AAAAA indicating all passed. Self-tests require 60 ms to complete, after which configuration commands are serviced.

### 5.3 Boot Configurations

The logic state of the BOOT pin after reset determines if the CS5376A actively reads configuration information from EEPROM or enters an idle state waiting for a microcontroller to write configuration commands.

#### **EEPROM Boot**

When the BOOT pin is high after reset, the CS5376A actively reads data from an external serial EEPROM and then begins operation in the specified configuration. Configuration commands and data are encoded in the EEPROM as specified in the 'Configuration By EEPROM' section of this data sheet, starting on page 26.

#### **Microcontroller Boot**

When the BOOT pin is low after reset, the CS5376A enters an idle state waiting for a microcontroller to write configuration commands and initialize filter operation. Configuration commands and data are written as specified in the 'Configuration By Microcontroller' section of this data sheet, starting on page 32.

## 6. CLOCK GENERATION

The CS5376A requires a 32.768 MHz master clock input, which is used to generate internal digital filter clocks and external modulator clocks.

## 6.1 Pin Description

### CLK - Pin 58

Clock input, nominal frequency 32.768 MHz.

## 6.2 Synchronous Clocking

To guarantee synchronous measurements throughout a sensor network, the CS5376A master clock should be distributed to arrive at all nodes in phase. The 32.768 MHz master clock can either be directly distributed through the system telemetry, or reconstructed locally using a VCXO based PLL. To ensure recovered clocks have identical phase, system PLL designs should use a phase/frequency detector architecture.

## 6.3 Master Clock Jitter and Skew

Care must be taken to minimize jitter and skew in the received master clock as both parameters affect measurement performance.

Jitter in the master clock causes jitter in the generated modulator clocks, resulting in sample timing errors and increased noise.

Skew in the master clock from node to node creates a sample timing offset, resulting in systematic measurement errors in the reconstructed signal.

## 7. SYNCHRONIZATION

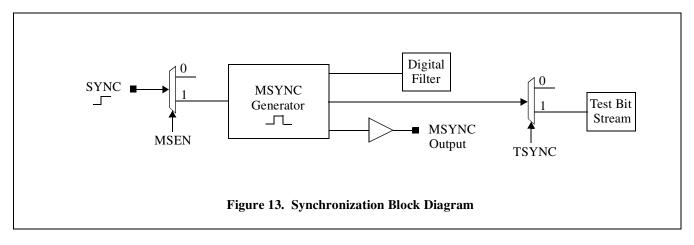

The CS5376A has a dedicated SYNC input that aligns the internal digital filter phase and generates an external signal for synchronizing modulator analog sampling. By providing simultaneous rising edges to the SYNC pins of multiple CS5376A devices, synchronous sampling across a network can be guaranteed.

## 7.1 Pin Description

### SYNC - Pin 59

Synchronization input, rising edge triggered.

## 7.2 MSYNC Generation

The SYNC signal rising edge is used to generate a retimed synchronization signal, MSYNC. The MSYNC signal reinitializes internal digital filter phase and is driven onto the MSYNC output pin to phase align modulator analog sampling.

The MSEN bit in the digital filter CONFIG register (0x00) enables MSYNC generation. See "Modulator Interface" on page 39 for more information about MSYNC.

## 7.3 Digital Filter Synchronization

The internal MSYNC signal resets the digital filter state machine to establish a known digital filter

phase. Filter convolutions restart, and the next output word is available one full sample period later.

Repetitive synchronization is supported when SYNC events occur at exactly the selected output word rate. In this case, re-synchronization occurs at the start of a convolution cycle when the digital filter state machine is already reset.

## 7.4 Modulator Synchronization

The external MSYNC signal phase aligns modulator analog sampling when connected to the CS5371/72 MSYNC input. This ensures synchronous analog sampling relative to MCLK.

Repetitive synchronization of the modulators is supported when SYNC events occur at exactly the selected output word rate. In this case, synchronization will occur at the start of analog sampling.

## 7.5 Test Bit Stream Synchronization

When the test bit stream generator is enabled, an MSYNC signal can reset the internal data pointer. This restarts the test bit stream from the first data point to establish a known output signal phase.

The TSYNC bit in the digital filter TBSCFG register (0x2A) enables synchronization of the test bit stream by MSYNC. When TSYNC is disabled, the test bit stream phase is not affected by MSYNC.

## 8. CONFIGURATION BY EEPROM

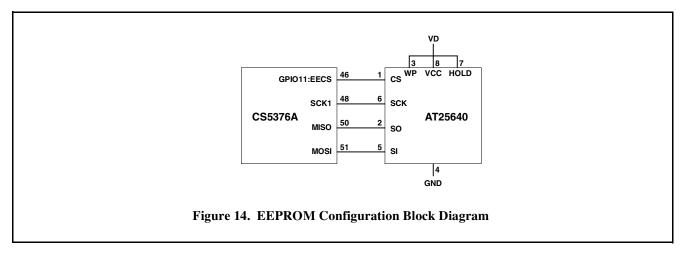

After reset, the CS5376A reads the state of the BOOT pin to determine a source for configuration commands. If BOOT is high, the CS5376A initiates serial transactions through the SPI 1 port to read configuration information from an external EEPROM.

### 8.1 Pin Descriptions

Pins required for EEPROM boot are listed here, other SPI 1 pins are inactive.

## GPIO11:EECS - Pin 46

EEPROM chip select output, active low.

### SCK1 - Pin 48

Serial clock output, nominally 1.024 MHz.

### MOSI - Pin 51

Serial data output pin. Valid on rising edge of SCK1, transition on falling edge.

### MISO - Pin 50

Serial data input pin. Valid on rising edge of SCK1, transition on falling edge.

## 8.2 EEPROM Hardware Interface

When booting from EEPROM the CS5376A SPI 1 port actively performs serial transactions, as shown

in Figure 15, to read configuration commands and data. 8-bit SPI opcodes and 16-bit addresses are combined to read back 8-bit configuration commands and 24-bit configuration data.

System design should include a connection to the configuration EEPROM for in-circuit reprogramming. The CS5376A SPI 1 pins tri-state when inactive to support external connections to the serial bus.

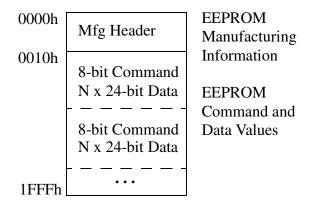

## 8.3 EEPROM Organization

The boot EEPROM holds the 8-bit commands and 24-bit data required to initialize the CS5376A into an operational state. Configuration information starts at memory location 0x10, with addresses 0x00 to 0x0F free for use as manufacturing header information.

The first serial transaction reads a 1-byte command from memory location 0x10 and then, depending on the command type, reads multiple 3-byte data words to complete the command. Command and data reads continue until the 'Filter Start' command is recognized.

The maximum number of bytes that can be written for a single configuration is approximately

| Instruction | Opcode     | Address                 | Definition                                      |

|-------------|------------|-------------------------|-------------------------------------------------|

| ad          | 0x03       | ADDR[15:0]              | Read data beginning at the address given in ADD |

| SPI 1 Read  | from EEPRO | OM                      |                                                 |

| SSI         |            | READ 2 BYTI<br>CMD ADDR |                                                 |

| MOSI        |            | 0x03 ADDR               |                                                 |

| MISO        |            |                         | DATA1 DATA2 DATA3                               |

| EECS        |            |                         |                                                 |

| Cycle       | 1          | 2 3 4                   | 5 6 7 8                                         |

| SCK1        |            |                         |                                                 |

| MOSI        | MSB        | 6 5 4                   | 3 2 1 LSB                                       |

| MISO        | MSB        | 6 5 4                   | 3 2 1 LSB X                                     |

| EECS        |            |                         |                                                 |

|             |            |                         |                                                 |

Figure 16. 8 Kbyte EEPROM Memory Organization

5 KByte (40 Kbit), which includes command overhead:

| Memory Requirement            | Bytes |

|-------------------------------|-------|

| Digital Filter Registers (22) | 154   |

| FIR Coefficients (255+255)    | 1537  |

| IIR Coefficients (3+5)        | 25    |

| Test Bit Stream Data (1024)   | 3076  |

| 'Filter Start' Command        | 1     |

| Total Bytes                   | 4793  |

Table 4. Maximum EEPROM Configuration

Supported serial configuration EEPROMs are SPI mode 0 (0,0) compatible, 16-bit addresses, 8-bit data, larger than 5 KByte (40 KBit). ATMEL AT25640, AT25128, or similar serial EEPROMs are recommended.

## 8.4 EEPROM Configuration Commands

A summary of available EEPROM commands is shown in Table 5.

## Write DF Register - 0x01

This EEPROM command writes a data value to the specified digital filter register. Digital filter registers control hardware peripherals and filtering functions. See "Digital Filter Registers" on page 87 for the bit definitions of the digital filter registers.

## Sample Command:

Write digital filter register 0x00 with data value 0x070431. Then write 0x20 with data 0x000240.

01 00 00 00 07 04 31

01 00 00 20 00 02 40

## Write FIR Coefficients - 0x02

This EEPROM command writes custom coefficients for the FIR1 and FIR2 filters. The first two data words set the number of FIR1 and FIR2 coefficients to be written. The remaining data words are the concatenated FIR1 and FIR2 coefficients.

A maximum of 255 coefficients can be written for each FIR filter, though the available digital filter computation cycles will limit their practical size. See "FIR Filter" on page 47 for more information about FIR filter coefficients.

Sample Command:

Write FIR1 coefficients 0x00022E, 0x000771 then FIR2 coefficients 0xFFFFB9, 0xFFFE8D.

02 00 00 02 00 00 02

00 02 2E 00 07 71 FF FF B9 FF FE 8D

## Write IIR Coefficients - 0x03

This EEPROM command writes custom coefficients for the two stage IIR filter. The IIR architecture and number of coefficients is fixed, so eight data words containing coefficient values always immediately follow the command byte. The IIR coefficient write order is: a11, b10, b11, a21, a22, b20, b21, and b22. See "IIR Filter" on page 55 for more information about IIR filter coefficients.

Sample Command:

Write IIR1 coefficients 0x84BC9D, 0x7DA1B1, 0x825E4F, and IIR2 coefficients 0x83694F, 0x3CAD5F, 0x3E5104, 0x835DF8, 0x3E5104.

03

84 BC 9D 7D A1 B1 82 5E 4F 83 69 4F

3C AD 5F 3E 51 04 83 5D F8 3E 51 04

#### Write ROM Coefficients - 0x04

This EEPROM command selects the on-chip coefficients for the FIR1, FIR2, IIR 1st order, and IIR 2nd order filters for use by the digital filter. One data word is required to select which internal coefficient sets to use. See "Filter Coefficient Selection" on page 41 for information about selecting on-chip FIR and IIR coefficient sets.

#### Sample Command:

Select IIR1 and IIR2 3 Hz @ 500 SPS low-cut coefficients, with FIR1 and FIR2 linear phase highcut coefficients. Data word 0x002200.

$04\ 00\ 22\ 00$

### Write TBS Data - 0x05

This EEPROM command writes a custom data set for the test bit stream (TBS) generator. This command, along with the ability to program the test bit stream generator interpolation and clock rate, can create custom frequency test signals.

The first data word sets the number of TBS data to be written and the remaining data words are the TBS data values. See "Test Bit Stream Generator" on page 64 for information about using custom test bit stream data sets.

| Name                   | CMD<br>8-bit | DATA<br>24-bit                                       | Description                       |

|------------------------|--------------|------------------------------------------------------|-----------------------------------|

| NOP                    | 00           | -                                                    | No Operation                      |

| WRITE DF REGISTER      | 01           | REG<br>DATA                                          | Write Digital Filter Register     |

| WRITE FIR COEFFICIENTS | 02           | NUM FIR1<br>NUM FIR2<br>(FIR COEF)                   | Write Custom FIR Coefficients     |

| WRITE IIR COEFFICIENTS | 03           | a11<br>b10<br>b11<br>a21<br>a22<br>b20<br>b21<br>b22 | Write Custom IIR Coefficients     |

| WRITE ROM COEFFICIENTS | 04           | COEF SEL                                             | Use On-Chip Coefficients          |

| WRITE TBS DATA         | 05           | NUM TBS<br>(TBS DATA)                                | Write Custom Test Bit Stream Data |

| WRITE ROM TBS          | 06           | -                                                    | Use On-Chip TBS Data              |

| FILTER START           | 07           | -                                                    | Start Digital Filter Operation    |

(DATA) indicates multiple words of this type are to be written.

#### **Table 5. EEPROM Boot Configuration Commands**

#### Sample Command:

Write test bit stream data 0x000000, 0x0007DA, 0x000FB5, 0x00178F.

05 00 00 04

00 00 00 00 07 DA 00 0F B5 00 17 8F

#### Write TBS ROM Data - 0x06

This EEPROM command selects the on-chip test bit stream (TBS) data for use by the TBS generator. No data words are required for this EEPROM command. See "Test Bit Stream Generator" on page 64 for more information about the on-chip test bit stream data set. Sample Command:

06

#### Filter Start - 0x07

This EEPROM command initializes and starts the digital filter. Measurement data becomes available one full sample period after this command is received. No data words are required for this EE-PROM command.

Sample Command:

07

### 8.5 Example EEPROM Configuration

Table 6 shows an example EEPROM file for a minimal CS5376A configuration.

| Addr | Data | Description            |

|------|------|------------------------|

| 00   | 00   | Mfg header             |

| 01   | 00   |                        |

| 02   | 00   |                        |

| 03   | 00   |                        |

| 04   | 00   |                        |

| 05   | 00   |                        |

| 06   | 00   |                        |

| 07   | 00   |                        |

| 08   | 00   |                        |

| 09   | 00   |                        |

| 0A   | 00   |                        |

| 0B   | 00   |                        |

| 0C   | 00   |                        |

| 0D   | 00   |                        |

| 0E   | 00   |                        |

| 0F   | 00   |                        |

| 10   | 04   | Write ROM Coefficients |

| 11   | 00   |                        |

| 12   | 22   |                        |

| 13   | 00   |                        |

| 14   | 06   | Write TBS ROM Data     |

| 15   | 01   | Write CONFIG Register  |

| 16   | 00   |                        |

| 17   | 00   |                        |

| 18   | 00   |                        |

| 19   | 07   |                        |

| 1A   | 04   |                        |

| 1B   | 31   |                        |

| 1C   | 01   | Write FILTCFG Register |

| 1D   | 00   |                        |

| 1E   | 00   |                        |

| 1F   | 20   |                        |

| Addr | Data | Description            |

|------|------|------------------------|

| 20   | 00   |                        |

| 21   | 02   |                        |

| 22   | 40   |                        |

| 23   | 01   | Write TBSCFG Register  |

| 24   | 00   |                        |

| 25   | 00   |                        |

| 26   | 2A   |                        |

| 27   | 07   |                        |

| 28   | 40   |                        |

| 29   | 40   |                        |

| 2A   | 01   | Write TBSGAIN Register |

| 2B   | 00   |                        |

| 2C   | 00   |                        |

| 2D   | 2B   |                        |

| 2E   | 04   |                        |

| 2F   | B0   |                        |

| 30   | 00   |                        |

| 31   | 07   | Filter Start           |

Table 6. Example EEPROM File

## 9. CONFIGURATION BY MICROCONTROLLER

After reset, the CS5376A reads the state of the BOOT pin to determine a source for configuration commands. If BOOT is low, the CS5376A receives configuration commands from a microcontroller.

## 9.1 Pin Descriptions

Pins required for microcontroller boot are listed here, other SPI 1 pins are inactive.

## <u>SSI</u> - Pin 49

Slave select input pin, active low. Serial chip select input from a microcontroller.

## SCK1 - Pin 48

Serial clock input pin. Serial clock input from microcontroller, maximum 4.096 MHz.

## MOSI - Pin 51

Serial data input pin. Valid on rising edge of SCK1, transition on falling edge.

### MISO - Pin 50

Serial data output pin. Valid on rising edge of SCK1, transition on falling edge. Open drain output requiring a 10 k $\Omega$  pull-up resistor.

## SINT - Pin 52

Serial interrupt output pin, active low. 1 uS active low pulse output when ready for next serial transaction.

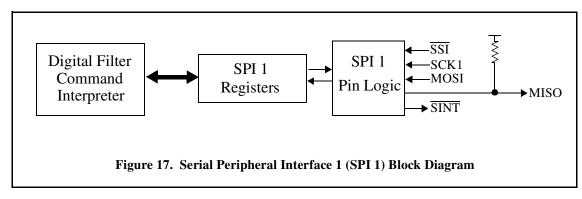

## 9.2 Microcontroller Hardware Interface

When booting from a microcontroller the CS5376A SPI 1 port receives configuration commands and configuration data through serial transactions, as shown in Figure 18. 8-bit SPI opcodes and 8-bit addresses are combined to read and write 24-bit configuration commands and data.

Microcontroller serial transactions require toggling the  $\overline{SSI}$  pin as the CS5376A chip select and writing a serial clock to the SCK1 input. Serial data is input to the CS5376A on the MOSI pin, and output from the CS5376A on the MISO pin.

### 9.3 Microcontroller Serial Transactions

Microcontroller configuration commands are written to the digital filter through the SPI 1 registers. A 24-bit command and two 24-bit data words can be written to the SPI 1 registers in any single serial transaction. Some commands require additional data words through additional serial transactions to complete.

### 9.3.1 SPI opcodes

A microcontroller communicates with the CS5376A SPI 1 port using standard 8-bit SPI opcodes and an 8-bit SPI address. The standard SPI 'Read' and 'Write' opcodes are listed in Figure 18.

| Instruction | Opcode       | Address    | Definition                                             |

|-------------|--------------|------------|--------------------------------------------------------|

| Write       | 0x02         | ADDR[7:0]  | Write SPI 1 registers beginning at the address in ADDF |

| Read        | 0x03         | ADDR[7:0]  | Read SPI 1 registers beginning at the address in ADDF  |

|             |              |            |                                                        |

|             |              |            |                                                        |

|             | oller Write  | to SPI 1   | <i>г</i>                                               |

| SSI         | \            |            |                                                        |

|             | /            |            |                                                        |

| MOSI        | X (          | 0x02 ADDR  | Å Data1 Å Data2 Å   Å DataN Å                          |

|             |              |            |                                                        |

| MISO        | XXX          |            |                                                        |

|             |              |            |                                                        |

| Microconti  | oller Read f | from SPI 1 |                                                        |

| SSI         |              |            |                                                        |

|             |              |            |                                                        |

| MOSI        | X (          | 0x03 ADDR  | ×XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                 |

|             |              |            |                                                        |

| MISO        |              |            | Å Data1 Å Data2 Å   Å DataN Å                          |

|             |              |            | ~                                                      |

|             | <b></b>      |            |                                                        |

| Cycle       | 1            | 2 3        | 4 5 6 7 8                                              |

| 0017        |              |            |                                                        |

| SCK1        |              |            |                                                        |

| MOOL        | V MSB V      | 6 \ 5 \    | 4 X 3 X 2 X 1 X LSB X                                  |

| MOSI        |              |            |                                                        |

| MISO -      | MSB \/       | 6 \ 5 \    | 4 X 3 X 2 X 1 X LSB X X                                |

| WIGO        |              | <u> </u>   |                                                        |

| SSI         |              |            |                                                        |

|             |              |            |                                                        |

|             |              |            |                                                        |

#### 9.3.2 SPI 1 registers

The SPI 1 registers are shown in Figure 19 and are 24-bit registers mapped into an 8-bit register space as high, mid, and low bytes. See "SPI 1 Registers" on page 82 for the bit definitions of the SPI 1 registers.

#### 9.3.3 SPI 1 transactions

A serial transaction to the SPI 1 registers starts with an SPI opcode, followed by an address, and then some number of data bytes written or read starting at that address.

Typical serial write transactions require sending groups of 5, 8, or 11 total bytes to the SPI1CMD or SPI1DAT1 registers.

Example 5-byte write transaction to SPI1CMD

02 03 12 34 56

Example 5-byte write transaction to SPI1DAT1

02 06 12 34 56

Example 8-byte write transaction to SPI1CMD

02 03 12 34 56 AB CD EF

Example 8-byte write transaction to SPI1DAT1

02 06 12 34 56 AB CD EF

Example 11-byte write transaction to SPI1CMD

02 03 12 34 56 AB CD EF 65 43 21

Typical serial read transactions require groups of 3 or 5 bytes, split between writing into MOSI and reading from MISO.

3-byte read transaction of mid-byte of SPI1CTRL

MOSI: 03 01 00

MISO: xx xx 12

5-byte read transaction of SPI1DAT1 MOSI: 03 06 00 00 00 MISO: xx xx 12 34 56

#### 9.3.4 Multiple serial transactions

Some configuration commands require multiple serial transactions to complete. There must be a small delay between transactions for the CS5376A to process the incoming data. Three methods can be used to ensure the CS5376A is ready to receive the next configuration command.

1) Delay a fixed 1 ms period to guarantee enough time for the command to be completed.

2) Monitor the  $\overline{\text{SINT}}$  pin for a 1 us active low pulse. This pulse output occurs once the CS5376A completes processing the current command.

3) Verify the status of the E2DREQ bit by reading the SPI1CTRL register. When low, the CS5376A is ready for the next command.

#### 9.3.5 Polling E2DREQ

One transaction type that can always be performed no matter the delay from the previous configuration command is reading E2DREQ in the mid-byte of the SPI1CTRL register. A 3-byte read transaction.

MOSI: 03 01 00 MISO: xx xx 01 <- E2DREQ bit high MISO: xx xx 00 <- E2DREQ bit low

| Name     | Addr.   | Туре | # Bits  | Description   |

|----------|---------|------|---------|---------------|

| SPI1CTRL | 00 - 02 | R/W  | 8, 8, 8 | SPI 1 Control |

| SPI1CMD  | 03 - 05 | R/W  | 8, 8, 8 | SPI 1 Command |

| SPI1DAT1 | 06 - 08 | R/W  | 8, 8, 8 | SPI 1 Data 1  |

| SPI1DAT2 | 09 - 0B | R/W  | 8, 8, 8 | SPI 1 Data 2  |

Figure 19. SPI 1 Registers

The E2DREQ bit reads high while a configuration command is being processed. When low, the digital filter is ready to receive a new configuration command.

## 9.4 Microcontroller Configuration Commands

A summary of available microcontroller configuration commands is listed in Table 7.

### Write DF Register - 0x01

This configuration command writes a specified digital filter register. Digital filter registers control hardware peripherals and filtering functions. See "Digital Filter Registers" on page 87 for the bit definitions of the digital filter registers.

Sample Command:

Write digital filter register 0x00 with data value 0x070431. Then write 0x20 with data 0x000240.

02 03 00 00 01 00 00 00 07 04 31 Delay 1 ms, monitor SINT, or poll E2DREQ 02 03 00 00 01 00 00 20 00 02 40 Delay 1 ms, monitor SINT, or poll E2DREQ

## Read DF Register - 0x02

This command reads a specified digital filter register. The register value is requested in the first SPI transaction, with the register value copied to SPI1DAT1 and read in a subsequent SPI transaction.

Sample Command:

Read digital filter registers 0x00 and 0x20.

02 03 00 00 02 00 00 00

| Name                   | CMD<br>24-bit | DAT1<br>24-bit           | DAT2<br>24-bit           | Description                       |

|------------------------|---------------|--------------------------|--------------------------|-----------------------------------|

| NOP                    | 000000        | -                        | -                        | No Operation                      |

| WRITE DF REGISTER      | 000001        | REG                      | DATA                     | Write Digital Filter Register     |

| READ DF REGISTER       | 000002        | REG<br>[DATA]            | -                        | Read Digital Filter Register      |

| WRITE FIR COEFFICIENTS | 000003        | NUM FIR1<br>(FIR COEF)   | NUM FIR2<br>(FIR COEF)   | Write Custom FIR Coefficients     |

| WRITE IIR COEFFICIENTS | 000004        | a11<br>b11<br>a22<br>b21 | b10<br>a21<br>b20<br>b22 | Write Custom IIR Coefficients     |

| WRITE ROM COEFFICIENTS | 000005        | COEF SEL                 | -                        | Use On-Chip Coefficients          |

| WRITE TBS DATA         | 000006        | NUM TBS<br>(TBS DATA)    | -<br>(TBS DATA)          | Write Custom Test Bit Stream Data |

| WRITE ROM TBS          | 000007        | -                        | -                        | Use On-Chip TBS Data              |

| FILTER START           | 000008        | -                        | -                        | Start Digital Filter Operation    |

| FILTER STOP            | 000009        | -                        | -                        | Stop Digital Filter Operation     |

[DATA] indicates data word returned from digital filter.

(DATA) indicates multiple words of this type are to be written.

#### Table 7. Microcontroller Boot Configuration Commands

Delay 1 ms, monitor SINT, or poll E2DREQ MOSI: 03 06 00 00 00 MISO: xx xx 07 04 31 02 03 00 00 02 00 00 20 Delay 1 ms, monitor SINT, or poll E2DREQ MOSI: 03 06 00 00 00 MISO: xx xx 00 02 40

## Write FIR Coefficients - 0x03

This command writes custom coefficients for the FIR1 and FIR2 filters. The first two data words set the number of FIR1 and FIR2 coefficients to be written. The remaining data words are the concatenated FIR1 and FIR2 coefficients.

A maximum of 255 coefficients can be written for each FIR filter, though the available digital filter computation cycles will limit their practical size. See "FIR Filter" on page 47 for more information about FIR filter coefficients.

Sample Command:

Write FIR1 coefficients 0x00022E, 0x000771 then FIR2 coefficients 0xFFFFB9, 0xFFFE8D.

02 03 00 00 03 00 00 02 00 00 02

Delay 1 ms, monitor SINT, or poll E2DREQ

02 06 00 02 2E 00 07 71

Delay 1 ms, monitor SINT, or poll E2DREQ

02 06 FF FF B9 FF FE 8D

Delay 1 ms, monitor SINT, or poll E2DREQ

### Write IIR Coefficients - 0x04

This command writes custom coefficients for the two stage IIR filter. The IIR architecture and number of coefficients is fixed, so eight coefficient values immediately follow this command. The IIR coefficient write order is: a11, b10, b11, a21, a22, b20, b21, and b22. See "IIR Filter" on page 55 for more information about IIR filter coefficients. Sample Command:

Write IIR1 coefficients 0x84BC9D, 0x7DA1B1, 0x825E4F, and IIR2 coefficients 0x83694F, 0x3CAD5F, 0x3E5104, 0x835DF8, 0x3E5104.

02 03 00 00 04 84 BC 9D 7D A1 B1

Delay 1 ms, monitor SINT, or poll E2DREQ

02 06 82 5E 4F 83 69 4F

Delay 1 ms, monitor SINT, or poll E2DREQ

02 06 3C AD 5F 3E 51 04

Delay 1 ms, monitor SINT, or poll E2DREQ

02 06 83 5D F8 3E 51 04

Delay 1 ms, monitor SINT, or poll E2DREQ

## Write ROM Coefficients - 0x05

This configuration command selects the on-chip coefficients for FIR1, FIR2, IIR 1st order, and IIR 2nd order filters for use by the digital filter. One data word is required to select which internal coefficient sets to use. See "Filter Coefficient Selection" on page 41 for information about selecting on-chip FIR and IIR coefficient sets.

Sample Command:

Select IIR1 and IIR2 3 Hz @ 500 SPS low-cut coefficients, with FIR1 and FIR2 linear phase highcut coefficients. Data word 0x002200.

02 03 00 00 05 00 22 00

Delay 1 ms, monitor SINT, or poll E2DREQ

### Write TBS Data - 0x06

This command writes a custom data set for the test bit stream (TBS) generator. This command, along with the ability to program the test bit stream generator interpolation and clock rate, can create custom frequency test signals.

The first data word sets the number of TBS data to be written and the remaining data words are the TBS data values. See "Test Bit Stream Generator"

on page 64 for information about using custom test bit stream data sets.

#### Sample Command:

Write test bit stream data 0x000000, 0x0007DA, 0x000FB5, 0x00178F.

02 03 00 00 06 00 00 04

Delay 1 ms, monitor SINT, or poll E2DREQ

02 06 00 00 00 00 07 DA

Delay 1 ms, monitor  $\overline{\text{SINT}}$ , or poll E2DREQ

02 06 00 0F B5 00 17 8F

Delay 1 ms, monitor  $\overline{\text{SINT}}$ , or poll E2DREQ

#### Write TBS ROM Data - 0x07

This command selects the on-chip test bit stream (TBS) data for use by the TBS generator. No data words are required for this configuration command. See "Test Bit Stream Generator" on page 64 for information about the on-chip test bit stream data set.

Sample Command:

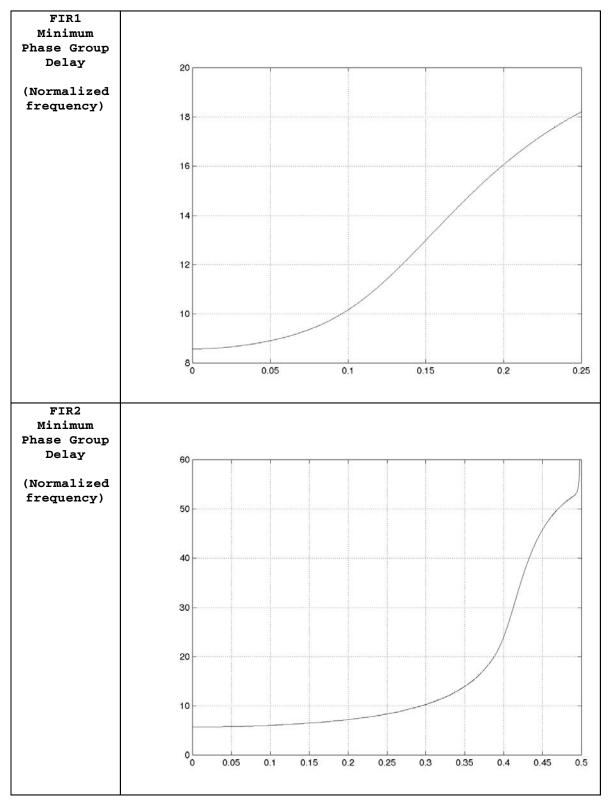

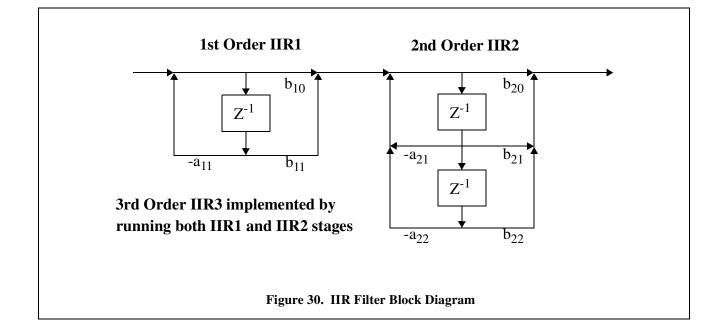

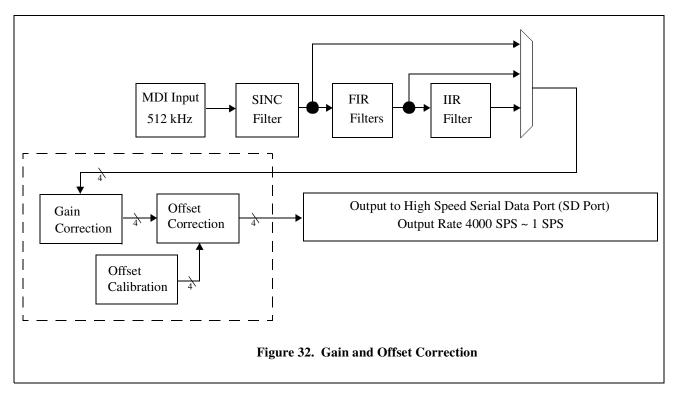

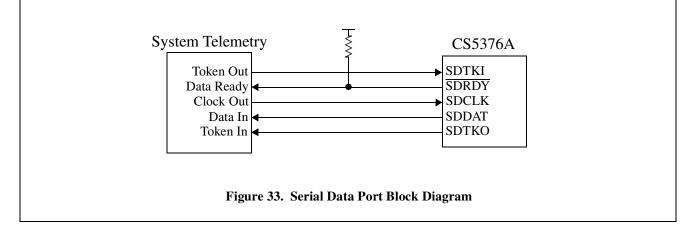

02 03 00 00 07