# **TDA9106**

# LOW COST DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

#### PRELIMINARY DATA

#### **HORIZONTAL**

- SELF-ADAPTATIVE

- DUAL PLL CONCEPT

- 150kHz MAXIMUM FREQUENCY

- X-RAY PROTECTION INPUT

- I<sup>2</sup>C CONTROLS: HORIZONTAL DUTY-CYCLE, H-POSITION, FREE RUNNING FREQUENCY, FREQUENCY GENERATOR FOR BURN-IN MODE

#### **VERTICAL**

- VERTICAL RAMP GENERATOR

- 50 TO 165Hz AGC LOOP

- GEOMETRY TRACKING WITH V-POS & AMP

- I<sup>2</sup>C CONTROLS: V-AMP, V-POS, S-CORR, C-CORR

#### I<sup>2</sup>C GEOMETRY CORRECTIONS

- VERTICAL PARABOLA GENERATOR (Pincushion, Keystone, Corner Correction, Top/bottom Corner Correction Balance)

- HORIZONTAL DYNAMIC PHASE (Side Pin Balance & Parallelogram)

- HORIZONTAL AND VERTICAL DYNAMIC FO-CUS (Horizontal Focus Amplitude, Horizontal Focus Symmetry)

#### **GENERAL**

- SYNC PROCESSOR

- HOR. & VERT. SYNC OUTPUT FOR MCU

- HOR. & VERT. BLANKING OUTPUTS

- 12V SUPPLY VOLTAGE

- 8V REFERENCE VOLTAGE

- HOR. & VERT. LOCK UNLOCK OUTPUTS

- READ/WRITE I<sup>2</sup>C INTERFACE

- HORIZONTAL MOIRE OR DAC OUTPUT

#### **DESCRIPTION**

f.dzsc.com

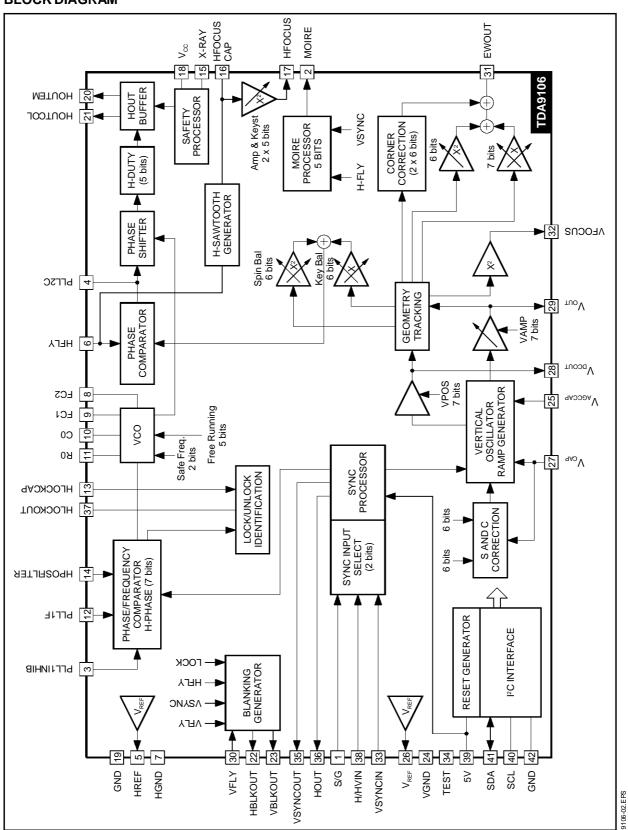

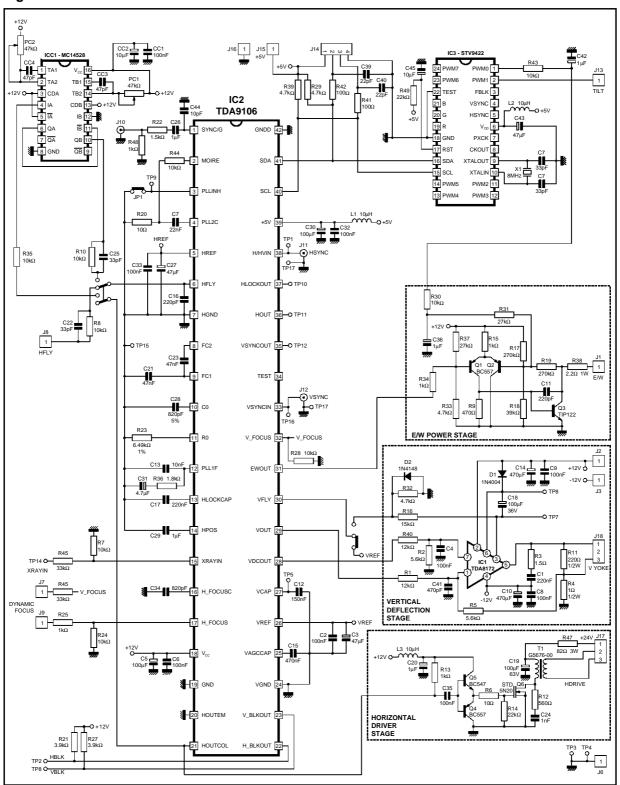

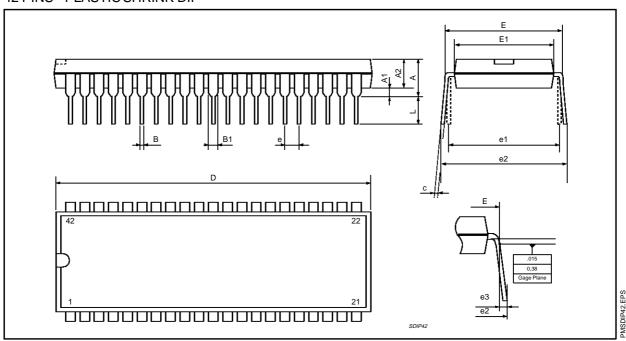

The TDA9106 is a monolithic integrated circuit assembled in 42 pins shrunk dual in line plastic package. This IC controls all the functions related to the horizontal and vertical deflection in multimodes or multi-frequency computer display monitors.

The internal sync processor, combined with the very powerful geometry correction block are making the TDA9106 suitable for very high performance monitors with very few external components.

It is particularly well suited for high-end 15" and 17" monitors.

Combined with ST7275 Microcontroller family, TDA9206 (Video preamplifier) and STV942x (On-Screen Display controller) the TDA9106 allows to built fully I<sup>2</sup>C bus controlled computer display monitors, thus reducing the number of external components to a minimum value.

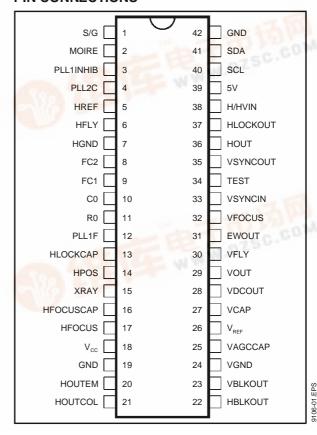

#### **PIN CONNECTIONS**

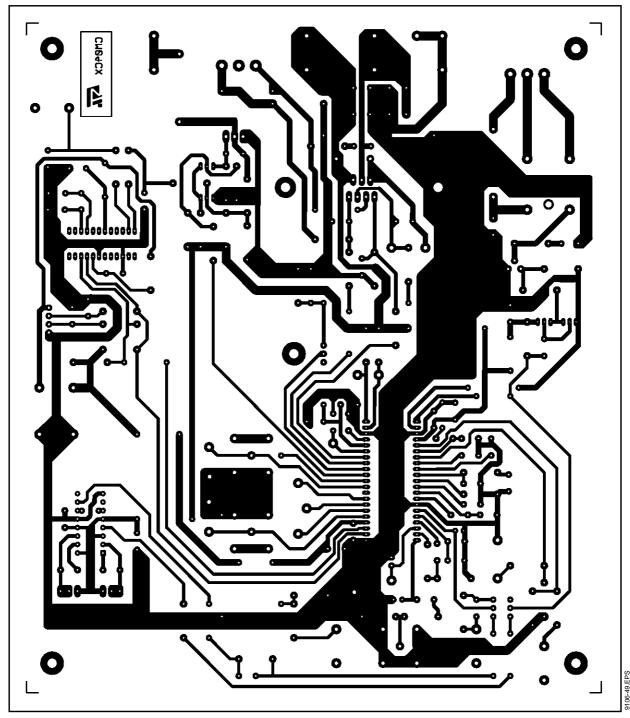

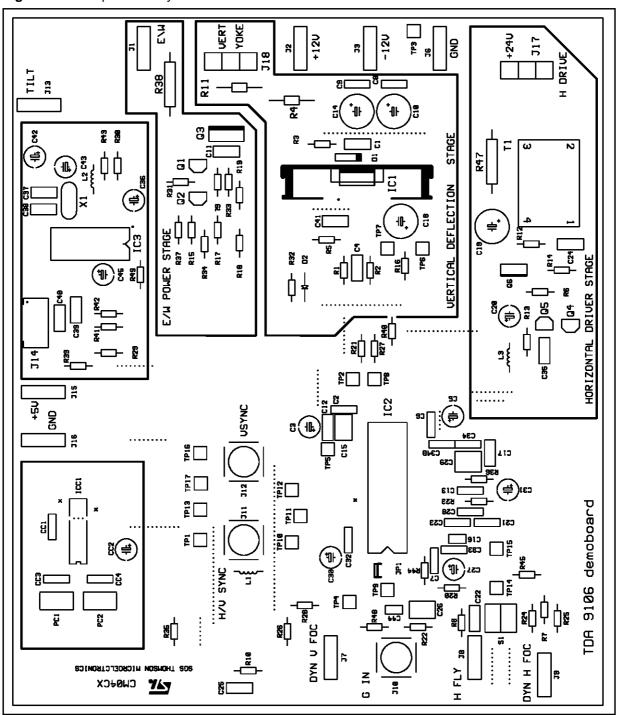

November 1997 1/30

#### **TDA9106**

#### **PIN CONNECTIONS**

| Pin | Name            | Function                                                                                  |

|-----|-----------------|-------------------------------------------------------------------------------------------|

| 1   | S/G             | Sync on green input                                                                       |

| 2   | MOIRE           | Moire output                                                                              |

| 3   | PLL1 INHIB      | TTL-Compatible input for PLL1 inhibition                                                  |

| 4   | PLL2C           | Second PLL Loop Filter                                                                    |

| 5   | HREF            | Horizontal Section Reference Voltage (to filter)                                          |

| 6   | HFLY            | Horizontal Flyback Input (positive polarity)                                              |

| 7   | HGND            | Horizontal Section Ground                                                                 |

| 8   | FC2             | VCO Low Threshold filtering Capacitor                                                     |

| 9   | FC1             | VCO High Threshold filtering Capacitor                                                    |

| 10  | C0              | Horizontal Oscillator Capacitor                                                           |

| 11  | R0              | Horizontal Oscillator Resistor                                                            |

| 12  | PLL1F           | First PLL Loop Filter                                                                     |

| 13  | HLOCKCAP        | First PLL Lock/Unlock Time Constant Capacitor                                             |

| 14  | HPOS            | Horizontal Centering Output (to filter)                                                   |

| 15  | XRAY            | X-RAY protection input (with internal latch function)                                     |

| 16  | HFOCUSCAP       | Horizontal Dynamic Focus Oscillator Capacitor                                             |

| 17  | HFOCUS          | Horizontal Dynamic Focus Output                                                           |

| 18  | V <sub>CC</sub> | Supply Voltage (12V Typ)                                                                  |

| 19  | GND             | General Ground (related to V <sub>CC</sub> )                                              |

| 20  | HOUTEM          | Horizontal Drive Output (internal transistor emitter)                                     |

| 21  | HOUTCOL         | Horizontal Drive Output (int. trans. open collector)                                      |

| 22  | HBLKOUT         | Horizontal Blanking Output (see activation table)                                         |

| 23  | VBLKOUT         | Vertical Blanking Output (see activation table)                                           |

| 24  | VGND            | Vertical Section Ground                                                                   |

| 25  | VAGCCAP         | Memory Capacitor for Automatic Gain Control Loop in Vertical Ramp Generator               |

| 26  | $V_{REF}$       | Vertical Section Reference Voltage (to filter)                                            |

| 27  | VCAP            | Vertical Sawtooth Generator Capacitor                                                     |

| 28  | $V_{DCOUT}$     | Vertical Position Reference Voltage Output                                                |

| 29  | VOUT            | Vertical Ramp Output (with frequency independant amplitude and S or C Corrections if any) |

| 30  | VFLY            | Vertical Flyback Input (positive polarity)                                                |

| 31  | EWOUT           | East/West Pincushion Correction Parabola Output (with Corner corrections if any)          |

| 32  | VFOCUS          | Vertical Dynamic Focus Output                                                             |

| 33  | VSYNCIN         | TTL-compatible Vertical Sync Input (for separated H&V)                                    |

| 34  | TEST            | Not to be used - Test pin                                                                 |

| 35  | VSYNCOUT        | TTL Vertical Sync Output (Extracted VSYNC in case of S/G or TTL Composite HV Inputs)      |

| 36  | HOUT            | TTL Horizontal Sync Output (To be used for frequency measurement)                         |

| 37  | HLOCKOUT        | First PLL Lock/Unlock Output (5V unlocked - 0V locked)                                    |

| 38  | H/HVIN          | TTL-compatible Horizontal Sync Input                                                      |

| 39  | 5V              | Supply Voltage (5V Typ.)                                                                  |

| 40  | SCL             | I <sup>2</sup> C-Clock input                                                              |

| 41  | SDA             | I <sup>2</sup> C-Data input                                                               |

| 42  | GND             | Ground (Related to 5V)                                                                    |

106-01.TBL

#### **QUICK REFERENCE DATA**

| Parameter                                                                    | Value      | Unit |

|------------------------------------------------------------------------------|------------|------|

| Horizontal Frequency                                                         | 15 to 150  | kHz  |

| Autosynch Frequency (for given R0 and C0)                                    | 1 to 4.5   | FH   |

| ± Horizontal Sync Polarity Input                                             | YES        |      |

| Polarity Detection (on both Horizontal and Vertical Sections)                | YES        |      |

| TTL Composite Synch or Sync on Green                                         | YES        |      |

| Lock/Unlock Identification (on both Horizontal 1st PLL and Vertical Section) | YES        |      |

| I <sup>2</sup> C Control for H-Position                                      | ± 10       | %    |

| XRay Protection                                                              | YES        |      |

| I <sup>2</sup> C Horizontal Duty Adjust                                      | 30 to 60   | %    |

| I <sup>2</sup> C Free Running Adjustment                                     | 0.8 to 1.3 | F0   |

| Stand-by Function                                                            | YES        |      |

| Two Polarities H-Drive Outputs                                               | YES        |      |

| Supply Voltage Monitoring                                                    | YES        |      |

| PLL1 Inhibition Possibility                                                  | YES        |      |

| Blanking Outputs (both Horizontal and Vertical)                              | YES        |      |

| Vertical Frequency                                                           | 35 to 200  | Hz   |

| Vertical Autosync (for 150nF)                                                | 50 to 165  | Hz   |

| Vertical S-Correction                                                        | YES        |      |

| Vertical C-Correction                                                        | YES        |      |

| Vertical Amplitude Adjustment                                                | YES        |      |

| Vertical Position Adjustment                                                 | YES        |      |

| East/West Parabola Output                                                    | YES        |      |

| Pin Cushion Correction Amplitude Adjustment                                  | YES        |      |

| Keystone Adjustment                                                          | YES        |      |

| Corner and Corner Balance Adjustments                                        | YES        |      |

| Internal Dynamic Horizontal Phase Control                                    | YES        |      |

| Side Pin Balance Amplitude Adjustment                                        | YES        |      |

| Parallelogram Adjustment                                                     | YES        |      |

| Tracking of Geometric Corrections                                            | YES        |      |

| Reference Voltage (both on Horizontal and Vertical)                          | YES        |      |

| Dynamic Focus (both Horizontal and Vertical)                                 | YES        |      |

| I <sup>2</sup> C Horizontal Dynamic Focus Amplitude Adjustment               | YES        |      |

| I <sup>2</sup> C Horizontal Dynamic Focus Keystone Adjustment                | YES        |      |

| Type of Input Sync Detection (supplied by 5V Digital Supply)                 | YES        |      |

| Horizontal Moiré Output                                                      | YES        |      |

| 1 <sup>2</sup> C Controlled H-Moiré Amplitude                                | YES        |      |

| Frequency Generator for Burn-in                                              | YES        |      |

| Fast I <sup>2</sup> C Read/Write                                             | 400        | kHz  |

06-02.TBL

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                                                                                                       | Value                           | Unit    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------|

| Vcc               | Supply Voltage (Pin 18)                                                                                                         | 13.5                            | V       |

| $V_{DD}$          | Supply Voltage (Pin 39)                                                                                                         | 5.7                             | V       |

| V <sub>IN</sub>   | Max Voltage on Pin 6 Pins 15, 21, 22, 23 Pin 1 Pin 4 Pins 3, 33,34,37,38,40,41 Pin 16 Pins 8, 9, 10, 11, 12, 13, 14, 25, 27, 30 | 1.8<br>12<br>3.6<br>4<br>5<br>6 | >>>>>   |

| VESD              | ESD susceptibility Human Body Model,100pF Discharge through 1.5k $\Omega$ EIAJ Norm,200pF Discharge through $0\Omega$           | 2<br>300                        | kV<br>V |

| T <sub>stg</sub>  | Storage Temperature                                                                                                             | -40, +150                       | °C      |

| Tj                | Junction Temperature                                                                                                            | +150                            | °C      |

| T <sub>oper</sub> | Operating Temperature                                                                                                           | 0, +70                          | °C      |

THERMAL DATA

| Symbol                | Parameter                                | Value | Unit |

|-----------------------|------------------------------------------|-------|------|

| R <sub>th (j-a)</sub> | Junction-ambient Thermal Resistance Max. | 65    | °C/W |

# SYNCHRO PROCESSOR Operating Conditions

| Symbol | Parameter                                              | Test Conditions | Min. | Тур. | Max. | Unit |

|--------|--------------------------------------------------------|-----------------|------|------|------|------|

| HsVR   | Horizontal Sync Input Voltage                          | Pin 38          | 0    |      | 5    | V    |

| MinD   | Minimum Horizontal Input Pulses Duration               | Pin 38          | 0.7  |      |      | μs   |

| Mduty  | Maximum Horizontal Input Signal Duty Cycle             | Pin 38          |      |      | 25   | %    |

| VsVR   | Vertical Sync Input Voltage                            | Pin 33          | 0    |      | 5    | V    |

| VSW    | Minimum Vertical Sync Pulse Width                      | Pin 33          | 5    |      |      | μs   |

| VSmD   | Maximum Vertical Sync Input Duty Cycle                 | Pin 33          |      |      | 15   | %    |

| VextM  | Maximum Vertical Sync Width on TTL H/Vcomposite or S/G | Pins 1, 38      |      |      | 750  | μs   |

## **Electrical Characteristics** (V<sub>DD</sub> = 5V, T<sub>amb</sub> = 25°C)

| Symbol  | Parameter                                                          | Test Conditions              | Min. | Тур.   | Max. | Unit |

|---------|--------------------------------------------------------------------|------------------------------|------|--------|------|------|

| VSGDC   | S/G Clamped DC Level                                               | Pin 1, $I_1 = -1\mu A$       |      | 1      |      | V    |

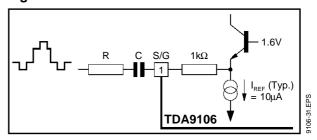

| ISGbias | Internal Diode Bias Current                                        | Pin 1, V <sub>1</sub> = 1.6V |      | 10     |      | μΑ   |

| VSGTh   | Slicing Level (see application design choice)                      | Pin 1                        |      | 0.2    |      | V    |

| VINTH   | Horizontal and Vertical Input Voltage (Pins 33,38)                 | Low Level<br>High Level      | 2.2  |        | 0.8  | V    |

| RIN     | Horizontal and Vertical Pull-Up Resistor                           | Pins 33,38                   |      | 200    |      | kΩ   |

| VOut    | Output Voltage (Pins 35,36,37)                                     | Low level<br>High Level      |      | 0<br>5 |      | V    |

| TfrOut  | Falling and Rising Output CMOS Buffer                              | Pins 35,36,37<br>Cout = 20pF |      | 100    |      | ns   |

| VHlock  | Horizontal 1st PLL Lock Output Status (Pin 37)                     | Locked<br>Unlocked           |      | 0<br>5 |      | V    |

| VoutT   | Extracted Vsync Integration Time (% of TH) on H/V Composite or S/G | Pin 35, C0 = 820pF           | 26   | 35     |      | %    |

3106-05.TBL

# I<sup>2</sup>C READ/WRITE

**Electrical Characteristics** (V<sub>DD</sub> = 5V,T<sub>amb</sub> = 25°C)

| Symbol                     | Parameter                                        | Test Conditions | Min. | Тур. | Max. | Unit |  |

|----------------------------|--------------------------------------------------|-----------------|------|------|------|------|--|

| I <sup>2</sup> C PROCESSOR |                                                  |                 |      |      |      |      |  |

| Fscl                       | Maximum Clock Frequency                          | Pin 40          | 400  |      |      | kHz  |  |

| Tlow                       | Low period of the SCL Clock                      | Pin 40          | 1.3  |      |      | μs   |  |

| Thigh                      | High period of the SCL Clock                     | Pin 40          | 0.6  |      |      | μs   |  |

| Vinth                      | SDA and SCL Input Threshold                      | Pins 40,41      |      | 2.2  |      | V    |  |

| VACK                       | Acknowledge Output Voltage on SDA input with 3mA | Pin 41          |      |      | 0.4  | V    |  |

See also I<sup>2</sup>C Table Control and I2C Sub Address Control

# HORIZONTAL SECTION Operating Conditions

| -                    | _                                                           |                                 |      |      |          |          |

|----------------------|-------------------------------------------------------------|---------------------------------|------|------|----------|----------|

| Symbol               | Parameter                                                   | Test Conditions                 | Min. | Тур. | Max.     | Unit     |

| VCO                  |                                                             | •                               | •    | •    | •        |          |

| R <sub>0(Min.)</sub> | Minimum Oscillator Resistor                                 | Pin 11                          | 6    |      |          | kΩ       |

| C <sub>0(Min.)</sub> | Minimum Oscillator Capacitor                                | Pin 10                          | 390  |      |          | pF       |

| F <sub>(Max.)</sub>  | Maximum Oscillator Frequency                                |                                 |      |      | 150      | kHz      |

| OUTPUTS              | SECTION                                                     |                                 |      |      |          |          |

| I6m                  | Maximum Input Peak Current                                  | Pin 6                           |      |      | 2        | mA       |

| HOI1<br>HOI2         | Horizontal Drive Output Maximum Current<br>Pin 20<br>Pin 21 | Sourced current<br>Sunk current |      |      | 20<br>20 | mA<br>mA |

# **Electrical Characteristics** ( $V_{CC} = 12V, T_{amb} = 25^{\circ}C$ )

| Symbol             | Parameter                                  | Test Conditions | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------------------|-----------------|------|------|------|------|

| SUPPLY A           | ND REFERENCE VOLTAGES                      | •               |      | •    | •    | •    |

| Vcc                | Supply Voltage                             | Pin 18          | 10.8 | 12   | 13.2 | V    |

| $V_{DD}$           | Supply Voltage                             | Pin 39          | 4.5  | 5    | 5.5  | V    |

| Icc                | Supply Current                             | Pin 18          |      | 50   |      | mA   |

| $I_{DD}$           | Supply Current                             | Pin 39          |      | 5    |      | mA   |

| V <sub>REF-H</sub> | Horizontal Reference Voltage               | Pin 5, I = 5mA  | 7.4  | 8    | 8.6  | V    |

| $V_{REF-V}$        | Vertical Reference Voltage                 | Pin 5, I = 5mA  | 7.4  | 8    | 8.6  | V    |

| I <sub>REF-H</sub> | Max. Sourced Current on V <sub>REF-H</sub> | Pin 5           |      |      | 5    | mA   |

| I <sub>REF-V</sub> | Max. Sourced Current on V <sub>REF-V</sub> | Pin 26          |      |      | 5    | mA   |

**HORIZONTAL SECTION** (continued) **Electrical Characteristics** ( $V_{CC} = 12V, T_{amb} = 25^{\circ}C$ ) (continued)

| Symbol                                         | Parameter                                                                                                 | Test Conditions                                                                                         | Min. | Тур.                          | Max. | Unit        |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-------------------------------|------|-------------|

| 1st PLL SE                                     | CTION                                                                                                     |                                                                                                         |      |                               |      |             |

| HpolT                                          | Polarity Integration Delay                                                                                |                                                                                                         | 0.75 |                               |      | ms          |

| V <sub>vco</sub>                               | VCO Control Voltage (Pin12)                                                                               | $V_{REF-H} = 8V$ $f_0$ $f_H(Max.)$                                                                      |      | V <sub>REF-H</sub> / 6<br>6.2 | 6    | V           |

| Vcog                                           | VCO Gain (Pin 12)                                                                                         | $R_0 = 6.49k\Omega$ , $C_0 = 820pF$ , $dF/dV = 1/11R_0C_0$                                              |      | 17                            |      | kHz/V       |

| Hph                                            | Horizontal Phase Adjustment                                                                               | % of Horizontal Period                                                                                  |      | ±10                           |      | %           |

| Hphmin<br>Hphtyp<br>Hphmax                     | Horizontal Phase Decoupling Output<br>Minimum Value<br>Typical Value<br>Maximum Value                     | Sub-Address 01, Pin 14<br>Byte x1111111<br>Byte x1000000<br>Byte x0000000                               |      | 2.8<br>3.4<br>4.0             |      | ><br>><br>> |

| f <sub>0</sub>                                 | Free Running Frequency                                                                                    | $R_0 = 6.49k\Omega$ , $C_0 = 820pF$ , $f_0 = 0.97/8R_0C_0$                                              |      | 22.3                          |      | kHz         |

| dF0/dT                                         | Free Running Frequency Thermal Drift (No drift on external components)                                    |                                                                                                         |      | -150                          |      | ppm/C       |

| f <sub>0</sub> (Min.)<br>f <sub>0</sub> (Max.) | Free Running Frequency Adjustment<br>Minimum Value<br>Maximum Value                                       | Sub-Address 02<br>Byte xxx11111<br>Byte xxx00000                                                        |      | 0.8<br>1.3                    |      | F0<br>F0    |

| CR                                             | PLL1 Capture Range                                                                                        | $R_0 = 6.49k\Omega$ , $C_0 = 820pF$ ,<br>from $f_0+0.5kHz$ to $4.5F_0$<br>$f_H(Min.)$<br>$f_H(Max.)$    | 100  |                               | 23.5 | kHz<br>kHz  |

| PLLinh                                         | PLL1 Inhibition (Pin3)                                                                                    | Typ Threshold = 1.6V<br>PLL ON<br>PLL OFF                                                               | 2    |                               | 0.8  | > >         |

| SFF                                            | Safe Forced Frequency<br>SF1 Byte 11xxxxxx<br>SF2 Byte 10xxxxxx                                           | Sub-Address 02                                                                                          |      | 2F0<br>3F0                    |      |             |

| FC1<br>FC2                                     | VCO Sawtooth Level<br>High FC1=(4.V <sub>REF-H</sub> )/5<br>Low FC2=(V <sub>REF-H</sub> )/5               | Pin 9 To filter<br>Pin 8 To filter                                                                      |      | 6.4<br>1.6                    |      | V           |

| 2nd PLL SE                                     | ECTION AND HORIZONTAL OUTPUT SECT                                                                         | ON                                                                                                      |      |                               |      |             |

| FBth                                           | Flyback Input Threshold Voltage (Pin 6)                                                                   |                                                                                                         | 0.65 | 0.75                          |      | V           |

| Hjit                                           | Horizontal Jitter (see Pins 8-9 filtering)                                                                |                                                                                                         |      | TBD                           |      | ppm         |

| HDmin<br>HDmax                                 | Horizontal Drive Output Duty-Cycle<br>(Pin 20 or 21) (see Note 1)<br>Low Level<br>High Level (see Note 2) | Sub-Address 00  Byte xxx11111  Byte xxx00000                                                            |      | 30<br>60                      |      | %<br>%      |

| XRAYth                                         | X-RAY Protection Input Threshold Voltage                                                                  | Pin 15                                                                                                  |      | 8                             |      | V           |

| Vphi2                                          | Internal Clamping Levels on 2nd PLL Loop Filter (Pin 4)                                                   | Low Level<br>High Level                                                                                 |      | 1.6<br>4.0                    |      | V           |

| VSCinh                                         | Threshold Voltage To Stop H-Out,V-Out when $V_{CC}$ < VSCinh                                              | Pin 18                                                                                                  |      | 7.5                           |      | V           |

| IHblk                                          | Maximum Horizontal Blanking Output<br>Current                                                             | I <sub>22</sub>                                                                                         |      |                               | 10   | mA          |

| VHblk                                          | Horizontal Blanking Output Low Level (Blanking ON)                                                        | $V_{22}$ with $I_{22} = 10$ mA                                                                          |      | 0.25                          | 0.5  | V           |

| HDvd<br>HDem                                   | Horizontal Drive Output Low Level (Pin 20 to GND) High Level (Pin 21 to $V_{CC}$ =12V)                    | V <sub>21</sub> -V <sub>20</sub> , I <sub>OUT</sub> = 20mA<br>V <sub>20</sub> , I <sub>OUT</sub> = 20mA | 9.5  | 1.1<br>10                     | 1.7  | V           |

Notes: 1. Duty Cycle is the ratio of power transistor OFF time to period. Power transistor is OFF when output transistor is OFF.

2. Initial Condition for Safe Operation Start Up (Max. duty cycle).

$\begin{array}{l} \textbf{HORIZONTAL SECTION} \ (continued) \\ \textbf{Electrical Characteristics} \ (V_{CC} = 12V, T_{amb} = 25^{o}C) \ (continued) \end{array}$

|                    | · · · · · ·                                                                                        | , , ,                                                                            |      |                   |      |                                                       |

|--------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|-------------------|------|-------------------------------------------------------|

| Symbol             | Parameter                                                                                          | Test Conditions                                                                  | Min. | Тур.              | Max. | Unit                                                  |

| HORIZONT           | AL DYNAMIC FOCUS SECTION                                                                           |                                                                                  |      |                   |      |                                                       |

| HDFst              | Horizontal Dynamic Focus Sawtooth<br>Minimum Level<br>Maximum Level                                | HfocusCap = $C_0$ = 820pF,<br>$f_H$ = 90kHz, Pin 16                              |      | 2<br>4.7          |      | V                                                     |

| HDFdis             | Horizontal Dynamic Focus Sawtooth Discharge Width                                                  | Driven by Hfly                                                                   |      | 500               |      | ns                                                    |

| HDFDC              | Bottom DC Output Level                                                                             | $R_{LOAD} = 10k\Omega$ , Pin 17                                                  |      | 2                 |      | V                                                     |

| TDHDF              | DC Output Voltage Thermal Drift                                                                    |                                                                                  |      | 200               |      | ppm/C                                                 |

| HDFamp             | Horizontal Dynamic Focus Amplitude<br>Min Byte xxx11111<br>Typ Byte xxx10000<br>Max Byte xxx00000  | Sub-Address 03, Pin 17, f <sub>H</sub> = 90kHz, Keystone Typ                     |      | 1<br>1.5<br>3     |      | V <sub>PP</sub><br>V <sub>PP</sub><br>V <sub>PP</sub> |

| HDFKeyst           | Horizontal Dynamic Focus Keystone  Min A/B Byte xxx11111  Typ Byte xxx10000  Max A/B Byte xxx00000 | Sub-Address 04,<br>f <sub>H</sub> = 90kHz, Typ Amp<br>B/A<br>A/B<br>A/B          |      | 3.5<br>1.0<br>3.5 |      |                                                       |

| MOIRE OUT          | <b>TPUT</b>                                                                                        |                                                                                  |      |                   |      |                                                       |

| R <sub>MOIRE</sub> | Minimum Output Resistor                                                                            | Pin 2                                                                            | 2    |                   |      | kΩ                                                    |

| V <sub>MOIRE</sub> | Output Voltage (moire off),<br>Subaddress 0F                                                       | Pin 2, $R_{MOIRE} = 2k\Omega$<br>Byte 0xx00000<br>Byte 0xx10000<br>Byte 0xx11111 |      | 0.2<br>1.1<br>2.0 |      | V<br>V                                                |

8/30

#### **VERTICAL SECTION Operating Conditions**

| Symbol            | Parameter                                              | Test Conditions | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------------------------------|-----------------|------|------|------|------|

| OUTPUTS SECTION   |                                                        |                 |      |      |      |      |

| VEWM              | Maximum EW Output Voltage                              | Pin 31          |      |      | 6.5  | V    |

| VEWm              | Minimum EW Output Voltage                              | Pin 31          | 1.8  |      |      | V    |

| VDFm              | Minimum Vertical Dynamic Focus Output Voltage          | Pin 32          | 1.8  |      |      | ٧    |

| R <sub>LOAD</sub> | Minimum Load for less than 1% Vertical Amplitude Drift | Pin 25          | 65   |      |      | МΩ   |

#### Electrical Characteristics (V<sub>CC</sub> = 12V, T<sub>amb</sub> = 25°C)

| Symbol            | Parameter                                                                                    | Test Conditions                                                                    | Min. | Тур.              | Max. | Unit        |

|-------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|-------------------|------|-------------|

| VERTICAL          | RAMP SECTION                                                                                 |                                                                                    | •    | •                 | •    | •           |

| VRB               | Voltage at Ramp Bottom Point                                                                 | V <sub>REF-V</sub> =8V, Pin 27                                                     |      | 2                 |      | V           |

| VRT               | Voltage at Ramp Top Point (with Sync) V <sub>REF-V</sub>                                     | Pin 27                                                                             |      | 5                 |      | V           |

| VRTF              | Voltage at Ramp Top Point (without Sync)                                                     | Pin 27                                                                             |      | VRT-<br>0.1       |      | V           |

| VSTD              | Vertical Sawtooth Discharge Time Duration (Pin 27)                                           | With 150nF Cap                                                                     |      | 80                |      | μs          |

| VFRF              | Vertical Free Running Frequency (see Notes 3 & 4)                                            | C <sub>OSC (Pin 27)</sub> = 150nF<br>Measured on Pin27,                            |      | 100               |      | Hz          |

| ASFR              | AUTO-SYNC Frequency                                                                          | C <sub>27</sub> = 150nF ±5%<br>See Note 5                                          | 50   |                   | 165  | Hz          |

| RAFD              | Ramp Amplitude Drift Versus Frequency at Maximum Vertical Amplitude                          | C <sub>27</sub> = 150nF<br>50Hz < f and f < 165Hz                                  |      | 200               | TBD  | ppm/Hz      |

| Rlin              | Ramp Linearity on Pin 27 (see Notes 3 & 4)                                                   | 2.5 < V <sub>27</sub> and V <sub>27</sub> < 4.5V                                   |      | 0.5               |      | %           |

| Vpos              | Vertical Position Adjustment Voltage (Pin28)                                                 | Sub Address 06 Byte x0000000 Byte x1000000 Byte x1111111                           | 3.65 | 3.2<br>3.5<br>3.8 | 3.3  | V<br>V<br>V |

| I <sub>VPOS</sub> | Max Current on Vertical Position Output                                                      | Pin 28                                                                             |      | ±2                |      | mA          |

| VOR               | Vertical Output Voltage<br>(peak-to-peak on Pin 29)                                          | Sub Address 05 Byte x0000000 Byte x1000000 Byte x1111111                           | 3.5  | 2.25<br>3<br>3.75 | 2.5  | V<br>V<br>V |

| VoutDC            | DC Voltage on Vertical Output                                                                | See Note 6, Pin 29                                                                 |      | 3.5               |      | V           |

| VOI               | Vertical Output Maximum Current (Pin29)                                                      |                                                                                    |      | ±5                |      | mA          |

| dVS               | Max Vertical S-Correction Amplitude<br>x0xxxxxx inhibits S-CORR<br>x1111111 gives max S-CORR | Subaddress 07 $\Delta$ V/V <sub>PP</sub> at T/4 $\Delta$ V/V <sub>PP</sub> at 3T/4 |      | -4<br>+4          |      | %<br>%      |

| Ccorr             | Vertical C-Corr Amplitude<br>x0xxxxxx inhibits C-CORR                                        | SubAddress 08 Byte x1000000 Byte x1100000 Byte x1111111                            |      | -3<br>0<br>3      |      | %<br>%<br>% |

| VflyTh            | Vertical Flyback Threshold                                                                   | Pin 30                                                                             |      | 1                 |      | V           |

| Vflylnh           | Inhibition of Vertical Flyback Input                                                         | See Note 7, Pin 30                                                                 | 7.5  |                   |      | V           |

Notes: 3. With Register 07 at Byte x0xxxxxx (Vertical S-Correction Control) then the S correction is inhibited, consequently the sawtooth has a linear shape.

4. With Register 08 at Byte x0xxxxxx (Vertical C - Correction Control) then the C correction is inhibited, consequently the sawtooth

has a linear shape.

<sup>nas a linear snape.

It is the frequency range for which the VERTICAL OSCILLATOR will automatically synchronize, using a single capacitor value on Pin 27 and with a constant ramp amplitude.

Voutde = (7/16).VREF-V. Typically 3.5V for Vertical reference voltage typical value (8V).

When Pin 30 (VREF-V) - 0.5V, Vfly input is inhibited and vertical blanking on vertical blanking output is replaced by vertical sawtooth discharge time.</sup>

**VERTICAL SECTION** (continued) **Electrical Characteristics**  $(V_{CC} = 12V, T_{amb} = 25^{\circ}C)$  (continued)

| Symbol           | Parameter                                                                                                                                                                                             | Test Conditions                                                                       | Min. | Тур.               | Max. | Unit                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|--------------------|------|------------------------------------|

| EAST/WEST        | FUNCTION                                                                                                                                                                                              |                                                                                       |      |                    |      |                                    |

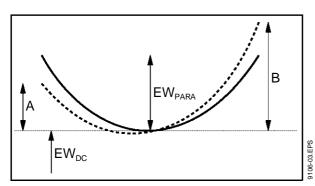

| $EW_DC$          | DC Output Voltage with Typ Vpos,Keystone, Corner and Corner Balance Inhibited                                                                                                                         | Pin 31, see Figure 1                                                                  |      | 2.5                |      | V                                  |

| $TDEW_DC$        | DC Output Voltage Thermal Drift                                                                                                                                                                       | See Note 8                                                                            |      | 100                |      | ppm/C                              |

| EWpara           | Parabola Amplitude with Vamp Max, V-Pos Typ, Keystone, Corner and Corner Balance Inhibited                                                                                                            | Subaddress 09 Byte 1x111111 Byte 1x100000 Byte 1x000000                               |      | 2.6<br>1.4<br>0    |      | V<br>V<br>V                        |

| EWtrack          | Parabola Amplitude Function of V-AMP Control (tracking between V-AMP and E/W) with Typ Vpos, Keystone, Corner and Corner Balance Inhibited, EW Typ Amplitude (see Note 9)                             | Subaddress 05 Byte 10000000 Byte 11000000 Byte 11111111                               |      | 0.45<br>0.8<br>1.4 |      | V<br>V<br>V                        |

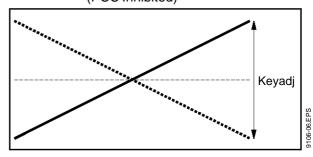

| KeyAdj           | Keystone Adjustment Capability with Typ Vpos,<br>Corner and Corner Balance Inhibited, EW Inhibited<br>and Vertical Amplitude Max<br>(see Note 9 and Figure 4)                                         | Subaddress 0A<br>Byte 10000000<br>Byte 11111111                                       |      | 1                  |      | V <sub>PP</sub><br>V <sub>PP</sub> |

| KeyTrack         | Intrinsic Keystone Function of V-POS Control (tracking between V-POS and EW) with Corner and Corner Balance Inhibited, EW Max Amplitude and Vertical Amplitude Max (see Note 9)  A/B Ratio  B/A Ratio | Subaddress 06  Byte x0000000  Byte x1111111                                           |      | 0.5<br>0.5         |      |                                    |

| Corner<br>Max    | Max Corner Correction Amplitude with Vamp Max, V-POS Typ, EWamp, Keystone and Corner Balance Inhibited (see Note 9)                                                                                   | Subaddress 0B<br>\( \Delta \text{EWout at T/6, 5T/6} \)  Byte x1111111  Byte x1000000 |      | +0.2<br>-0.2       |      | V                                  |

| Corner<br>BalMax | Max Corner Balance Correction Amplitude with Vamp Max, V-POS Typ, EWamp, Keystone and Corner Inhibited                                                                                                | Byte 01111111<br>ΔEWout at T/4<br>ΔEWout at 3T/4                                      |      | +0.2<br>-0.2       |      | V<br>V                             |

|                  | Subaddress 0C (see Note 9)                                                                                                                                                                            | Byte 01000000<br>ΔEWout at T/4<br>ΔEWout at 3T/4                                      |      | -0.2<br>+0.2       |      | V                                  |

| NTERNAL H        | ORIZONTAL DYNAMIC PHASE CONTROL FUNCT                                                                                                                                                                 | ION                                                                                   |      |                    |      |                                    |

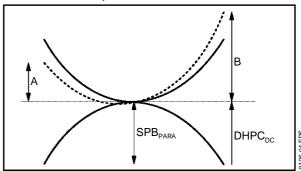

| SPBpara          | Side Pin Balance Parabola Amplitude (Figure 2) with Vamp Max, V-POS Typ and Parallelogram Inhibited (see Notes 9 & 10)                                                                                | Subaddress 0D<br>Byte x1111111<br>Byte x1000000                                       |      | +2.8<br>-2.8       |      | %TH<br>%TH                         |

| SPBtrack         | Side Pin Balance Parabola Amplitude function of Vamp Control (tracking between Vamp and SPB) with SPB Max, V-POS Typ and Parallelogram Inhibited (see Notes 9 & 10)                                   | Subaddress 05 Byte 10000000 Byte 11000000 Byte 11111111                               |      | 1.0<br>1.8<br>2.8  |      | %TH<br>%TH<br>%TH                  |

| ParAdj           | Parallelogram Adjustment Capability with Vamp Max, V-POS Typ and SPB Inhibited (see Notes 9, 10 & 11)                                                                                                 | Subaddress 0E<br>Byte x1111111<br>Byte x1000000                                       |      | +2.8<br>-2.8       |      | %TH<br>%TH                         |

| Partrack         | Intrinsic Parallelogram Function of Vpos Control (tracking between V-Pos and DHPC) with Vamp Max, SPB Max and Parallelogram Inhibited (see Notes 9 & 10)  A/B Ratio  B/A Ratio                        | Subaddress 06  Byte x0000000  Byte x1111111                                           |      | 0.5<br>0.5         |      |                                    |

Notes: 8. These parameters are not tested on each unit. They are measured during our internal qualification 9. Refers to Notes 3 & 4 from last section.

10.TH is the Horizontal PLL Period Duration.

11.Figure 2 is representing effect of dynamic horizontal phase control.

## **VERTICAL SECTION (continued)**

Electrical Characteristics (V<sub>CC</sub> = 12V, T<sub>amb</sub> = 25°C) (continued)

| Symbol                          | Parameter                                                                                                       | Test Conditions                                                  | Min. | Тур.              | Max. | Unit  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|-------------------|------|-------|--|--|--|

| VERTICAL DYNAMIC FOCUS FUNCTION |                                                                                                                 |                                                                  |      |                   |      |       |  |  |  |

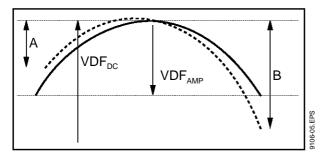

| VDF <sub>DC</sub>               | DC Output Voltage with V-Pos Typ                                                                                | See Figure 3                                                     |      | 6                 |      | V     |  |  |  |

| TDVDF <sub>DC</sub>             | DC Output Voltage Thermal Drift                                                                                 | See Note 12                                                      |      | 100               |      | ppm/C |  |  |  |

| VDFAMP                          | Parabola Amplitude Function of Vamp (tracking between Vamp and VDF) with V-Pos Typ (see Figure 3) (see Note 13) | Subaddress 05<br>Byte 10000000<br>Byte 11000000<br>Byte 11111111 |      | 0.9<br>1.6<br>2.5 |      | >>>   |  |  |  |

| VDFKEY                          | Parabola Assymetry Function of VPos Control (tracking between V-Pos and VDF) with Vamp Max. (see Note 13)       | Subaddress 06<br>Byte x0000000<br>Byte x1111111                  |      | 0.5<br>0.5        |      |       |  |  |  |

Notes: 12. Parameter not tested on each unit but measured during our internal qualification procedure including batches coming from corners of our process and also temperature characterization

13. S and C corrections are inhibited so the output sawtooth has a linear shape.

Figure 1: E/W Output

Figure 3: Vertical Dynamic Focus Function

Figure 2: Dynamic Horizontal Phase Control Output

Figure 4: Keystone Effect on E/W Output (PCC Inhibited)

### TYPICAL VERTICAL OUTPUT WAVEFORMS

| Function                              | Sub<br>Address | Pin | Byte                             | Specification                                                            | Picture Image |

|---------------------------------------|----------------|-----|----------------------------------|--------------------------------------------------------------------------|---------------|

| Vertical Size                         | 05             | 29  | 10000000                         | 2.25V<br>3.75V                                                           |               |

| Vertical<br>Position<br>DC<br>Control | 06             | 28  | x0000000<br>x1000000<br>x1111111 | 3.2V<br>3.5V<br>3.8V                                                     | <u>†</u> ↓    |

| Vertical<br>S<br>Linearity            | 07             | 29  | x0xxxxxx<br>Inhibited            | $V_{pp}$ $\frac{\Delta V}{V_{pp}} = 4\%$                                 |               |

| Vertical<br>C<br>Linearity            | 08             | 29  | x1000000<br>x1111111             | $V_{pp}$ $\frac{\Delta V}{V_{pp}} = 3\%$ $\frac{\Delta V}{V_{pp}} = 3\%$ | <b>*</b>      |

#### **GEOMETRY OUTPUT WAVEFORMS**

| Function                       | Sub<br>Address | Pin      | Byte                                                | Specification                   | Picture Image |

|--------------------------------|----------------|----------|-----------------------------------------------------|---------------------------------|---------------|

| Trapezoid<br>Control           | 0A             | 31       | EWamp<br>Typ.<br>10000000                           | 2.75V<br>2.75V<br>2.5V<br>3.75V |               |

| Pin Cushion<br>Control         | 09             | 31       | Keystone<br>Inhibited<br>1x000000<br>1x111111       | 2.5V — OV 2.5V                  | <u> </u>      |

| Parrallelogram<br>Control      | 0E             | Internal | SPB<br>Inhibited<br>x1000000<br>x1111111            | 3.7V 2.8% TH                    |               |

| Side Pin<br>Balance<br>Control | 0D             | Internal | Parallelogram<br>Inhibited<br>X10000000<br>x1111111 | 3.7V 2.8% TH 2.8% TH            |               |

| Vertical<br>Dynamic<br>Focus   |                | 32       |                                                     | 6V 2.5V                         |               |

### **GEOMETRY OUTPUT WAVEFORMS** (continued)

| Function       | Sub<br>Address | Pin | Byte                      | Specification                | Picture Image |

|----------------|----------------|-----|---------------------------|------------------------------|---------------|

| Corner Control | ОВ             | 31  | EWamp<br>Typ.<br>x1111111 | Corner effect without Corner |               |

| Comer control  | OB             | 31  | 01000000                  | Corner                       |               |

| Corner Balance | 0C             | 31  | EWamp<br>Typ.<br>10000000 | Corner                       |               |

| Control        | 00             | 31  | 11111111                  | Corner                       |               |

**Note:** The specification of output voltage is indicated on 3.75V<sub>PP</sub> vertical sawtooth output condition. The output voltage depends on vertical sawtooth output voltage.

#### I<sup>2</sup>C BUS ADDRESS TABLE

#### **Sub Address Definition**

Slave Address (8C): Write Mode

|   | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|---|----|----|----|----|----|----|----|----|

| 0 | Х  | Х  | Х  | Х  | 0  | 0  | 0  | 0  |

| 1 | Х  | Х  | Х  | Х  | 0  | 0  | 0  | 1  |

| 2 | Х  | Х  | Х  | Х  | 0  | 0  | 1  | 0  |

| 3 | Х  | Х  | Х  | Х  | 0  | 0  | 1  | 1  |

| 4 | Х  | Х  | Х  | Х  | 0  | 1  | 0  | 0  |

| 5 | Х  | Х  | Х  | Х  | 0  | 1  | 0  | 1  |

| 6 | Х  | Х  | Х  | Х  | 0  | 1  | 1  | 0  |

| 7 | Х  | Х  | Х  | Х  | 0  | 1  | 1  | 1  |

| 8 | Х  | Х  | Х  | Х  | 1  | 0  | 0  | 0  |

| 9 | Х  | Х  | Х  | Х  | 1  | 0  | 0  | 1  |

| Α | Х  | Х  | Х  | Х  | 1  | 0  | 1  | 0  |

| В | Х  | Х  | Х  | Х  | 1  | 0  | 1  | 1  |

| С | Х  | Х  | Х  | Х  | 1  | 1  | 0  | 0  |

| D | Х  | Х  | Х  | Х  | 1  | 1  | 0  | 1  |

| Е | Х  | Х  | Х  | Х  | 1  | 1  | 1  | 0  |

| F | Х  | Х  | Х  | Х  | 1  | 1  | 1  | 1  |

Horizontal Drive Selection / Horizontal Duty Cycle

Horizontal Position

Safety Frequency / Free Running Frequency

Synchro Priority / Horizontal Focus Amplitude

Refresh / Horizontal Focus Keystone

Vertical Ramp Amplitude

Vertical Position Adjustment

S Correction

C Correction

E/W Amplitude

E/W Keystone

Cbow Corner

#### Slave Address (8D): Read Mode

|   | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|---|----|----|----|----|----|----|----|----|

| 0 | Х  | Х  | Х  | Х  | 0  | 0  | 0  | 0  |

Synchro and Polarity Detection

Moire Control Amplitude

Spin Corner Side Pin Balance Parallelogram

# $I^2$ C BUS ADDRESS TABLE (continued)

Table: Register Map

|      | D8                   | D7                       | D6                                 | D5     | D4               | D3               | D2      | D1  |

|------|----------------------|--------------------------|------------------------------------|--------|------------------|------------------|---------|-----|

| WRIT | E MODE               |                          |                                    |        |                  |                  |         |     |

|      | Blk Sel              | HDrive                   |                                    |        | Hoi              | rizontal Duty C  | ycle    |     |

| 00   | 1, Blk<br>[0]        | 0, off<br>[1], on        |                                    | [0]    | [0]              | [0]              | [0]     | [0] |

|      | Xray                 |                          |                                    | Horizo | ontal Phase Adj  | ustment          | l       |     |

| 01   | 1, reset<br>[0]      | [1]                      | [0]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      | Safety F             | requency                 | Free Ru                            |        | Running Frequ    | unning Frequency |         |     |

| 02   | 1, on<br>[0], off    | 1, F0 x 2<br>[0], F0 x 3 |                                    | [0]    | [0]              | [0]              | [0]     | [0] |

|      |                      | Priority                 |                                    |        | Horizo           | ntal Focus Am    | plitude |     |

| 03   | 0, Vextr<br>[1], Vin | 0, S/G<br>[1], H/V       |                                    | [1]    | [0]              | [0]              | [0]     | [0] |

| 04   | Detect<br>Refresh    |                          |                                    |        | Horizo           | ontal Focus Ke   | ystone  |     |

| 04   | [0], off             |                          |                                    | [1]    | [0]              | [0]              | [0]     | [0] |

| 05   | Vramp                |                          | Vertical Ramp Amplitude Adjustment |        |                  |                  |         |     |

| 05   | 0, off<br>[1], on    | [1]                      | [0]                                | [0]    | [0]              | [0]              | [0]     | [0] |

| 06   |                      |                          |                                    | Vertic | al Position Adju | ıstment          | •       |     |

|      |                      | [1]                      | [0]                                | [0]    | [0]              | [0]              | [0]     | [0] |

| 07   |                      | S Select<br>1, on        |                                    |        | S Cor            | rection          | T       |     |

| "    |                      | [0]                      | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

| 00   |                      | C Select                 |                                    |        | C Cor            | rection          |         | _   |

| 80   |                      | 1, on<br>[0]             | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      | EW Sel               |                          |                                    |        |                  | _                |         |     |

| 09   | 0, off<br>[1]        |                          | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      | EW Key               |                          |                                    | E      | ast/West Keysto  | one              |         |     |

| 0A   | 0, off [1]           | [1]                      | [0]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      | Test H               | Cbow Sel                 |                                    | ·      | Cbow             | Corner           | ı       |     |

| 0B   | 1, on<br>[0], off    | 1, on<br>[0]             | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      | Test V               | Spin Sel                 |                                    |        | Spin (           | Corner           |         |     |

| OC   | 1, on<br>[0], off    | 1, on<br>[0]             | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      |                      | SPB Sel                  |                                    | ·      | Side Pin         | Balance          | ı       |     |

| 0D   |                      | 0, off<br>[1]            | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

|      |                      | Parallelo                |                                    | •      | Paralle          | elogram          | •       |     |

| 0E   |                      | 0, off<br>[1]            | [1]                                | [0]    | [0]              | [0]              | [0]     | [0] |

| 2-   | Moire                |                          |                                    |        |                  | Moire Control    |         | _   |

| 0F   | 1, on<br>[0], off    |                          |                                    | [0]    | [0]              | [0]              | [0]     | [0] |

READ MODE

|   |    | Hlock            | Vlock            | Xray              | Polarity [            | Detection              | Sy                      | nchro Detection      | on                   |

|---|----|------------------|------------------|-------------------|-----------------------|------------------------|-------------------------|----------------------|----------------------|

| 0 | 00 | 0, on<br>[1], no | 0, on<br>[1], no | 1, on<br>[0], off | H/V pol [1], negative | V pol<br>[1], negative | Vext det<br>[0], no det | H det<br>[0], no det | V det<br>[0], no det |

[] initial value

#### **OPERATING DESCRIPTION**

# I - GENERAL CONSIDERATIONS I.1 - Power Supply

The typical values of the power supply voltages  $V_{CC}$  and  $V_{DD}$  are respectively 12V and 5V. Perfect operation is obtained if  $V_{CC}$  and  $V_{DD}$  are maintened in the limits: 10.8 to 13.2V and 4.5 to 5.5V.

In order to avoid erratic operation of the circuit during transient phase of  $V_{CC}$  switching on, or switching off, the value of  $V_{CC}$  is monitored and the outputs of the circuit are inhibited if  $V_{CC}$  is less than 7.5V typically.

In the same manner,  $V_{DD}$  is monitored and internal set-up is made until  $V_{DD}$  reaches 4V (see  $I^2C$  Control Table for power on reset).

In order to have a very good power supply rejection, the circuit is internally powered by several internal voltage references (the unique typical value of which is 8V). Two of these voltage references are externally accessible, one for the vertical part and one for the horizontal one. If needed, these voltage references can be used (until load is less than 5mA). Furthermore it is necessary to filter the a.m. voltage references by the use of external capacitor connected to ground, in order to minimize the noise and consequently the "jitter" on vertical and horizontal output signals.

#### I.2 - I<sup>2</sup>C Control

TDA9106 belongs to the I<sup>2</sup>C controlled device family, instead of being controlled by DC voltages on dedicated control pins, each adjustment can be realized through the I<sup>2</sup>C Interface.

The I<sup>2</sup>C bus is a serial bus with a clock and a data input. The general function and the bus protocol are specified in the Philips-bus data sheets.

The interface (Data and Clock) is TTL-level compatible. The internal threshold level of the input comparator is 2.2V (when V<sub>DD</sub> is 5V). Spikes of up to 50ns are filtered by an integrator and maximum clock speed is limited to 400kHz.

The data line (SDA) can be used in a bidirectional way that means in read-mode the IC clocks out a reply information (1 byte) to the micro-processor.

The bus protocol prescribes always a full-byte transmission. The first byte after the start condition is used to transmit the IC-address(7 bits-8C) and the read/write bit (0 write - 1 read).

#### I.3 - Write Mode

In write mode the second byte sent contains the subaddress of the selected function to adjust (or controls to affect) and the third byte the corresponding data byte. It is possible to send more than one data byte to the IC. If after the third byte no stop or start condition is detected, the circuit increments automatically the momentary subaddress in the subaddress counter by one (auto-increment mode). So it is possible to transmit immediately the next data bytes without sending the IC address or subaddress. It can be useful so as to reinitialize the whole controls very quickly (flash manner). This procedure can be finished by a stop condition.

The circuit has 16 adjustment capabilities: 3 for Horizontal part, 4 for Vertical one, 2 for E/W correction, 2 for original Corner correction, 2 for the Dynamic Horizontal phase control, 1 for Moire option and 2 for Horizontal Dynamic Focus.

20 bits are also dedicated to several controls (ON/OFF, Horizontal Safety Frequency, Synchro Priority, Detection Refresh and Xray reset).

#### I.4 - Read Mode

During read mode the second byte transmits the reply information.

The reply byte contains Horizontal and Vertical Lock/Unlock status, Xray activated or not, the Horizontal and Vertical polarity detection. It also contains Synchro detection status that is useful for  $\mu P$  to assign Sync priority.

A stop condition always stops all activities of the bus decoder and switches the data and the clock line (SDA and SCL) to high impedance.

See I<sup>2</sup>C Subaddress and control tables.

#### I.5 - Synchro Processor

The internal Sync Processor allows the TDA9106 to accept any kind of input synchro signals:

- separated Horizontal & Vertical TTL-compatible sync signals,

- composite Horizontal &Vertical TTL-compatible sync signals,

- sync on green or composite video signal.

#### I.6 - Sync Identification Status

TDA9106 is able to feed back to the MCU (thanks to I<sup>2</sup>C) the Sync input status (sync identification) so that the MCU can choose Sync priority through I<sup>2</sup>C.

As extracted Vertical sync pulse is performed when choice already occured and when 12V is supplied, we recommend to use the device as following: (that means that even in Power management mode the IC is able to inform MCU on detected synchro signals due to its 5V supply).

First, refresh Synchro detection by I<sup>2</sup>C. Then check the status of H/V det and Vdet by I<sup>2</sup>C read.

Sync priority choice should be:

Table 1: Sync Priority Choice

| H/V det | V det | Sync priority<br>Subaddress 03<br>D8 D7 |   | Comment              |

|---------|-------|-----------------------------------------|---|----------------------|

|         |       |                                         |   | Synchro type         |

| Yes     | Yes   | 1                                       | 1 | Separated H & V      |

| Yes     | No    | 0                                       | 1 | Composite TTL<br>H&V |

| No      | No    | 0                                       | 0 | Sync on Green        |

Of course, when choice is done, one can refresh the synchro detections and verify that extracted Vsync is present and that no synchro type change occured.

Synchro processor is also giving synchro polarity information.

#### I.7 - IC status

The IC can inform the MCU either the 1st Horizontal PLL or Vertical section are locked or not, and if Xray has been activated.

This last status permits to the MCU:

- reset the Xray internal latch decreasing the V<sub>CC</sub> supply

- directly reset throw the I<sup>2</sup>C interface.

#### I.8 - Synchro Inputs

Both H/HVin and Vsyncin inputs are TTL compatible trigger with Hysterisis to avoid erratic detection. It includes pull up resistor to V<sub>DD</sub>.

Vertical sync extractor is included for composite sync or composite video. Application engineer must adapt resistor R and capacitor C dedicated to its application.

Figure 5

Resistor R is fixed by detection threshold wanted:

R < (V<sub>THRESHOLD</sub> / I<sub>REF</sub>)

Then C is determined by maximum pulse width to detect (in general, vertical sync width):

RC > (max pulse width)

#### I.9 - Synchro Processor Outputs

Synchro processor delivers on 3 TTL-compatible CMOS outputs the following signals :

- Hout as follow:

| Sync Mode     | Hout Mode     | Hout Polarity |  |

|---------------|---------------|---------------|--|

| Separated     | Horizontal    | Same as Input |  |

| TTL Composite | TTL Composite | Same as Input |  |

| S/G           | Composite     | Negative      |  |

- Vsyncout is either vertical extracted pulse output or Vsyncin input. It keeps the input polarity.

- Hlockoutis the Horizontal 1st PLL status: 0V when locked. It permits MCU to adjust free running frequency and optimizes the IC performance.

106-34.EPS

#### **OPERATING DESCRIPTION** (continued)

#### **II - HORIZONTAL PART**

#### **II.1 - Internal Input Conditions**

Horizontal part is internally fed by synchro processor with a digital signal. corresponding to horizontal synchro pulses or to TTL composite input.

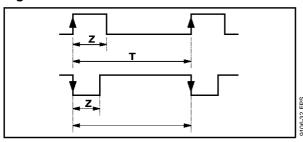

Concerning the duty cycle of the input signal, the following signals (positive or negative) may be applied to the circuit.

Using internal integration, both signals are recognized on condition that Z/T < 25%. Synchronization occurs on the leading edge of the internal sync signal. The minimum value of Z is  $0.7\mu s$ .

Figure 6

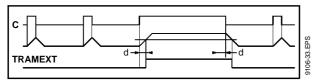

An other integration is able to extract vertical pulse of composite synchroif duty cycle is more than 25% (typically d = 35%).

Figure 7

The last feature performed is the equalizing pulses removing to avoid parasitic pulses on phase comparator input which is intolerent to wrong or missing pulse.

#### II.2 - PLL1

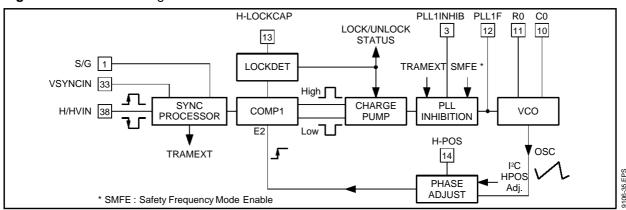

The PLL1 is composed of a phase comparator, an external filter and a voltage controlled oscillator (VCO).

The phase comparator is a "phase frequency" type designed in CMOS technology. This kind of phase detector avoids locking on false frequencies. It is followed by a "charge pump", composed of two current sources sunk and sourced (I = 1mA Typ. when locked, I = 140 $\mu$ A when unlocked). This difference between lock/unlock permits a smooth catching of horizontal frequency by PLL1. This effect is reinforced by an internal original slow down

system when PLL1 is locked avoiding Horizontal too fast frequency change.

The dynamic behaviour of the PLL is fixed by an external filter which integrates the current of the charge pump. A "CRC" filter is generally used (see Figure 8).

Figure 8

PLL1 is internally inhibited during extracted vertical sync (if any) to avoid taking in account missing pulses or wrong pulses on phase comparator. The inhibition results from the opening of a switch located between the charge pump and the filter (see Figure 9). For particular synchro type, MCU can drive Pin 3 to high level (TTL compatible input) to inhibit PLL1. It can also be used to avoid PLL1 locking on synchro inputs if a "dangerous" mode is detected by the MCU.

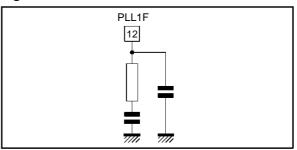

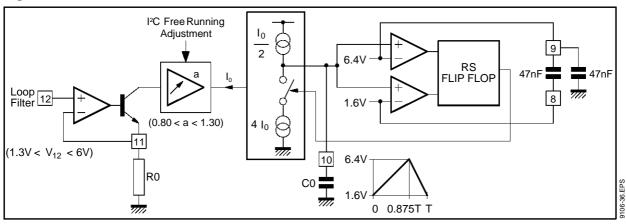

The VCO uses an external RC network. It delivers a linear sawtooth obtained by charge and discharge of the capacitor, by a current proportionnal to the current in the resistor. Typical thresholds of sawtooth are 1.6V and 6.4V. These two levels are accessible to be filtered as on Figure 10 to improve jitter.

The control voltage of the VCO is typically comprised between 1.33V and 6V (see Figure 10). The theorical frequency range of this VCO is in the ratio 1 to 4.5, the effective frequency range has to be smaller 1 to 4.2 due to clamp intervention on filter lowest value. To avoid spread of external components and the circuit itself, it is possible to adjust free running frequency through I<sup>2</sup>C. This adjustment can be made automatically on the manufacturing line without manual operation by using Hlock/unlock information. The adjustment range is 0.8 to 1.3 F0 (where 1.3 F0 is the free running frequency at power on reset).

The synchro frequency has to be always higher than the free running frequency. As an example for a synchro range from 24kHz to 100kHz, the suggested free running frequency is 23kHz.

Figure 9: PLL1 Block Diagram

Figure 10: Details of VCO

An other feature is the capability for MCU to force horizontal frequency through I<sup>2</sup>C to 2xF0 or 3xF0 (for burn in mode or safety requirement). In this case, inhibition switch is opened leaving PLL1 free but voltage on PLL1 filter is forced to 2.66V for 2xF0 or 4.0V for 3xF0.

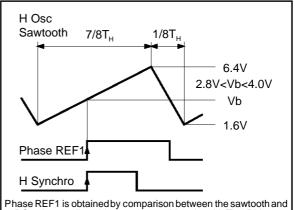

The PLL1 ensures the coincidence between the leading edge of the synchro signal and a phase reference obtained by comparison between the sawtooth of the VCO and an internal DC voltage  $I^2C$  adjustable between 2.8V and 4.0V (corresponding to  $\pm$  10%) (see Figure 11). This voltage has to be filtered on Pin 14 so as to optimize jitter.

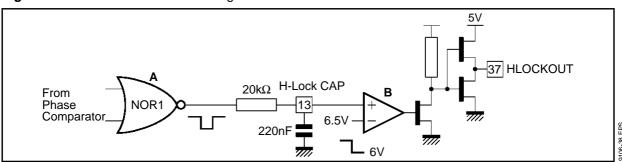

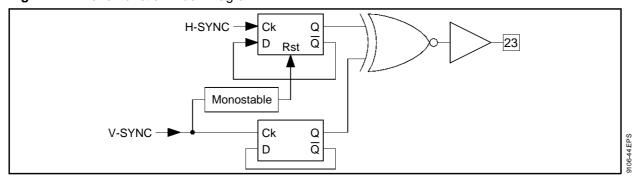

The TDA9106 also includes a Lock/Unlock identification block which senses in real time wheither PLL1 is locked on the incoming horizontal sync signal or not. The resulting information is available on Hlockout (see Synchro Processor). The block function is described in Figure 12.

The NOR1 gate is receiving the phase comparator output pulses (which also drive the charge pump). When PLL1 is locked, on point A there is a very small negative pulse (about 100ns) at each hori-

zontal cycle, so after RC filter, there is a high level on Pin 13 which forces Hlockout to low level. Hysterisis comparator detects locking when Pin 13 is reaching 6.5V and unlocking when Pin 13 is decreasing to 6.0V.

Figure 11: PLL1 Timing Diagram

a DC voltage adjustable between 2.8V and 4.0V. The PLL1 ensures the exact coincidence between the signals phase REF and HSYNS. A  $\pm$  T/10 phase adjustment is possible.

301 20 30

Figure 12: LOCK/UNLOCK Block Diagram

When PLL1 is unlocked, the 100ns negative pulse on A becomes much larger and consequently the average level on Pin 13 decreases. It forces Hlockout to go high.

The Pin 13 status is approximately the following:

- near 0V when there is no H-Sync

- between 0 and 4V with H-Sync frequency different from VCO

- between 4 to 8 V when VCO frequency reaches H-Sync one (but not already in phase)

- near 8V when PLL1 is locked.

It is important to notice that Pin 13 is not an output pin but is only used for filtering purpose (see Figure 12).

The lock/unlock information is also available throw I<sup>2</sup>C read.

#### II.3 - PLL2

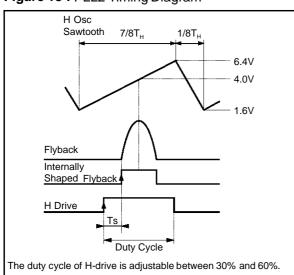

The PLL2 ensures a constant position of the shaped flyback signal in comparion with the saw-tooth of the VCO (Figure 13).

Figure 13: PLL2 Timing Diagram

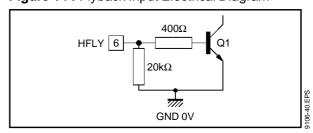

The phase comparator of PLL2 (phase type comparator) is followed by a charge pump with  $\pm$  0.5mA (typ.) output current.

The flyback input is composed of an NPN transistor. This input must be current driven. The maximum recommanded input current is 2mA (see Figure 14).

Figure 14: Flyback Input Electrical Diagram

The duty cycle is adjustable through  $I^2C$  from 30% to 60%. For Start Up safe operation, initial duty cycle (after Power on reset) is 60% so as to avoid too long conduction of BU transistor.

Maximum storage time is about 43.75% - (Tfly/2.TH). Typically, Tfly/TH is around 20% that means Ts max is around 33.75%.

#### **II.4 - Output Section**

The H-drive signal is transmitted to the output through a shaping block ensuring Ts and I<sup>2</sup>C adjustable duty cycle. In order to secure scanning power part operation, the output is inhibited in the following circumstances:

- V<sub>CC</sub> too low

- Xray protection activated

- During horizontal flyback

- I<sup>2</sup>C bit control (voluntary inhibition by MCU).

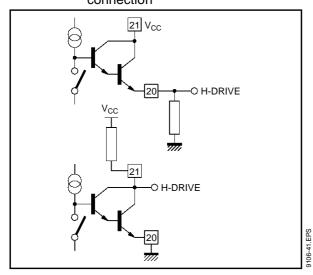

The output stage is composed of a NPN Darlington bipolar transistor. Both the collector and the emittor are accessible (see Figure 16).

The output Darlington is in off-state when the power scanning transistor is also in off-state.

Figure 16: Output stage simplified diagram, showing the two possibilities of connection

The maximum output current is 20mA, and the corresponding voltage drop of the output darlington is 1.1V typically.

It is evident that the power scanning transistor cannot be directly driven by the integrated circuit.

An interface has to be designed between the circuit and the power transistor which can be of bipolar or MOS type.

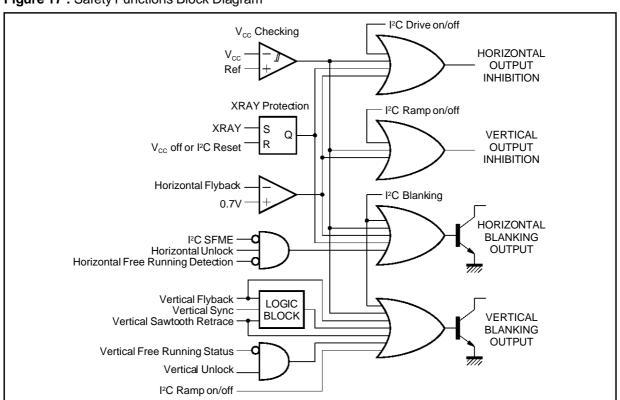

#### **II.5 - X-RAY Protection**

The activation of the X-Ray protection is obtained by application of a high level on the X-Ray input (Pin 15 > 8V). The consequencies of X-Ray protection are:

- inhibition of H-Drive output

- activation of horizontal blanking output.

- activation of vertical blanking output.

The reset of this protection is obtained either by V<sub>CC</sub> switch off or I<sup>2</sup>C reset by MCU (see Figure 17).

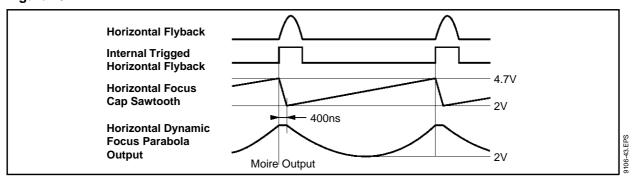

#### II.6 - Horizontal Dynamic Focus

TDA9106 delivers an horizontal parabola wave form on Pin 17. This parabola is performed from a sawtoothin phase with flyback pulse. This sawtooth is present on Pin 16 where the horizontal focus capacitor is the same as C0 to obtain a controlled amplitude (from 2 to 4.7V typically).

Symmetry (keystone) and amplitude are I<sup>2</sup>C adjustable (see Figure 18). This signal has to be connected to the CRT focusing grids and mixed with vertical dynamic focus.

Figure 17: Safety Functions Block Diagram

Figure 18

#### **II.7 - Moire Output**

The moire output is intented to correct a beat between horizontal video pixel period and actual CRT pixel width.

The moire signal is a combination of Horizontal and Vertical frequency signals.

To achieve a moire cancellation, it has to be connected to any point on the chassis controlling the horizontal position. We recommend to introduce this "Horizontal Controlled Jitter" on the relative ground

of PLL2 capacitor where this "controlled jitter" frequency type will directly affect the horizontal position. The amplitude of the signal is I<sup>2</sup>C adjustable.

### One point to notice is:

- in case H-Moire is not necessary in the application, H-Moire output (Pin 2) can be turned to as a 5 bits digital to analog converter output (0.3V to 2.2V V output voltage),

- in case of no use in application, this pin must be left high impedance(or resistor to ground).

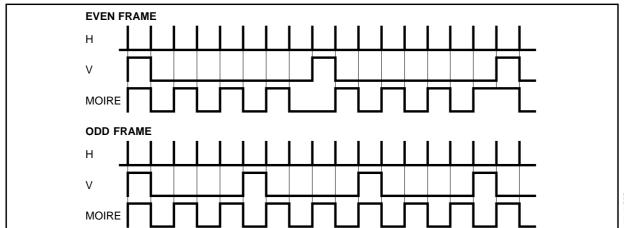

Figure 19: Moire Function Block Diagram

Figure 20: Moire Output Waveform

#### **III - VERTICAL PART**

#### **III.1 - Geometric Corrections**

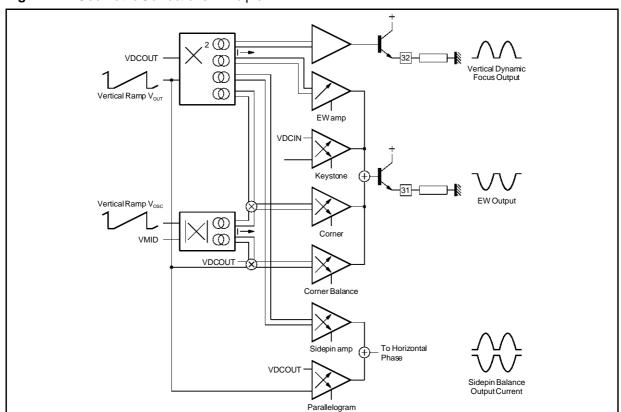

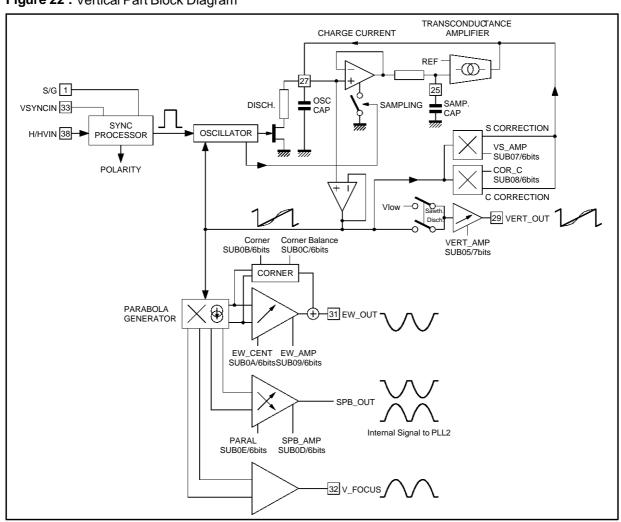

The principle is represented in Figure 21.

Starting from the vertical ramp, a parabola shaped current is generated for E/W correction, dynamic horizontal phase control correction, and vertical dynamic Focus correction.

The base of the parabola generator is an analog multiplier the output current of which is equal to:

$$\Delta I = k \cdot (V_{OUT} - V_{DCOUT})^2$$