# 10-, 12-, 14-Bit, 1200 MSPS DACS

# AD9734/AD9735/AD9736

#### **FEATURES**

Pin-compatible family Excellent dynamic performance

AD9736: SFDR = 82 dBc at f<sub>OUT</sub> = 30 MHz AD9736: SFDR = 69 dBc at f<sub>OUT</sub> = 130 MHz AD9736: IMD = 87 dBc at f<sub>OUT</sub> = 30 MHz AD9736: IMD = 82 dBc at f<sub>OUT</sub> = 130 MHz

LVDS data interface with on-chip 100  $\Omega$  terminations

Built-in self test

LVDS sampling integrity

LVDS-to-DAC data transfer integrity

Low power: 380 mW ( $I_{FS} = 20 \text{ mA}$ ;  $f_{OUT} = 330 \text{ MHz}$ )

1.8/3.3 V dual-supply operation

Adjustable analog output

8.66 mA to 31.66 mA (RL = 25  $\Omega$  to 50  $\Omega$ )

On-chip 1.2 V reference

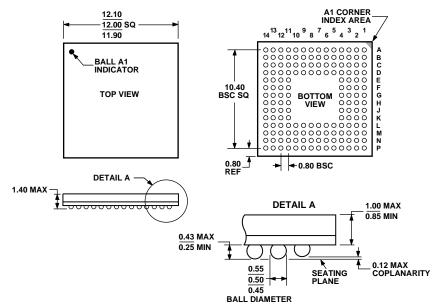

160-lead chip scale ball grid array (CSP\_BGA) package

#### **APPLICATIONS**

Broadband communications systems

Cellular infrastructure (digital predistortion)

Point-to-point wireless

CMTS/VOD

Instrumentation, automatic test equipment Radar, avionics

#### PRODUCT DESCRIPTION

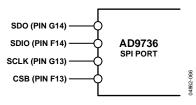

The AD9736, AD9735, and AD9734 are high performance, high frequency DACs that provide sample rates of up to 1200 MSPS, permitting multicarrier generation up to their Nyquist frequency. The AD9736 is the 14-bit member of the family, while the AD9735 and the AD9734 are the 12-bit and 10-bit members, respectively. They include a serial peripheral interface (SPI) port that provides for programming of many internal parameters and also enables readback of status registers. A reduced-specification LVDS interface is utilized to achieve the high sample rate. The output current can be programmed over a range of 8.66 mA to 31.66 mA. The AD973x family is manufactured on a 0.18  $\mu m$  CMOS process and operates from 1.8 V and 3.3 V supplies for a total power consumption of 380 mW in bypass mode. It is supplied in a 160-lead chip scale ball grid array for reduced package parasitics.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

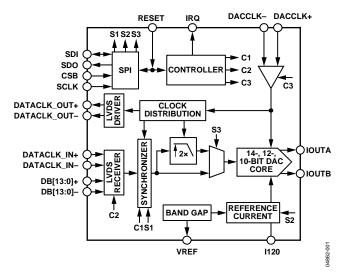

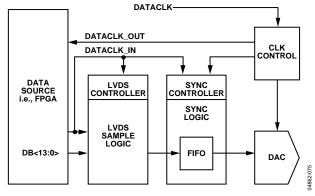

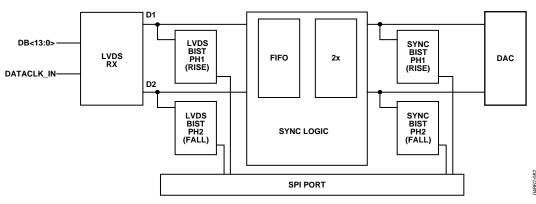

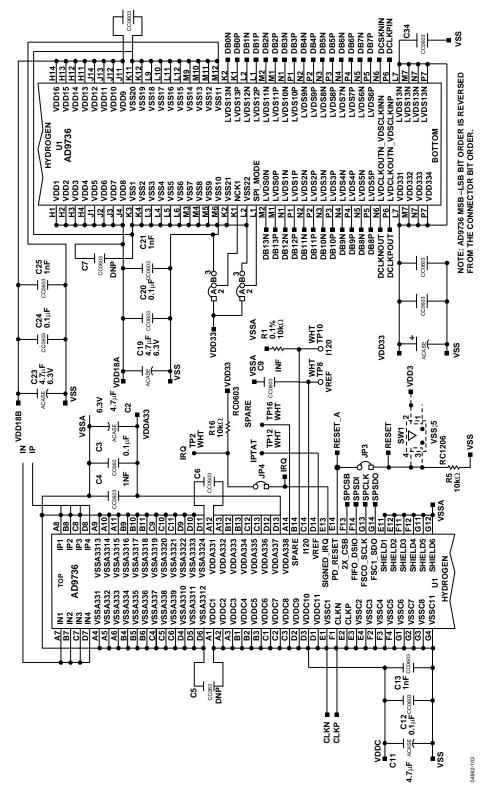

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **PRODUCT HIGHLIGHTS**

- Low noise and intermodulation distortion (IMD) features enable high quality synthesis of wideband signals at intermediate frequencies up to 600 MHz.

- 2. Double data rate (DDR) LVDS data receivers support the maximum conversion rate of 1200 MSPS.

- 3. Direct pin programmability of basic functions or SPI port access for complete control of all AD973x family functions.

- 4. Manufactured on a CMOS process, the AD973x family uses a proprietary switching technique that enhances dynamic performance.

- 5. The current output(s) of the AD9736 family are easily configured for single-ended or differential circuit topologies.

# **TABLE OF CONTENTS**

| DC Specifications 4                                                       |

|---------------------------------------------------------------------------|

| Digital Specifications                                                    |

| AC Specifications                                                         |

| Absolute Maximum Ratings                                                  |

| ESD Caution                                                               |

| Pin Configuration and Function Descriptions10                             |

| Terminology                                                               |

| Typical Performance Characteristics                                       |

| AD9736 Static Linearity, 10 mA Full Scale14                               |

| AD9736 Static Linearity, 20 mA Full Scale                                 |

| AD9736 Static Linearity, 30 mA Full Scale                                 |

| AD9735 Static Linearity, 10 mA, 20 mA, 30 mA Full Scale . 17              |

| AD9734 Static Linearity, 10 mA, 20 mA, 30 mA Full Scale . 18              |

| AD9736 Power Consumption, 20 mA Full Scale 19                             |

| AD9736 Dynamic Performance, 20 mA Full Scale 19                           |

| AD9736 Dynamic Performance, 20 mA Full Scale 21                           |

| AD9736, AD9735, AD9734 WCDMA ACLR, 20 mA Full<br>Scale                    |

| AD9735, AD9734 Dynamic Performance, 20 mA Full Scale24                    |

| SPI Register Map25                                                        |

| SPI Register Descriptions                                                 |

| MODE Register (REG 00)                                                    |

| Interrupt Request Register (IRQ) (Reg 01)26                               |

| Full Scale Current (FSC) Register (Regs 02, 03)27                         |

| LVDS Controller (LVDS_CNT) Register (Regs 04, 05, 06) 27                  |

| SYNC Controller (SYNC_CNT) Register (Regs 07, 08) 28                      |

| Cross Controller (CROS_CNT) Register (Regs 10, 11) 28                     |

| Analog Control (ANA_CNT) Register (Regs 14, 15)29                         |

| Built-in Self Test Control (BIST_CNT) Registers (Regs 17, 18, 19, 20, 21) |

| Controller Clock Predivider (CCLK_DIV) Reading Register (Reg 22)30        |

| L | neory of Operation                                             | . 31 |

|---|----------------------------------------------------------------|------|

| , | erial Peripheral Interface                                     | . 32 |

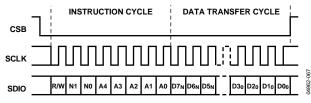

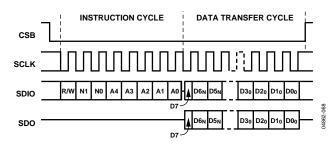

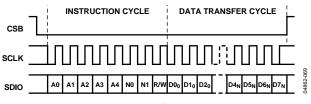

|   | General Operation of the Serial Interface                      | . 32 |

|   | Short Instruction Mode (8-Bit Instruction)                     | . 32 |

|   | Long Instruction Mode (16-Bit Instruction)                     | . 32 |

|   | Serial Interface Port Pin Descriptions                         | . 32 |

|   | MSB/LSB Transfers                                              | . 33 |

|   | Notes on Serial Port Operation                                 | . 33 |

|   | Pin Mode Operation                                             | . 34 |

|   | Reset Operation                                                | . 34 |

|   | Programming Sequence                                           | . 34 |

|   | Interpolation Filter                                           | . 35 |

|   | Data Interface Controllers                                     | . 35 |

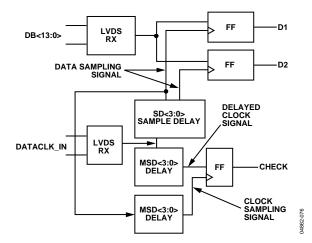

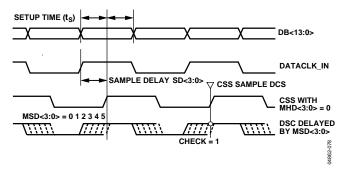

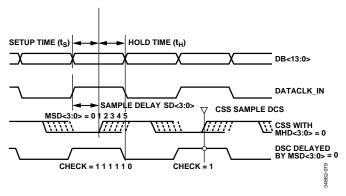

|   | LVDS Sample Logic                                              | . 36 |

|   | LVDS Sample Logic Calibration                                  | . 36 |

|   | Operating the LVDS Controller In Manual Mode via the S<br>Port |      |

|   | Operating the LVDS Controller in Surveillance and Auto Mode    | . 37 |

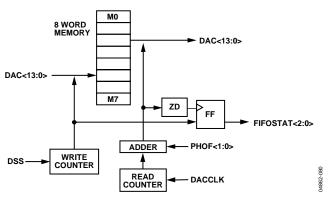

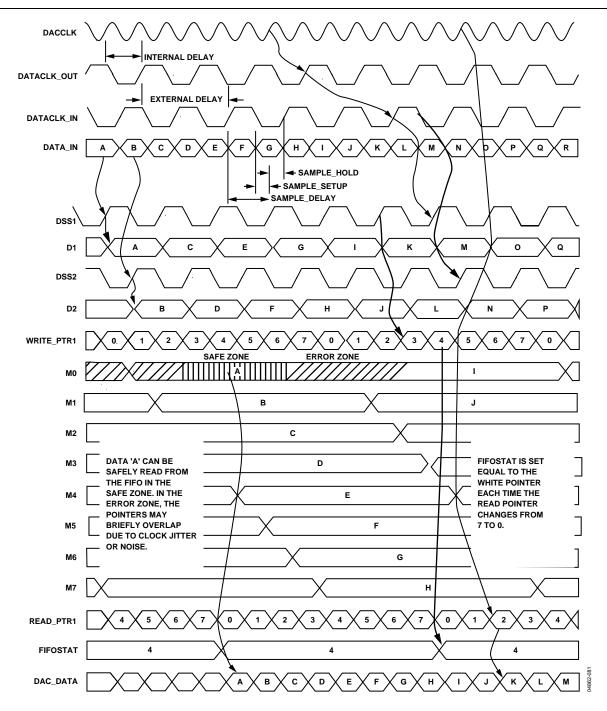

| ; | YNC Logic and Controller                                       | . 38 |

|   | SYNC Logic and Controller Operation                            | . 38 |

|   | Operating in Manual Mode                                       | . 38 |

|   | Operation in Surveillance and Auto Modes                       | . 38 |

|   | FIFO Bypass                                                    | . 38 |

| ) | igital Built-In Self Test (BIST)                               | . 40 |

|   | Overview                                                       | . 40 |

|   | AD973x BIST Procedure                                          | . 41 |

|   | AD973x Expected BIST Signatures                                | . 41 |

|   | Generating Expected Signatures                                 | . 42 |

| _ | ross Controller Registers                                      | 43   |

| Analog Control Registers                      | 44 |

|-----------------------------------------------|----|

| Band Gap Temperature Characteristic Trim Bits | 44 |

| Mirror Roll-Off Frequency Control             | 44 |

| Headroom Bits                                 | 44 |

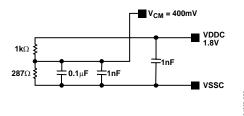

| Voltage Reference                             | 45 |

| Applications Information                      | 46 |

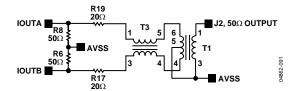

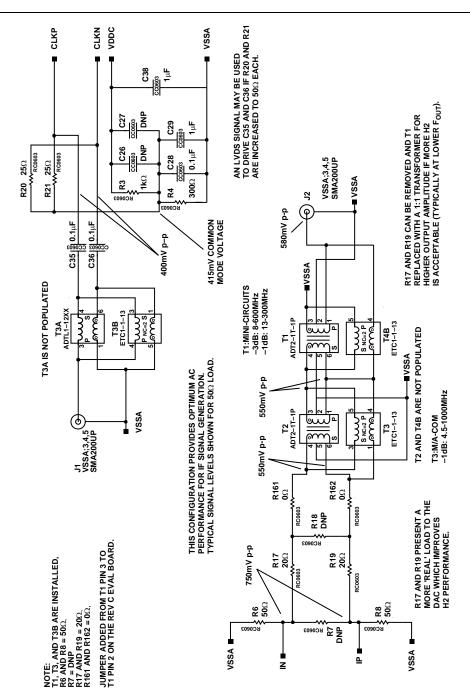

| Driving the DACCLK Input                      | 46 |

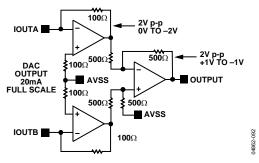

| DAC Output Distortion Sources                 | 47 |

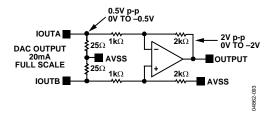

| DC-Coupled DAC Outputs                        | 48 |

| DAC Data Sources                   | 45 |

|------------------------------------|----|

| Input Data Timing                  | 50 |

| Synchronization Timing             | 51 |

| Power Supply Sequencing            | 52 |

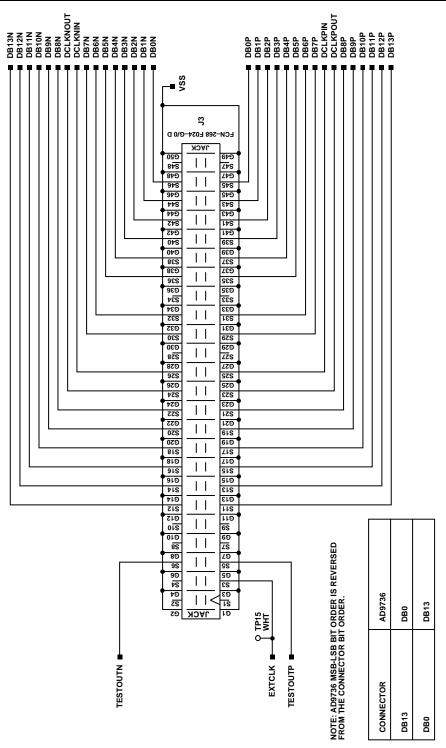

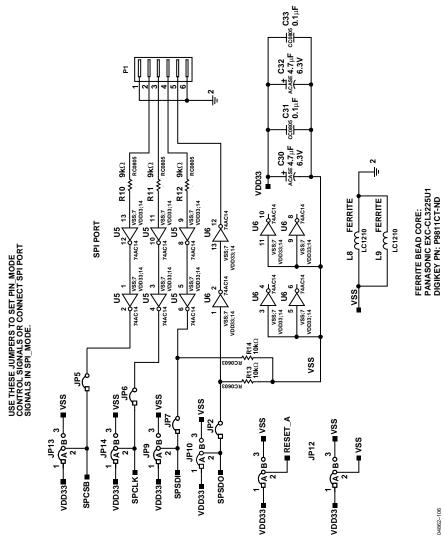

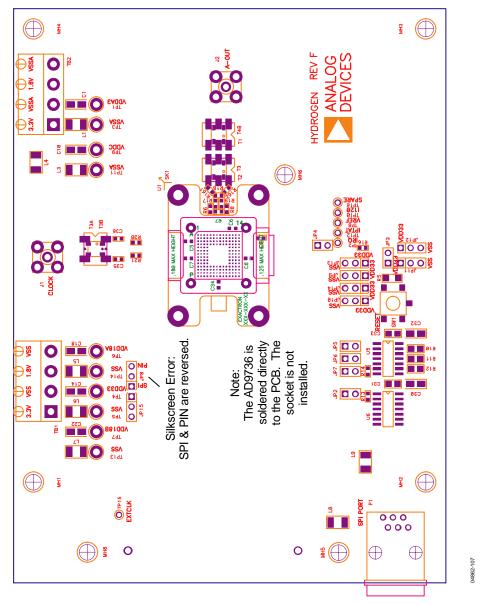

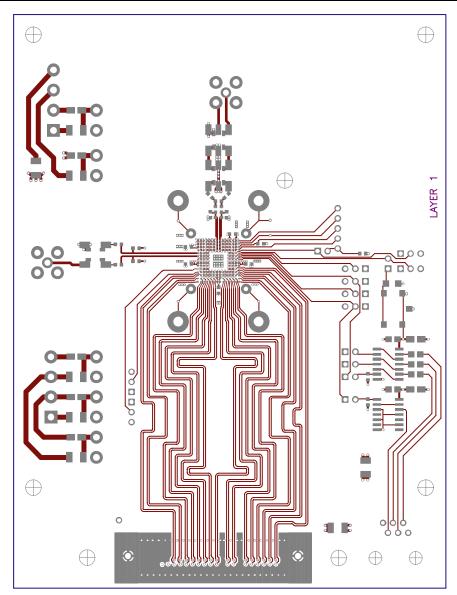

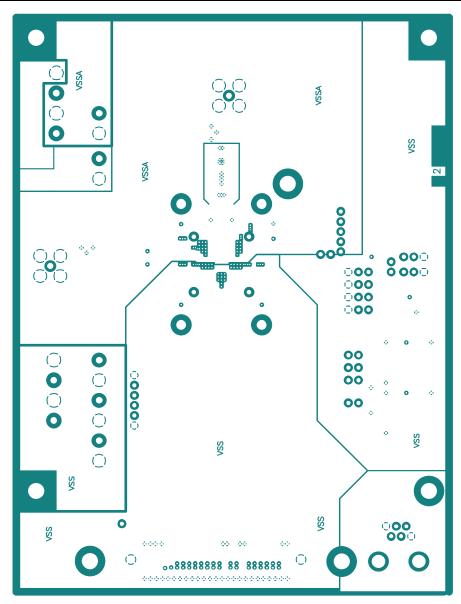

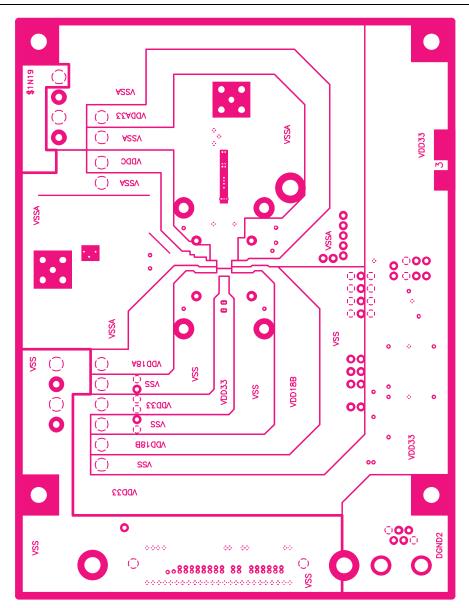

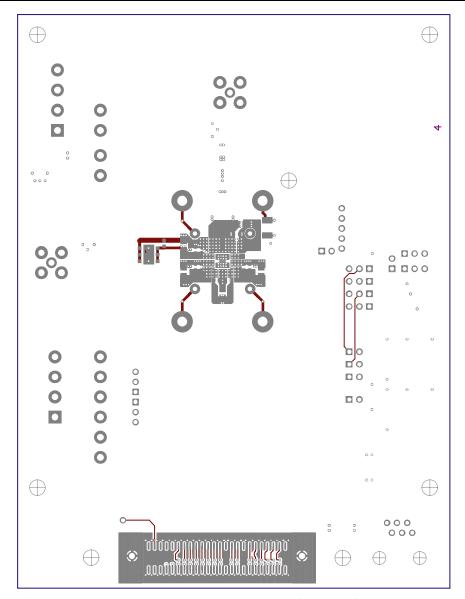

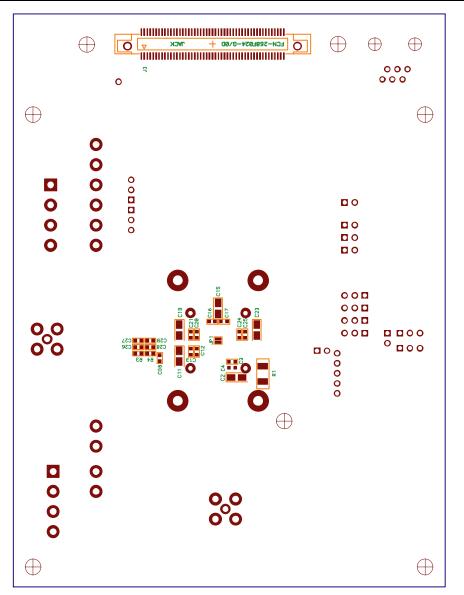

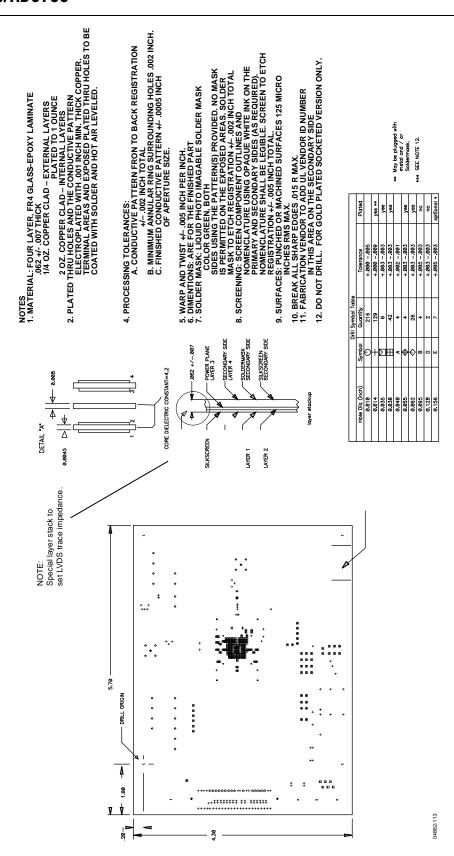

| AD973x Evaluation Board Schematics | 53 |

| AD973x Evaluation Board PCB Layout | 58 |

| Outline Dimensions                 | 65 |

| Ordering Guide                     | 65 |

### **REVISION HISTORY**

4/05—Revision 0: Initial Version

# DC SPECIFICATIONS

AVDD33 = DVDD33 = 3.3 V, CVDD18 = DVDD18 = 1.8 V, maximum sample rate,  $I_{FS}$  = 20 mA, 1× mode, 25  $\Omega$  1% balanced load, unless otherwise noted.

Table 1.

|                                            |       | AD9736 |       | AD9735 |        | AD9734 |       |        |       |        |

|--------------------------------------------|-------|--------|-------|--------|--------|--------|-------|--------|-------|--------|

| Parameter                                  | Min   | Тур    | Max   | Min    | Тур    | Max    | Min   | Тур    | Max   | Unit   |

| RESOLUTION                                 |       | 14     |       |        | 12     |        |       | 10     |       | Bits   |

| ACCURACY                                   |       |        |       |        |        |        |       |        |       |        |

| Integral Nonlinearity (INL)                | -5.6  | ±1.0   | +5.6  | -1.5   | ±0.50  | +1.5   | -0.5  | ±0.12  | +0.5  | LSB    |

| Differential Nonlinearity (DNL)            | -2.1  | ±0.6   | +2.1  | -0.5   | ±0.25  | +0.5   | -0.1  | ±0.06  | +0.1  | LSB    |

| ANALOG OUTPUTS                             |       |        |       |        |        |        |       |        |       |        |

| Offset Error                               | -0.01 | ±0.005 | +0.01 | -0.01  | ±0.005 | +0.01  | -0.01 | ±0.005 | +0.01 | % FSR  |

| Gain Error (With Internal<br>Reference)    |       | ±1.0   |       |        | ±1.0   |        |       | ±1.0   |       | % FSR  |

| Gain Error (Without Internal<br>Reference) |       | ±1.0   |       |        | ±1.0   |        |       | ±1.0   |       | % FSR  |

| Full-Scale Output Current                  | 8.66  | 20.2   | 31.66 | 8.66   | 20.2   | 31.66  | 8.66  | 20.2   | 31.66 | mA     |

| Output Compliance Range                    | -1.0  |        | +1.0  | -1.0   |        | 1.0    | -1.0  |        | +1.0  | V      |

| Output Resistance                          |       | 10     |       |        | 10     |        |       | 10     |       | ΜΩ     |

| Output Capacitance                         |       | 1      |       |        | 1      |        |       | 1      |       | pF     |

| TEMPERATURE DRIFT                          |       |        |       |        |        |        |       |        |       |        |

| Offset                                     |       | 0      |       |        | 0      |        |       | 0      |       | ppm/°C |

| Gain                                       |       | 80     |       |        | 80     |        |       | 80     |       | ppm/°C |

| Reference Voltage <sup>1</sup>             |       | 40     |       |        | 40     |        |       | 40     |       | ppm/°C |

| REFERENCE                                  |       |        |       |        |        |        |       |        |       |        |

| Internal Reference Voltage <sup>1</sup>    | 1.14  | 1.2    | 1.26  | 1.14   | 1.2    | 1.26   | 1.14  | 1.2    | 1.26  | V      |

| Output Resistance <sup>2</sup>             |       | 5      |       |        | 5      |        |       | 5      |       | kΩ     |

| ANALOG SUPPLY VOLTAGES                     |       |        |       |        |        |        |       |        |       |        |

| AVDD33                                     | 3.13  | 3.3    | 3.47  | 3.13   | 3.3    | 3.47   | 3.13  | 3.3    | 3.47  | V      |

| CVDD18                                     | 1.70  | 1.8    | 1.90  | 1.70   | 1.8    | 1.90   | 1.70  | 1.8    | 1.90  | V      |

| DIGITAL SUPPLY VOLTAGES                    |       |        |       |        |        |        |       |        |       |        |

| DVDD33                                     | 3.13  | 3.3    | 3.47  | 3.13   | 3.3    | 3.47   | 3.13  | 3.3    | 3.47  | V      |

| DVDD18                                     | 1.70  | 1.8    | 1.90  | 1.70   | 1.8    | 1.90   | 1.70  | 1.8    | 1.90  | V      |

| SUPPLY CURRENTS<br>1× Mode, 1.2 GSPS       |       |        |       |        |        |        |       |        |       |        |

| I <sub>AVDD33</sub>                        |       | 25     |       |        | 25     |        |       | 25     |       | mA     |

| I <sub>CVDD18</sub>                        |       | 47     |       |        | 47     |        |       | 47     |       | mA     |

| I <sub>DVDD33</sub>                        |       | 10     |       |        | 10     |        |       | 10     |       | mA     |

| I <sub>DVDD18</sub>                        |       | 122    |       |        | 122    |        |       | 122    |       | mA     |

| FIR Bypass (1 $\times$ ) Mode              |       | 380    |       |        | 380    |        |       | 380    |       | mW     |

| 2× Mode, 1.2 GSPS                          |       |        |       |        |        |        |       |        |       |        |

| I <sub>AVDD33</sub>                        |       | 25     |       |        | 25     |        |       | 25     |       | mA     |

| I <sub>CVDD18</sub>                        |       | 47     |       |        | 47     |        |       | 47     |       | mA     |

| I <sub>DVDD33</sub>                        |       | 10     |       |        | 10     |        |       | 10     |       | mA     |

| I <sub>DVDD18</sub>                        |       | 234    |       |        | 234    |        |       | 234    |       | mA     |

| FIR 2× Interpolation Filter<br>Enabled     |       | 550    |       |        | 550    |        |       | 550    |       | mW     |

|                      |     | AD973 | 6    |     | AD973 | 5    |     | AD973 | 4    |      |

|----------------------|-----|-------|------|-----|-------|------|-----|-------|------|------|

| Parameter            | Min | Тур   | Max  | Min | Тур   | Max  | Min | Тур   | Max  | Unit |

| Static, No Clock     |     |       |      |     |       |      |     |       |      |      |

| I <sub>AVDD33</sub>  |     | 25    |      |     | 25    |      |     | 25    |      | mA   |

| I <sub>CVDD18</sub>  |     | 8     |      |     | 8     |      |     | 8     |      | mA   |

| I <sub>DVDD33</sub>  |     | 10    |      |     | 10    |      |     | 10    |      | mA   |

| I <sub>DVDD18</sub>  |     | 2     |      |     | 2     |      |     | 2     |      | mA   |

| FIR Bypass (1×) Mode |     | 133   |      |     | 133   |      |     | 133   |      | mW   |

| Sleep Mode, No Clock |     |       |      |     |       |      |     |       |      |      |

| I <sub>AVDD33</sub>  |     | 2.5   | 3.15 |     | 2.5   | 3.15 |     | 2.5   | 3.15 | mA   |

| FIR Bypass (1×) Mode |     | 59    | 65   |     | 59    | 65   |     | 59    | 65   | mW   |

| Power-Down Mode      |     |       |      |     |       |      |     |       |      |      |

| I <sub>AVDD33</sub>  |     | 0.01  | 0.13 |     | 0.01  | 0.13 |     | 0.01  | 0.13 | mA   |

| ICVDD18              |     | 0.02  | 0.12 |     | 0.02  | 0.12 |     | 0.02  | 0.12 | mA   |

| I <sub>DVDD33</sub>  |     | 0.01  | 0.12 |     | 0.01  | 0.12 |     | 0.01  | 0.12 | mA   |

| I <sub>DVDD18</sub>  |     | 0.01  | 0.11 |     | 0.01  | 0.11 |     | 0.01  | 0.11 | mA   |

| FIR Bypass (1×) Mode |     | 0.12  | 1.24 |     | 0.12  | 1.24 |     | 0.12  | 1.24 | mW   |

$<sup>^{1}</sup>$  Default band gap adjustment (Reg0E<2:0> = 0h).  $^{2}$  Use an external amplifier to drive any external load.

# **DIGITAL SPECIFICATIONS**

AVDD33 = DVDD33 = 3.3 V, CVDD18 = DVDD18 = 1.8 V, maximum sample rate,  $I_{FS}$  = 20 mA, 1× mode, 25  $\Omega$  1% balanced load, unless otherwise noted.

LVDS drivers and receivers are compliant to the IEEE-1596 reduced range link, unless otherwise noted.

Table 2.

| Parameter                                                                                                                 | Min  | Тур | Max  | Unit    |

|---------------------------------------------------------------------------------------------------------------------------|------|-----|------|---------|

| LVDS DATA INPUTS                                                                                                          |      |     |      |         |

| (DB[13:0]+, DB[13:0]-) DB+ = $V_{ia}$ , DB- = $V_{ib}$                                                                    |      |     |      |         |

| Input Voltage Range, $V_{ia}$ or $V_{ib}$                                                                                 | 825  |     | 1575 | mV      |

| Input Differential Threshold, V <sub>idth</sub>                                                                           | -100 |     | +100 | mV      |

| Input Differential Hysteresis, V <sub>idthh</sub> – V <sub>idthl</sub>                                                    |      | 20  |      | mV      |

| Receiver Differential Input Impedance, R <sub>in</sub>                                                                    | 80   |     | 120  | Ω       |

| LVDS Input Rate                                                                                                           | 1200 |     |      | MSPS    |

| LVDS Minimum Data Valid Period (t <sub>MDE</sub> )                                                                        |      |     | 344  | ps      |

| LVDS CLOCK INPUT                                                                                                          |      |     |      |         |

| (DATACLK_IN+, DATACLK_IN-) DATACLK_IN+ = V <sub>ia</sub> , DATACLK_IN- = V <sub>ib</sub>                                  | 025  |     | 4575 | .,      |

| Input Voltage Range, V <sub>ia</sub> or V <sub>ib</sub>                                                                   | 825  |     | 1575 | mV      |

| Input Differential Threshold <sup>1</sup> , V <sub>idth</sub>                                                             | -100 | 20  | +100 | mV      |

| Input Differential Hysteresis, V <sub>idthl</sub> - V <sub>idthl</sub>                                                    |      | 20  | 400  | mV      |

| Receiver Differential Input Impedance, R <sub>in</sub>                                                                    | 80   |     | 120  | Ω       |

| Maximum Clock Rate                                                                                                        | 600  |     |      | MHz     |

| LVDS CLOCK OUTPUT (DATACLK_OUT+, DATACLK_OUT+) DATACLK_OUT+ = $V_{oa}$ , DATACLK_OUT- = $V_{ob}$ 100 $\Omega$ Termination |      |     |      |         |

| Output Voltage High, Voa or Vob                                                                                           |      |     | 1375 | mV      |

| Output Voltage Low, V <sub>oa</sub> or V <sub>ob</sub>                                                                    | 1025 |     |      | mV      |

| Output Differential Voltage,  Vod                                                                                         | 150  | 200 | 250  | mV      |

| Output Offset Voltage, Vos                                                                                                | 1150 |     | 1250 | mV      |

| Output Impedance, Single-Ended, R <sub>o</sub>                                                                            | 80   | 100 | 120  | Ω       |

| Ro Mismatch Between A and B, ΔR <sub>o</sub>                                                                              |      |     | 10   | %       |

| Change in  Vod  Between 0 and 1, $ \Delta V_{od} $                                                                        |      |     | 25   | mV      |

| Change in Vos Between 0 and 1, $\Delta V_{os}$                                                                            |      |     | 25   | mV      |

| Output Current—Driver Shorted to Ground, Isa, Isb                                                                         |      |     | 20   | mA      |

| Output Current—Driver Shorted to Glound, Isa, Isb  Output Current—Drivers Shorted Together, Isab                          |      |     | 4    | mA      |

| Power-Off Output Leakage, $ I_{xa} $ , $ I_{xb} $                                                                         |      |     | 10   | mA      |

| Maximum Clock Rate                                                                                                        | 600  |     | 10   | MHz     |

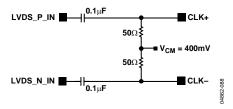

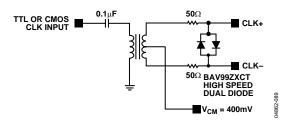

| DAC CLOCK INPUT (CLK+, CLK-)                                                                                              | 000  |     |      | IVII IZ |

| Input Voltage Range, CLK– or CLK+                                                                                         | 0    |     | 800  |         |

| Differential Peak-to-Peak Voltage                                                                                         | 400  | 800 | 1600 | mV      |

| Common-Mode Voltage                                                                                                       | 300  | 400 | 500  | mV      |

| Maximum Clock Rate                                                                                                        | 1200 | 400 | 300  | MHz     |

| SERIAL PERIPHERAL INTERFACE                                                                                               | 1200 |     |      | 1411.12 |

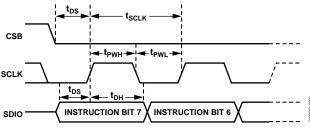

| Maximum Clock Rate (fsclk, 1/tsclk)                                                                                       |      |     | 20   | MHz     |

| Minimum Pulse Width High, t <sub>PWH</sub>                                                                                | 20   |     | 20   | ns      |

| Minimum Pulse Width Low, tpw/                                                                                             | 20   |     |      | ns      |

| Minimum SDIO and CSB to SCLK Setup, t <sub>DS</sub>                                                                       | 20   | 10  |      | ns      |

| Minimum SCLK to SDIO Hold. ton                                                                                            |      | 5   |      | ns      |

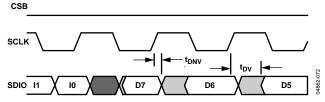

| Maximum SCLK to Valid SDIO and SDO, tov                                                                                   |      | 20  |      | ns      |

| Minimum SCLK to Invalid SDIO and SDO, t <sub>DNV</sub>                                                                    |      | 5   |      | ns      |

| Parameter                         | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| INPUTS (SDI, SDIO, SCLK, CSB)     |     |     |     |      |

| Voltage in High, V <sub>ih</sub>  | 2.0 | 3.3 |     | ٧    |

| Voltage in Low, V <sub>il</sub>   |     | 0   | 8.0 | V    |

| Current in High, I <sub>ih</sub>  | -10 |     | +10 | μΑ   |

| Current in Low, I <sub>il</sub>   | -10 |     | +10 | μΑ   |

| Input Capacitance                 |     |     |     | pF   |

| SDIO OUTPUT                       |     |     |     |      |

| Voltage out High, V <sub>oh</sub> | 2.4 |     | 3.6 | V    |

| Voltage out Low, Vol              | 0   |     | 0.4 | ٧    |

| Current out High, Ioh             |     | 4   |     | mA   |

| Current out Low, Iol              |     | 4   |     | mA   |

$<sup>^{\</sup>rm 1}$  Refer to the Input Data Timing section for recommended LVDS differential drive levels.

# **AC SPECIFICATIONS**

AVDD33 = DVDD33 = 3.3 V, CVDD18 = DVDD18 = 1.8 V, maximum sample rate,  $I_{FS}$  = 20 mA, 1× mode, 25  $\Omega$  1% balanced load, unless otherwise noted.

Table 3.

|                                           |        | AD9736 |     |      | AD9735 | 5   |      | AD97   | 34  |        |

|-------------------------------------------|--------|--------|-----|------|--------|-----|------|--------|-----|--------|

| Parameter                                 | Min    | Тур    | Max | Min  | Тур    | Max | Min  | Тур    | Max | Unit   |

| DYNAMIC PERFORMANCE                       |        |        |     |      |        |     |      |        |     |        |

| Maximum Update Rate                       | 1200   |        |     | 1200 |        |     | 1200 |        |     | MSPS   |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)        |        |        |     |      |        |     |      |        |     |        |

| $f_{DAC} = 800 \text{ MSPS}$              |        |        |     |      |        |     |      |        |     |        |

| $f_{OUT} = 20 \text{ MHz}$                |        | 75     |     |      | 75     |     |      | 75     |     | dBc    |

| $f_{DAC} = 1200 \text{ MSPS}$             |        |        |     |      |        |     |      |        |     |        |

| $f_{OUT} = 50 \text{ MHz}$                |        | 80     |     |      | 76     |     |      | 76     |     | dBc    |

| $f_{OUT} = 100 \text{ MHz}$               |        | 77     |     |      | 74     |     |      | 71     |     | dBc    |

| $f_{OUT} = 316 \text{ MHz}$               |        | 63     |     |      | 63     |     |      | 60     |     | dBc    |

| $f_{OUT} = 550 \text{ MHz}$               |        | 55     |     |      | 54     |     |      | 53     |     | dBc    |

| TWO-TONE INTERMODULATION DISTORTION (IMD) |        |        |     |      |        |     |      |        |     |        |

| $f_{DAC} = 1200 MSPS$                     |        |        |     |      |        |     |      |        |     |        |

| $f_{OUT2} = f_{OUT} + 1.25 \text{ MHz}$   |        |        |     |      |        |     |      |        |     |        |

| $f_{OUT} = 40 \text{ MHz}$                |        | 88     |     |      | 84     |     |      | 83     |     | dBc    |

| $f_{OUT} = 50 \text{ MHz}$                |        | 85     |     |      | 84     |     |      | 83     |     | dBc    |

| $f_{OUT} = 100 \text{ MHz}$               |        | 84     |     |      | 81     |     |      | 79     |     | dBc    |

| $f_{OUT} = 315 \text{ MHz}$               |        | 70.5   |     |      | 67     |     |      | 66     |     | dBc    |

| f <sub>оит</sub> = 550 MHz                |        | 65     |     |      | 60     |     |      | 60     |     | dBc    |

| NOISE SPECTRAL DENSITY (NSD)              |        |        |     |      |        |     |      |        |     |        |

| Single Tone                               |        |        |     |      |        |     |      |        |     |        |

| $f_{DAC} = 1200 \text{ MSPS}$             |        |        |     |      |        |     |      |        |     |        |

| $f_{OUT} = 50 \text{ MHz}$                |        | -165   |     |      | -162   |     |      | -154   |     | dBm/Hz |

| $f_{OUT} = 100 \text{ MHz}$               |        | -164   |     |      | -161   |     |      | -154   |     | dBm/Hz |

| $f_{OUT} = 241MHz$                        | -158.5 | -160.5 |     |      | -159.5 |     |      | -155   |     | dBm/Hz |

| $f_{OUT} = 316 \text{ MHz}$               |        | -158   |     |      | -157   |     |      | -152   |     | dBm/Hz |

| $f_{OUT} = 550 \text{ MHz}$               |        | -155   |     |      | -155   |     |      | -149   |     | dBm/Hz |

| Eight-Tone                                |        |        |     |      |        |     |      |        |     |        |

| $f_{DAC} = 1200 MSPS, 500 kHz Tone$       |        |        |     |      |        |     |      |        |     |        |

| Spacing                                   |        |        |     |      |        |     |      |        |     |        |

| $f_{OUT} = 50 \text{ MHz}$                |        | -166.5 |     |      | -163   |     |      | -154   |     | dBm/Hz |

| $f_{OUT} = 100 \text{ MHz}$               |        | -166   |     |      | -163   |     |      | -152   |     | dBm/Hz |

| $f_{OUT} = 241MHz$                        | -163.3 | -165   |     |      | -161.5 |     |      | -150.5 | 5   | dBm/Hz |

| $f_{OUT} = 316 \text{ MHz}$               |        | -164   |     |      | -162   |     |      | -151   |     | dBm/Hz |

| $f_{OUT} = 550 \text{ MHz}$               |        | -162   |     |      | -160   |     |      | -150   |     | dBm/Hz |

## **ABSOLUTE MAXIMUM RATINGS**

Table 4.

|                   | With       |        |                 |

|-------------------|------------|--------|-----------------|

| Parameter         | Respect to | Min    | Max             |

| AVDD33            | AVSS       | -0.3 V | +3.6 V          |

| DVDD33            | DVSS       | -0.3 V | +3.6 V          |

| DVDD18            | DVSS       | -0.3 V | +1.98 V         |

| CVDD18            | CVSS       | -0.3 V | +1.98 V         |

| AVSS              | DVSS       | -0.3 V | +0.3 V          |

| AVSS              | CVSS       | -0.3 V | +0.3 V          |

| DVSS              | CVSS       | -0.3 V | +0.3 V          |

| CLK+, CLK-        | CVSS       | -0.3 V | CVDD18 + 0.18 V |

| PIN_MODE          | DVSS       | -0.3 V | DVDD33 + 0.3 V  |

| DATACLK_IN,       |            |        |                 |

| DATACLK_OUT       | DVSS       | -0.3 V | DVDD33 + 0.3 V  |

| LVDS Data Inputs  | DVSS       | -0.3 V | DVDD33 + 0.3 V  |

| IOUTA, IOUTB      | AVSS       | -1.0 V | AVDD33 + 0.3 V  |

| I120, VREF, IPTAT | AVSS       | -0.3 V | AVDD33 + 0.3 V  |

| IRQ, CSB, SCLK,   |            |        |                 |

| SDO, SDIO, RESET  | DVSS       | -0.3 V | DVDD33 + 0.3 V  |

| Junction Temp.    |            |        | 150°C           |

| Storage Temp.     |            | −65°C  | +150°C          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Note that this device in its current form does not meet Analog Devices' standard requirements for ESD as measured against the charged device model (CDM). As such, special care should be used when handling this product, especially in a manufacturing environment. Analog Devices will provide a more ESD-hardy product in the near future at which time this warning will be removed from this datasheet.

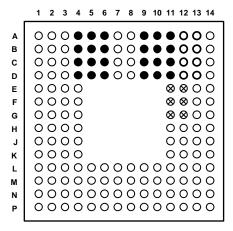

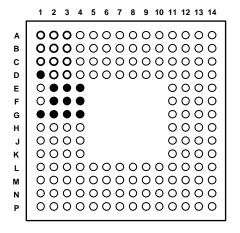

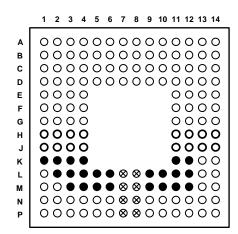

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- **O**AVDD33, 3.3V, ANALOG SUPPLY

- AVSS, ANALOG SUPPLY GROUND

- ⊗ AVSS, ANALOG SUPPLY GROUND SHIELD

Figure 2. AD9736 Analog Supply Pins (Top View)

- OCVDD18, 1.8V CLOCK SUPPLY

- **CVSS, CLOCK SUPPLY GROUND**

Figure 3. AD9736 Clock Supply Pins (Top View)

- **O** DVDD18, 1.8V DIGITAL SUPPLY ⊗ DVDD33, 3.3V DIGITAL SUPPLY

- DVSS DIGITAL SUPPLY GROUND

Figure 4. AD9736 Digital Supply Pins (Top View)

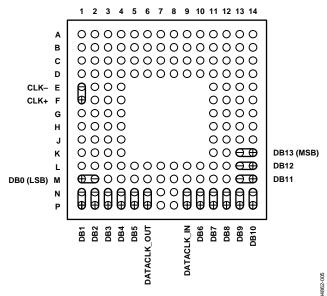

Figure 5. AD9736 Digital LVDS Inputs, Clock I/O (Top View)

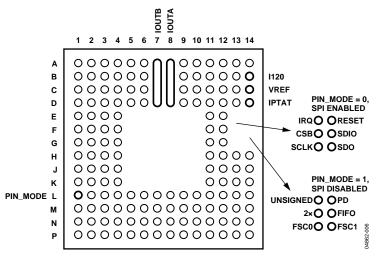

Figure 6. AD9736 Analog I/O and SPI Control Pins (Top View)

**Table 5. Pin Function Descriptions**

| Pin No.                                                                                                  | Mnemonic        | Description                                                                                                                           |

|----------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2, A3, B1, B2, B3, C1, C2, C3, D2, D3                                                               | CVDD18          | 1.8 V Clock Supply.                                                                                                                   |

| A4, A5, A6, A9, A10, A11, B4, B5, B6, B9, B10, B11, C4, C5, C6, C9, C10, C11, D4, D5, D6, D9, D10, D11   | AVSS            | Analog Supply Ground.                                                                                                                 |

| A7, B7, C7, D7                                                                                           | IOUTB           | DAC Negative Output; 10 mA to 30 mA full-scale output current.                                                                        |

| A8, B8, C8, D8                                                                                           | IOUTA           | DAC Positive Output; 10 mA to 30 mA full-scale output current.                                                                        |

| A12, A13, B12, B13, C12, C13, D12, D13                                                                   | AVDD33          | 3.3 V Analog Supply.                                                                                                                  |

| A14                                                                                                      | DNC             | Do Not Connect.                                                                                                                       |

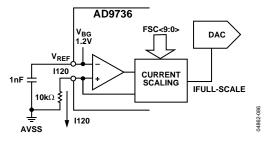

| B14                                                                                                      | l120            | Nominal 1.2 V Reference; tie to analog ground via 10 k $\Omega$ resistor to generate a 120 $\mu$ A reference current.                 |

| C14                                                                                                      | VREF            | Band Gap Voltage Reference I/O; tie to analog ground via 1 nF capacitor, output impedance approximately 5 k $\Omega$ .                |

| D1, E2, E3, E4, F2, F3, F4, G1, G2, G3, G4                                                               | CVSS            | Clock Supply Ground.                                                                                                                  |

| D14                                                                                                      | IPTAT           | Factory Test Pin; output current proportional to absolute temperature, approximately 10 μA at 25°C with approximately 20 nA/°C slope. |

| E1, F1                                                                                                   | DACCLK-/DACCLK+ | Negative/Positive DAC Clock Input (DACCLK).                                                                                           |

| E11, E12, F11, F12, G11, G12                                                                             | AVSS            | Analog Supply Ground Shield; tie to AVSS at the DAC.                                                                                  |

| E13                                                                                                      | IRQ/UNSIGNED    | If PIN_MODE = 0, IRQ: Active low open-drain interrupt request output, pull up to DVDD33 with 10 k $\Omega$ resistor.                  |

|                                                                                                          |                 | If PIN_MODE = 1, UNSIGNED: Digital input pin where 0 = twos complement input data format, 1 = unsigned.                               |

| E14                                                                                                      | RESET/PD        | If PIN_MODE = 0, RESET: 1 resets the AD9736.                                                                                          |

|                                                                                                          |                 | If PIN_MODE = 1, PD: 1 puts the AD9736 in the power-down state.                                                                       |

| F13                                                                                                      | CSB/2×          | See Serial Peripheral Interface and Pin Mode Operation sections for pin description.                                                  |

| F14                                                                                                      | SDIO/FIFO       | See the Pin Mode Operation section for pin description.                                                                               |

| G13                                                                                                      | SCLK/FSC0       | See the Pin Mode Operation section for pin description.                                                                               |

| G14                                                                                                      | SDO/FSC1        | See the Pin Mode Operation section for pin description.                                                                               |

| H1, H2, H3, H4, H11, H12, H13, H14, J1, J2, J3, J4, J11, J12, J13, J14                                   | DVDD18          | 1.8 V Digital Supply.                                                                                                                 |

| K1, K2, K3, K4, K11, K12, L2, L3, L4, L5, L6,<br>L9, L10, L11, L12, M3, M4, M5, M6, M9,<br>M10, M11, M12 | DVSS            | Digital Supply Ground.                                                                                                                |

| Pin No.                        | Mnemonic        | Description                                                    |

|--------------------------------|-----------------|----------------------------------------------------------------|

| K13, K14                       | DB<13>-/DB<13>+ | Negative/Positive Data Input Bit 13 (MSB); reduced swing LVDS. |

| L1                             | PIN_MODE        | 0 = SPI Mode; SPI enabled.                                     |

|                                |                 | 1 = PIN Mode; SPI disabled, direct pin control.                |

| L7, L8, M7, M8, N7, N8, P7, P8 | DVDD33          | 3.3 V Digital Supply.                                          |

| L13, L14                       | DB<12>-/DB<12>+ | Negative/Positive Data Input Bit 12; reduced swing LVDS.       |

| M2, M1                         | DB<0>-/DB<0>+   | Negative/Positive Data Input Bit 0 (LSB); reduced swing LVDS.  |

| M13, M14                       | DB<11>-/DB<11>+ | Negative/Positive Data Input Bit 11; reduced swing LVDS.       |

| N1, P1                         | DB<1>-/DB<1>+   | Negative/Positive Data Input Bit 1; reduced swing LVDS.        |

| N2, P2                         | DB<2>-/DB<2>+   | Negative/Positive Data Input Bit 2; reduced swing LVDS.        |

| N3, P3                         | DB<3>-/DB<3>+   | Negative/Positive Data Input Bit 3; reduced swing LVDS.        |

| N4, P4                         | DB<4>-/DB<4>+   | Negative/Positive Data Input Bit 4; reduced swing LVDS         |

| N5, P5                         | DB<5>-/DB<5>+   | Negative/Positive Data Input Bit 5; reduced swing LVDS.        |

| N6, P6                         | DATACLK_OUT-/   | Negative/Positive Data Output Clock; reduced swing LVDS.       |

|                                | DATACLK_OUT+    |                                                                |

| N9, P9                         | DATACLK_IN-/    | Negative/Positive Data Input Clock; reduced swing LVDS         |

|                                | DATACLK_IN+     |                                                                |

| N10, P10                       | DB<6>-/DB<6>+   | Negative/Positive Data Input Bit 6; reduced swing LVDS.        |

| N11, P11                       | DB<7>-/DB<7>+   | Negative/Positive Data Input Bit 7; reduced swing LVDS.        |

| N12, P12                       | DB<8>-/DB<8>+   | Negative/Positive Data Input Bit 8; reduced swing LVDS.        |

| N13, P13                       | DB<9>-/DB<9>+   | Negative/Positive Data Input Bit 9; reduced swing LVDS.        |

| N14, P14                       | DB<10>-/DB<10>+ | Negative/Positive Data Input Bit 10; reduced swing LVDS.       |

## **TERMINOLOGY**

### **Linearity Error (Integral Nonlinearity or INL)**

The maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero to full scale.

#### Differential Nonlinearity (DNL)

The measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

#### Monotonicity

A DAC is monotonic if the output either increases or remains constant as the digital input increases.

#### **Offset Error**

The deviation of the output current from the ideal of zero is called the offset error. For IOUTA, 0 mA output is expected when the inputs are all 0s. For IOUTB, 0 mA output is expected when all inputs are set to 1s.

#### **Gain Error**

The difference between the actual and ideal output span. The actual span is determined by the output when all inputs are set to 1s minus the output when all inputs are set to 0s.

#### **Output Compliance Range**

The range of allowable voltage at the output of a current output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation or breakdown, resulting in nonlinear performance.

#### **Temperature Drift**

Specified as the maximum change from the ambient (25°C) value to the value at either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per °C. For reference drift, the drift is reported in ppm per °C.

### **Power Supply Rejection**

The maximum change in the full-scale output as the supplies are varied from nominal to minimum and maximum specified voltages.

#### **Settling Time**

The time required for the output to reach and remain within a specified error band about its final value, measured from the start of the output transition.

### Glitch Impulse

Asymmetrical switching times in a DAC give rise to undesired output transients that are quantified by a glitch impulse. It is specified as the net area of the glitch in pV-s.

#### Spurious-Free Dynamic Range

The difference, in dB, between the rms amplitude of the output signal and the peak spurious signal over the specified bandwidth.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal. It is expressed as a percentage or in decibels (dB).

#### **Multitone Power Ratio**

The spurious-free dynamic range containing multiple carrier tones of equal amplitude. It is measured as the difference between the rms amplitude of a carrier tone to the peak spurious signal in the region of a removed tone.

# TYPICAL PERFORMANCE CHARACTERISTICS

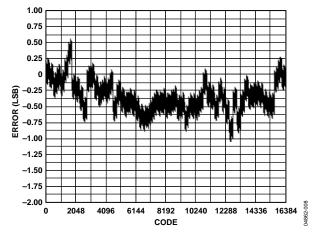

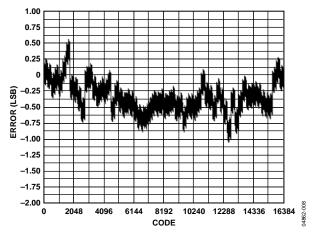

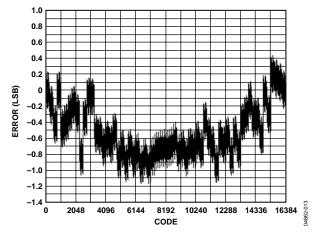

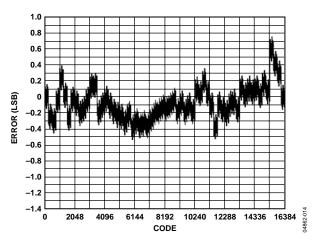

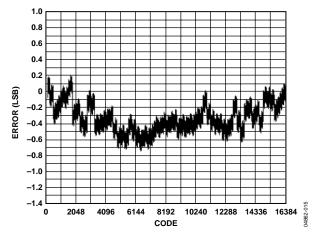

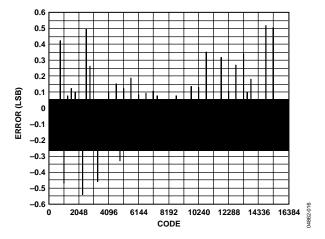

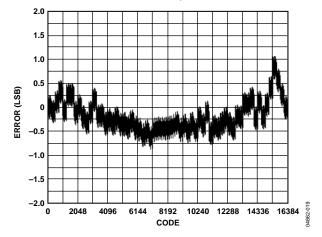

## AD9736 STATIC LINEARITY, 10 mA FULL SCALE

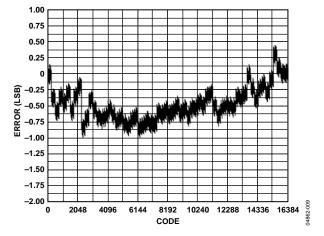

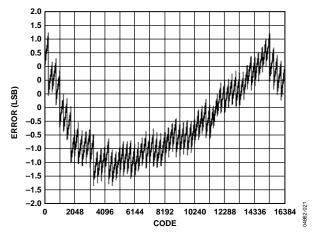

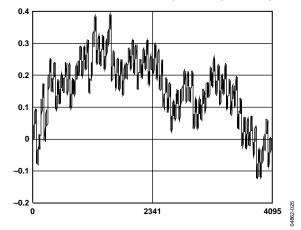

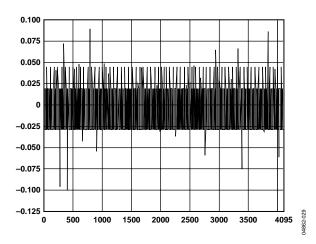

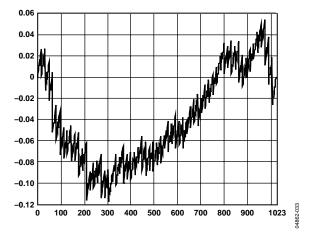

Figure 7. AD9736 INL, -40°C, 10 mA FS

Figure 8. AD9736 INL, 25°C, 10 mA FS

Figure 9. AD9736 INL, 85°C, 10 mA FS

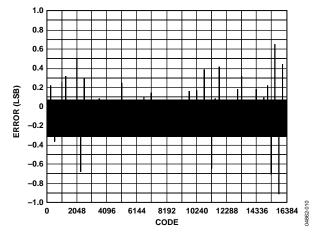

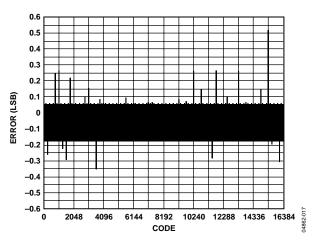

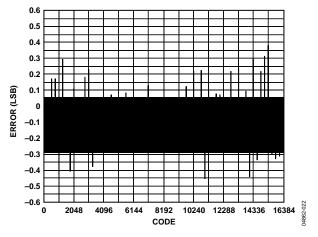

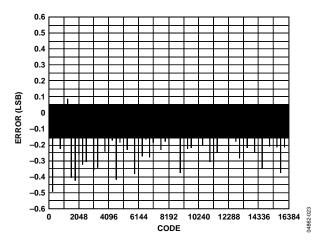

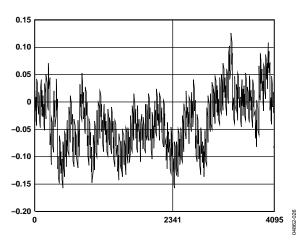

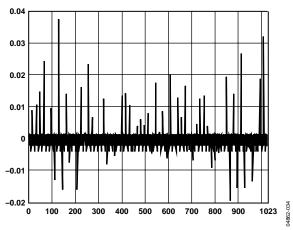

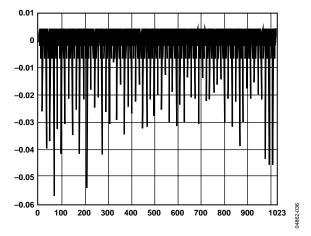

Figure 10. AD9736 DNL, -40°C, 10 mA FS

Figure 11. AD976 DNL, 25°C, 10 mA FS

Figure 12. AD9736 DNL, 85°C, 10 mA FS

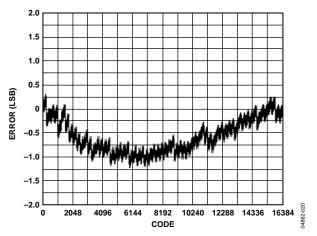

### AD9736 STATIC LINEARITY, 20 mA FULL SCALE

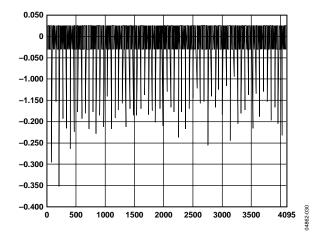

Figure 13. AD9736 INL, −40°C, 20 mA FS

Figure 14. AD9736 INL, 25°C, 20 mA FS

Figure 15. AD9736 INL, 85°C, 20 mA FS

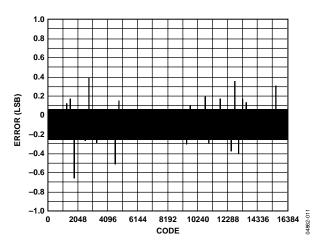

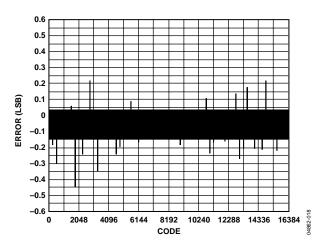

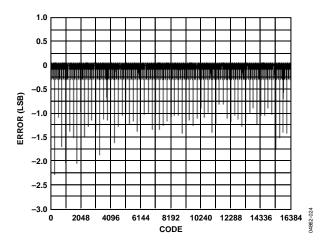

Figure 16. AD9736 DNL, −40°C, 20 mA FS

Figure 17. AD9736 DNL, 25°C, 20 mA FS

Figure 18. AD9736 DNL, 85°C, 20 mA FS

### AD9736 STATIC LINEARITY, 30 mA FULL SCALE

Figure 19. AD9736 INL, -40°C, 30 mA FS

Figure 20. AD9736 INL, 25°C, 30 mA FS

Figure 21. AD9736 INL, 85°C, 30 mA FS

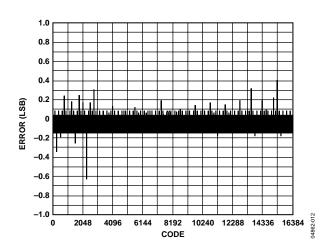

Figure 22. AD9736 DNL, -40°C, 30 mA FS

Figure 23. AD9736 DNL, 25°C, 30 mA FS

Figure 24. AD9736 DNL, 85°C, 30 mA FS

### AD9735 STATIC LINEARITY, 10 mA, 20 mA, 30 mA FULL SCALE

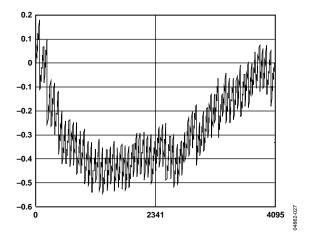

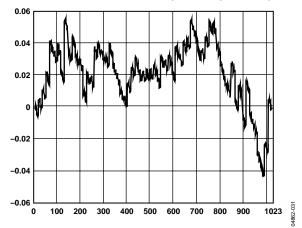

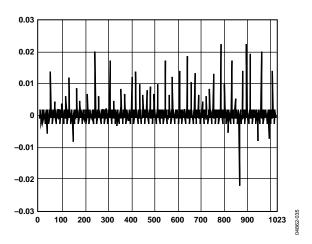

Figure 25. AD9735 INL, 25°C, 10 mA FS

Figure 26. AD9735 INL, 25°C, 20 mA FS

Figure 27. AD9735 INL, 25 °C, 30 mA FS

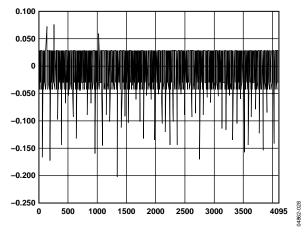

Figure 28. AD9735 DNL, 25°C, 10 mA FS

Figure 29. AD9735 DNL, 25°C, 20 mA FS

Figure 30. AD9735 DNL, 25°C, 30 mA FS

### AD9734 STATIC LINEARITY, 10 mA, 20 mA, 30 mA FULL SCALE

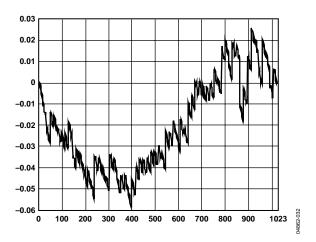

Figure 31. AD9734 INL, 25°C, 10 mA FS

Figure 32. AD9734 INL, 25°C, 20 mA FS

Figure 33. AD9734 INL, 25°C, 30 mA FS

Figure 34. AD9734 DNL, 25°C, 10 mA FS

Figure 35. AD9734 DNL, 25℃, 20 mA FS

Figure 36. AD9734 DNL, 25°C, 30 mA FS

### AD9736 POWER CONSUMPTION, 20 mA FULL SCALE

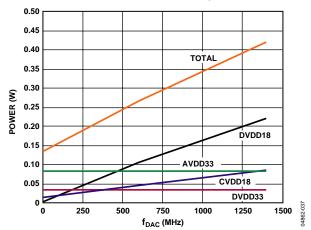

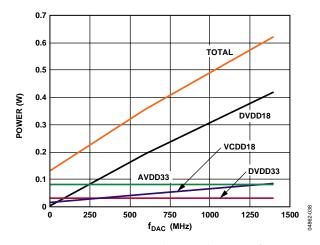

Figure 37. AD9736 1× Mode Power vs.  $f_{DAC}$  at 25°C

Figure 38. AD9736, 2× Interpolation Mode Power vs. f<sub>DAC</sub> at 25°C

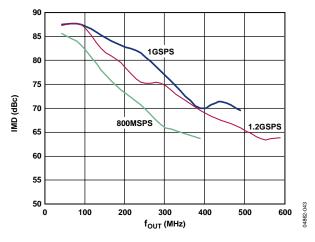

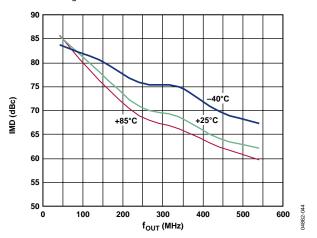

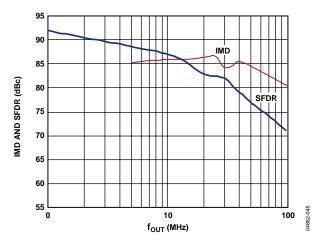

### **AD9736 DYNAMIC PERFORMANCE, 20 mA FULL SCALE**

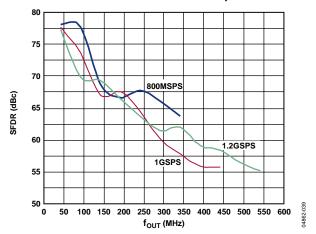

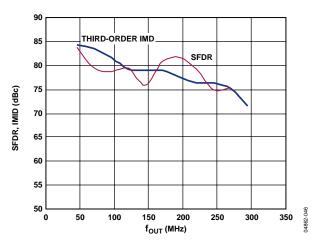

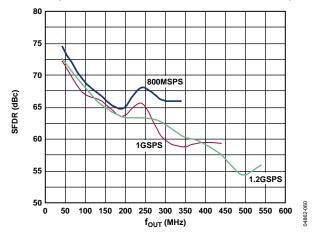

Figure 39. AD9736 SFDR vs. four over fDAC at 25°C

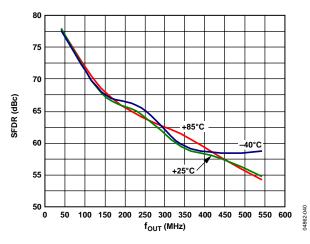

Figure 40. AD9736 SFDR vs. f<sub>OUT</sub> over Temperature

Figure 41. AD9736 SFDR vs.  $f_{OUT}$  over 50 parts, 25°C, 1.2 GSPS

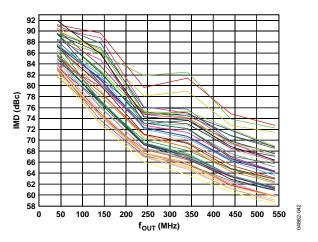

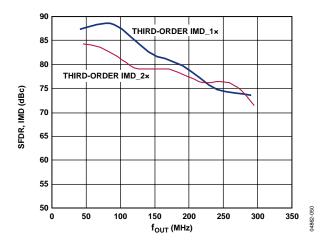

Figure 42. AD9736 IMD vs.  $f_{OUT}$  over 50 parts, 25°C,1.2 GSPS

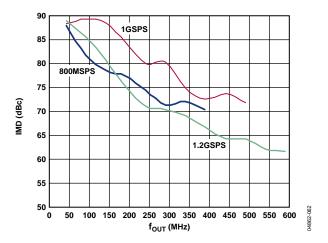

Figure 43. AD9736 IMD vs. fout over fDAC at 25°C

Figure 44. AD9736 IMD vs. fout over Temperature, 1.2 GSPS

Figure 45. AD9736 Low Frequency IMD and SFDR vs. f<sub>OUT</sub>, 25°C, 1.2 GSPS

Figure 46. AD9736 IMD and SFDR vs. f<sub>OUT</sub>, 25°C, 1.2 GSPS, 2× Interpolation

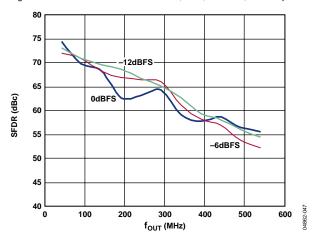

Figure 47. AD9736 SFDR vs. fout over Aout, 25°C, 1.2 GSPS

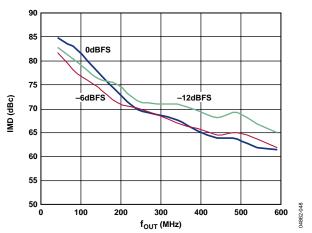

Figure 48. AD9736 IMD vs. f<sub>OUT</sub> over A<sub>OUT</sub>, 25°C, 1.2 GSPS

### **AD9736 DYNAMIC PERFORMANCE, 20 mA FULL SCALE**

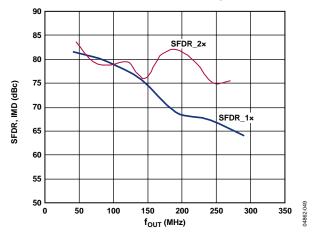

Figure 49. AD9736 SFDR vs. f<sub>OUT</sub>, 25°C, 1.2 GSPS, 1× and 2× Interpolation

Figure 50. AD9736 IMD vs.  $f_{OUT}$ , 25°C, 1.2 GSPS, 1× and 2× Interpolation

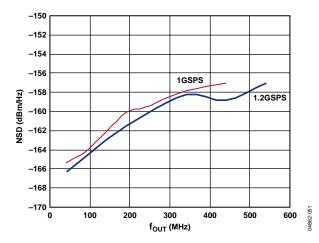

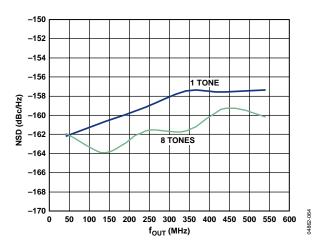

Figure 51. AD9736 1-Tone NSD vs. four over fdac, 25°C

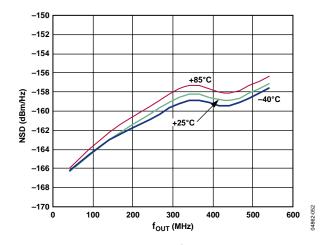

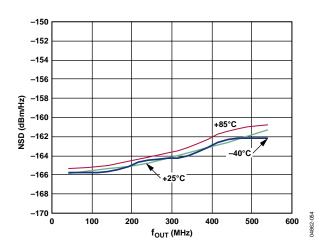

Figure 52. AD9736 1-Tone NSD vs.  $f_{OUT}$  over Temperature, 1.2 GSPS

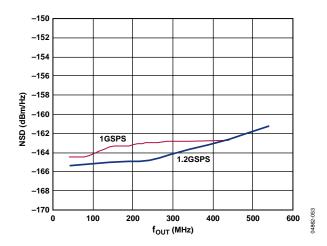

Figure 53. AD9736 8-Tone NSD vs. f<sub>OUT</sub> over f<sub>DAC</sub>, 25°C

Figure 54. AD9736 8-Tone NSD vs.  $f_{OUT}$  over Temperature, 1.2 GSPS

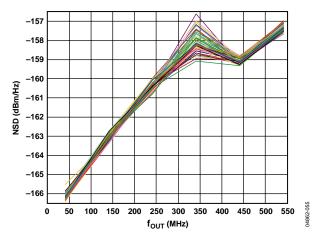

Figure 55. AD9736 1-Tone NSD vs.  $f_{\rm OUT}$  over 50 Parts, 1.2 GSPS, 25°C

Figure 56. AD9736 1-Tone NSD vs. f<sub>OUT</sub> over 50 Parts, 1.2 GSPS, 25℃

## AD9736, AD9735, AD9734 WCDMA ACLR, 20 mA FULL SCALE

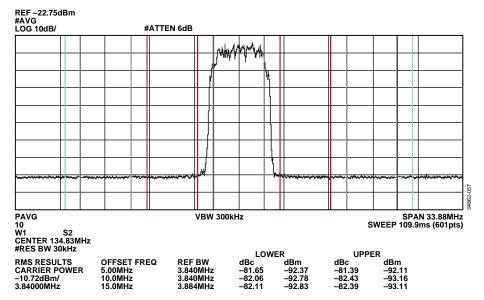

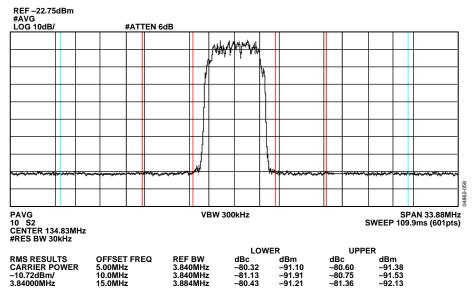

Figure 57. AD9736 WCDMA Carrier at 134.83 MHz,  $f_{DAC} = 491.52$  MSPS

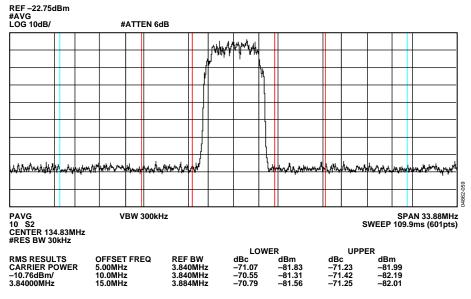

Figure 58. AD9735 WCDMA Carrier at 134.83 MHz,  $f_{DAC} = 491.52$  MSPS

Figure 59. AD9734 WCDMA Carrier at 134.83 MHz,  $f_{DAC} = 491.52$  MSPS

### AD9735, AD9734 DYNAMIC PERFORMANCE, 20 mA FULL SCALE

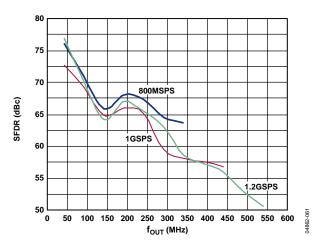

Figure 60. AD9735 SFDR vs. fout over fDAC, 1.2 GSPS

Figure 61. AD9734 SFDR vs. fout over fDAC, 1.2 GSPS

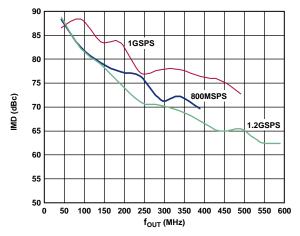

Figure 62. AD9735 IMD vs.  $f_{OUT}$  over  $f_{DAC}$ , 1.2 GSPS

Figure 63. AD9734 IMD vs. fout over fDAC, 1.2 GSPS

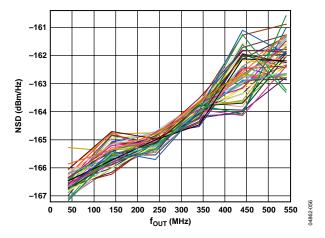

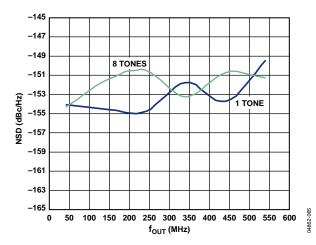

Figure 64. AD9735 NSD vs. f<sub>OUT</sub>, 1.2 GSPS

Figure 65. AD9734 NSD vs. fout, 1.2 GSPS

# **SPI REGISTER MAP**

Write 0 to unspecified or reserved bit locations. Reading these bits returns unknown values.

Table 6. SPI Register Map

| ADR<br>Dec | ADR<br>Hex | Register<br>Name | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3    | Bit 2     | Bit 1    | Bit 0    | Default<br>Hex | Pin Mode<br>Hex |

|------------|------------|------------------|-----------|-----------|-----------|-----------|----------|-----------|----------|----------|----------------|-----------------|

| 0          | 00         | MODE             | SDIO_DIR  | LSBFIRST  | RESET     | LONG_INS  | 2X MODE  | FIFO MODE | DATAFRMT | PD       | 00             | 00              |

| 1          | 01         | IRQ              | LVDS      | SYNC      | CROSS     | RESV'D    | IE_LVDS  | IE_SYNC   | IE_CROSS | RESV'D   | 00             | 00              |

| 2          | 02         | FSC_1            | SLEEP     |           |           |           |          |           | FSC<9>   | FSC<8>   | 02             | 02              |

| 3          | 03         | FSC_2            | FSC<7>    | FSC<6>    | FSC<5>    | FSC<4>    | FSC<3>   | FSC<2>    | FSC<1>   | FSC<0>   | 00             | 00              |

| 4          | 04         | LVDS_CNT1        | MSD<3>    | MSD<2>    | MSD<1>    | MSD<0>    | MHD<3>   | MHD<2>    | MHD<1>   | MHD<0>   | 00             | 00              |

| 5          | 05         | LVDS_CNT2        | SD<3>     | SD<2>     | SD<1>     | SD<0>     | LCHANGE  | ERR_HI    | ERR_LO   | CHECK    | 00             | 00              |

| 6          | 06         | LVDS_CNT3        | LSURV     | LAUTO     | LFLT<3>   | LFLT<2>   | LFLT<1>  | LFLT<0>   | LTRH<1>  | LTRH<0>  | 00             | 00              |

| 7          | 07         | SYNC_CNT1        | FIFOSTAT3 | FIFOSTAT2 | FIFOSTAT1 | FIFOSTAT0 | VALID    | SCHANGE   | PHOF<1>  | PHOF<0>  | 00             | 00              |

| 8          | 08         | SYNC_CNT2        | SSURV     | SAUTO     | SFLT<3>   | SFLT<2>   | SFLT<1>  | SFLT<0>   | RESV'D   | STRH<0>  | 00             | 00              |

| 9          | 09         | RESERVED         |           |           |           |           |          |           |          |          |                |                 |

| 10         | 0A         | CROS_CNT1        |           |           | UPDEL<5>  | UPDEL<4>  | UPDEL<3> | UPDEL<2>  | UPDEL<1> | UPDEL<0> | 00             | 00              |

| 11         | 0B         | CROS_CNT2        |           |           | DNDEL<5>  | DNDEL<4>  | DNDEL<3> | DNDEL<2>  | DNDEL<1> | DNDEL<0> | 00             | 00              |

| 12         | 0C         | RESERVED         |           |           |           |           |          |           |          |          |                |                 |

| 13         | 0D         | RESERVED         |           |           |           |           |          |           |          |          |                |                 |

| 14         | 0E         | ANA_CNT1         | MSEL<1>   | MSEL<0>   |           |           |          | TRMBG<2>  | TRMBG<1> | TRMBG<0> | C0             | C0              |

| 15         | 0F         | ANA_CNT2         | HDRM<7>   | HDRM<6>   | HDRM<5>   | HDRM<4>   | HDRM<3>  | HDRM<2>   | HDRM<1>  | HDRM<0>  | CA             | CA              |

| 16         | 10         | RESERVED         |           |           |           |           |          |           |          |          |                |                 |

| 17         | 11         | BIST_CNT         | SEL<1>    | SEL<0>    | SIG_READ  |           |          | LVDS_EN   | SYNC_EN  | CLEAR    | 00             | 00              |

| 18         | 12         | BIST<7:0>        |           |           |           |           |          |           |          |          |                |                 |

| 19         | 13         | BIST<15:8>       |           |           |           |           |          |           |          |          |                |                 |

| 20         | 14         | BIST<23:16>      |           |           |           |           |          |           |          |          |                |                 |

| 21         | 15         | BIST<31:24>      |           |           |           |           |          |           |          |          |                |                 |

| 22         | 16         | CCLK_DIV         | RESV'D    | RESV'D    | RESV'D    | RESV'D    | CCD<3>   | CCD<2>    | CCD<1>   | CCD<0>   | 00             | 00              |

# **SPI REGISTER DESCRIPTIONS**

Reading these registers returns previously written values for all defined register bits, unless otherwise noted. Reset value for write registers in **bold** text.

## **MODE REGISTER (REG 00)**

| ADR  | Name | Bit 7    | Bit 6   | Bit 5 | Bit 4    | Bit 3   | Bit 2     | Bit 1    | Bit 0 |

|------|------|----------|---------|-------|----------|---------|-----------|----------|-------|

| 0x00 | MODE | SDIO_DIR | LSB/MSB | RESET | LONG_INS | 2× MODE | FIFO MODE | DATAFRMT | PD    |

### **Table 7. MODE Register Bit Descriptions**

| Bit Name  | Read/Write | Description                                                                                                                                                                                                                           |

|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDIO_DIR  | :WRITE ->  | 0, Input only per SPI standard 1, Bidirectional per SPI standard                                                                                                                                                                      |

| LSBFIRST  | : WRITE -> | <ul><li>0, MSB first per SPI standard</li><li>1, LSB first per SPI standard</li><li>NOTE: Only change LSB/MSB order in single-byte instructions to avoid erratic behavior due to bit order errors.</li></ul>                          |

| RESET     | :WRITE->   | <ul> <li>0, Execute software reset of SPI and controllers, reload default register values except registers 0x00 and 0x04</li> <li>1, Set software reset, write 0 on the next (or any following) cycle to release the reset</li> </ul> |

| LONG_INS  | :WRITE ->  | <b>0,</b> Short (single-byte) instruction word 1, Long (two-byte) instruction word, not necessary since the maximum internal address is REG31 (0x1F)                                                                                  |

| 2×_MODE   | :WRITE ->  | <b>0,</b> Disable 2× interpolation filter 1, Enable 2× interpolation filter                                                                                                                                                           |

| FIFO_MODE | :WRITE ->  | <b>0,</b> Disable FIFO synchronization 1, Enable FIFO synchronization                                                                                                                                                                 |

| DATAFRMT  | :WRITE ->  | <b>0,</b> Signed input DATA with midscale = 0x0000<br>1, Unsigned input DATA with midscale = 0x2000                                                                                                                                   |

| PD        | :WRITE ->  | <b>0,</b> Enable LVDS Receiver, DAC, and clock circuitry 1, Power down LVDS Receiver, DAC, and clock circuitry                                                                                                                        |

### **INTERRUPT REQUEST REGISTER (IRQ) (REG 01)**

| Ī | ADR  | Name | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2   | Bit 1    | Bit 0  |  |  |  |  |

|---|------|------|-------|-------|-------|--------|---------|---------|----------|--------|--|--|--|--|

| Ĭ | 0x01 | IRQ  | LVDS  | SYNC  | CROSS | RESV'D | IE_LVDS | IE_SYNC | IE_CROSS | RESV'D |  |  |  |  |

### **Table 8. Interrupt Register Bit Descriptions**

| Bit Name  | Read/Write | Description                                                                                                                                                  |

|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVDS      | : WRITE -> | Don't Care                                                                                                                                                   |

|           | : READ ->  | 0, No active LVDS receiver interrupt 1, Interrupt in LVDS receiver occurred                                                                                  |

| SYNC      | : WRITE -> | Don't Care                                                                                                                                                   |

|           | : READ ->  | 0, No active SYNC logic interrupt<br>1, Interrupt in SYNC logic occurred                                                                                     |

| CROSS     | : WRITE -> | Don't Care                                                                                                                                                   |

|           | : READ ->  | 0, No active CROSS logic interrupt<br>1, Interrupt in CROSS logic occurred                                                                                   |

| IE_LVDS   | : WRITE -> | <ul><li>0, Reset LVDS receiver interrupt and disable future LVDS receiver interrupts</li><li>1, Enable LVDS receiver interrupt to activate IRQ pin</li></ul> |

| IE_SYNC   | : WRITE -> | <ul><li>0, Reset SYNC logic interrupt and disable future SYNC logic interrupts</li><li>1, Enable SYNC logic interrupt to activate IRQ pin</li></ul>          |

| IE_CROSS: | WRITE ->   | <ul><li>0, Reset CROSS logic interrupt and disable future CROSS logic interrupts</li><li>1, Enable CROSS logic interrupt to activate IRQ pin</li></ul>       |

## **FULL SCALE CURRENT (FSC) REGISTER (REGS 02, 03)**

| ADR  | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x02 | FSC_1 | SLEEP  |        |        |        |        |        | FSC<9> | FSC<8> |

| 0x03 | FSC_2 | FSC<7> | FSC<6> | FSC<5> | FSC<4> | FSC<3> | FSC<2> | FSC<1> | FSC<0> |

## Table 9. Full Scale Output Register Bit Descriptions

| Bit Name | Read/Write | Description                            |

|----------|------------|----------------------------------------|

| SLEEP    | :WRITE ->  | 0, Enable DAC output                   |

|          |            | 1, Set DAC output current to 0 mA      |

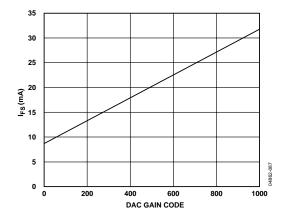

| FSC<9:0> | :WRITE ->  | 0x000, 10 mA full-scale output current |

|          |            | 0x200, 20 mA full-scale output current |

|          |            | 0x3FF, 30 mA full-scale output current |

## LVDS CONTROLLER (LVDS\_CNT) REGISTER (REGS 04, 05, 06)

| ADR  | Name      | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|------|-----------|--------|--------|---------|---------|---------|---------|---------|---------|

| 0x04 | LVDS_CNT1 | MSD<3> | MSD<2> | MSD<1>  | MSD<0>  | MHD<3>  | MHD<2>  | MHD<1>  | MHD<0>  |

| 0x05 | LVDS_CNT2 | SD<3>  | SD<2>  | SD<1>   | SD<0>   | LCHANGE | ERR_HI  | ERR_LO  | CHECK   |

| 0x06 | LVDS_CNT3 | LSURV  | LAUTO  | LFLT<3> | LFLT<2> | LFLT<1> | LFLT<0> | LTRH<1> | LTRH<0> |

### Table 10. LVDS Controller Register Bit Descriptions

| Bit Name   | Read/Write | Description                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| MSD<3:0>   | : WRITE -> | <b>0x0,</b> Set setup delay for the measurement system                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|            | : READ ->  | If (LAUTO = 1) the latest measured value for the setup delay If (LAUTO = 0) read back of the last SPI write to this bit                                                                                                                                      |  |  |  |  |  |  |  |

| MHD<3:0>   | : WRITE -> | 0x0, Set hold delay for the measurement system                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|            | : READ ->  | If ( LAUTO = 1) the latest measured value for the hold delay If ( LAUTO = 0) read back of the last SPI write to this bit                                                                                                                                     |  |  |  |  |  |  |  |

| SD<3:0>    | : WRITE->  | 0x0, Set sample delay                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|            | : READ ->  | If ( LAUTO = 1) the result of a measurement cycle is stored in this register If ( LAUTO = 0) read back of the last SPI write to this bit                                                                                                                     |  |  |  |  |  |  |  |

| LCHANGE    | : READ ->  | 0, No change from previous measurement 1, Change in value from the previous measurement NOTE: The average filter and the threshold detection are not applied to this bit                                                                                     |  |  |  |  |  |  |  |

| ERR_HI     | : READ ->  | One of the 15 LVDS inputs is above the input voltage limits of the IEEE reduce link specification.                                                                                                                                                           |  |  |  |  |  |  |  |

| ERR_LO     | : READ ->  | One of the 15 LVDS inputs is below the input voltage limits of the IEEE reduced link specification.                                                                                                                                                          |  |  |  |  |  |  |  |

| CHECK      | : READ ->  | 0, Phase measurement—sampling in the previous or following DATA cycle 1, Phase measurement—sampling in the correct DATA cycle                                                                                                                                |  |  |  |  |  |  |  |

| LSURV      | : WRITE -> | <ul> <li>0, The controller stops after completion of the current measurement cycle</li> <li>1, Continuous measurements are taken and an interrupt is issued if the clock alignment drifts beyond the threshold value</li> </ul>                              |  |  |  |  |  |  |  |

| LAUTO:     | WRITE ->   | 0, Sample delay is not automatically updated 1, Continuously starts measurement cycles and updates the sample delay according to the measurement NOTE: LSURV (Reg 06, Bit 7) must be set to 1 and the LVDS IRQ (Reg 01 Bit 3) must be set to 0 for AUTO mode |  |  |  |  |  |  |  |

| LFLT<3:0>  | : WRITE -> | <b>0x0,</b> Average filter length, Delay = Delay + Delta Delay / 2^ LFLT<3:0>, values greater than 12 (0x0C) are clipped to 12                                                                                                                               |  |  |  |  |  |  |  |

| LTRH<2:0>: | : WRITE -> | 000, Set auto update threshold values                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

## SYNC CONTROLLER (SYNC\_CNT) REGISTER (REGS 07, 08)

| ADR  | Name      | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|------|-----------|-----------|-----------|-----------|-----------|---------|---------|---------|---------|

| 0x07 | SYNC_CNT1 | FIFOSTAT3 | FIFOSTAT2 | FIFOSTAT1 | FIFOSTAT0 | VALID   | SCHANGE | PHOF<1> | PHOF<0> |

| 0x08 | SYNC_CNT2 | SSURV     | SAUTO     | SFLT<3>   | SFLT<2>   | SFLT<1> | SFLT<0> | RESV'D  | STRH<0> |

### **Table 11. SYNC Controller Register Bit Descriptions**

| Bit Name      | Read/Write | Description                                                                                                                                                                                                                                                                   |

|---------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIFOSTAT<2:0> | : READ ->  | Position of FIFO read counter, range from 0 to 7                                                                                                                                                                                                                              |

| FIFOSTAT<3>   | : READ ->  | 0, SYNC logic OK<br>1, Error in SYNC logic                                                                                                                                                                                                                                    |

| VALID         | : READ ->  | 0, FIFOSTAT<3:0> is not valid yet 1, FIFOSTAT<3:0> is valid after a reset                                                                                                                                                                                                     |

| SCHANGE       | :READ ->   | 0, No change in FIFOSTAT<3:0> 1, FIFOSTAT<3:0> has changed since the previous measurement cycle when SSURV = 1 (surveillance mode active)                                                                                                                                     |

| PHOF<1:0>     | : WRITE -> | 00, Change the readout counter                                                                                                                                                                                                                                                |

|               | :READ ->   | Current setting of the readout counter (PHOF<1:0>) in surveillance mode (SSURV = 1) after an interrupt Current calculated optimal readout counter value in AUTO mode (SAUTO = 1)                                                                                              |

| SSURV:        | WRITE ->   | <ul> <li>0, The controller stops after completion of the current measurement cycle</li> <li>1, Continuous measurements are taken and an interrupt is issued if the readout counter drifts beyond the threshold value</li> </ul>                                               |

| SAUTO         | : WRITE -> | 0, Readout counter (PHOF<3:0>) is not automatically updated 1, Continuously starts measurement cycles and updates the readout counter according to the measurement NOTE: SSURV (Reg 08 Bit 7) must be set to 1 and the SYNC IRQ (Reg 01 Bit 2) must be set to 0 for AUTO mode |

| SFLT<3:0>     | : WRITE -> | <b>0x0,</b> Average filter length, FIFOSTAT = FIFOSTAT + Delta FIFOSTAT/2 ^ SFLT<3:0>, values greater than 12 (0x0C) are clipped to 12                                                                                                                                        |

| STRH<0>       | : WRITE -> | <b>0,</b> If FIFOSTAT<2:0> = 0   7, generate a SYNC interrupt 1, If FIFOSTAT<2:0> = 0   1   6   7, generate a SYNC interrupt                                                                                                                                                  |

## CROSS CONTROLLER (CROS\_CNT) REGISTER (REGS 10, 11)

| ADR  | Name      | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|------|-----------|-------|-------|----------|----------|----------|----------|----------|----------|

| 0x0A | CROS_CNT1 | _     | 1     | UPDEL<5> | UPDEL<4> | UPDEL<3> | UPDEL<2> | UPDEL<1> | UPDEL<0> |

| 0x0B | CROS_CNT2 | _     | ı     | DNDEL<5> | DNDEL<4> | DNDEL<3> | DNDEL<2> | DNDEL<1> | DNDEL<0> |

## **Table 12. Cross Controller Register Description**

| Bit Name   | Read/Write | Description                                                                                         |

|------------|------------|-----------------------------------------------------------------------------------------------------|

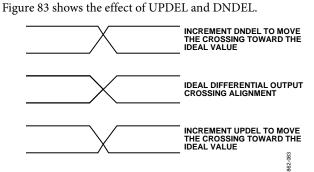

| UPDEL<5:0> | : WRITE -> | <b>0x00,</b> Move the differential output stage switching point up, set to 0 if DNDEL is non-zero   |

| DNDEL<5:0> | : WRITE -> | <b>0x00,</b> Move the differential output stage switching point down, set to 0 if UPDEL is non-zero |

## ANALOG CONTROL (ANA\_CNT) REGISTER (REGS 14, 15)

| ADR  | Name     | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|------|----------|---------|---------|---------|---------|---------|----------|----------|----------|

| 0x0E | ANA_CNT1 | MSEL<1> | MSEL<0> | -       | -       | -       | TRMBG<2> | TRMBG<1> | TRMBG<0> |

| 0x0F | ANA_CNT2 | HDRM<7> | HDRM<6> | HDRM<5> | HDRM<4> | HDRM<3> | HDRM<2>  | HDRM<1>  | HDRM<0>  |

## **Table 13. Analog Control Register Bit Descriptions**

| Bit Name   | Read/Write | Description                                                                                                                                                                                                                                                                          |

|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

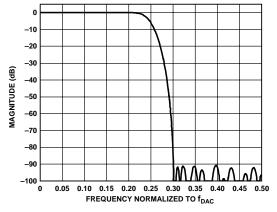

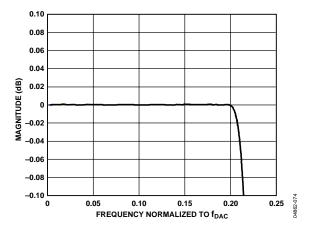

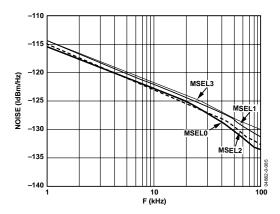

| MSEL<1:0>  | : WRITE -> | 00, Mirror roll off frequency control = bypass 01, Mirror roll off frequency control = narrowest bandwidth 10, Mirror roll off frequency control = medium bandwidth 11, Mirror roll off frequency control = widest bandwidth NOTE: See plot in the Analog Control Registers section. |

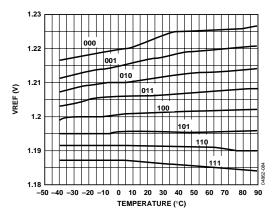

| TRMBG<2:0> | : WRITE -> | <b>000,</b> Band gap temperature characteristic trim NOTE: See the plot in the Analog Control Registers section.                                                                                                                                                                     |

| HDRM<7:0>  | : WRITE -> | OxCA, Output stack headroom control HDRM<7:4> set reference offset from AVDD33 (VCAS centering) HDRM<3:0> set overdrive (current density) trim (temperature tracking) Note: Set to 0xCA for optimum performance                                                                      |

## BUILT-IN SELF TEST CONTROL (BIST\_CNT) REGISTERS (REGS 17, 18, 19, 20, 21)

| ADR  | Name        | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|------|-------------|----------|----------|----------|----------|----------|----------|----------|----------|

| 0x11 | BIST_CNT    | SEL<1>   | SEL<0>   | SIG_READ |          |          | LVDS_EN  | SYNC_EN  | CLEAR    |

| 0x12 | BIST<7:0>   | BIST<7>  | BIST<6>  | BIST<5>  | BIST<4>  | BIST<3>  | BIST<2>  | BIST<1>  | BIST<0>  |

| 0x13 | BIST<15:8>  | BIST<15> | BIST<14> | BIST<13> | BIST<12> | BIST<11> | BIST<10> | BIST<9>  | BIST<8>  |

| 0x14 | BIST<23:16> | BIST<23> | BIST<22> | BIST<21> | BIST<20> | BIST<19> | BIST<18> | BIST<17> | BIST<16> |

| 0x15 | BIST<31:24> | BIST<31> | BIST<30> | BIST<29> | BIST<28> | BIST<27> | BIST<26> | BIST<25> | BIST<24> |

### **Table 14. BIST Register Bit Descriptions**

| Bit Name   | Read/Write | Description                                                                                                                                                                                                                     |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL<1:0>   | : WRITE -> | 00, Write result of the LVDS Phase 1 BIST to BIST<31:0> 01, Write result of the LVDS Phase 2 BIST to BIST<31:0> 10, Write result of the SYNC Phase 1 BIST to BIST<31:0> 11, Write result of the SYNC Phase 2 BIST to BIST<31:0> |

| SIG_READ   | : WRITE -> | 0, No action 1, Enable BIST signature readback                                                                                                                                                                                  |

| LVDS_EN    | WRITE->    | 0, No action 1, Enable LVDS BIST                                                                                                                                                                                                |

| SYNC_EN    | : WRITE -> | 0, No action 1, Enable SYNC BIST                                                                                                                                                                                                |

| CLEAR      | : WRITE -> | 0, No action<br>1, Clear all BIST registers                                                                                                                                                                                     |

| BIST<31:0> | : READ ->  | Results of the built-in self test                                                                                                                                                                                               |

# CONTROLLER CLOCK PREDIVIDER (CCLK\_DIV) READING REGISTER (REG 22)

| ADR  | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------|----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x16 | CCLK_DIV | RESV'D | RESV'D | RESV'D | RESV'D | CCD<3> | CCD<2> | CCD<1> | CCD<0> |

## **Table 15. Clock Predivider Register Bit Descriptions**

| Bit Name | Read/Write | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCD<3:0> | : WRITE -> | Ox0, Controller clock = DACCLK/16  0x1, Controller clock = DACCLK/32  0x2, Controller clock = DACCLK/64  0xF, Controller clock = DACCLK/524288  NOTE: The 100 MHz to 1.2 GHz DACCLK must be divided to less than 10 MHz for correct operation.  CCD<3:0> must be programmed to divide the DACCLK so that this relationship is not violated.  Controller Clock = DACCLK/(2 ^ ( CCD<3:0> + 4 )) |

## THEORY OF OPERATION

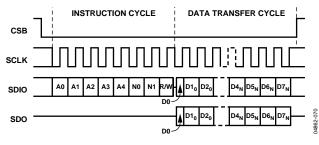

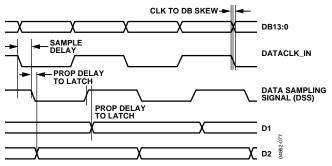

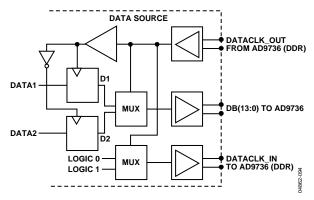

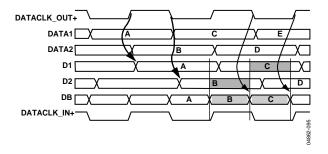

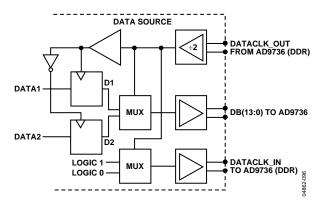

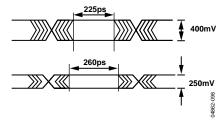

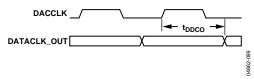

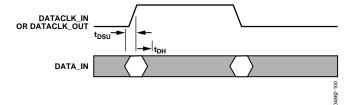

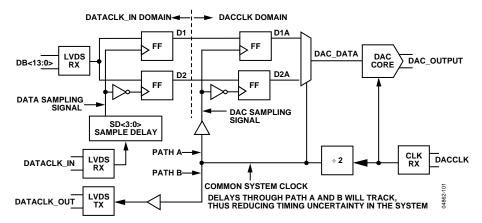

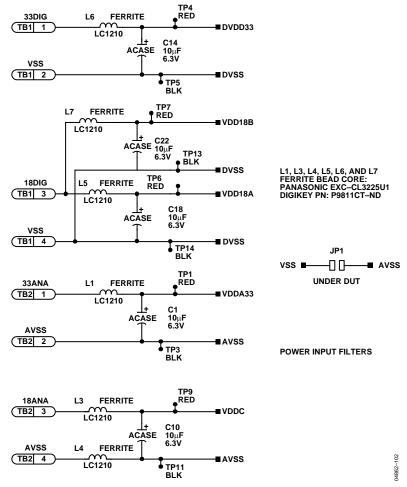

The AD9736, AD9735, and AD9734 are 14-, 12-, and 10-bit DACs that run at an update rate up to 1.2 GSPS. Input data can be accepted up to the full 1.2 GSPS rate, or a 2× interpolation filter may be enabled (2× mode) allowing full speed operation with a 600 MSPS input data rate. DATA and DATACLK\_IN inputs are parallel LVDS, meeting the IEEE reduced swing LVDS specifications with the exception of input hysteresis. The DATACLK\_IN input runs at one-half the input DATA rate in a double data rate (DDR) format. Each edge of DATACLK\_IN is used to transfer DATA into the AD9736, as shown in Figure 77.