# HDSL/MDSL ANALOG FRONT END

## FEATURES

- COMPLETE ANALOG INTERFACE

- T1, E1, AND MDSL OPERATION

- CLOCK SCALEABLE SPEED

- SINGLE CHIP SOLUTION

- +5V ONLY (5V OR 3.3V DIGITAL)

- 250mW POWER DISSIPATION

- 48-PIN SSOP

- -40°C TO +85°C OPERATION

#### CLARK WWW

### DESCRIPTION

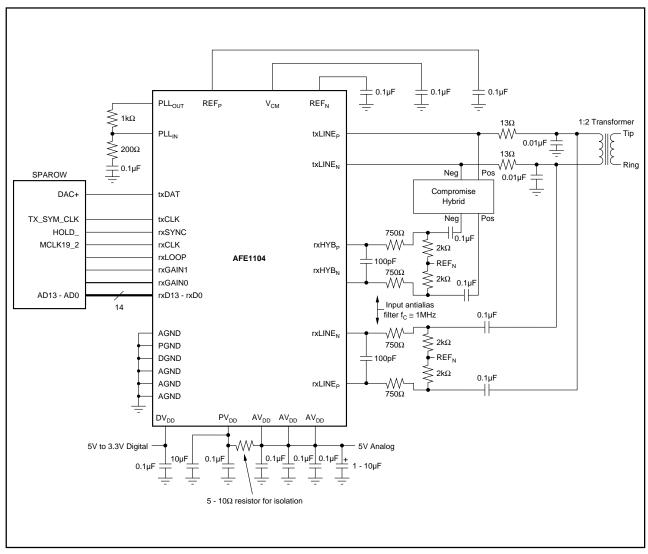

Burr-Brown's Analog Front End greatly reduces the size and cost of an HDSL or MDSL system by providing all of the active analog circuitry needed to connect PairGain Technologies SPAROW HDSL digital signal processor to an external compromise hybrid and a 1:2 HDSL line transformer. All internal filter responses as well as the pulse former output scale with clock frequency—allowing the AFE1104 to operate over a range of bit rates from 196kbps to 1.168Mbps.

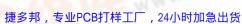

Functionally, this unit is separated into a transmit and a receive section. The transmit section generates, filters, and buffers outgoing 2B1Q data. The receive section filters and digitizes the symbol data received on the telephone line and passes it to the SPAROW. The HDSL Analog Interface is a monolithic device fabricated on  $0.6\mu$ CMOS. It operates on a single +5V supply. It is housed in a 48-pin SSOP package.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

Typical at 25°C,  $AV_{DD}$  = +5V,  $DV_{DD}$  = +3.3V,  $f_{tx}$  = 584kHz (E1 rate), unless otherwise specified.

|                                               |                                                                   |                             | AFE1104E             |                               |                     |

|-----------------------------------------------|-------------------------------------------------------------------|-----------------------------|----------------------|-------------------------------|---------------------|

| PARAMETER                                     | COMMENTS                                                          | MIN                         | ТҮР                  | MAX                           | UNITS               |

| RECEIVE CHANNEL                               |                                                                   |                             |                      |                               |                     |

| Number of Inputs                              | Differential                                                      | 2                           |                      |                               |                     |

| Input Voltage Range                           | Balanced Differential <sup>(1)</sup>                              |                             | ±3.0                 |                               | V                   |

| Common-Mode Voltage                           | 1.5V CMV Recommended                                              |                             | +1.5                 |                               | V                   |

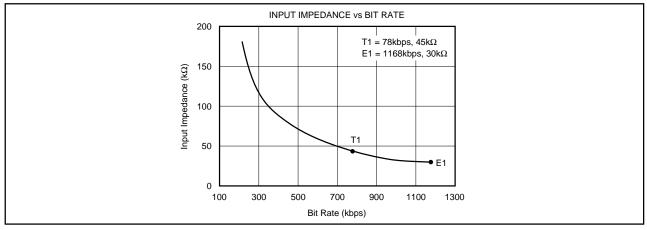

| Input Impedance                               | All Inputs                                                        | See Tv                      | pical Performar      |                               | v                   |

| Input Capacitance                             | Air inputs                                                        | 000 19                      |                      |                               | pF                  |

| Input Gain Matching                           | Line Input vs Hybrid Input                                        |                             | +2                   |                               | рі<br>%             |

| Resolution                                    | Line input vs Hybrid input                                        | 14                          | <u></u>              |                               | Bits                |

| Programmable Gain                             | Four Coincy OdP 2 2EdP 6dP and 0dP                                | 0                           |                      | 9                             | dB                  |

|                                               | Four Gains: 0dB, 3.25dB, 6dB, and 9dB                             | 0                           | 6                    | 9                             | Symbol              |

| Settling Time for Gain Change                 |                                                                   |                             | 0                    |                               | Periods             |

|                                               | Testad et Fach Osia Deser                                         |                             |                      |                               | %FSR <sup>(2)</sup> |

| Gain + Offset Error                           | Tested at Each Gain Range                                         |                             | 5                    |                               | %FSR(2)             |

| Output Data Coding                            |                                                                   |                             | wo's Compleme        |                               |                     |

| Output Data Rate, rxSYNC <sup>(3)</sup>       |                                                                   | 98                          |                      | 584                           | kHz                 |

| TRANSMIT CHANNEL                              |                                                                   |                             |                      |                               |                     |

| Transmit Symbol Rate, f <sub>tx</sub>         |                                                                   | 98                          |                      | 584                           | kHz                 |

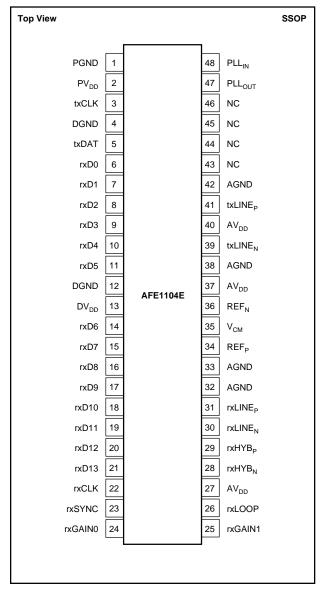

| T1 Transmit –3dB Point                        | Bellcore TA-NWT-3017 Compliant                                    |                             | 196                  |                               | kHz                 |

| T1 Rate Power Spectral Density <sup>(4)</sup> |                                                                   | See Ty                      | pical Performar      | nce Curves                    |                     |

| E1 Transmit –3dB Point                        | ETSI RTR/TM-03036 Compliant                                       |                             | 292                  |                               | kHz                 |

| E1 Rate Power Spectral Density <sup>(4)</sup> |                                                                   | See Ty                      | pical Performar      | nce Curves                    |                     |

| Transmit Power <sup>(4, 5)</sup>              |                                                                   | 13                          | Ì                    | 14                            | dBm                 |

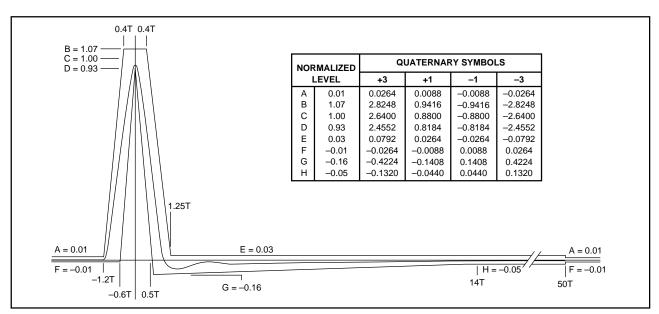

| Pulse Output                                  |                                                                   | See Ty                      | ,<br>pical Performar | ce Curves                     |                     |

| Common-Mode Voltage, V <sub>CM</sub>          |                                                                   |                             | AV <sub>DD</sub> /2  | 1                             | V                   |

| Output Resistance <sup>(6)</sup>              | DC to 1MHz                                                        |                             | 1                    |                               | Ω                   |

|                                               |                                                                   |                             |                      |                               |                     |

|                                               | rxGAIN = 0dB, Loopback Enabled                                    |                             |                      | -67                           | dB                  |

|                                               | rxGAIN = 0dB, Loopback Enabled $rxGAIN = 0dB$ , Loopback Disabled |                             |                      | _67                           | dB                  |

|                                               | rxGAIN = 3.25dB, Loopback Disabled                                |                             |                      | 67<br>69                      | dВ                  |

|                                               | rxGAIN = 6dB, Loopback Disabled                                   |                             |                      |                               | dВ                  |

|                                               | rxGAIN = 6dB, Loopback Disabled                                   |                             |                      | -71<br>-73                    | dВ                  |

| DIGITAL INTERFACE <sup>(6)</sup>              |                                                                   | _                           |                      | 10                            | QD                  |

| Logic Levels                                  |                                                                   |                             |                      |                               |                     |

| •                                             | 11 1 4 10 10                                                      |                             |                      |                               | V                   |

| V <sub>IH</sub>                               | $ I_{\rm H}  < 10\mu{\rm A}$                                      | DV <sub>DD</sub> -1<br>-0.3 |                      | DV <sub>DD</sub> +0.3<br>+0.8 | V                   |

| V <sub>IL</sub>                               | I <sub>IL</sub>   < 10μΑ                                          |                             |                      | +0.8                          |                     |

| V <sub>OH</sub>                               | $I_{OH} = -20\mu A$                                               | DV <sub>DD</sub> -0.5       |                      |                               | V                   |

| V <sub>OL</sub>                               | $I_{OL} = 20\mu A$                                                |                             |                      | +0.4                          | V                   |

| Receive Channel Interface                     |                                                                   |                             |                      | 045                           |                     |

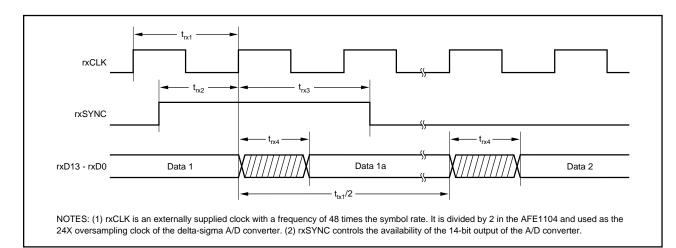

| t <sub>rx1</sub>                              | rxCLK Period                                                      | 35                          |                      | 215                           | ns                  |

|                                               | rxCLK Duty Cycle                                                  | 45                          |                      | 55                            | %                   |

| t <sub>rx2</sub>                              | rxSYNC to rxCLK Setup Time                                        | 10                          |                      |                               | ns                  |

| t <sub>rx3</sub>                              | rxCLK to rxSYNC Hold Time                                         | 10                          |                      |                               | ns                  |

| t <sub>rx4</sub>                              | rxCLK to rxD13 - rxD0 Delay                                       | 1                           |                      | 50                            | ns                  |

| Transmit Channel Interface                    |                                                                   | 1                           |                      |                               |                     |

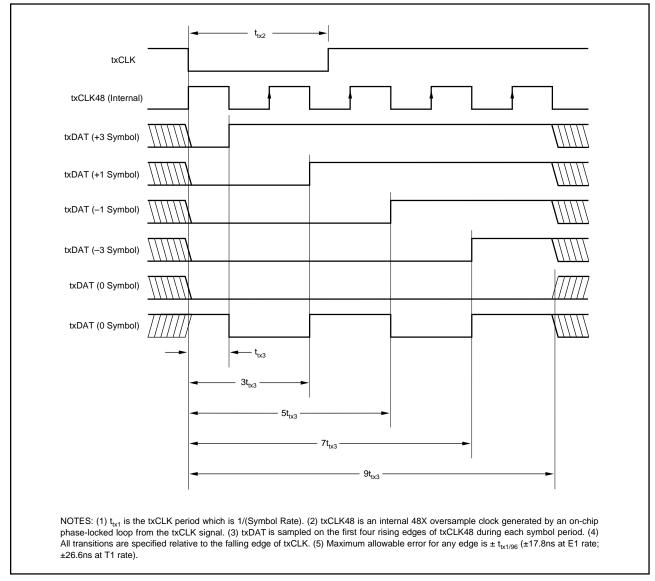

| t <sub>tx1</sub>                              | txCLK Period                                                      | 1.7                         |                      | 10.2                          | μs                  |

| t <sub>tx2</sub>                              | txCLK Pulse Width                                                 | 50                          |                      |                               | ns                  |

| t <sub>tx3</sub>                              | Basic txDAT Pulse Unit                                            |                             | t <sub>tx1</sub> /96 |                               | ns                  |

| POWER                                         |                                                                   |                             |                      |                               |                     |

| Analog Power Supply Voltage                   | Specification                                                     |                             | 5                    |                               | V                   |

| Analog Power Supply Voltage                   | Operating Range                                                   | 4.75                        |                      | 5.25                          | V                   |

| Digital Power Supply Voltage                  | Specification                                                     |                             | 3.3                  |                               | V                   |

| Digital Power Supply Voltage                  | Operating Range                                                   | 3.15                        |                      | 5.25                          | V                   |

| Power Dissipation <sup>(4, 5, 8)</sup>        | $DV_{DD} = 3.3V$                                                  |                             | 250                  |                               | mW                  |

| Power Dissipation <sup>(4, 5, 8)</sup>        | $DV_{DD} = 5V$                                                    | 1                           | 300                  |                               | mW                  |

| PSRR                                          |                                                                   | 60                          |                      |                               | dB                  |

|                                               |                                                                   | +                           |                      |                               |                     |

|                                               |                                                                   | -40                         |                      | +85                           | °C                  |

| Operating <sup>(6)</sup>                      |                                                                   | -40                         |                      | CO+                           | -U                  |

NOTES: (1) With a balanced differential signal, the positive input is  $180^{\circ}$  out of phase with the negative input, therefore the actual voltage swing about the common mode voltage on each pin is  $\pm 1.5V$  to achieve a differential input range of  $\pm 3.0V$  or 6Vp-p. (2) FSR is Full-Scale Range. (3) The output data is available at twice the symbol rate with interpolated values. (4) With a pseudo-random equiprobable sequence of HDSL pulses; 13.5dBm applied to the transformer (27dBm output from txLINE<sub>p</sub> and txLINE<sub>p</sub>). (5) See the Discussion of Specifications section of this data sheet for more information. (6) Guaranteed by design and characterization. (7) Uncanceled Echo is a measure of the total analog errors in the transmitter and receiver sections including the effect of non-linearity and noise. See the Discussion of Specifications section includes only the power dissipated within the component and does not include power dissipated in the external loads. See the Discussion of Specifications section for more information.

#### **PIN DESCRIPTIONS**

| PIN # | TYPE   | NAME                | DESCRIPTION                                                      |  |

|-------|--------|---------------------|------------------------------------------------------------------|--|

| 1     | Ground | PGND                | Analog Ground for PLL                                            |  |

| 2     | Power  | PVpp                | Analog Supply (+5V) for PLL                                      |  |

| 3     | Input  | txCLK               | Transmit Symbol Clock (392kHz for T1, 584kHz for E1)             |  |

| 4     | Ground | DGND                | Digital Ground                                                   |  |

| 5     | Input  | txDAT               | DAC+ Line from SPAROW                                            |  |

| 6     | Output | rxD0                | ADC Output Bit-0                                                 |  |

| 7     | Output | rxD1                | ADC Output Bit-1                                                 |  |

| 8     | Output | rxD2                | ADC Output Bit-2                                                 |  |

| 9     | Output | rxD3                | ADC Output Bit-3                                                 |  |

| 10    | Output | rxD4                | ADC Output Bit-4                                                 |  |

| 11    | Output | rxD5                | ADC Output Bit-5                                                 |  |

| 12    | Ground | DGND                | Digital Ground                                                   |  |

| 13    | Power  | DV <sub>DD</sub>    | Digital Supply (+3.3V to +5V)                                    |  |

| 14    | Output | rxD6                | ADC Output Bit-6                                                 |  |

| 15    | Output | rxD7                | ADC Output Bit-7                                                 |  |

| 16    | Output | rxD8                | ADC Output Bit-8                                                 |  |

| 17    | Output | rxD9                | ADC Output Bit-9                                                 |  |

| 18    | Output | rxD10               | ADC Output Bit-10                                                |  |

| 19    | Output | rxD11               | ADC Output Bit-11                                                |  |

| 20    | Output | rxD12               | ADC Output Bit-12                                                |  |

| 21    | Output | rxD13               | ADC Output Bit-13                                                |  |

| 22    | Input  | rxCLK               | A/D Clock (18.816MHz for T1, 28.03MHz for E1)                    |  |

| 23    | Input  | rxSYNC              | ADC Sync Signal (392kHz for T1, 584kHz for E1)                   |  |

| 24    | Input  | rxGAIN0             | Receive Gain Control Bit-0                                       |  |

| 25    | Input  | rxGAIN1             | Receive Gain Control Bit-1                                       |  |

| 26    | Input  | rxLOOP              | Loopback Control Signal (loopback is enabled by positive signal) |  |

| 27    | Power  | AV <sub>DD</sub>    | Analog Supply (+5V)                                              |  |

| 28    | Input  | rxHYB <sub>N</sub>  | Negative Input from Hybrid Network                               |  |

| 29    | Input  | rxHYB <sub>P</sub>  | Positive Input from Hybrid Network                               |  |

| 30    | Input  | rxLINE <sub>N</sub> | Negative Line Input                                              |  |

| 31    | Input  | rxLINE <sub>P</sub> | Positive Line Input                                              |  |

| 32    | Ground | AGND                | Analog Ground                                                    |  |

| 33    | Ground | AGND                | Analog Ground                                                    |  |

| 34    | Output | REF <sub>P</sub>    | Positive Reference Output, Nominally 3.5V                        |  |

| 35    | Output | V <sub>CM</sub>     | Common-Mode Voltage (buffered), Nominally 2.5V                   |  |

| 36    | Output | REF <sub>N</sub>    | Negative Reference Output, Nominally 1.5V                        |  |

| 37    | Power  | AV <sub>DD</sub>    | Analog Supply (+5V)                                              |  |

| 38    | Ground | AGND                | Analog Ground                                                    |  |

| 39    | Output | txLINE <sub>N</sub> | Transmit Line Output Negative                                    |  |

| 40    | Power  | AV <sub>DD</sub>    | Analog Supply (+5V)                                              |  |

| 41    | Output | txLINE <sub>P</sub> | Transmit Line Output Positive                                    |  |

| 42    | Ground | AGND                | Analog Ground                                                    |  |

| 43    | NC     | NC                  | Connection to Ground Recommended                                 |  |

| 44    | NC     | NC                  | Connection to Ground Recommended                                 |  |

| 45    | NC     | NC                  | Connection to Ground Recommended                                 |  |

| 46    | NC     | NC                  | Connection to Ground Recommended                                 |  |

| 47    | Output | PLL <sub>OUT</sub>  | PLL Filter Output                                                |  |

| 48    | Input  | PLLIN               | PLL Filter Input                                                 |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **PIN CONFIGURATION**

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Inputs: Current                                                        |

|-------------------------------------------------------------------------------|

| Voltage AGND –0.3V to AV <sub>DD</sub> +0.3V                                  |

| Analog Outputs Short Circuit to Ground (+25°C) Continuous                     |

| AV <sub>DD</sub> to AGND0.3V to 6V                                            |

| PV <sub>DD</sub> to PGND0.3V to 6V                                            |

| DV <sub>DD</sub> to DGND0.3V to 6V                                            |

| PLL <sub>IN</sub> or PLL <sub>OUT</sub> to PGND0.3V to PV <sub>DD</sub> +0.3V |

| Digital Input Voltage to DGND0.3V to DV <sub>DD</sub> +0.3V                   |

| Digital Output Voltage to DGND0.3V to DV <sub>DD</sub> +0.3V                  |

| AGND, DGND, PGND Differential Voltage0.3V                                     |

| Junction Temperature (T <sub>J</sub> ) +150°C                                 |

| Storage Temperature Range40°C to +125°C                                       |

| Lead Temperature (soldering, 3s) +260°C                                       |

| Power Dissipation 700mW                                                       |

#### **PACKAGE/ORDERING INFORMATION**

| PRODUCT  | PACKAGE             | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | TEMPERATURE<br>RANGE |

|----------|---------------------|---------------------------------------------|----------------------|

| AFE1104E | 48-Pin Plastic SSOP | 333                                         | -40°C to +85°C       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **TYPICAL PERFORMANCE CURVES**

### At Output of Pulse Transformer

Typical at 25°C,  $AV_{DD}$  = +5V,  $DV_{DD}$  = +3.3V, unless otherwise specified.

CURVE 1. Upper Bound of Power Spectral Density Measured at the Transformer Output.

## THEORY OF OPERATION

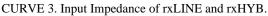

The transmit channel consists of a switched-capacitor pulse forming network followed by a differential line driver. The pulse forming network receives symbol data from SPAROW'S DAC+ line and generates a 2B1Q output waveform. The output meets the pulse mask and power spectral density requirements defined in European Telecommunications Standards Institute document RTR/TM-03036 for E1 mode and in sections 6.2.1 and 6.2.2.1 of Bellcore technical advisory TA-NWT-001210 for T1 mode. The differential line driver uses a composite output stage combining class B operation (for high efficiency driving large signals) with class AB operation (to minimize crossover distortion).

The receive channel is designed around a fourth-order delta sigma A/D converter. It includes a difference amplifier that can be used with an external compromise hybrid for first order analog crosstalk reduction. A programmable gain amplifier with gains of 0dB to +9dB is also included. The delta sigma modulator operating at a 24X oversampling ratio produces 14 bits of resolution at output rates up to 584kHz. The basic functionality of the AFE1104 is illustrated in Figure 1 shown below.

The receive channel operates by summing the two differential inputs, one from the line (rxLINE) and the other from the compromise hybrid (rxHYB). The connection of these two inputs so that the hybrid signal is subtracted from the line signal is described in the paragraph titled "Echo Cancellation in the AFE". The equivalent gain for each input in the difference amp is 1. The resulting signal then passes to a programmable gain amplifier which can be set for gains of 0dB through 9dB. The ADC converts the signal to a 14-bit digital word, rxD13 - rxD0.

#### rxLOOP INPUT

rxLOOP is the loopback control signal. When enabled, the  $rxLINE_{P}$  and  $rxLINE_{N}$  inputs are disconnected from the

AFE. The  $rxHYB_P$  and  $rxHYB_N$  inputs remain connected. Loopback is enabled by applying a positive signal (Logic 1) to rxLOOP.

#### ECHO CANCELLATION IN THE AFE

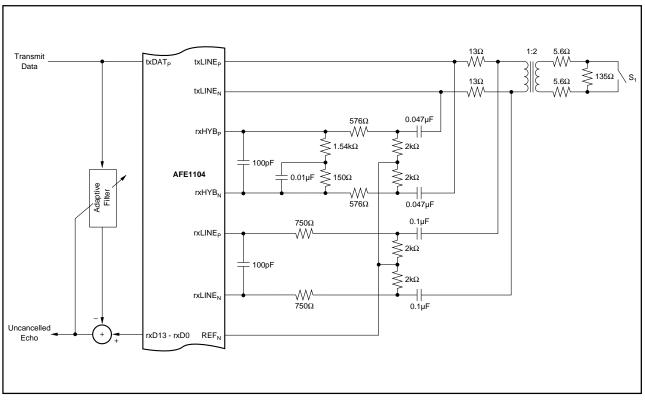

The rxHYB input is designed to be subtracted from the rxLINE input for first order echo cancellation. To accomplish this, note that the rxLINE input is connected to the same polarity signal at the transformer (positive to positive and negative to negative) while the rxHYB input is connected to opposite polarity through the compromise hybrid (negative to positive and positive to negative) as shown in Figure 2.

#### **RECEIVE DATA CODING**

The data from the receive channel A/D converter is in two's complement code.

| ANALOG INPUT        | OUTPUT CODE (rxD13 - rxD0) |

|---------------------|----------------------------|

| Positive Full Scale | 011111111111               |

| Mid Scale           | 0000000000000              |

| Negative Full Scale | 100000000000               |

# RECEIVE CHANNEL PROGRAMMABLE GAIN AMPLIFIER

The gain of the amplifier at the input of the Receive Channel is set by two gain control pins, rxGAIN1 and rxGAIN0. The resulting gain between 0dB and +9dB is shown below.

| rxGAIN1 | rxGAIN0 | GAIN   |

|---------|---------|--------|

| 0       | 0       | 0dB    |

| 0       | 1       | 3.25dB |

| 1       | 0       | 6dB    |

| 1       | 1       | 9dB    |

FIGURE 1. Functional Block Diagram of AFE1104.

FIGURE 2. Basic Connection Diagram.

#### rxHYB AND rxLINE INPUT ANTI-ALIASING FILTERS

The –3dB frequency of the input anti-aliasing filter for the rxLINE and rxHYB differential inputs should be about 1MHz. Suggested values for the filter are  $750\Omega$  for each of the two input resistors and 100pF for the capacitor. Together the two  $750\Omega$  resistors and the 100pF capacitor result in a –3dB frequency of just over 1MHz. The  $750\Omega$  input resistors will result in a minimal voltage divider loss with the input impedance of the AFE1104.

This circuit applies at both T1 and E1 rates. For slower rates, the antialiasing filters will give best performance with their -3dB frequency approximately equal to the bit rate. For example, a -3dB frequency of 500kHz should be used for a single pair bit rate of 500kbps.

#### rxHYB AND rxLINE INPUT BIAS VOLTAGE

The transmitter output on the txLINE pins is centered at midscale, 2.5V. But, the rxLINE input signal is centered at 1.5V in the circuit shown in Figure 2 above.

Inside the AFE1104, the rxHYB and rxLINE signals are subtracted as described in the paragraph on echo cancellation above. This means that the rxHYB inputs need to be centered at 1.5V just as the rxLINE signal is centered at 1.5V. REF<sub>N</sub> (Pin 36) is a 1.5V voltage source. The external compromise hybrid must be designed so that the signal into the rxHYB inputs is centered at 1.5V.

#### TIMING DIAGRAMS

FIGURE 3. Transmit Channel Timing.

0

FIGURE 4. Receive Channel Timing.

#### **RECEIVE TIMING**

The rxSYNC signal controls portions of the A/D converter's decimation filter and the data output timing of the A/D converter. It is generated at the symbol rate by the user and must be synchronized with rxCLK. The bandwidth of the A/D converter decimation filter is equal to one half of the symbol rate. The A/D converter data output rate is 2X the symbol rate. The specifications of the AFE1104 assume that one A/D converter output is used per symbol period and the other interpolated output is ignored. The Receive Timing Diagram suggests using the rxSYNC pulse to read the first data output in a symbol period. Either data output may be used. Both data outputs may be used for more flexible post-processing.

## DISCUSSION OF SPECIFICATIONS

#### UNCANCELED ECHO

The key measure of transceiver performance is uncanceled echo. This measurement is made as shown in the diagram of Figure 5 and the measurement is made as follows. The AFE is connected to an output circuit including a typical 1:2 line transformer. The line is simulated by a  $135\Omega$  resistor. Symbol sequences are generated by the tester and applied both to the AFE and to the input of an adaptive filter. The output of the adaptive filter is subtracted from the AFE output to form the uncanceled echo signal. Once the filter taps have converged, the RMS value of the uncancelled echo is calculated. Since there is no far-end signal source or additive line noise, the uncanceled echo contains only noise and linearity errors generated in the transmitter and receiver.

The data sheet value for uncancelled echo is the ratio of the RMS uncanceled echo (referred to the receiver input through the receiver gain) to the nominal transmitted signal (13.5dBm into  $135\Omega$ , or 1.74Vrms). This echo value is measured under a variety of conditions: with loopback enabled (line input disconnected); with loopback disabled under all receiver gain ranges; and with the line shorted (S<sub>1</sub> closed in Figure 5).

#### POWER DISSIPATION

Approximately 75% of the power dissipation in the AFE1104 is in the analog circuitry, and this component does not change with clock frequency. However, the power dissipation in the digital circuitry does decrease with lower clock frequency. In addition, the power dissipation in the digital section is decreased when operating from a smaller supply voltage, such as 3.3V. (The analog supply,  $AV_{DD}$ , must remain in the range 4.75V to 5.25V).

FIGURE 5. Uncanceled Echo Test Diagram.

The power dissipation listed in the specifications section applies under these normal operating conditions: 5V Analog Power Supply; 3.3V Digital Power Supply; standard 13.5dBm delivered to the line; and a pseudo-random equiprobable sequence of HDSL output pulses. The power dissipation specifications includes all power dissipated in the AFE1104, it does not include power dissipated in the external load. The external power is 16.5dBm, 13.5dBm to the line and 13.5dBm to the impedance matching resistors. The external load power of 16.5dBm is 45mW. The typical power dissipation in the AFE1104 under various conditions is shown in Table I.

| BIT RATE<br>PER AFE1104<br>(Symbols/sec) | DVDD<br>(V) | TYPICAL POWER<br>DISSIPATION<br>IN THE AFE1104<br>(mW) |

|------------------------------------------|-------------|--------------------------------------------------------|

| 584 (E1)                                 | 3.3         | 250                                                    |

| 584 (E1)                                 | 5           | 300                                                    |

| 392 (T1)                                 | 3.3         | 240                                                    |

| 392 (T1)                                 | 5           | 270                                                    |

| 146 (E1/4)                               | 3.3         | 230                                                    |

| 146 (E1/4)                               | 5           | 245                                                    |

TABLE I. Typical Power Dissipation.

### LAYOUT

The analog front end of an HDSL system has a number of conflicting requirements. It must accept and deliver digital outputs at fairly high rates of speed, phase-lock to a high-speed digital clock, and convert the line input to a high-precision (14-bit) digital output. Thus, there are really three sections of the AFE1104: the digital section, the phase-locked loop, and the analog section.

The power supply for the digital section of the AFE1104 can range from 3.3V to 5V. This supply should be decoupled to digital ground with a ceramic  $0.1\mu$ F capacitor placed as close to DGND (pin 12) and DV<sub>DD</sub> (pin 13) as possible. Ideally, both a digital power supply plane and a digital ground plane should run up to and underneath the digital

pins of the AFE11104 (pins 3 through 26). However,  $DV_{DD}$  may be supplied by a wide printed circuit board (PCB) trace. A digital ground plane underneath all digital pins is strongly recommended.

The phase-locked loop is powered from  $PV_{DD}$  (pin 2) and its ground is referenced to PGND (pin 1). Note that  $PV_{DD}$  must be in the 4.75V to 5.25V range. This portion of the AFE1104 should be decoupled with both a 10µF Tantalum capacitor and a 0.1µF ceramic capacitor. The ceramic capacitor should be placed as close to the AFE1104 as possible. The placement of the Tantalum capacitor is not as critical, but should be close. In each case, the capacitor should be connected between  $PV_{DD}$  and PGND.

In most systems, it will be natural to derive  $PV_{DD}$  from the  $AV_{DD}$  supply. A 5 $\Omega$  to 10 $\Omega$  resistor should be used to connect  $PV_{DD}$  to the analog supply. This resistor in combination with the 10 $\mu$ F capacitor form a lowpass filter—keeping glitches on  $AV_{DD}$  from affecting  $PV_{DD}$ . Ideally,  $PV_{DD}$  would originate from the analog supply (via the resistor) near the power connector for the printed circuit board. Likewise, PGND should connect to a large PCB trace or small ground plane which returns to the power supply connector underneath the  $PV_{DD}$  supply path. The PGND "ground plane" should also extend underneath PLL<sub>IN</sub> and PLL<sub>OUT</sub> (pins 47 and 48).

The remaining portion of the AFE1104 should be considered analog. All AGND pins should be connected directly to a common analog ground plane and all  $AV_{DD}$  pins should be connected to an analog 5V power plane. Both of these planes should have a low impedance path to the power supply.

Ideally, all ground planes and traces and all power planes and traces should return to the power supply connector before being connected together (if necessary). Each ground and power pair should be routed over each other, should not overlap any portion of another pair, and the pairs should be separated by a distance of at least 0.25 inch (6mm). One exception is that the digital and analog ground planes should be connected together underneath the AFE1104 by a small trace.