# AK2302

## Dual PCM Codec/Filter COMBO LSI

#### Features

- ☐ Meets ITU recommendations

- Complete CODEC and filtering system for two telephone lines including

- free operational amplifier for gain adjustment in both direction

- internal precision reference voltage

- antialiasing filtering

- smoothing filtering

- sinX/X correction

- A-law/  $\mu$  -law pin selectable

- interface to PCM highway for both channels in common

- separate frame sync at each channel

- $\square$ Single +5V  $\pm$  5% operation

- $\square$ 24pin VSOP small package (7.9×7.6mm)

- ☐ Auto power save mode

- ☐Power on reset

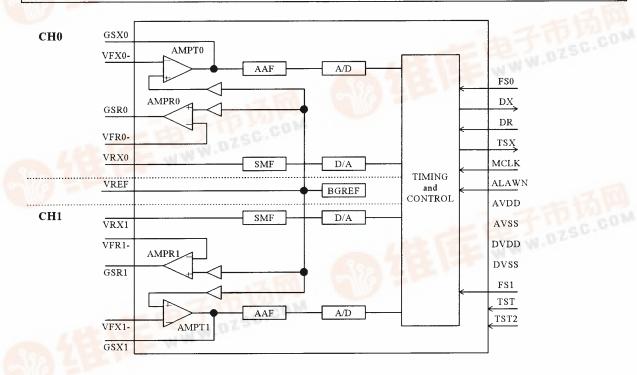

#### **Block Diagram**

**'98/10**

#### General Description

(Description)

☐Time Slot Assignment

Some type of time slot assignment is necessary because two channels are sharing a signal PCM data input pin and a output pin.

Synchronous timing for the dual CODEC is defined by either FS0 or FS1 whichever comes first after the device initialization sequence(first FS). Another FS must be delayed from the first one by the multiple of 8 MCLK cycles. FS0 and FS1 must be derived from MCLK, and their periodicity must be 256 MCLK cycles.

Time slot 0 is determined by the slot defined by FS0 or FS1 whichever comes first. If the other channel is to be used, FS for other channel must be delayed from the first by a multiple 8 MCLK cycles.

In order to change channel in use and time slot assignment for each channel in use, the device must be reset in power down mode (TST pin low or absence of first FS), before channels and time slots can be selected as described above.

□Power Down

The device goes into power down mode if TST pin is low or the FS0 or FS1 defining slot0, i.e. first FS, is not present more than  $4 \times Ts (=500) \mu sec$ . In power down mode, MCLK doesn't need to be input.

□Power on Reset

When power is first applied, power on reset circuitry initializes AK2302. During the 150 ms (typical value) initialization sequence, any input signal on FSn (n=0 or 1) will not be taken notice of ("don't care").

MCLK must be supplied constantly except when the device is in power down mode.

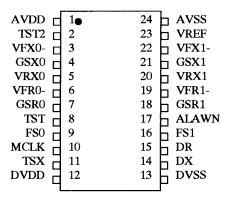

#### ■Pin assignment

0176-E-01 -2- '98/10

## Circuit Description

| Block      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMPT0,1    | Op-amp for input gain adjustment. AK2302 has an op-amp at each analog input. This op-amp is used as an inverting amplifier. Adjusting the gain with external resistors. The resistor lager than $10k\Omega$ is recommended for the feedback resistor.                                                                                                                                                                                                                                                                                                    |

| AMPR0,1    | Op-amp for output gain adjustment. AK2302 has an op-amp at each analog output. This op-amp is used as an inverting amplifier. Adjusting the gain with external resistors. The resistor lager than $10k\Omega$ is recommended for the feedback resistor.                                                                                                                                                                                                                                                                                                  |

| AAF        | Integrated anti-aliasing filter which prevents signals around the sampling rate from folding back into the voiceband. AAF is a 2nd order RC low-pass filter.                                                                                                                                                                                                                                                                                                                                                                                             |

| A/D        | Converts analog signal to 8bit PCM data according to the companding schemes of ITU recommendation G.711; A-law or $\mu$ -law. The band limiting filter is also integrated. The selection of companding schemes is set by ALAWN pin as follows: "H": $\mu$ -Law "L": A-Law                                                                                                                                                                                                                                                                                |

| D/A        | Expands 8bit PCM data according to A-law or $\mu$ -law. The selection of companding schemes is set by ALAWN pin as follows:  "H": $\mu$ -Law  "L": A-Law                                                                                                                                                                                                                                                                                                                                                                                                 |

| SMF        | Extracts the inband signal from D/A output. It also corrects the sinx/x effect of D/A output.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BGREF      | Provides the stable analog ground voltage (2.4V) using an on-chip band-gap reference circuit which is temperature compensated.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TIMING and | 8bit PCM data of CH0 and CH1 is multiplexed into serial data of 2.048Mb/s at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CONTROL    | rising edges of MCLK and comes out from DX. The start bit of transmit PCM data of CH0 and CH1 are defined by FS0 and FS1 respectively. This 3-state output remains in the high impedance state except during the assigned transmit time slot. Receive serial PCM data from DR at the rate of 2.048Mb/s at the falling edges of MCLK is demultiplexed into 2CH serial data. The start bit of receive PCM data of CH0 and CH1 are defined by FS0 and FS1 respectively. The received data is divided into 8bit blocks and sent to CH0 and CH1 sequentially. |

## Pin/Function

| Pin# | Name  | I/O_ | Function                                                                                                                                                                                                                                                                   | Remarks |

|------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1    | AVDD  | Ţ -  | Analog positive supply voltage. Systems analog +5V supply.                                                                                                                                                                                                                 |         |

| 2    | TST2  | I    | Test pin. Tie to logic high for normal operation. The device enters test mode with TST2 low.                                                                                                                                                                               |         |

| 3    | VFX0- | I    | Transmit analog input. Inverting input of transmit input                                                                                                                                                                                                                   |         |

|      | CCVO  | 0    | amplifier for channel 0. Output of transmit input amplifier for channel 0.                                                                                                                                                                                                 |         |

| 4    | GSX0  |      | Receive analog output of SMF for channel 0. This output                                                                                                                                                                                                                    |         |

| 5    | VRX0  | 0    | can drive 10kΩ or larger, and 50pF or smaller.                                                                                                                                                                                                                             |         |

| 6    | VFR0- | I    | Inverting input of receive output amplifier for channel 0.                                                                                                                                                                                                                 |         |

| 7    | GSR0  | 0    | Output of receive output amplifier for channel 0.                                                                                                                                                                                                                          |         |

| 8    | TST   | I    | Test (Power down) pin. Tie to logic high for normal operation. The device enters power down mode with TST low.                                                                                                                                                             |         |

| 9    | FS0   | I    | Frame sync input for channel 0.<br>FS0 must be derived from MCLK, and its periodicity must be<br>256 MCLK cycles.                                                                                                                                                          |         |

| 10   | MCLK  | I    | Master clock 2.048MHz input.                                                                                                                                                                                                                                               |         |

| 11   | TSX   | О    | Open drain output. Pulsing low during digital transmission cycles.                                                                                                                                                                                                         |         |

| 12   | DVDD  |      | Digital positive supply voltage. System digital +5V supply.                                                                                                                                                                                                                |         |

| 13   | DVSS  | -    | Digital negative supply voltage. System digital ground.                                                                                                                                                                                                                    |         |

| 14   | DX    | O    | Serial output of 2.048Mb/s PCM data. The PCM data is shifted out at the rising edges of MCLK. The start bit of transmit PCM data is defined by either FS0 or FS1. This tri-state output remains in the high impedance state except during the assigned transmit time slot. |         |

| 15   | DR    | I    | Serial input of 2.048Mb/s PCM data. The PCM data is shifted in at the falling edges of MCLK. The start bit of receive PCM data is defined by either FS0 or FS1.                                                                                                            |         |

| 16   | FS1   | I    | Frame sync input for channel 1.<br>FS1 must be derived from MCLK, and its periodicity must be<br>256 MCLK cycles.                                                                                                                                                          |         |

| 17   | ALAWN | I    | Companding schemes selection.  "H": \(\mu\text{-Law}\)  "L": A-Law                                                                                                                                                                                                         |         |

| 18   | GSR1  | 0    | Output of receive output amplifier for channel 1.                                                                                                                                                                                                                          |         |

| 19   | VFR1- | I    | Inverting input of receive output amplifier for channel 1.                                                                                                                                                                                                                 |         |

| 20   | VRX1  | О    | Receive analog output of SMF for channel 1. This output can drive $10k\Omega$ or larger, and $50pF$ or smaller.                                                                                                                                                            |         |

| 21   | GSX1  | 0    | Output of transmit input amplifier for channel 1.                                                                                                                                                                                                                          |         |

| 22   | VFX1- | I    | Transmit analog input. Inverting input of transmit input amplifier for channel 1.                                                                                                                                                                                          |         |

| 23   | VREF  | 0    | Analog ground output. To stabilize the analog ground, connect to AVSS with $1.0 \mu F$ or larger.                                                                                                                                                                          |         |

| 24   | AVSS  |      | Analog negative supply voltage. System analog ground.                                                                                                                                                                                                                      |         |

#### Absolute Maximum Ratings

| Parameter                                |    | Symbol | Min  | Max      | Units        |

|------------------------------------------|----|--------|------|----------|--------------|

| Power Supply Voltages                    |    |        |      |          |              |

| Digital Power Supply                     |    | DVDD   | -0.3 | 6.5      | $\mathbf{V}$ |

| Analog Power Supply                      | 1) | AVDD   | -0.3 | 6.5      | V            |

| DVSS Voltage                             |    | DVSS   | -0.1 | 0.1      | V            |

| Digital Input Voltage                    |    | VTD    | -0.3 | AVDD+0.3 | V            |

| Analog Input Voltage                     |    | VTA    | -0.3 | AVDD+0.3 | V            |

| Input current (except power supply pins) |    | IIN    | -10  | 10       | m A          |

| Storage Temperature                      |    | Tstg   | -55  | 125      | °C           |

Note 1) All voltages with respect to ground. : AVSS=DVSS=0V

Warning: Exceeding absolute maximum ratings may cause permanent damage.

Normal operation is not guaranteed at these extremes.

#### **Recommended Operating Conditions**

| Parameter                     | Symbol | Min  | Тур   | Max  | Units    |

|-------------------------------|--------|------|-------|------|----------|

| Power Supplies 1)             |        |      |       |      |          |

| Analog power supply           | AVDD   | 4.75 | 5.0   | 5.25 | V        |

| Digital power supply          | DVDD   | 4.75 | 5.0   | AVDD | V        |

| Ambient Operating Temperature | Ta     | -40  |       | 85   | <b>℃</b> |

| Master Clock Frequency        | MCLK   |      | 2.048 |      | MHz      |

Note 1) If DVDD is greater than AVDD, then IDD will increase

Note) All voltages reference to ground : AVSS=DVSS=0V

#### **Electrical Characteristics**

Unless otherwise noted, guaranteed for AVDD=DVDD=+5V±5%, Ta = -40~+85°C, MCLK=2.048MHz.

#### ■ DC characteristics

| Parameter                 | Symbol | Conditions                                             | Min | Тур | Max | Units |

|---------------------------|--------|--------------------------------------------------------|-----|-----|-----|-------|

| Power Consumption         | PDD    | Normal operation<br>Supplying MCLK<br>Outputs unloaded |     | 60  | 80  | mW    |

| Output High Voltage       | Voh    | IOH=-3.2mA                                             | 2.4 |     |     | V     |

| Output Low Voltage        | Vol    | IoL=3.2mA                                              |     | .,  | 0.4 | V     |

| Input High Voltage        | Vih    |                                                        | 2.0 |     |     | V     |

| Input Low Voltage         | VIL    |                                                        |     |     | 0.8 | V     |

| Input Leakage Current     | Ιi     | All pins except TST,TST2                               | -10 |     | +10 | μA    |

| Input Capacitance         | Ci     |                                                        |     |     | 5   | pF    |

| Output Leakage<br>Current | Io     | Tri-state mode                                         | -10 |     | +10 | μΑ    |

#### ■Absolute Gain

| Parameter              | Conditions          | Min    | Тур   | Max  | Units |

|------------------------|---------------------|--------|-------|------|-------|

|                        |                     | 141111 |       | MIGA |       |

| Analog Input Level     | Input: 0dBm0@1020Hz |        | 0.849 |      | Vrms  |

| Absolute Transmit Gain |                     | -0.25  | _     | 0.25 | dB    |

|                        | VDD=5V, Ta=25°C     | -0.15  |       | 0.15 | dB    |

| Analog Output Level    | Input: 0dBm0@1020Hz |        | 0.849 | I    | Vrms  |

| Absolute Receive Gain  |                     | -0.25  | _     | 0.25 | dB    |

|                        | VDD=5V, Ta=25°C     | -0.15  | _     | 0.15 | dB    |

| Maximum Overload Level | 3.14dBm0            |        | 1.219 |      | Vrms  |

**■**Gain Tracking

| Gain Hacking                 |                  |                 |      |     |     |       |

|------------------------------|------------------|-----------------|------|-----|-----|-------|

| Parameter                    | Con              | Conditions      |      | Тур | Max | Units |

| Transmit Gain Tracking Error | Reference Level: | -55dBm0~-50dBm0 | -1.2 | _   | 1.2 |       |

|                              | -10dBm0          | -50dBm0~-40dBm0 | -0.4 | _   | 0.4 | dB    |

|                              | 1020Hz Tone      | -40dBm0∼ 3dBm0  | -0.2 | _   | 0.2 |       |

| Receive Gain Tracking Error  | Reference Level: | -55dBm0~-50dBm0 | -1.2 | _   | 1.2 |       |

|                              | -10dBm0          | -50dBm0~-40dBm0 | -0.4 | _   | 0.4 | dΒ    |

|                              | 1020Hz Tone      | -40dBm0∼ 3dBm0  | -0.2 | _   | 0.2 |       |

■Frequency Response

| Parameter                   | Con          | ditions             | Min   | Тур | Max  | Units |

|-----------------------------|--------------|---------------------|-------|-----|------|-------|

| Transmit Frequency Response | Relative to: | $0.05 \mathrm{kHz}$ | _     | _   | -30  |       |

|                             | 0dBm0@1020Hz | 0.06kHz             |       | _   | -26  |       |

|                             |              | $0.2 \mathrm{kHz}$  | -1.8  | _   | 0    |       |

|                             |              | 0.3~3.0kHz          | -0.15 | _   | 0.15 | dΒ    |

|                             |              | 3.4kHz              | -0.8  | _   | 0    |       |

|                             |              | 4.0kHz              | _     | _   | -14  |       |

| Receive Frequency Response  | Relative to: | 0~3.0kHz            | -0.15 |     | 0.15 |       |

|                             | 0dBm0@1020Hz | 3.4kHz              | -0.8  | -   | 0    | dB    |

|                             |              | 4.0kHz              | _     | _   | -14  |       |

Note) Not tested in production. Parameters guaranteed by design.

#### **■**Distortion

| Parameter                               | Cor           | nditions        | Min        | Тур | Max | Units |

|-----------------------------------------|---------------|-----------------|------------|-----|-----|-------|

| Transmit Signal to Distortion           | 1020Hz Tone   | -40dBm0~-45dBm0 | 36         | _   |     |       |

|                                         | -             | -30dBm0~-40dBm0 | 30         | _   |     | dB    |

|                                         |               | 0dBm0~-30dBm0   | <b>2</b> 5 | _   | _   |       |

| Receive Signal to Distortion            | 1020Hz Tone   | -40dBm0~-45dBm0 | 36         | _   | _   |       |

|                                         |               | -30dBm0~-40dBm0 | 30         | _   | _   | dB    |

|                                         |               | 0dBm0~-30dBm0   | 25         | _   | _   |       |

| Single Frequency Distortion<br>Transmit |               |                 | _          | _   | -46 | dB    |

| Single Frequency Distortion<br>Receive  |               |                 |            | _   | -46 | dB    |

| Intermodulation Distortion              | -6dBm@860Hz,1 | 380Hz           |            | _   | -42 | dB    |

Note) C-message Weighted for  $\mu$ -Law, Psophometric Weighted for A-Law

0176-E-01 -6 - '98/10

**■**Envelope delay Distortion

| Parameter                | Conditions                 | Min | Тур | Max | Units   |

|--------------------------|----------------------------|-----|-----|-----|---------|

| Transmit Delay, Absolute | f=1600Hz                   | _   | _   | 315 | μs      |

| Transmit Delay, Relative | f=500Hz~600Hz              | _   | _   | 220 |         |

|                          | f=600Hz~1000Hz             | -   |     | 145 |         |

|                          | f=1000Hz~2600Hz            | _   | _   | 75  | μs      |

|                          | f=2600Hz~2800Hz            | _   | _   | 105 |         |

|                          | f=2800Hz~3000Hz            | _   | _   | 155 |         |

| Receive Delay, Absolute  | f=1600Hz                   |     |     |     |         |

|                          | 1st FS channel             | 1   | 1   | 200 | $\mu$ s |

|                          | 2 <sup>nd</sup> FS channel | _   | _   | 202 |         |

| Receive Delay, Relative  | f=500Hz~1000Hz             | -40 | _   | _   |         |

|                          | f=1000Hz~1600Hz            | -30 | _   | _   |         |

|                          | f=1600Hz~2600Hz            | _   | _   | 90  | μs      |

|                          | f=2600Hz~2800Hz            | _   | _   | 125 |         |

|                          | f=2800Hz~3000Hz            | _   | _   | 175 |         |

Note) Not tested in production. Parameters guaranteed by design.

#### Noise

| Parameter                   | Condition               | ıs                   | Min      | Тур | Max | Units  |

|-----------------------------|-------------------------|----------------------|----------|-----|-----|--------|

| Transmit Noise 1)           | μ-law, C-message        |                      | <b>—</b> | 5   | 10  | dBrnC0 |

|                             | A-law, Psophometr       | ric                  | _        | -85 | -80 | dBm0p  |

| Receive Noise 2)            | μ-law, C-message        |                      | _        | 5   | 10  | dBrnC0 |

|                             | A-law, Psophometr       | ic                   | _        | -85 | -80 | dBm0p  |

| Noise, Single Frequency     | VFXIN = 0 Vrms, DR = DX |                      |          | _   | -53 | dBm0   |

|                             | f=0~100kHz              |                      |          |     |     |        |

| PSRR, Transmit 3)           | AVDD=DVDD=5V            | AVDD=DVDD=5V±100mVop |          |     | _   | dB     |

|                             | f=0~50kHz               |                      |          |     |     |        |

| PSRR, Receive <sup>3)</sup> | AVDD=DVDD=5V            | ± 100mVop            | 40       | _   | _   | dB     |

|                             | f=0~50kHz               |                      |          |     |     |        |

| Spurious Out-of-Band Signal | 0dBm0,                  | 4.6~7.6kHz           | _        |     | -32 |        |

| at VRX Output <sup>3)</sup> | 0.3~3.4kHz              | 7.6~8.4kHz           | _        |     | -40 | dB     |

|                             | PCM CODE                | 8.4~100kHz           | _        |     | -32 |        |

Note 1) Analog Input = Analog Ground

Note 2) Digital Input(RD) = +0 Code

Note 3) Not tested in production. Parameters guaranteed by design.

#### **■**Interchannel Crosstalk

| Parameter            | Conditions                       | Min | Тур | Max | Units |

|----------------------|----------------------------------|-----|-----|-----|-------|

| Transmit to Receive  | 0dBm0@VFXIN, Idle PCM code       | _   | _   | -75 | dB    |

| Receive to Transmit  | 0dBm0 code level, VFXIN = 0 Vrms | T - | _   | -75 | dB    |

| Transmit to Transmit | 0dBm0@VFXIN, Idle PCM code       | _   | _   | -75 | dB    |

| Receive to Receive   | 0dBm0 code level, VFXIN = 0 Vrms | _   | _   | -75 | dB    |

### ■Intrachannel Crosstalk

| Parameter           | Conditions                       | Min | Тур | Max | Units |

|---------------------|----------------------------------|-----|-----|-----|-------|

| Transmit to Receive | 0dBm0@VFXIN, Idle PCM code       |     |     | -75 | dB    |

| Receive to Transmit | 0dBm0 code level, VFXIN = 0 Vrms | _   | _   | -75 | dB    |

Note) Not tested in production. Parameters guaranteed by design.

■ Analog Interface Transmit Input Amplifier

| Analog Interface Trans | Conditions                           | Min  | Тур | Max  | Units       |

|------------------------|--------------------------------------|------|-----|------|-------------|

| Parameter              |                                      |      | тур |      | <del></del> |

| Input Leakage Current  | 0.6V < V < 4.2V                      | -100 |     | +100 | nA          |

| Input Resistance       |                                      | 10   | _   | _    | ΜΩ          |

| Input Voltage          | Relative AVSS                        | 2.3  | 2.4 | 2.5  | V           |

| Voltage Gain           |                                      | 5000 | _   | _    | V/V         |

| Unity-Gain Bandwidth   |                                      | 1    | 2   | -    | MHz         |

| Offset Voltage         |                                      | -20  | _   | +20  | mV          |

| Load Resistance        |                                      | 10   | _   | _    | kΩ          |

| Load Capacitance       |                                      | _    |     | 50   | pF          |

| Output Voltage Swing   |                                      |      | 3.6 |      | Vp-p        |

| Output Resistance      |                                      |      | _   | 10   | Ω           |

| Power Supply Rejection | Feedback Resistor less than 20k Ω 1) | 40   | _   | _    | dB          |

| Ratio                  | $f = 0 \sim 60 \text{kHz},$          |      |     |      |             |

Note 1) Between GSXn and VFXn- (n = 0 or 1)

Note) Not tested in production. Parameters guaranteed by design.

■ Analog Interface Receive Output

| Parameter            | Conditions     | Min | Тур | Max | Units |

|----------------------|----------------|-----|-----|-----|-------|

| Output Voltage       | 0dBm0 PCM code | 2.3 | 2.4 | 2.5 | V     |

| Load Resistance      |                | 10  |     |     | kΩ    |

| Load Capacitance     |                |     |     | 50  | pF    |

| Output Voltage Swing |                |     | 3.6 |     | Vp-p  |

| Output Resistance    |                |     |     | 10  | Ω     |

Note) Not tested in production. Parameters guaranteed by design.

■ Analog Interface Receive Output Amplifier

| Parameter              | Conditions                           | Min  | Тур | Max  | Units |

|------------------------|--------------------------------------|------|-----|------|-------|

| Input Leakage Current  | 0.6V < V < 4.2V                      | -100 | _   | +100 | nA    |

| Input Resistance       |                                      | 10   | _   |      | ΜΩ    |

| Input Voltage          | Relative AVSS                        | 2.3  | 2.4 | 2.5  | V     |

| Voltage Gain           |                                      | 5000 | _   | _    | V/V   |

| Unity-Gain Bandwidth   |                                      | 1    | 2   | _    | MHz   |

| Offset Voltage         |                                      | -20  | _   | +20  | mV    |

| Load Resistance        |                                      | 10   | -   | _    | kΩ    |

| Load Capacitance       |                                      |      | -   | 50   | pF    |

| Output Voltage Swing   |                                      | _    | 3.6 | _    | Vp-p  |

| Output Resistance      |                                      |      | _   | 10   | Ω     |

| Power Supply Rejection | Feedback Resistor less than 20k Ω 1) | 40   |     | _    | dB    |

| Ratio                  | $f = 0 \sim 60 \text{kHz},$          |      |     |      |       |

Note 1) Between GSXn and VFXn- (n = 0 or 1)

Note) Not tested in production. Parameters guaranteed by design.

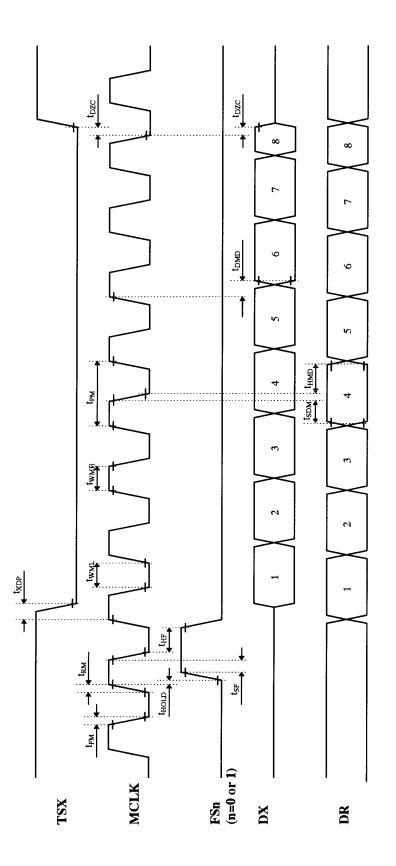

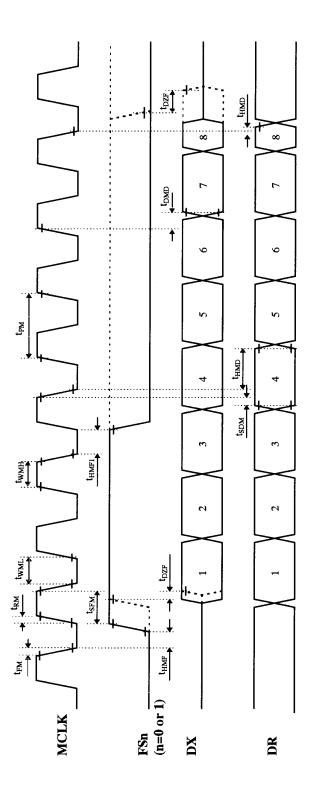

#### **■**Timing Specification

Unless otherwise noted, the specification applies for TA = -40 to +85°C, DVDD = AVDD = 5V+/-5%, DVSS = AVSS = 0V and MCLK = 2.048 MHz. All other limits are assured by correlation with other production tests and/or product design and characterization. All timing parameters are measured at VOH = 2.0V and VOL = 0.7V.

| Parameter                                             | Symbol                     | Min | Тур   | Max    | Units | Ref fig |

|-------------------------------------------------------|----------------------------|-----|-------|--------|-------|---------|

| Frequency of Master Clock                             | 1/t <sub>PM</sub>          | _   | 2.048 | _      | MHz   | 1,2     |

| Width of Master Clock High                            | twmn                       | 195 | _     | _      | ns    | 1,2     |

| Width of Master Clock Low                             | twmL                       | 195 | _     | _      | ns    | 1,2     |

| Rise time of Master Clock                             | trm                        | _   | _     | 40     | ns    | 1,2     |

| Fall time of Master Clock                             | tгм                        | _   | _     | 40     | ns    | 1,2     |

| Delay time to Valid Data from FS or MCLK, whichever   | tdzf                       | 20  | _     | 165    | ns    | 2       |

| comes later, and Delay time from FS to Data Output    |                            |     |       |        |       |         |

| disabled <sup>1)</sup>                                |                            |     |       |        |       |         |

| Delay time from MCLK Low to Data Output disable       | $\mathbf{t}_{	extsf{DZC}}$ | 50  | _     | 165    | ns    | 1       |

| Setup time from DR Valid to MCLK Low                  | tsdm                       | 40  | _     | _      | ns    | 1,2     |

| Hold time from MCLK Low to DR Invalid                 | $\mathbf{t}_{HMD}$         | 50  |       | _      | ns    | 1,2     |

| Hold time from MCLK Low to Frame Sync High            | thmf                       | 10  | -     | _      | ns    | 2       |

| Setup time from Frame Sync to MCLK Low                |                            | 70  | _     | ТРМ-70 | ns    | 2       |

| Hold time from 3rd period of MCLK Low to Frame Sync   | thmf1                      | 90  |       | _      | ns    | 2       |

| Delay time from MCLK High to Data Valid <sup>1)</sup> | tomd                       | 0   | _     | 170    | ns    | 1,2     |

| Setup time from FS to MCLK Low                        | tsf                        | 80  | _     | ТРМ-80 | ns    | 1       |

| Hold time from MCLK low to FS Low                     | thf                        | 100 | -     | _      | ns    | 1       |

| Delay time to TSX Low <sup>2)</sup>                   | txdp                       | 0   | _     | 140    | ns    | 1       |

| Hold time from bit clock Low to Frame Sync            | thold                      | 0   | _     |        | ns    | 1       |

Note 1) Load on DX 150 pF plus 2 LSTTL load

Note 2) Load on TSX 0-150 pF plus pull up resistor 1.5k Ω minimum

Figure 1. Short Frame Sync Timing Diagram

0176-E-01

Figure 2. Long Frame Sync Timing Diagram

- 11 -

#### **Application Circuit Example**

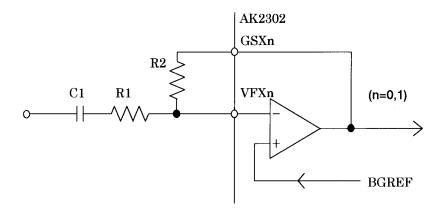

#### @Analog input circuit (AMPT0,1)

AK2302 has an op-amp at analog input of each channel. Each op-amp can be used as a gain adjustment.

Op-amp can be used as an inverting amplifier. Feedback resistor must be  $10k\Omega$  or larger.

C1=0.47  $\mu$ F R1=R2=33k  $\Omega$

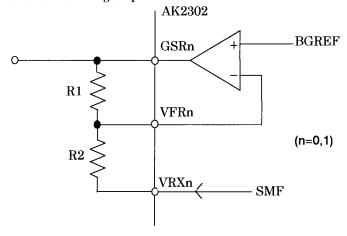

#### ©Analog output circuit (AMPR0,1)

AK2302 has an op-amp at analog input of each channel. Each op-amp can be used as a gain adjustment.

Op-amp can be used as an inverting amplifier. Feedback resistor must be  $10k\Omega$  or larger.

$R1=R2=33k\Omega$

####

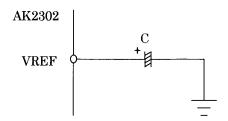

To stabilize analog ground (VREF), connect to AVSS through  $1.0 \mu F$  or larger capacitor.

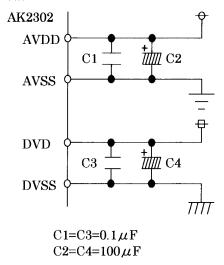

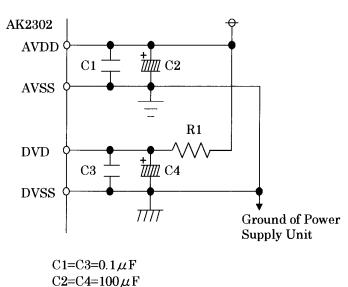

#### **OPower Supply**

To attenuate the power supply noise, connect capacitors between AVDD and AVSS, and DVDD and DVSS, as shown below.

To use the same supply for both digital and analog power supply (DVDD and AVDD), insert  $10\,\Omega$  resistor between AVDD and DVDD. AVSS and DVSS must be separated on the board, and connected them at power supply unit.

$R1=10\Omega$

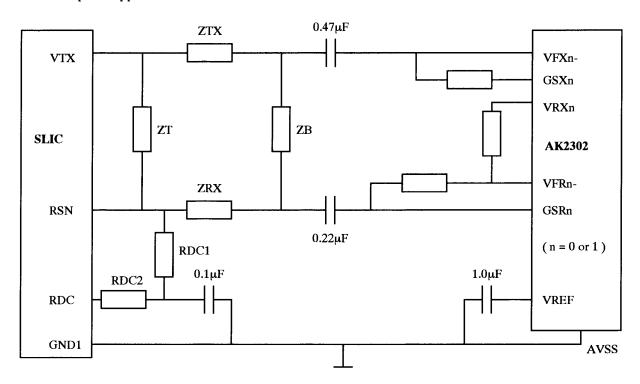

#### **©**Application for SLIC

The example of application circuit with SLIC.

System Analog Ground

## **Packaging Information**

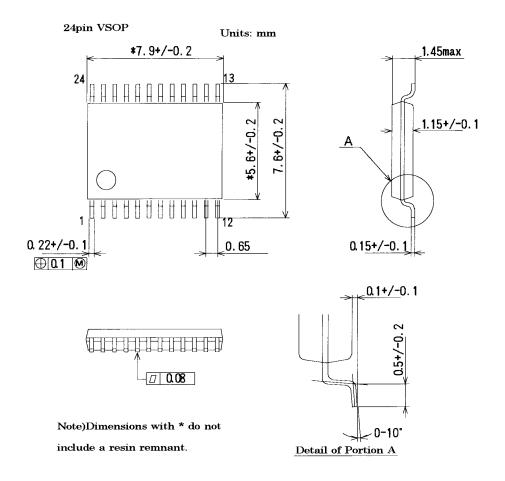

#### □24pin VSOP

#### **■**Marking

- (1) Pin#1 indication

- (2) Date Code: 5 digit XXXYZ(3) Marketing Code: AK2302

- (4) AKM Logo

#### **Outline Dimensions**

[Material]

Resin

: Low Stress Type Epoxy Resin

Lead Frame

: Cu

#### IMPORTANT NOTICE

• These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

- (a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- (b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.