ASAHI KASEI

[AK8850]

## AK8850 NTSC Digital Video Decoder

### General Description

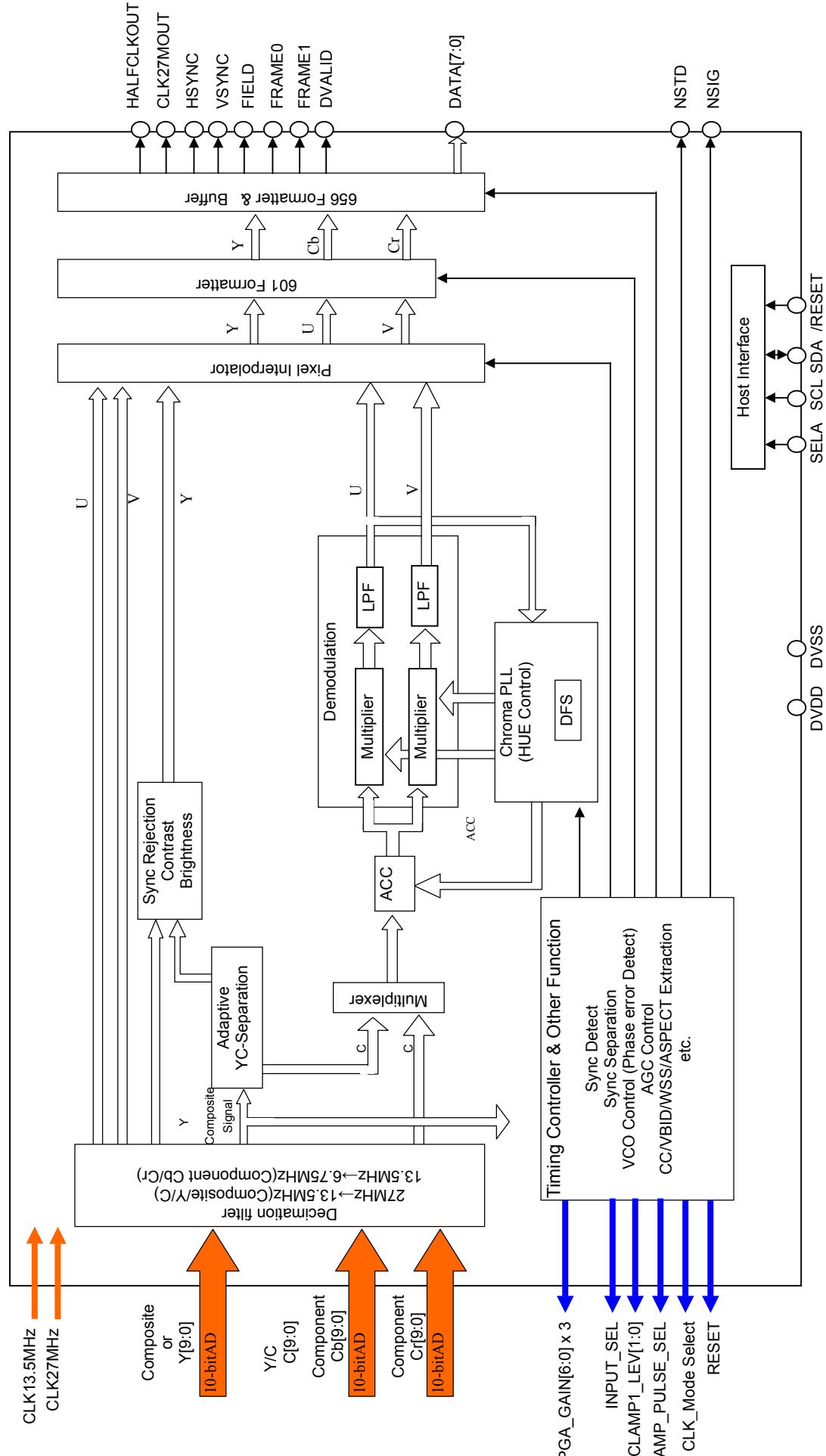

The AK8850 decodes NTSC composite video, S-Video and Component Video signals (525/625) into digital formats. Digital output conforms to ITU-R BT.601 and ITU-R BT.656\* YCrCb specifications. The AK8850 outputs a control signal to generate clocks synchronized with either Horizontal Sync or Vertical Sync signals. Its clock rate is 27 MHz.

An encoded VBID Closed Caption signal can be extracted from the video signal and sent to an external pin on the AK8850.

### Features

- NTSC-M Composite signal and S-Video signal decoder

- Component Video decoder for 525 / 625 systems ( Betacam, MII, EBU N10 )

- On-chip triple 10-Bit ADCs ( 27 MHz operation )

- On-chip Programmable Gain Amp ( PGA ), ranging from 0 dB to 12 dB in 0.1 dB / steps

- Input-synchronized clock is generated by an external VCXO

- Sub-Carrier generation by Digital Synthesizer ( DFS )

- Auto Color Control ( ACC )

- Auto Gain Control ( AGC )

- Adaptive 3-line Y-C separation

- ITU-R BT.656 format output ( 4:2:2 8-Bit parallel output with EAV / SAV )

- NTSC Closed Caption signal decoding function

- VBID Program condition decoding function

- WSS Program condition decoding function

- Video Aspect Signal decoding function on Line 16 and Line 279

- Sleep function

- 6-channel Analog inputs

- I2C Control

- 3.3 V CMOS

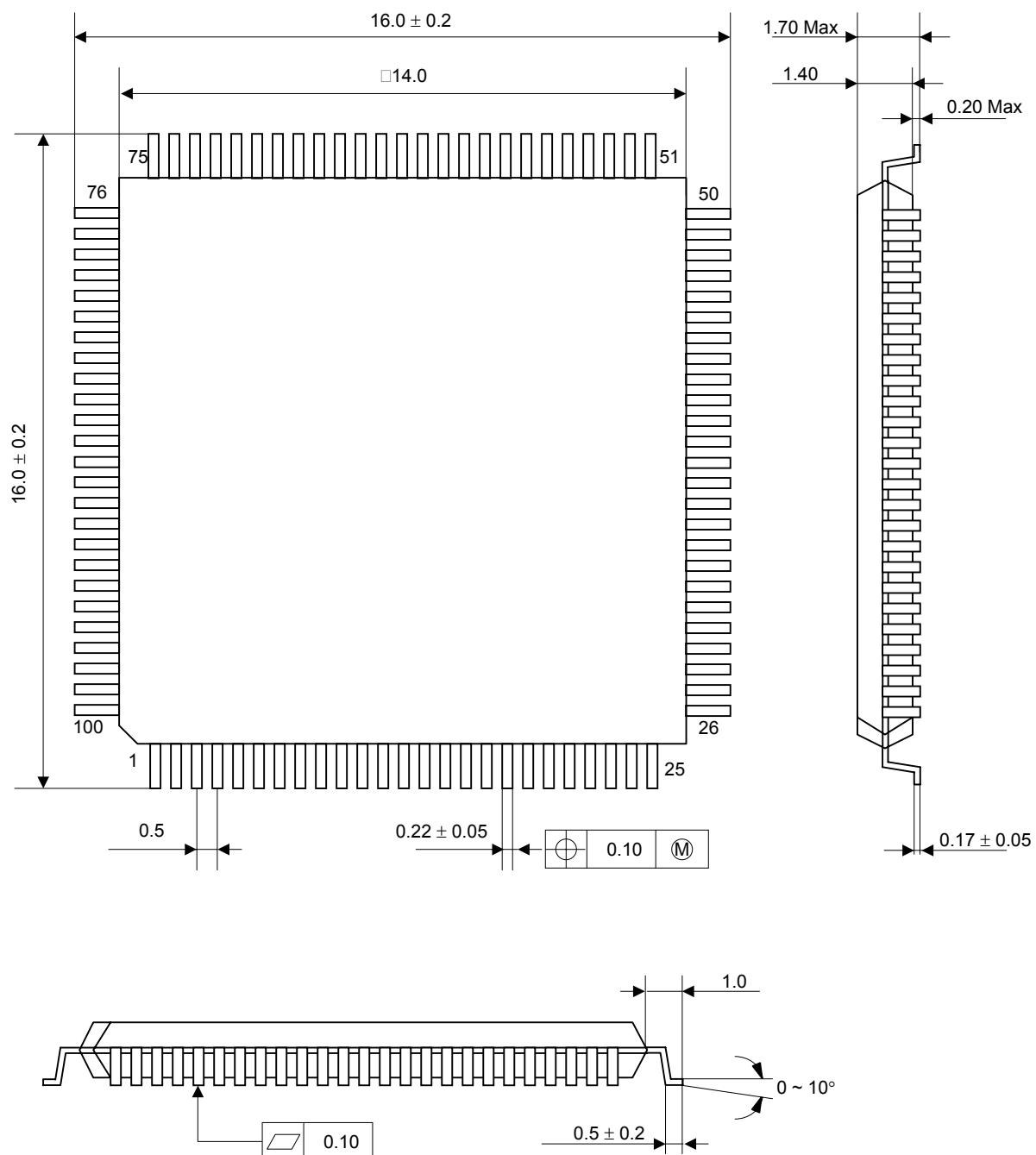

- 100-Pin LQFP package

note: \* ITU-R BT.656 spec may not be satisfied, as it is dependent upon input signal quality.

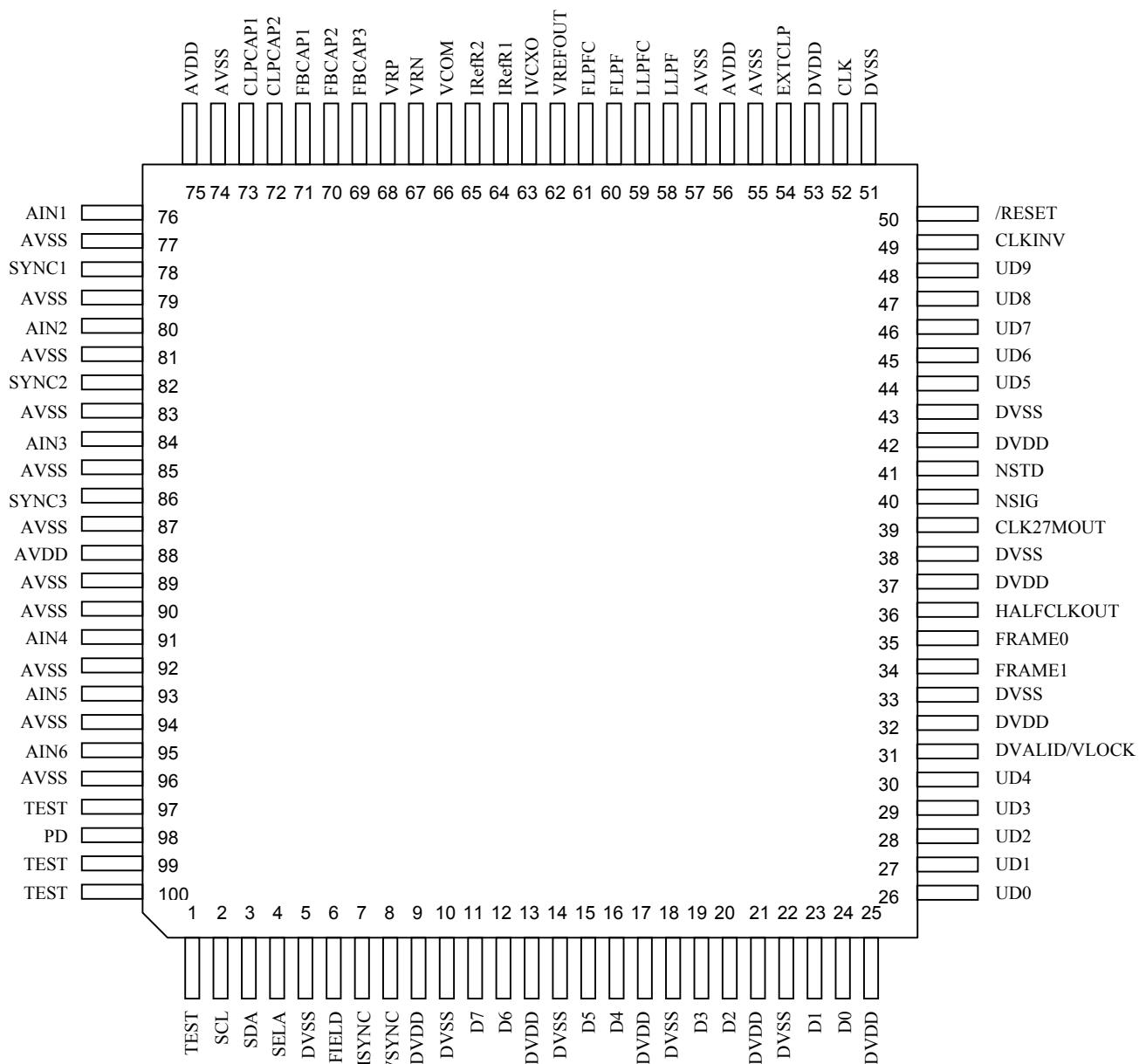

## 2. Pin Assignment

## 3. Pin Functional Description

| Pin Number | Identification | I/O | Description                                                                                                                                                                 |

|------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2          | SCL            | I   | I2C bus Clock                                                                                                                                                               |

| 3          | SDA            | I/O | I2C bus Data (Open Collector )                                                                                                                                              |

| 4          | SELA           | I   | I2C bus address selector                                                                                                                                                    |

| 6          | FIELD          | O   | FIELD Identify<br>Low□EVEN<br>High□ODD                                                                                                                                      |

| 7          | HSYNC          | O   | Hsync Timing output pin                                                                                                                                                     |

| 8          | VSYNC          | O   | Vsync Timing output pin. (It is possible to output V_Blank Signal (VD) by setting a register)                                                                               |

| 11         | D7 (MSB)       | O   | Decoded data output pin (MSB)                                                                                                                                               |

| 12         | D6             | O   |                                                                                                                                                                             |

| 15         | D5             | O   |                                                                                                                                                                             |

| 16         | D4             | O   |                                                                                                                                                                             |

| 19         | D3             | O   |                                                                                                                                                                             |

| 20         | D2             | O   |                                                                                                                                                                             |

| 23         | D1             | O   |                                                                                                                                                                             |

| 24         | D0 (LSB)       | O   | Decoded data output pin (LSB)                                                                                                                                               |

| 31         | DVALID/VLOCK   | O   | Active Video Timing signal (720 Pixel)<br>It can also output VLOCK status by setting a register.                                                                            |

| 34         | FRAME1/CSYNC   | O   | When a standard signal is input, a color frame signal is output.<br>When a non-standard signal input, this pin outputs a timing signal that is toggled every 525/625 lines. |

| 35         | FRAME0         | O   | FRAME1 pin can output the CYSNC signal by setting a register.                                                                                                               |

| 36         | HALFCLKOUT     | O   | When Rec.656 data is output, this signal identifies the signal as Y or C.<br>(This rate is about 13.5MHz)                                                                   |

| 39         | CLK27MOUT      | O   | Output Timing of output data (About 27MHz)                                                                                                                                  |

| 40         | NSIG           | O   | When No-signal is input this pin goes High.                                                                                                                                 |

| 41         | NSTD           | O   | When Non-standard signal is input, this pin goes High.                                                                                                                      |

| 49         | CLKINV         | I   | This pin decides the polarization of CLK27MOUT.                                                                                                                             |

| 50         | /RESET         | I   | Reset Signal input pin. (Low Active)<br>After Power up or power down mode, Reset signal should be Low at least 10msec.                                                      |

| 52         | CLK            | I   | Input 27MHz Clock.                                                                                                                                                          |

| 54         | EXTCLP         | I/O | External Clamp timing input pin.                                                                                                                                            |

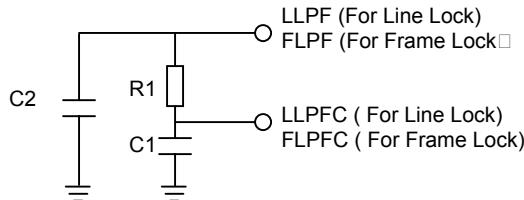

| 58         | LLPF           | O   | Connect Loop Filter for Line Lock clock.                                                                                                                                    |

| 59         | LLPFC          | O   | Connect Capacitors for Line Lock clock.                                                                                                                                     |

| 60         | FLPF           | O   | Connect Loop Filter for Frame Lock clock.                                                                                                                                   |

| 61         | FLPFC          | O   | Connect Capacitors for Frame Lock clock.                                                                                                                                    |

| 62         | VREFOUT        | O   | Internal Voltage Reference output pin.<br>Terminate with 0.1uF or larger capacitor between AVSS.                                                                            |

| 63         | IVCXO          | O   | Control voltage output pin for the external VCXO.<br>Connect via a resistor to AVSS.                                                                                        |

| 64         | IRefR1         | O   | Terminate with 13kΩ resistor (0.1% accuracy) to AVSS.<br>This Register sets the reference current for the PLL Block.                                                        |

| 65         | IRefR2         | O   | Terminate with 4.7kΩ Register (0.1% accuracy) between AVSS.<br>This Register sets the internal reference current.                                                           |

| 66         | VCOM           | O   | Internal common voltage for ADC output pin.<br>Terminate with 0.1uF or larger capacitor between AVSS.                                                                       |

| 67         | VRN            | O   | Internal negative voltage for ADC output pin.<br>Terminate with 0.1uF or larger capacitor between AVSS.                                                                     |

| 68         | VRP            | O   | Internal positive voltage for ADC output pin.<br>Terminate with 0.1uF or larger capacitor between AVSS.                                                                     |

| 69         | FBCAP3         | O   | Terminate using a 0.033uF capacitor between AVSS. (for Clamp Level)                                                                                                         |

|                                                              |         |     |                                                                                                                                                                |

|--------------------------------------------------------------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70                                                           | FBCAP2  | O   | Terminate 0.033uF capacitor between AVSS. (for Clamp Level)                                                                                                    |

| 71                                                           | FBCAP1  | O   | Terminate 0.033uF capacitor between AVSS. (for Clamp Level)                                                                                                    |

| 72                                                           | CLPCAP2 | O   | Terminate 0.1uF capacitor between AVSS. (for Clamp)                                                                                                            |

| 73                                                           | CLPCAP1 | O   | Terminate 0.1uF capacitor between AVSS. (for Clamp)                                                                                                            |

| 76                                                           | AIN1    | I   |                                                                                                                                                                |

| 80                                                           | AIN2    | I   |                                                                                                                                                                |

| 84                                                           | AIN3    | I   |                                                                                                                                                                |

| 91                                                           | AIN4    | I   |                                                                                                                                                                |

| 93                                                           | AIN5    | I   |                                                                                                                                                                |

| 95                                                           | AIN6    | I   |                                                                                                                                                                |

| 78                                                           | SYNC1   | I   |                                                                                                                                                                |

| 82                                                           | SYNC2   | I   |                                                                                                                                                                |

| 86                                                           | SYNC3   | I   |                                                                                                                                                                |

| 98                                                           | PD      | I   | Power Down Control Pin. When this pin becomes High, the AK8850 enters a power down state. When returning from power down mode, AK8850 requires reset sequence. |

| 56,75,88                                                     | AVDD    | P   | Analog power supply (3.3V) pin.                                                                                                                                |

| 55,57,74,<br>77,79,81,<br>83,85,87,<br>89,90,92,<br>94,96,96 | AVSS    | G   | Analog Ground pin.                                                                                                                                             |

| 9,13,17,<br>21,25,32,<br>37,42,53                            | DVDD    | P   | Digital power supply (3.3V) pin.                                                                                                                               |

| 5,10,14,<br>18, 2,33,<br>38,43,51                            | DVSS    | G   | Digital Ground pin.                                                                                                                                            |

| 26,27,28,<br>29,30,44,<br>45,46,47,<br>48                    | UD[9:0] | I/O | These pins are for test purpose. These pins should be NC.                                                                                                      |

| 1,44,45,<br>46,47,48,<br>97,99,<br>100                       | TEST    | I   | These pins are for test purpose. Connect to the DVSS.                                                                                                          |

## 4. Electrical Specifications

## 4-1. Absolute Maximum Ratings

| Item                                                 | Min.          | Max       | Unit      |

|------------------------------------------------------|---------------|-----------|-----------|

| Supply Voltage $\square$ VDD $\square$<br>DVDD, AVDD | $\square$ 0.3 | 4.5       | V         |

| Input Pin Voltage (Vin)                              | $\square$ 0.3 | VDD + 0.3 | V         |

| Input Pin Current (Iin)                              | $\square$ 10  | 10        | mA        |

| Storage Temperature                                  | $\square$ 40  | 125       | $\square$ |

note) each ground pin ( DVSS,AVSS ) is equal to 0 V (voltage reference ).

## 4-2. Recommended Operating Conditions

| Item                           | Min.         | Typ. | Max. | Unit      |

|--------------------------------|--------------|------|------|-----------|

| Supply Voltage<br>AVDD<br>DVDD | 3.0          | 3.3  | 3.6  | V         |

|                                | 3.0          | 3.3  | 3.6  | V         |

| Operating Temperature          | $\square$ 10 |      | 85** | $\square$ |

note) \* each ground pin ( DVSS,AVSS ) is equal to 0 V (voltage reference ).

\*\* Assumes mounting on a 4-layer PCB  $\square$ >100mm x 100mm x 1.6mm  $\square$ with wiring density greater than 60%.

## 4-3DC Characteristics ( DVDD=AVDD=3.0 ~ 3.6 V at room temperature )

| Item                                                               | Symbol | Min.   | Typ. | Max.     | Unit | Condition                       |

|--------------------------------------------------------------------|--------|--------|------|----------|------|---------------------------------|

| Digital Input High Voltage                                         | VIH    | 0.7VDD |      |          | V    |                                 |

| Digital Input Low Voltage                                          | VIL    |        |      | 0.3VDD   | V    |                                 |

| Digital Input Leak Current                                         | IIL    |        |      | $\pm$ 10 | uA   |                                 |

| Digital Output High Voltage                                        | VOH    | 2.4    |      |          | V    | $\square$ IOH = $\square$ 400uA |

| Digital Output High Voltage                                        | VOL    |        |      | 0.4      | V    | $\square$ IOL = 1.2mA           |

| I <sup>2</sup> C Input High Voltage<br>I <sup>2</sup> C (SDA, SCL) | VIHC   | 0.7VDD |      |          | V    |                                 |

| I <sup>2</sup> C Input Low Voltage<br>I <sup>2</sup> C (SDA, SCL)  | VILC   |        |      | 0.3VDD   | V    |                                 |

| I <sup>2</sup> C (SDA) L $\square$                                 | VOLC   |        |      | 0.4      | V    | $\square$ IOLC = 3mA            |

## 4-4. AC Characteristics

| Item                             | Symbol | Min. | Typ. | Max. | Unit | Condition |

|----------------------------------|--------|------|------|------|------|-----------|

| Digital Maximum Load Capacitance |        | 15   |      | 40   | pF   |           |

## 4-5. Analog Characteristics and Power Dissipation

## Selector and Clamp (AVDD=3.3V, Room Temperature)

| Item                                      | Symbol | Min. | Typ.     | Max. | Unit            | Condition    |

|-------------------------------------------|--------|------|----------|------|-----------------|--------------|

| Maximum Input Range (AIN1 $\square$ AIN6) | VIMX   | 1.20 | 1.28     |      | V <sub>PP</sub> | PGA Gain 0dB |

| Composite, Luminance Signal Clamp Level   | VYCP   |      | 0.70     |      | V               |              |

| C/U/V Signal Clamp Level                  | VCCP   |      | 1.34     |      | V               |              |

| Clamp Current                             | CLPI   |      | $\pm 70$ |      | uA              |              |

| Isolation between ADC                     |        |      | -60      |      | dB              | 5.5MHz       |

## PGA (AVDD=3.3V, Room Temperature)

| Item                   | Symbol | Min. | Typ.    | Max. | Unit | Condition |

|------------------------|--------|------|---------|------|------|-----------|

| Min.Gain               | GMN    |      | 0       |      | dB   |           |

| Max Gain               | GMX    |      | 12      |      | dB   |           |

| Gain Step              | GST    |      | 0.094   |      | dB   |           |

| Relative Gain accuracy | ERP    |      | $\pm 1$ |      | LSB  |           |

## ADC (AVDD=3.3V, Room Temperature)

| Item                       | Symbol | Min. | Typ.      | Max       | Unit | Condition                               |

|----------------------------|--------|------|-----------|-----------|------|-----------------------------------------|

| Resolution                 | RES    |      |           | 10        | bits |                                         |

| Operating Clock Frequency  | FS     |      | 27        |           | MHz  |                                         |

| Integral Non Linearity     | INL    |      | $\pm 2.0$ | $\pm 4.0$ | LSB  | fs=27MHz                                |

| Differential Non Linearity | DNL    |      | $\pm 0.8$ | $\pm 2.0$ | LSB  | fs=27MHz                                |

| S/N                        | SN     |      | 54        |           | dB   | fin=1MHz Ain= $\square$ 1dB<br>fs=27MHz |

| S/(N+D)                    | SND    |      | 51        |           | dB   | fin=1MHz Ain= $\square$ 1dB<br>fs=27MHz |

## Power Consumption (DVDD=AVDD=3.3V, Room Temperature)

| Item                          | Symbol | Min. | Typ. | Max | Unit | Condition                                                               |

|-------------------------------|--------|------|------|-----|------|-------------------------------------------------------------------------|

| Compensation Current (Active) |        |      | 216  | 280 | mA   |                                                                         |

| Digital + Analog              |        |      | 71   |     | mA   | 3ch operating                                                           |

| Analog                        |        |      | 145  |     | mA   | 25pFLoad, Color bar input                                               |

| Power Down Current Mode 1     |        |      |      |     |      | Mode 1: Set by Register                                                 |

| Digital + Analog              |        |      | 58   | 75  | mA   | Mode 2: Set by PD pin                                                   |

| Analog                        |        |      | 22   |     | mA   |                                                                         |

| Digital                       |        |      | 36   |     | mA   | *It requires several second from Mode 2 power down mode to Active mode. |

| Mode 2                        |        |      |      |     |      |                                                                         |

| Digital + Analog              |        |      | 0.01 | 0.2 | mA   |                                                                         |

| Analog                        |        |      | 0.01 |     | mA   |                                                                         |

| Digital                       |        |      | 0.01 |     | mA   |                                                                         |

## 4-6. AC Timing ( DVDD=3.0 ~ 3.6 V at 25 deg. C )

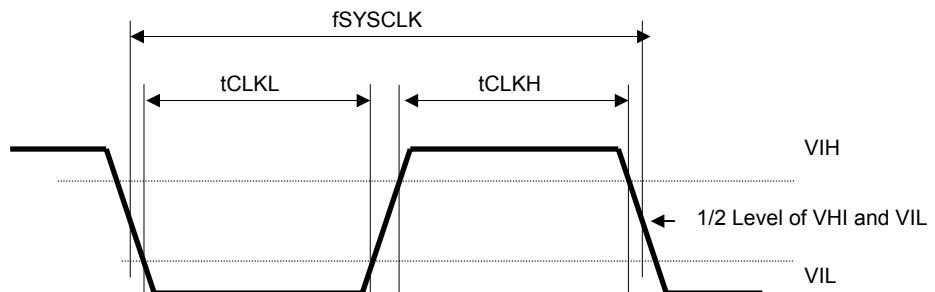

## 4-6-1 Clock Input

| item                   | Symbol       | Min. | Typ. | Max       | Unit |

|------------------------|--------------|------|------|-----------|------|

| CLK                    | $f_{SYSCLK}$ |      | 27   |           | MHz  |

| CLK pulse width (High) | $t_{CLKH}$   | 15   |      |           | nsec |

| CLK pulse width (Low)  | $t_{CLKL}$   | 15   |      |           | nsec |

| Stability of Clock     |              |      |      | $\pm 100$ | ppm  |

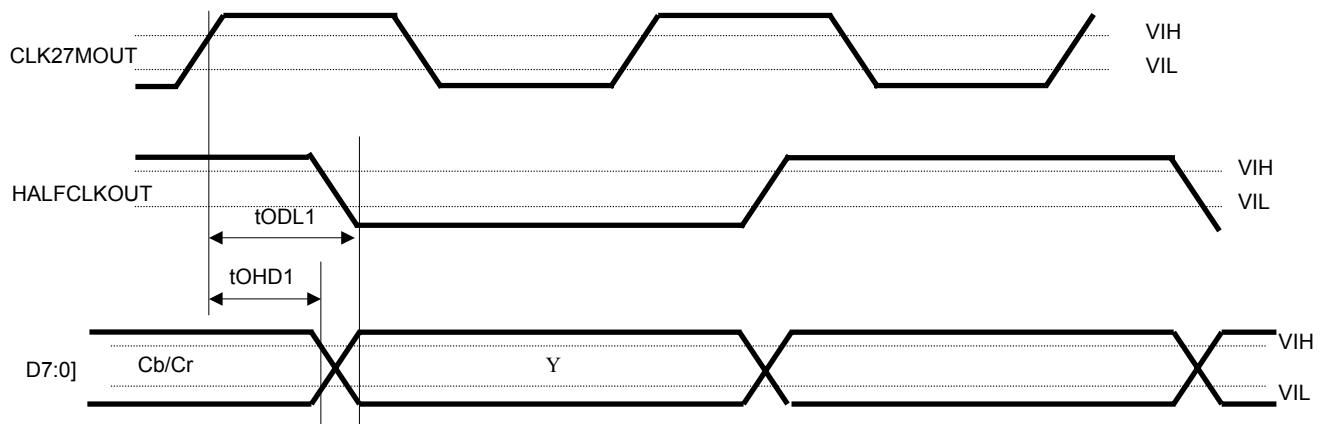

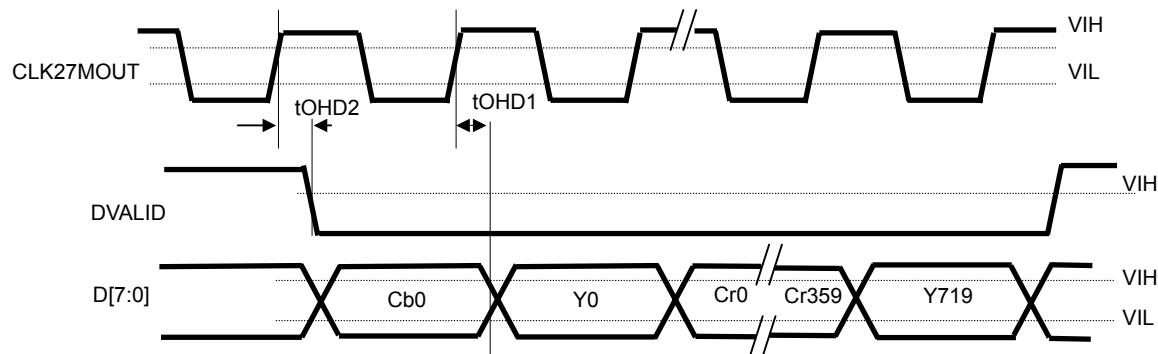

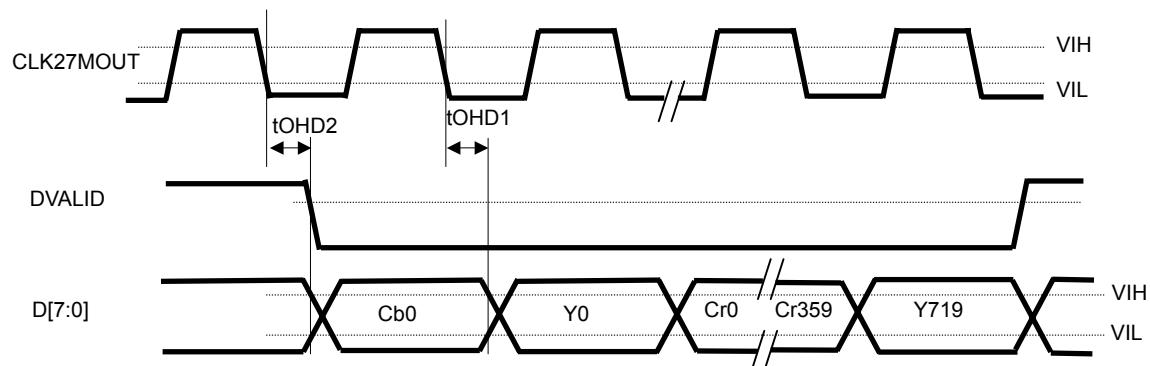

## 4-6-2 Output Data Timing ( D7 ~ D0 )

## 4-6-2-1 CLKINVpin = L

| Item                   | Symbol     | Min. | Typ. | Max. | Unit | Note    |

|------------------------|------------|------|------|------|------|---------|

| Output Data Delay Time | $t_{ODL1}$ |      |      | 25.0 | nsec |         |

| Output Data Hold Time  | $t_{OHD1}$ | 3.0  |      |      | nsec | CL 25pF |

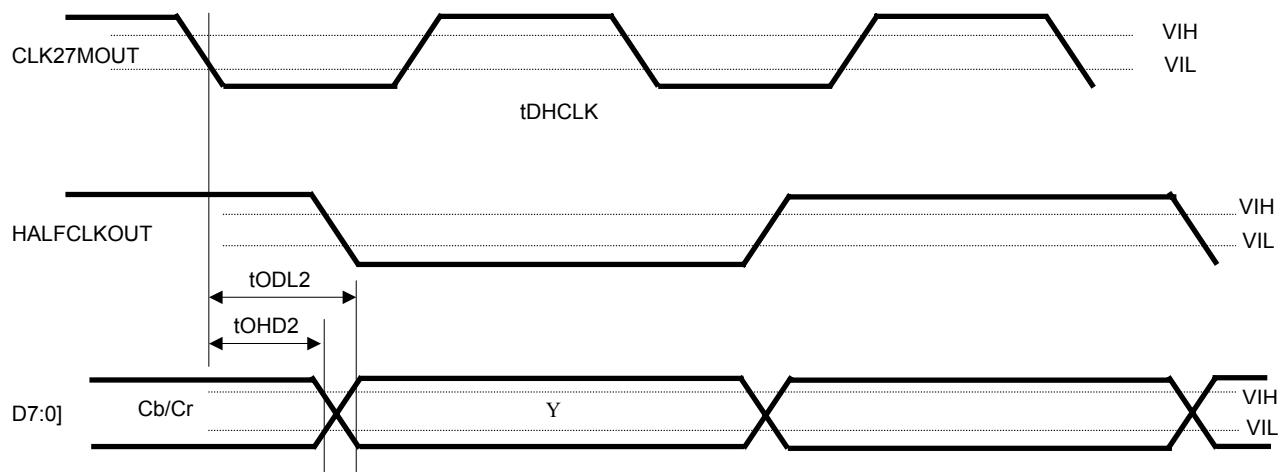

## 4-6-2-2 CLKINVpin = H

| Item                   | Symbol | Min. | Typ. | Max. | Unit | Note    |

|------------------------|--------|------|------|------|------|---------|

| Output Data Delay Time | tODL2  |      |      | 25.0 | nsec | CL 25pF |

| Output Data Hold Time  | tOHD2  | 3.0  |      |      | nsec |         |

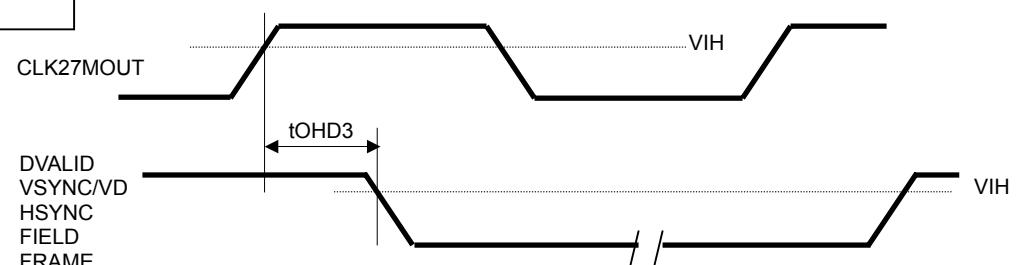

## 4-6-3 Output Data Timing ( DVALID/VSYNC/HSYNC/FIELD/FRAME0/FRAME1 )

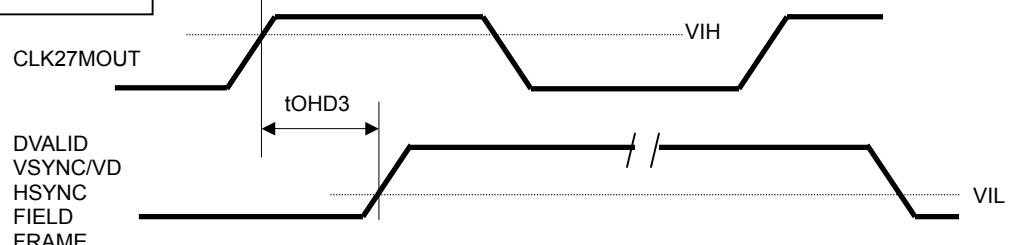

## 4-6-3-1 CLKINVpin = L

Output Control Register

DVALID=L

VSYNC=L

HSYNC =L

FIELD=L

FRAME=L

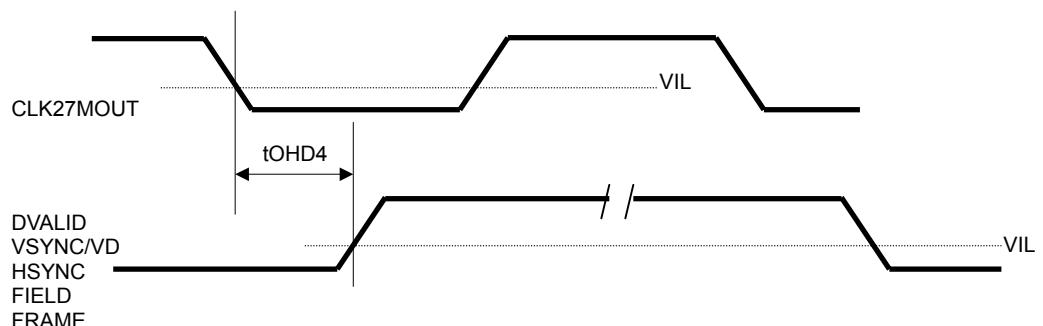

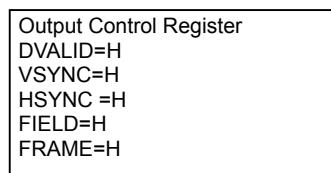

Output Control Register

DVALID=H

VSYNC=H

HSYNC =H

FIELD=H

FRAME=H

| Item                  | Symbol | Min. | Typ. | Max. | Unit | Note    |

|-----------------------|--------|------|------|------|------|---------|

| Output Data Hold Time | tOHD3  | 3.0  |      |      | nsec | CL 25pF |

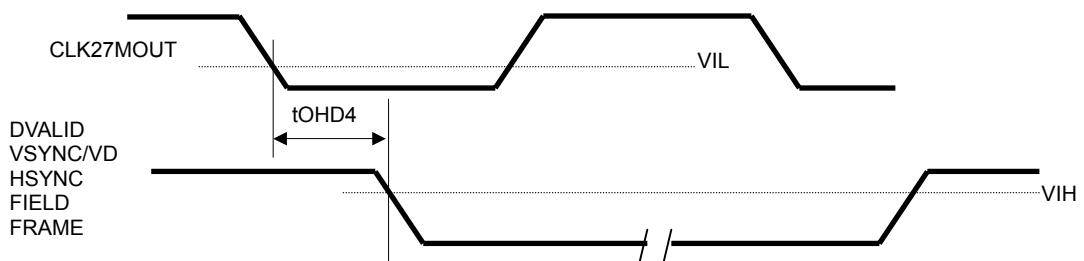

## 4-6-3-2 CLKINVpin = H

| Item                  | Symbol     | Min. | Typ. | Max | Unit | Note    |

|-----------------------|------------|------|------|-----|------|---------|

| Output Data Hold Time | $t_{OHD4}$ | 3.0  |      |     | nsec | CL 25pF |

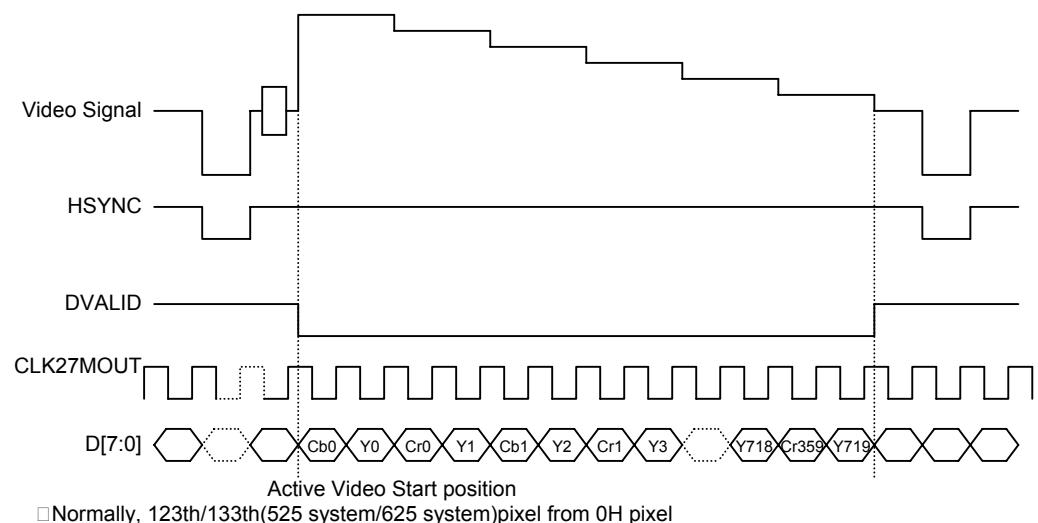

## 4-6-4 Output Data Timing ( CLK27MOUT, DVALID signal, D7~D0 relation )

## 4-6-4-1 CLKINVpin L and Output Control Register DVALID-bit=L

## 4-6-4-3 CLKINV pin H and Output Control Register DVALID-bit=L

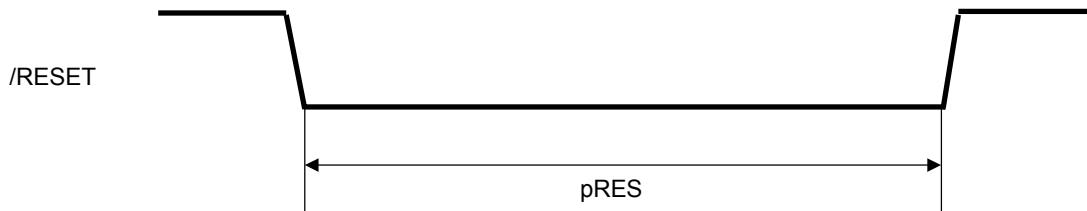

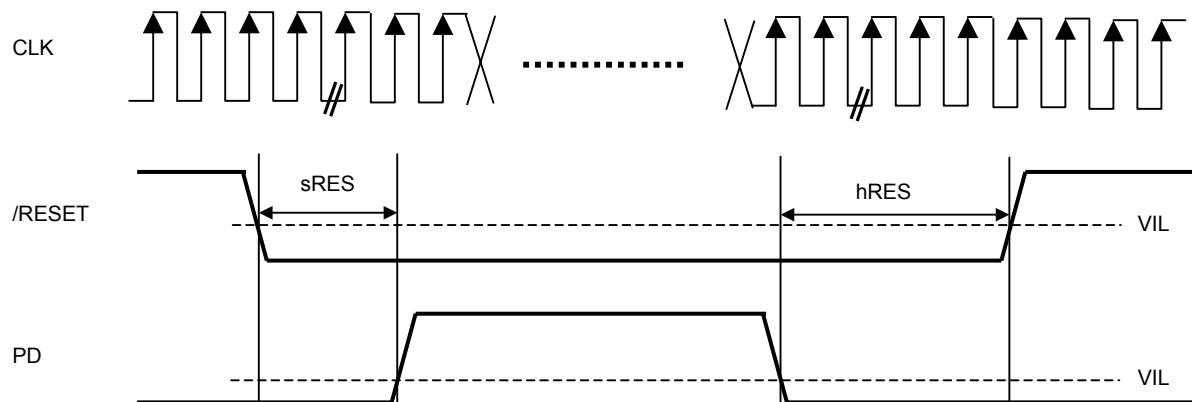

## 4-6-5 Reset Timing ( initialization )

Reset Signal ( Reset Signal should be held Low state for 10msec or longer)

| Item               | Symbol | Min. | Typ. | Max. | Unit | Note |

|--------------------|--------|------|------|------|------|------|

| /RESET Pulse width | pRES   | 10   |      |      | msec |      |

Note □ System Control Pins (SELA, CLKINV, PD etc.) remain in their states for at least 10 clock cycles before/after a reset signal input.

## 4-6-6 Power-Down / Up Sequence

| Item                                       | Symbol | Min. | Typ. | Max. | Unit | Note                 |

|--------------------------------------------|--------|------|------|------|------|----------------------|

| RESET pulse width (Setting PD mode)        | sRES   | 100  |      |      | CLK  | from CLK Rising edge |

| RESET pulse width (Returning from PD mode) | hRES   | 10   |      |      | msec |                      |

Note) After PD pin becomes High (power down state), /RESETpin status is irrelevant.

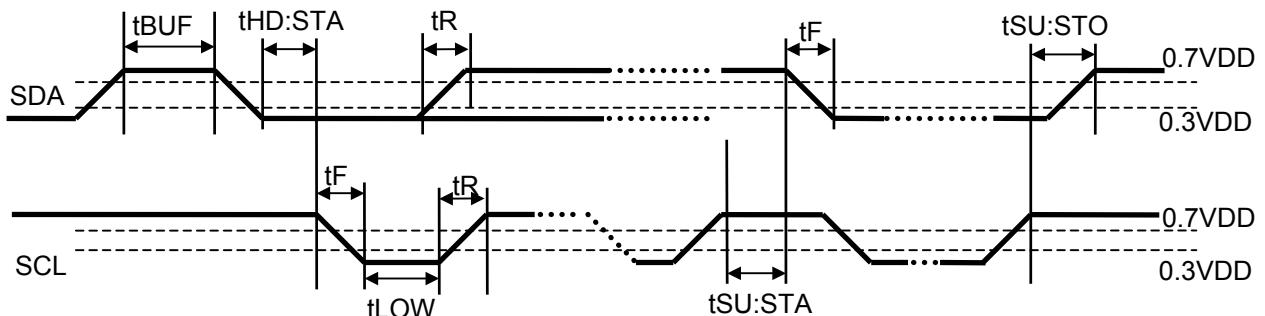

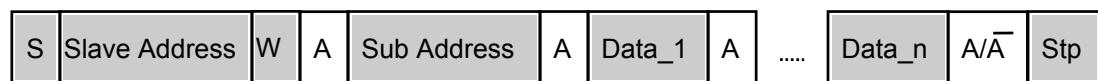

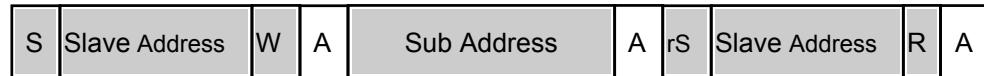

4-6-7 I<sup>2</sup>C bus Input & Output Timing ( SCL 400KHz cycle mode )

## (1) Timing 1

| Item                        | Symbol  | Min. | Max. | Unit |

|-----------------------------|---------|------|------|------|

| Bus Free Time               | tBUF    | 1.3  |      | usec |

| Hold Time (Start Condition) | tHD:STA | 0.6  |      | usec |

| Clock Pulse Low Time        | tLOW    | 1.3  |      | usec |

| Input Signal Rise Time      | tR      |      | 300  | nsec |

| Input Signal Fall Time      | tF      |      | 300  | nsec |

| Setup Time(Start Condition) | tSU:STA | 0.6  |      | usec |

| Setup Time(Stop Condition)  | tSU:STO | 0.6  |      | usec |

All the figures shown above are not defined by the AK8850 but are defined by I<sup>2</sup>C Bus standard.

Please see the I<sup>2</sup>C Bus standard for further details

## (2) Timing 2

| Item                  | Symbol  | Min.   | Max.   | Unit |

|-----------------------|---------|--------|--------|------|

| Data Setup Time       | tSU:DAT | 100(1) |        | nsec |

| Data Hold Time        | tHD:DAT | 0.0    | 0.9(2) | usec |

| Clock Pulse High Time | tHIGH   | 0.6    |        | usec |

(1) In case of normal I<sup>2</sup>C bus mode tSU:DAT  $\geq$  250nsec

(2) Using under minimum tLOW, this value must be satisfied.

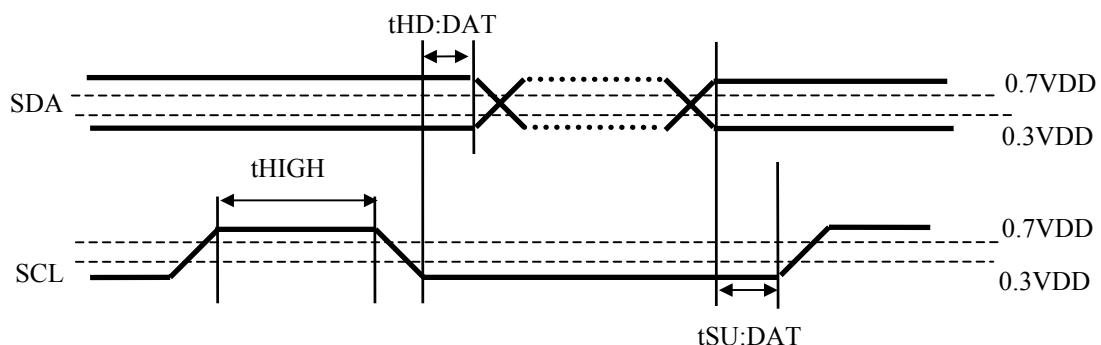

## 5. Output Signal Timing Description

### 5-1. NTSC Input

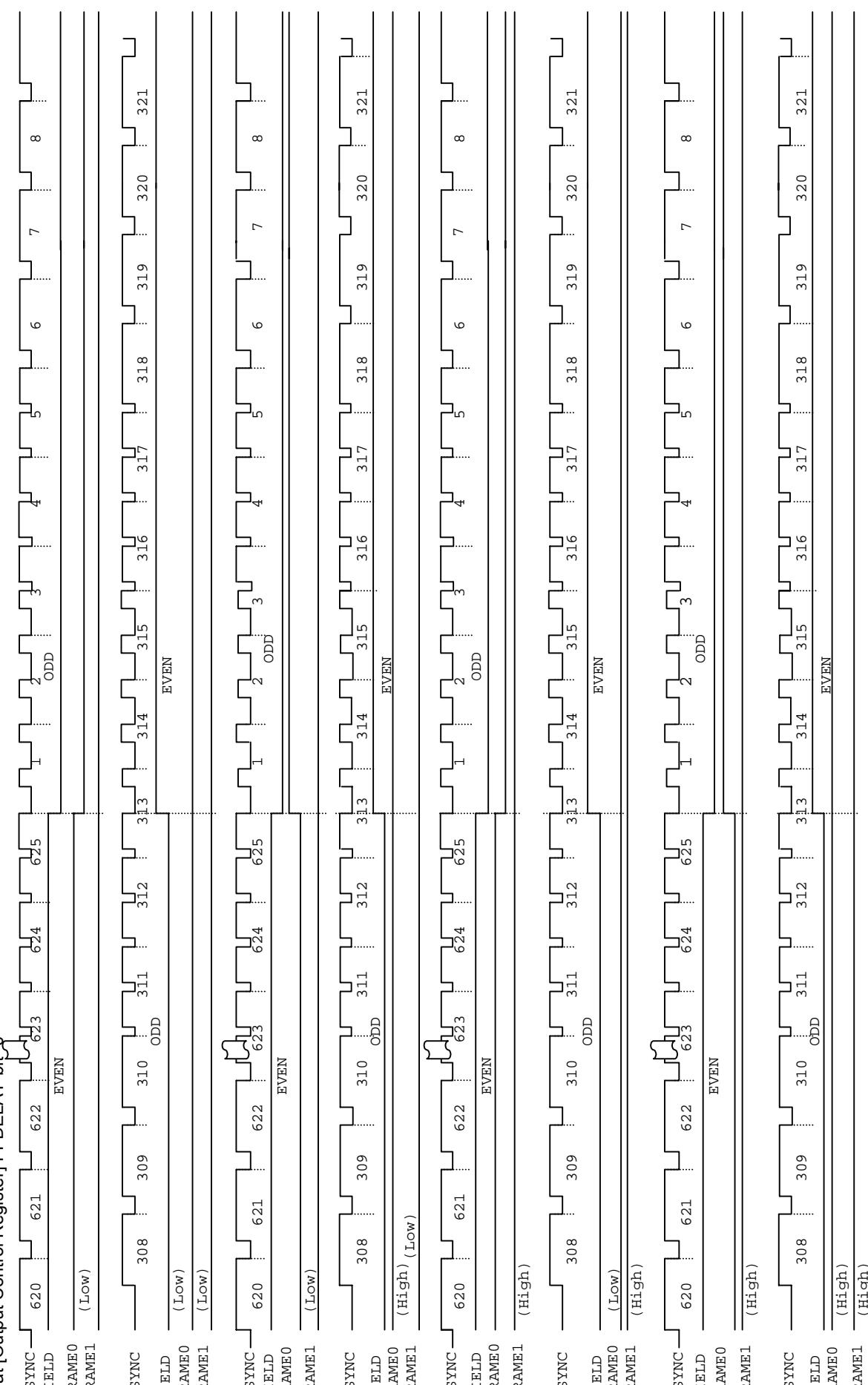

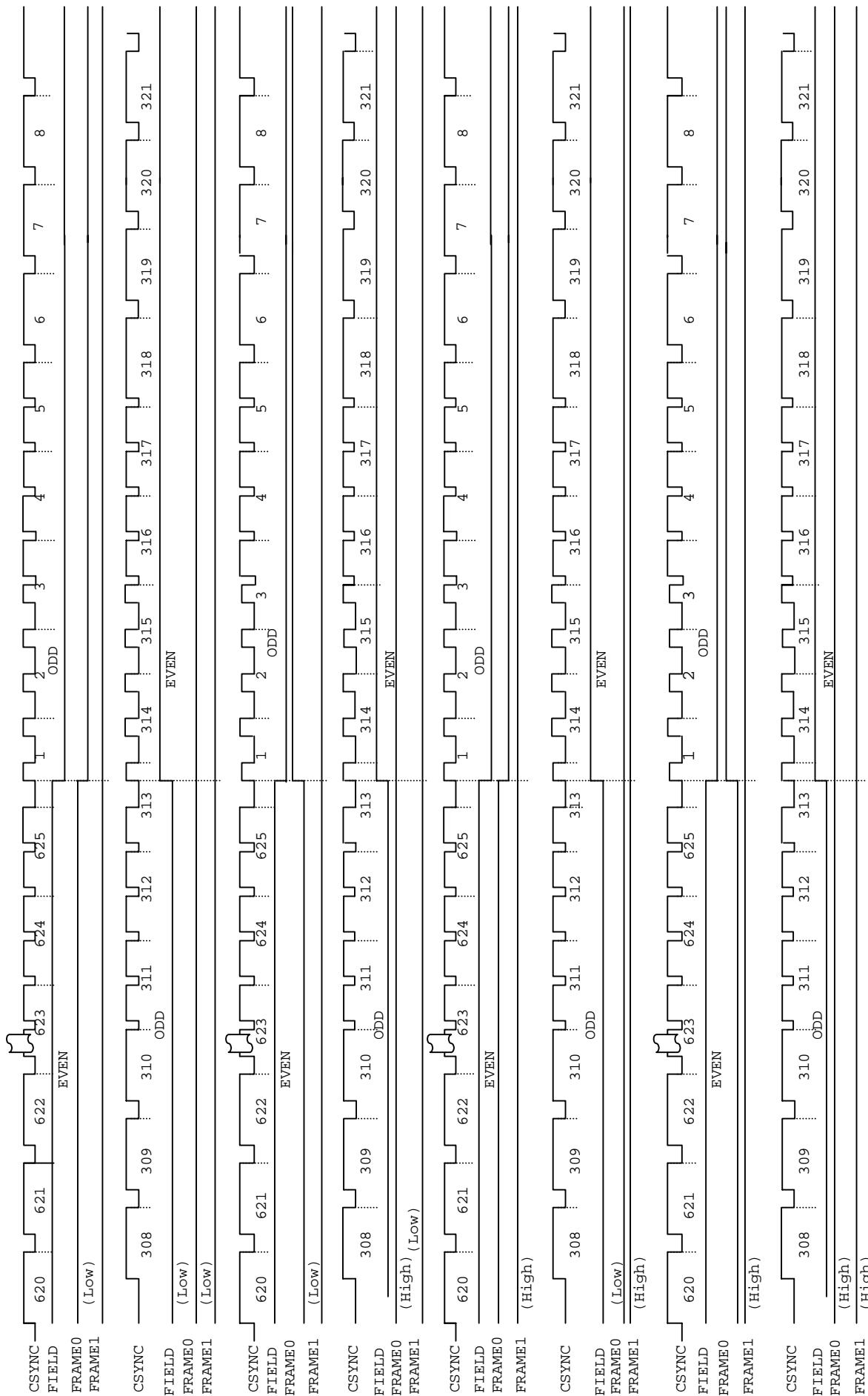

Vertical Sync timing, Field signal and Frame signal timing relations are shown below. The logic states of HSYNC/VSYNC/FIELD/FRAME can be altered via register settings. Depending on the register setting either VSYNC or VD signal is available. FIELD output and FRAME output signals change states on the rising edge of CSYNC just before the 0.5H delay period that is controlled by the Output Control Register. The 0.5H delay timing is shown on page 18.

(High) Frame timing signal output is as shown above when standard signals are input to the AK8850. If a Non-standard signal is input to AK8850, the number of Color frame is not guaranteed. When the input signal changes from non-standard to standard, that the Frame timing signal may not change for 512 lines (max) as the AK8850 synchronizes to the input video signal.

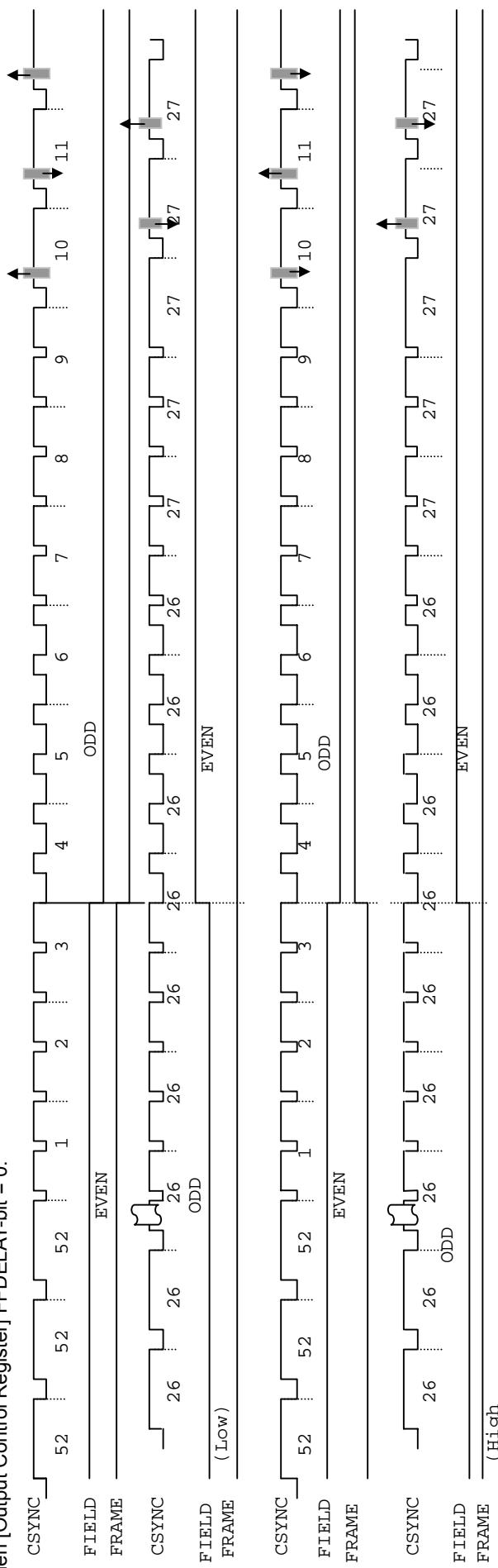

## 5-2. FIELD/FRAME Signal Output Timing Diagram with NTSC signal input (CSYNC & FIELD/FRAME0/FRAME1 relationships)

when [Output Control Register] FFDELAY-bit = 0:

at [Output Control Register] FFDELAY-bit = 1:

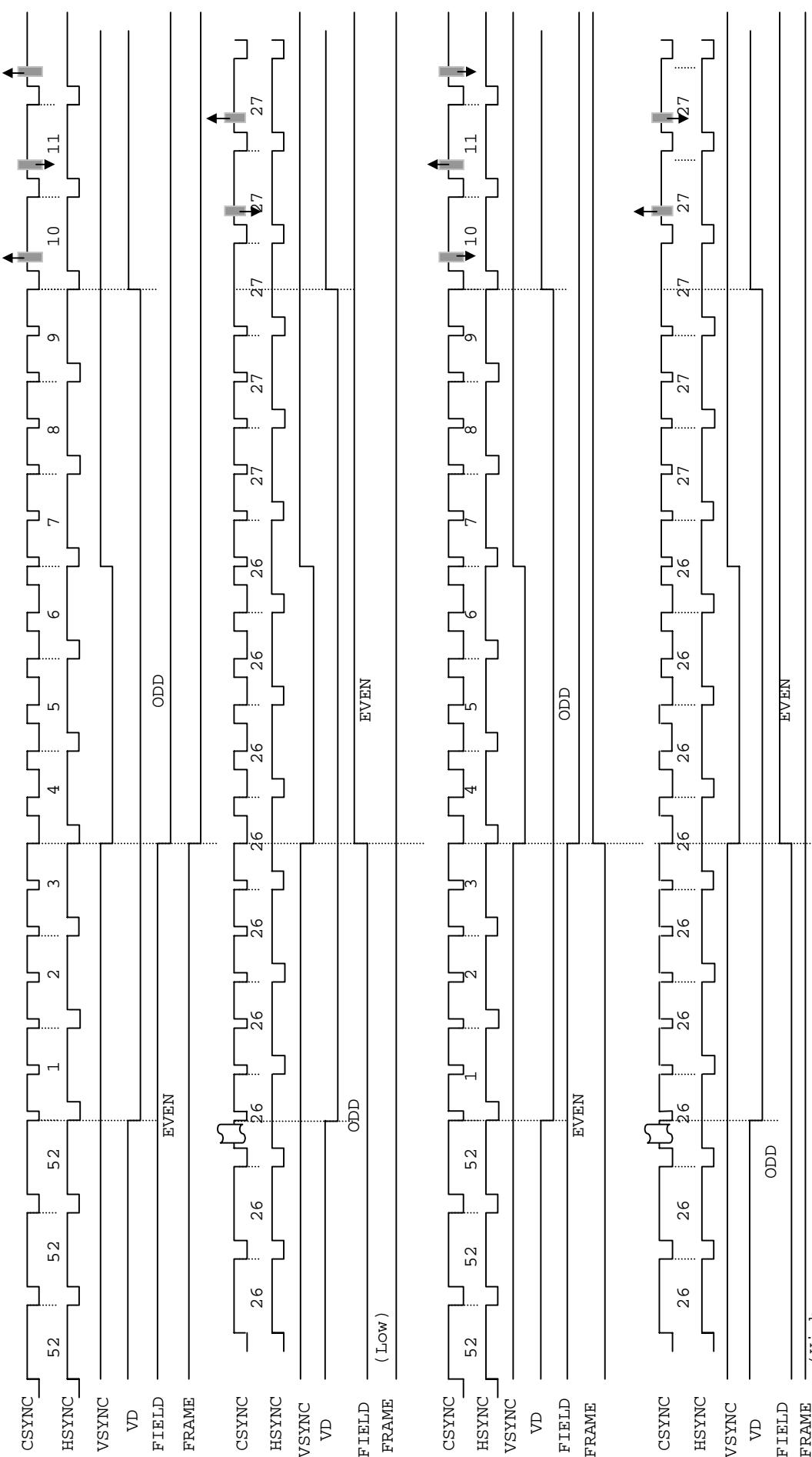

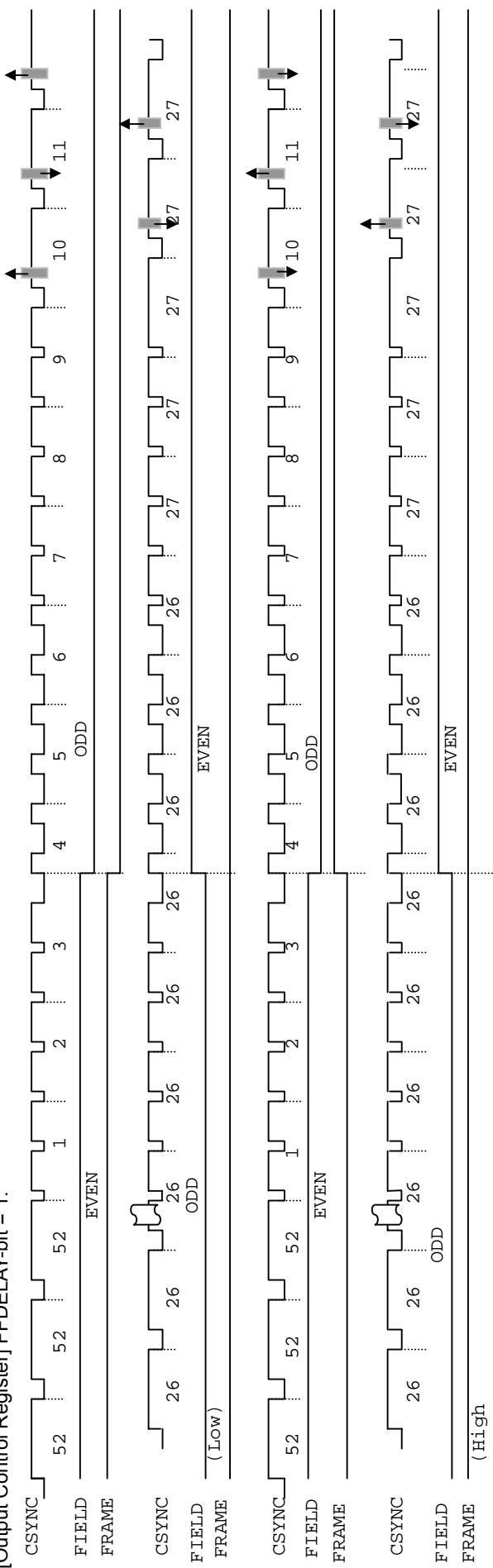

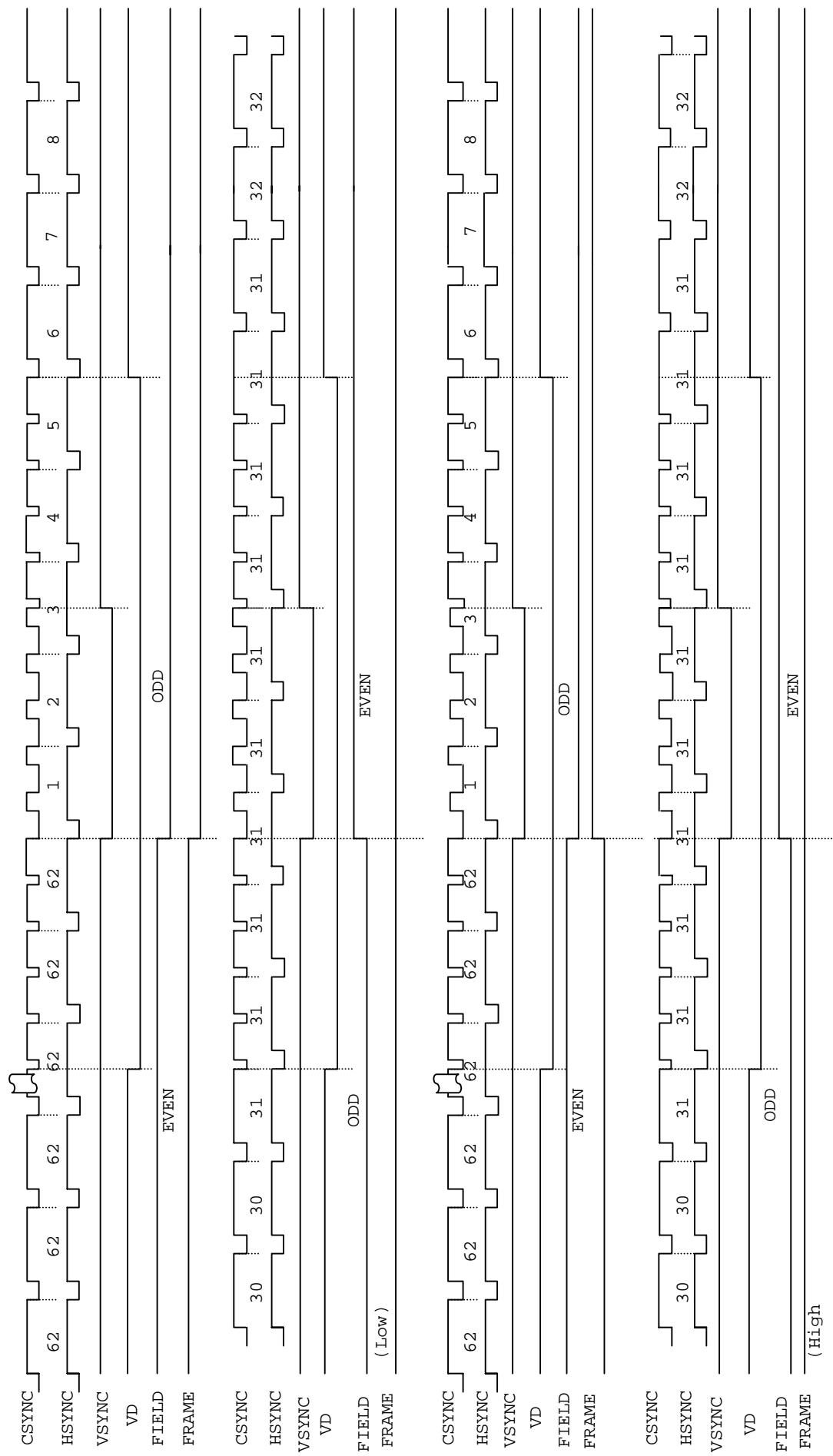

### 5-3. Output Signal Timing Diagram ( CCI-R625 Component input )

The VERTICAL Sync, FIELD signal and FRAME signal timing relationships are shown. The logical state of HSYNC/VSYNC/FIELD/FRAME can be altered by using register settings. Either VSYNC or VD output signals are available on the VSYNC output pin, depending upon the register setting. The FIELD output and the FRAME output signals change state on the rising edge of the CSYNC, prior to the 0.5H delay period that is controlled by the output control register. Field/FRAME output timings are shown on pages 20 and 21.

### 625 Component Signal Output Timing Diagram ( CSYNC & FIELD/FRAME0/FRAME1 relationship )

5-5 625 Component Signal Output Timing Diagram ( CSYNC & FIELD/FRAME0/FRAME1 relationship )

when [Output Control Register] FFDELAY-bit = 1

## 6. Functional Summary

### 6-1. Clock

#### 1. Line Locked Clock mode:

An operating mode where the device operates using a clock synchronized with the Horizontal Sync signal for each line.

#### 2. Frame Locked Clock mode:

The device operates using a clock synchronized with the Vertical Sync signal at each Frame.

#### 3. Fixed Clock mode:

An external clock is used.

These clock modes are set with the Control 2 register. Since both the Line Locked and Frame Locked modes use an input-signal synchronized clock, ITU-R BT.656\* compatible output is available, although input signal quality may prevent full ITU-R BT.656 compatibility.

### 6-2. Analog Interface

The AK8850 decodes NTSC-M compatible Composite video signals, S-video and Component signals. For CCIR625 systems, only the Component signal is used. Registers control setup selection.

### 6-3. Input Signals

The device accepts NTSC-M Composite, S-Video, Composite (Betacam, MII) and 625 Component signals (EBU N10). Required input signal quality is as follows.

#### 6-3-1 Composite, S video input signal quality

| Item                                              | Input Range | Unit | Condition                                             |

|---------------------------------------------------|-------------|------|-------------------------------------------------------|

| Video signal input level                          | $\pm 6$     | dB   | Video signal should be input with -6dB level          |

| Color Burst input level $\square \square \square$ | $\pm 10$    | dB   | (divided by a resistor), and through 0.1uF capacitor. |

#### 6-3-2. Supporting signal characteristics for Composite and S-video signals

| Item                   | Process                                                                                                                                                  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lack of HSYNC          | Running with self timing                                                                                                                                 |

| Lack of VSYNC          | Running with self-timing. When VSYNC is absent for two consecutive cycles, the AK8850 identifies this as a "no-signal" state and sets the NSIG pin High. |

| B/W Video Signal input | Set B/W mode using the register.                                                                                                                         |

#### 6-3-3. Component input signal

A Standard signal is applied in Component decode mode. Supported Component signal conditions are listed below.

| Input video source        | Sync level | Luminance (Setup Level) | Luminance Level (max) | Luminance (Range) | U/V (Range) | Note                          |

|---------------------------|------------|-------------------------|-----------------------|-------------------|-------------|-------------------------------|

| BETACAM (w/o Setup)       | 286        | 0                       | 714                   | 714               | $\pm 504$   | Luminance 100% U/V 100% Level |

| BETACAM (with 7.5% Setup) | 286        | 53.6                    | 714                   | 660.4             | $\pm 350$   | Luminance 100% U/V 75% Level  |

| MII (w/o Setup)           | 300        | 0                       | 700                   | 700               | $\pm 350$   | Luminance 100% U/V 100% Level |

| MII (with Setup)          | 300        | 52.5                    | 700                   | 647.5             | $\pm 243$   | Luminance 100% U/V 75% Level  |

| 625 system (EBU N10)      | 300        | 0                       | 700                   | 700               | $\pm 350$   | Luminance 100% U/V 100% Level |

#### 6-4. Analog Input Signal Processing

Input Selector : -60 dB (inter-channel isolation)

PGA : 0 ~ 12 dB

AD converter : operates at 27 MHz

Line-lock or Frame-lock PLL clocks are used in normal operation.

#### 6-5. Y/C Separation Function

Adaptive Y/C separation:

Adaptive Y/C separation enables adjustment of the Chroma Signal Bandwidth. Adaptive Y/C Separation can also be fixed to either 3-line 2 dimensional Y/C separation or single dimension Y/C separation.

#### 6-6. Output Signal Bandwidth

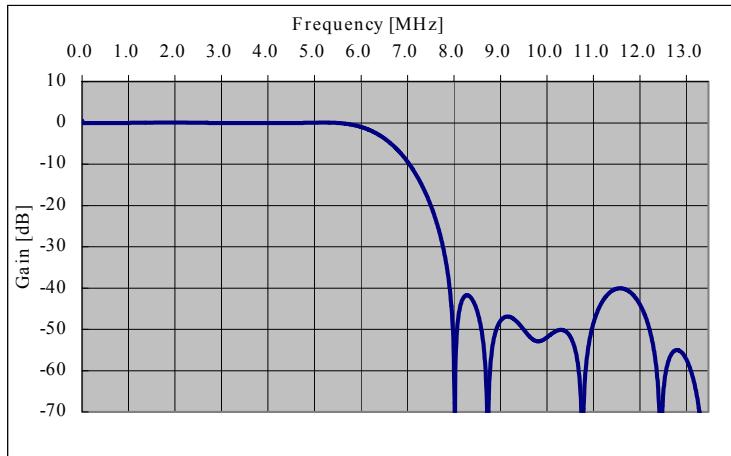

At Composite signal input,

Luminance Signal Bandwidth : DC ~ 5.75 MHz + 0.5 /- 1.5 dB

Chroma Signal Bandwidth : +/- 500 KHz ~ +/- 1 MHz ( -3 dB ) ( 3 ranges selectable )

At Component signal input,

Luminance Signal Bandwidth : DC ~ 5.75 MHz +0.5 / -1.5 dB

Chroma Signal Bandwidth : DC ~ 5.75 MHz +0.5 / -1.5 dB

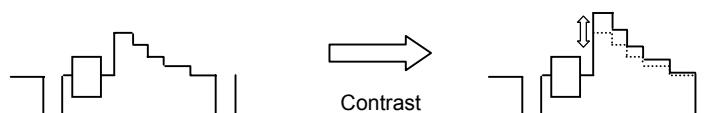

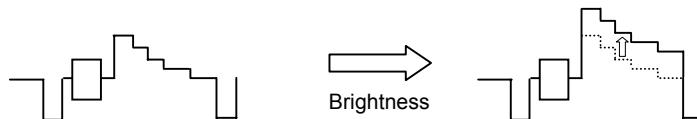

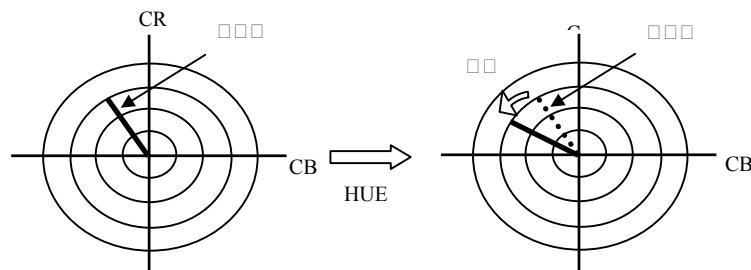

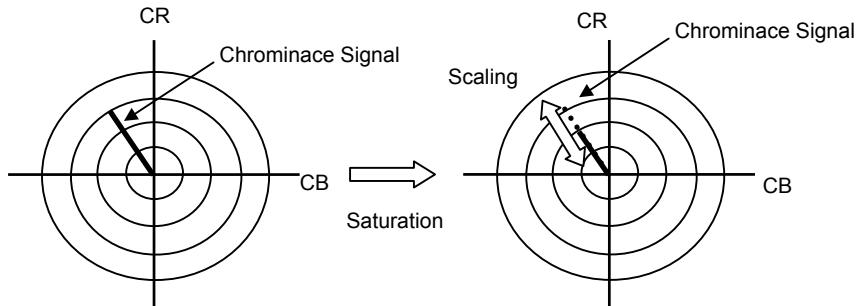

#### 6-7. Video Quality Control Function

Contrast, Brightness, HUE and Color Saturation levels are adjustable.

No HUE adjustment is possible when a Component video signal is input.

#### 6-8. Output Interface

- ITU-R BT.601 compatible signal output levels

- Decoded data is output in ITU-R BT.656 format ( depends on the input signal quality ).

- Ability to detect signals during Active Video period using HSYNC/VSYNC ( FIELD )/ DVALID signals

- 8-Bit output at 27 MHz rate

#### 6-9. Other Functions

- Black level signal is output when no signal is applied ( Y = 16Cb,Cr = 128 )

- "Lack of signal" input detection

- I2C Bus Interface ( 400 KHz )

- Power Save Mode

- Closed Caption, VBID, WSS and Video Aspect ratio decoding Functions.

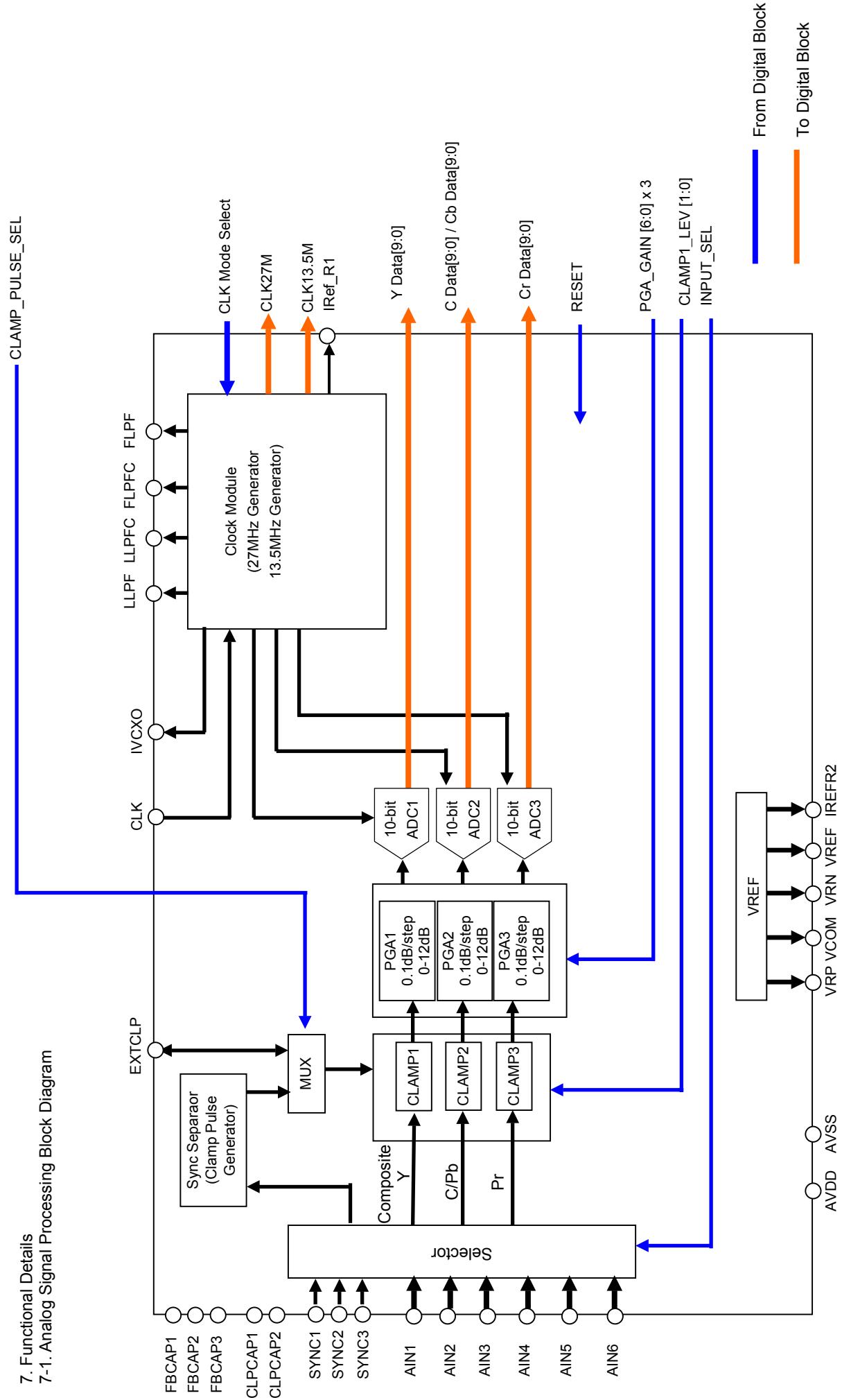

## 7. Functional Details

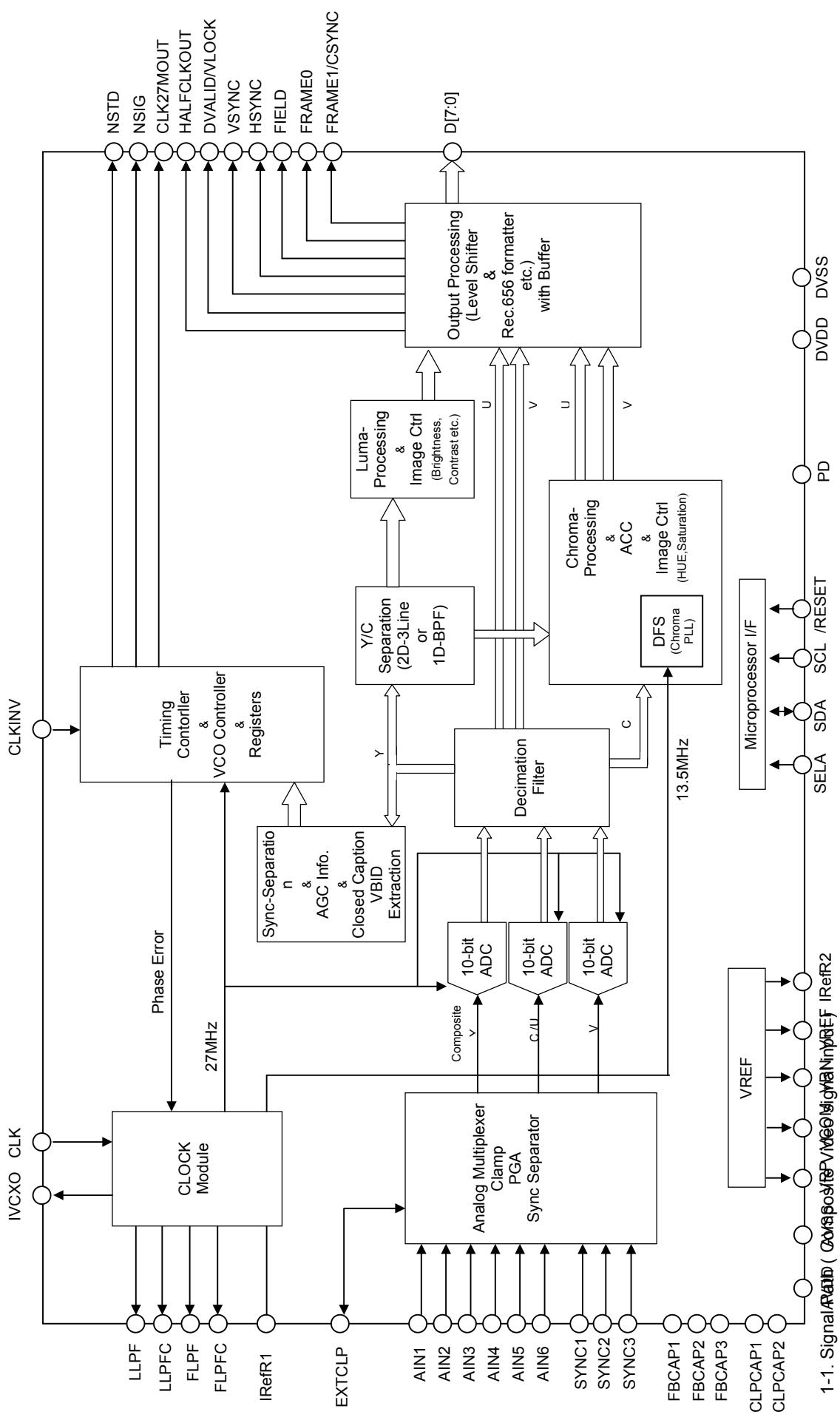

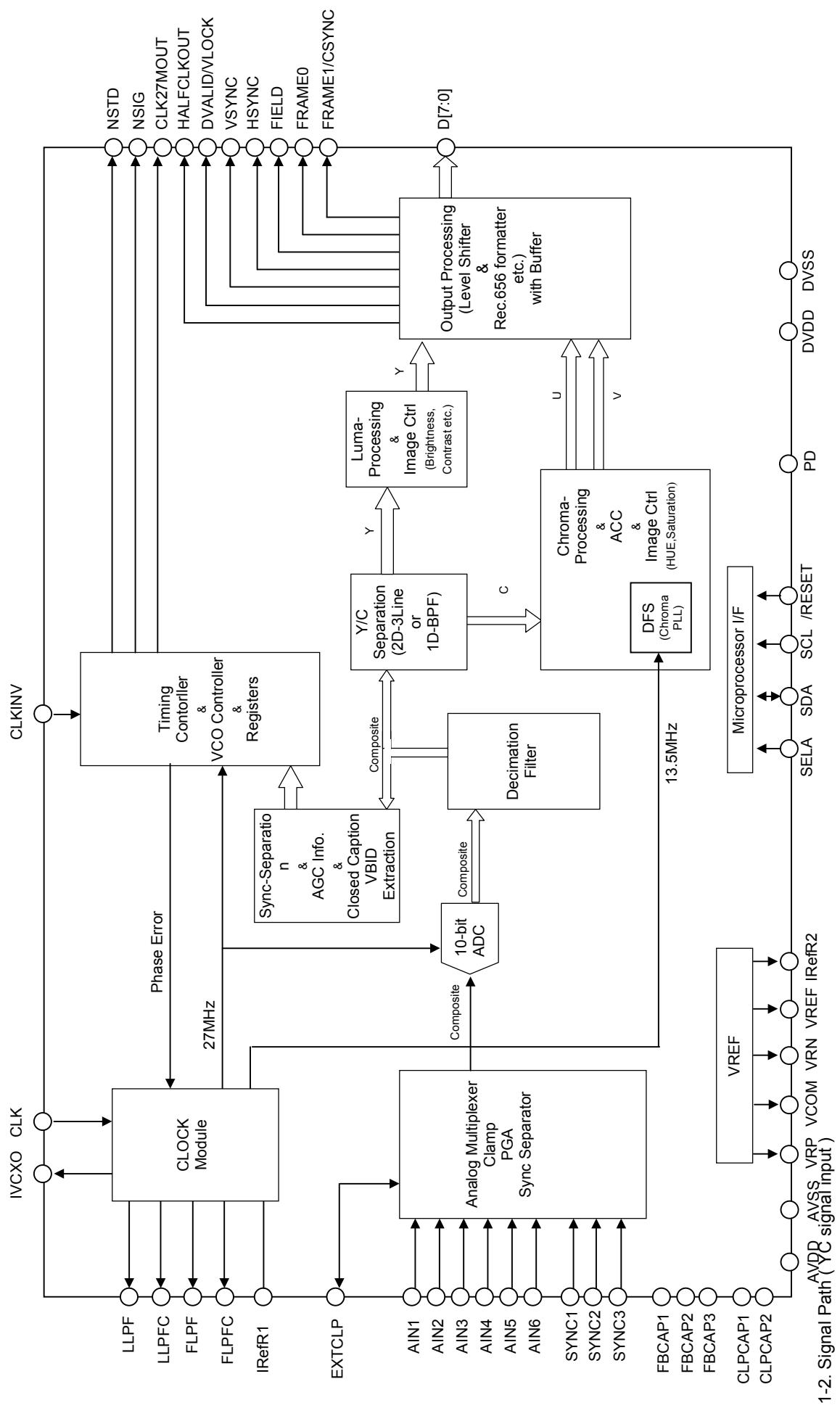

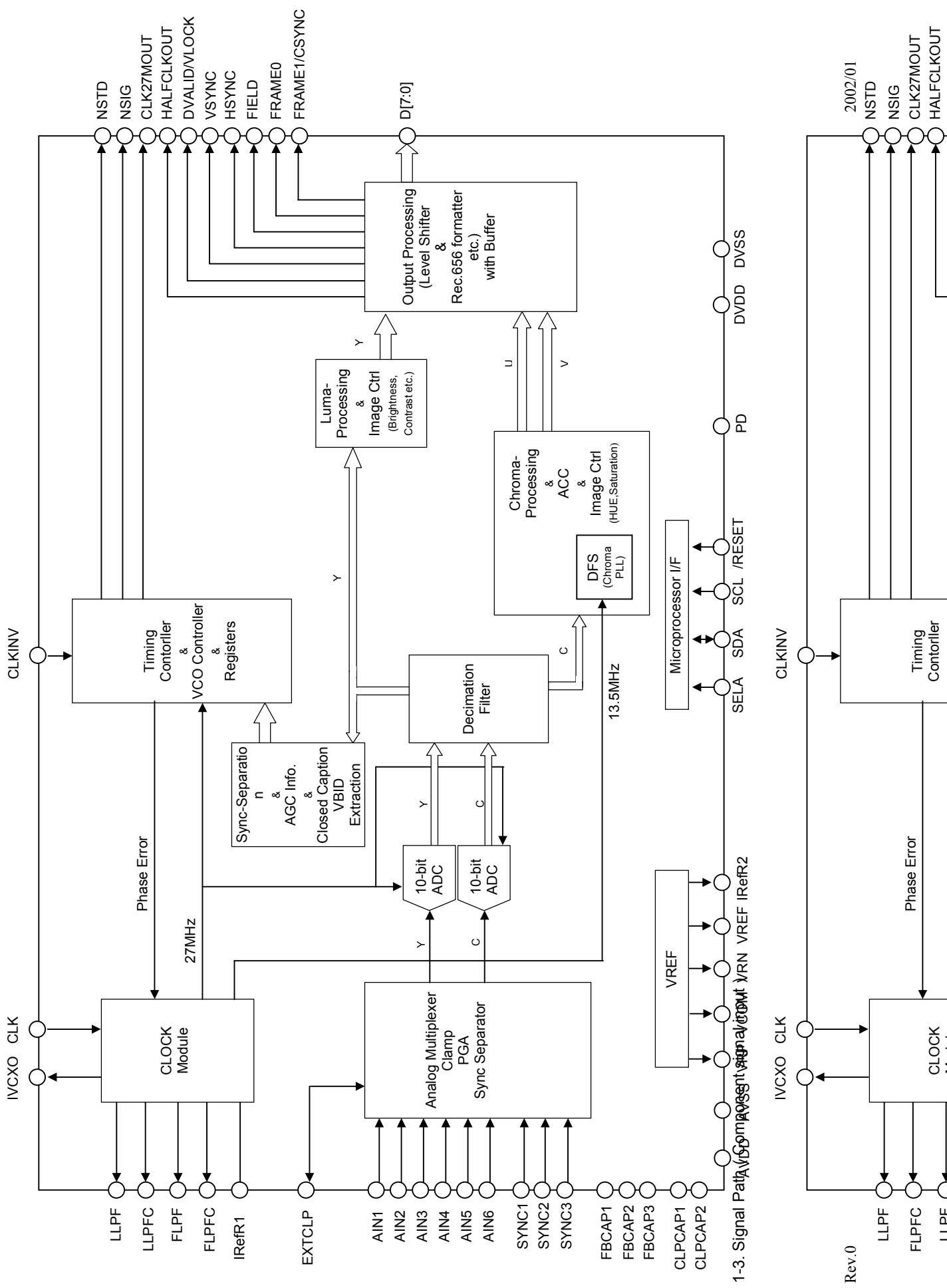

### 7.1. Analog Signal Processing Block Diagram

## 7-2. Analog Signal Process Functional Specifications

### 7-2-1. Input Signal Selector Module

The AK8850 has six (6) input pins. The input signal selector module selects one of the video sources. The Video sources available are single-pin Composite, 2-pin Y / C and 3-pin Component signals. A Video source to be decoded is selected by the [INPUT SIGNAL SELECT REGISTER].

The type of Video signal to be decoded is set by the [INPUT VIDEO STANDARD REGISTER].

#### COMPOSITE SIGNAL INPUT:

This input is digitized by the CLAMP1, PGA1 and ADC1 in the Analog Signal Processing Block Diagram. When decoding composite video, the ADC2 and ADC3 blocks can be placed in power save mode by programming the [ POWER SAVE REGISTER].

#### Y/C SIGNAL (S-VIDEO ) INPUT:

The Y-signal is digitized by the CLAMP1, PGA1 and ADC1 as in the Composite signal input case. The C Signal is digitized by the CLAMP2, PGA2 and ADC2. The ADC3 block can be placed in Power Save mode by programming the [ POWER SAVE REGISTER ].

#### COMPONENT SIGNAL INPUT:

In this case, the Y signal is digitized by the CLAMP1, PGA1 and ADC1 as in the Composite signal input case. The Pb signal is digitized by the CLAMP2, PGA2 and ADC2, while the Pr signal is digitized by the CLAMP3, PGA3 and ADC3.

Description of the input signal-type set register and input signal select control register:

The input signal type is set by the [ INPUT VIDEO STANDARD REGISTER ] and input signal path is selected by the [ INPUT SIGNAL SELECT REGISTER ].

#### [Input Video Standard Register]

| bit 7         | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| Reserved      | NENT  | B/W   | SETUP | VS3   | VS2   | VS1   | VS0   |

| Default Value |       |       |       |       |       |       |       |

| 0             | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### [Input Signal Select Register]

| bit 7         | bit 6    | bit 5   | bit 4   | bit 3  | bit 2  | bit 1  | bit 0  |

|---------------|----------|---------|---------|--------|--------|--------|--------|

| Reserved      | Reserved | SYNCIN1 | SYNCIN0 | INSEL3 | INSEL2 | INSEL1 | INSEL0 |

| Default Value |          |         |         |        |        |        |        |

| 0             | 0        | 0       | 1       | 0      | 0      | 0      | 1      |

[ VS3 : VS0]-bit and NENT-bit setting are also described.

#### [Input Video Standard Register] [VS3:VS0]-bit setting

| [VS3:VS0]-bit | Input Signal source     | Note |

|---------------|-------------------------|------|

| 0000          | NTSC                    |      |

| 1111          | Component 625 (EBU N10) |      |

SETUP-bit :

| SETUP-bit | Setup or No-Setup    | Note |

|-----------|----------------------|------|

| 0         | No Setup in          |      |

| 1         | With Setup signal in |      |

B/W-bit : for Black and White video signal

| B/W-bit | B/W signal or not            | Note                             |

|---------|------------------------------|----------------------------------|

| 0       | Color video signal           |                                  |

| 1       | Black and White video Signal | YC separation function turns off |

NENT-bit : Setting for Component signal input

| NENT-bit | Signal source of Component | Note             |

|----------|----------------------------|------------------|

| 0        | MII                        | 300mV Sync level |

| 1        | Betacam                    | 286mV Sync level |

(Supplement)

There are 3 categories of Video signals which are summarized in Table 7-2-1-1 below.

| Classifying                |                                  | Signal source           |

|----------------------------|----------------------------------|-------------------------|

| No. of Lines<br>in a Frame | 525-lines system                 | NTSC Composite          |

|                            |                                  | NTSC YC                 |

|                            |                                  | MII Component           |

|                            |                                  | Betacam Component       |

|                            | 625-lines system                 | 625 (EBU-N10) Component |

| Sync Level                 | 286mV Sync level<br>(40IRE □□□□) | NTSC Composite          |

|                            | NTSC YC                          |                         |

|                            | Betacam                          |                         |

|                            | 300mV Sync level                 | MII Component           |

|                            |                                  | 625 (EBU-N10) Component |

Table 7-2-1-1

The input signal path ( input signal setting) is selected by [ INSEL3 : INSEL0 ]-bits ( BIT-3:BIT0) in the [ INPUT SIGNAL SELECT REGISTER].

The upper 2-bits ( INSEL3 : INSEL2 ) identify Composite /YC and Component signals.

| [INSEL3:INSEL0] (bit3:bit0) □□□ | Signal Select                                               |

|---------------------------------|-------------------------------------------------------------|

| [0,0,0,0]                       | No Signal is selected.                                      |

| [0,0,0,1]                       | Composite signal is input from AIN1 (Default)               |

| [0,0,1,0]                       | Composite signal is input from AIN2                         |

| [0,0,1,1]                       | Composite signal is input from AIN3                         |

| [0,1,1,0]                       | Y-Signal from AIN2<br>C-Signal from AIN4                    |

| [0,1,1,1]                       | Y-Signal from AIN2<br>C-Signal from AIN4                    |

| [1,0,1,1]                       | Y-Signal from AIN3 U-Signal from AIN5<br>V-Signal from AIN6 |

As shown in the above table ,the AK8850 accepts following 4 input signals:

- Composite signal x 3 ch

- Composite signal x 2 ch + Y / C input x 1 ch

- Composite signal x 1 ch + Y / C input x 2 ch

- Composite signal x 1 ch + Y / C input x 1 ch + Component signal x 1 ch

Please refer to item ( 1-6 ) of Section 7-2-2 CLAMP for SYNC 1 / 2 / 3 combinations.

Register settings for the various input signal types are summarized in the following Table 7-2-1-2.

For Black & White signal input, set [ B / W ]-bit to "1".

| Input<br>Signal<br>Register<br>bit setting | NTSC Composite □ 525 Component |            |            |            |           |          |       |          | 625-System |

|--------------------------------------------|--------------------------------|------------|------------|------------|-----------|----------|-------|----------|------------|

|                                            | Composite                      |            | Y/C        |            | Component |          |       |          | Component  |

|                                            |                                |            |            |            | Betacam   |          | MII   |          |            |

|                                            | Setup                          | No Setup   | Setup      | No Setup   | Setup     | No Setup | Setup | No Setup | No Setup   |

| [VS3:VS0]-bit                              | 0000                           | 0000       | 0000       | 0000       | 0000      | 0000     | 0000  | 0000     | 1111       |

| [Setup]-bit                                | 1                              | 0          | 1          | 0          | 1         | 0        | 1     | 0        | 0          |

| [NENT]-bit                                 | don't care                     | don't care | don't care | don't care | 1         | 1        | 0     | 0        | don't care |

| INSEL[3:2]-bit                             | 00                             | 00         | 01         | 01         | 10        | 10       | 10    | 10       | 10         |

Table 7-2-1-2

### 7-2-2. Clamp

The CLAMP function stabilizes the AC-coupled Video input signal level. The AK8850 utilizes both an Analog Clamp circuit and a Digital Clamp circuit.

When the Composite and Y signals (S-video,Component Y signal ) are input, the SYNC-TIP level or PEDESTAL level of Composite signal and LUMINANCE signal ( Y ) are clamped. The digitized input signal data is further signal-processed and clamped to the PEDESTAL level( digital pedestal clamp ).

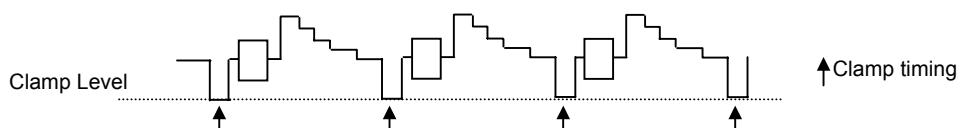

Clamp functions take place during the clamp pulse, as described below, in (1) SYNC SEPARATION FUNCTION.

The Clamp interval is equal to the HSYNC interval (approximately 15 KHz ).

Both the C and Pb/Pr signals are clamped at the SYNC-TIP timing of the Luminance signal.

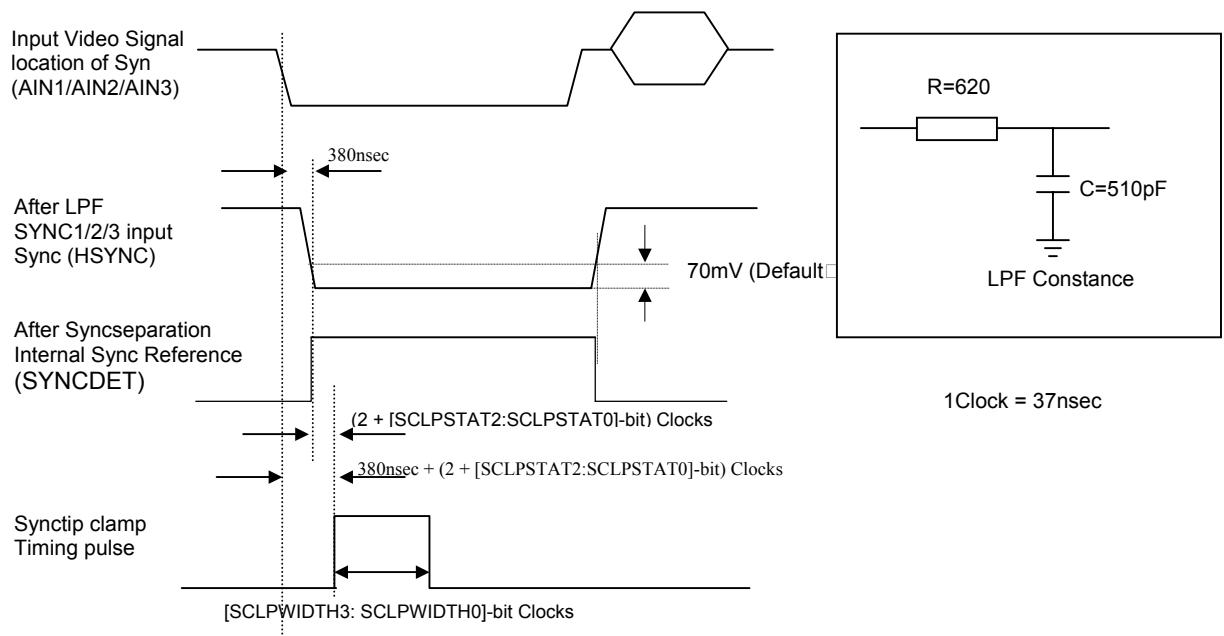

#### (1) SYNC SEPARATION FUNCTION( Clamp timing pulse generation )

In order to separate the SYNC signal of the target signal, the Clamp Timing Pulse is used to clamp the input signal to a pre-determined level which is fed back via the Ain pin. To generate a Clamp timing pulse ,select one of the SYNC1 / SYNC2 / SYNC3 input signals by setting [ SYNCIN1 : SYNCIN0] of the ( INPUT SIGNAL SELECT REGISTER).

The selected signal must be a signal which corresponds to AIN1~ AIN6 signals.

The separated SYNC signal is used for the clamp timing.

Sync-separation is done by slicing approximately 70 mV positive point ( default value ) from the SYNC-TIP level.

As described above, the Clamp timing pulse is generated based on the separated signal ( SYNC DET ).The slice point is adjustable by register settings.

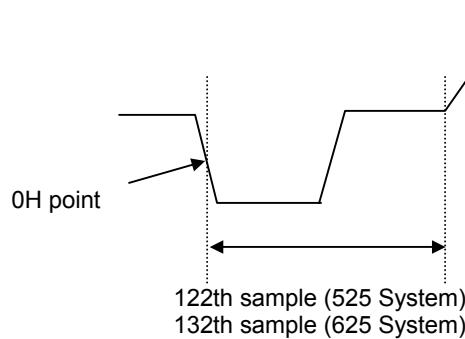

## ( 1-1) SYNC-TIP Clamp Timing Pulse

The Start point and pulse width of the SYNC-TIP timing pulse is set by the [CLAMP TIMING 1 CONTROL REGISTER ].

The Start point of the SYNC-TIP timing pulse is set by [SCLPSTAT 2 : SCLPSTAT 0 ]-bit of the [ CLAMP TIMING 1 CONTROL REGISTER ] as shown below.

The CLAMP period ( pulse width ) is set by [SCLPWIDTH 3 : SCLPWIDTH 0 ]-bit of the [ CLAMP TIMING 1 CONTROL REGISTER ].

Clamp pulse point and pulse width setting is further described in item( 1-6 )SYNC-SEPARATION RELATED REGISTER DESCRIPTION.

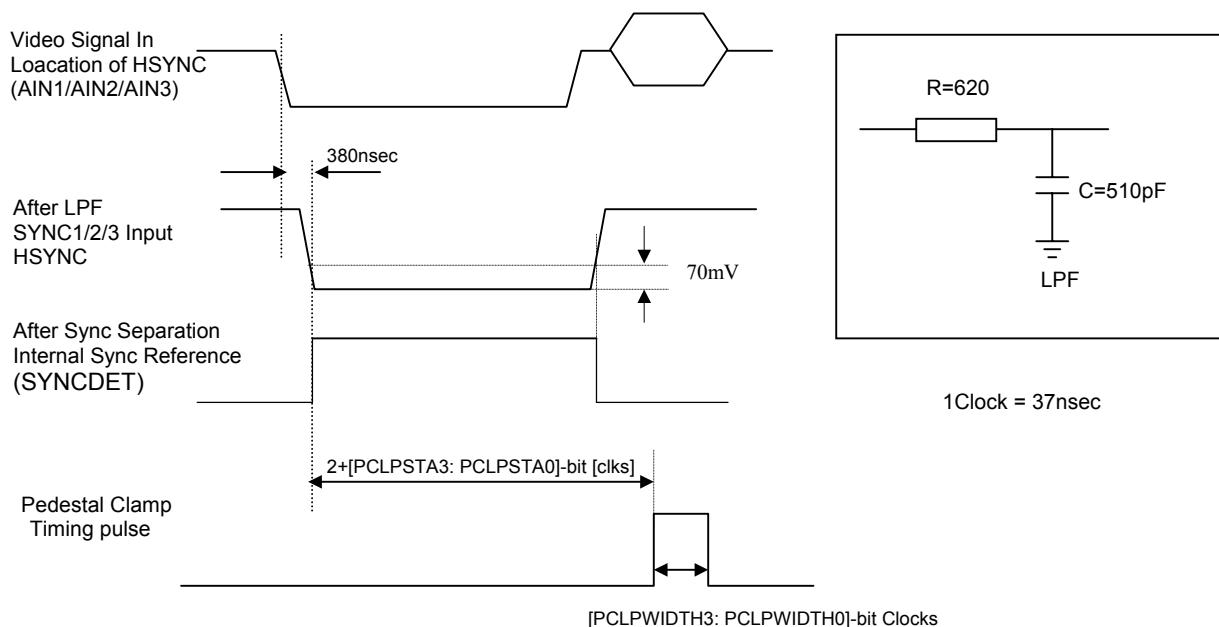

## ( 1-2 ) PEDESTAL CLAMP TIMING PULSE

The AK8850's Clamp point is initially set to the SYNC-TIP level. It is possible to clamp it at the Pedestal point by changing a register value.

The Start point of the Pedestal clamp timing pulse is set by [ PCLPSTAT 2 : PCLPSTAT 0 ]-bit of the [ CLAMP TIMING 2 CONTROL REGISTER] as shown below.

The Clamp period ( pulse width ) is set by [ PCLPWIDTH3 : PCLPWIDTH 0]-bit of the [ CLAMP TIMING 2 CONTROL REGISTER ].

## SYNC-SEPARATION RELATED REGISTER DESCRIPTION.

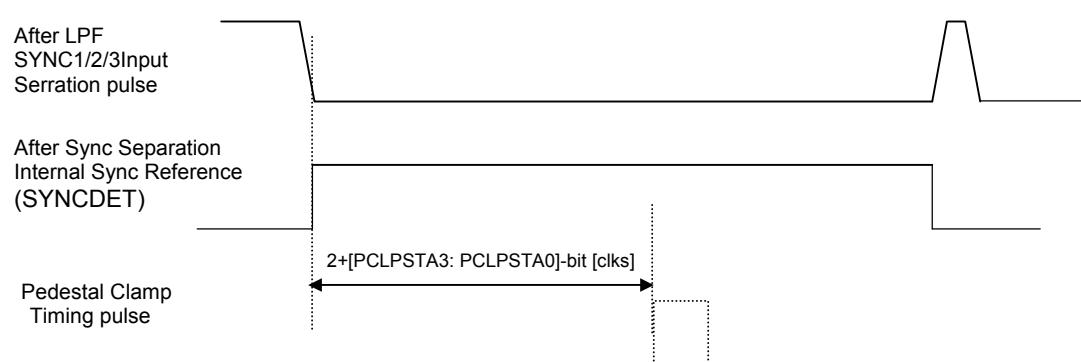

During the SERRATION pulse period, if no SYNCDET falling edge is detected before the start position set by [ PCLPSTA2 : PCLSTA0]-bit, the Pedestal clamp timing pulse is not generated. This avoids mis-clamping of Serration pulse input.

\* Operation with typical video input signal

\* Operation with Serration pulse input signal

at HSYNC Inputat Serration pulse Input

### ( 1-3 ) CLAMP PULSE MASK FUNCTION

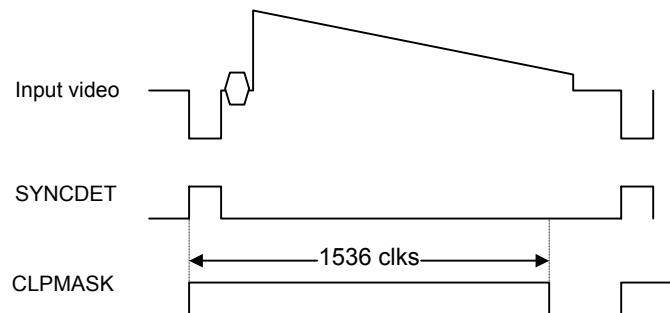

To avoid mis-clamping, the SYNCDET signal is masked outside the SYNC signal period. The masking period is from the rising edge of the SYNCDET signal to 1536 clock periods ( 1 clock = 37 ns ). During this period, no SYNCDET signal is generated ( refer to the timing diagram below ).

This pulse mask is reset via register programming ( refer to item 1-6-5 ).

### ( 1-4 ) EXTERNAL CLAMP TIMING INPUT VIA EXTCLP PIN

It is possible to input an external clamp timing pulse via the EXTCLP pin by setting the INCLPTMG-bit and [ FBCLPTMG1 : FBCLPTMG0 ]-bits of the [ CLAMP CONTROL REGISTER ]. For further register settings, please refer to item ( 1-6 ) SYNC SEPARATION REGISTER RELATED DESCRIPTION.

### ( 1-5 ) CLAMP TIMING PULSE MONITOR FUNCTION

It is possible to monitor the internal clamp timing through the EXTCLP pin only when no external clamp timing is used. Output signals monitored on EXTCLP pin are SYNC-TIP clamp timing pulse, Pedestal clamp timing pulse and SYNCDET signal. The target signal is selected by [ EXTCLP1 : EXTCLP0 ]-bit of the [ CLAMP TIMING 1 CONTROL REGISTER ].

### ( 1-6 ) SYNC-SEPARATION RELATED REGISTER DESCRIPTION

Sync-separation and Clamp pulse related registers are [ INPUT SIGNAL SELECT REGISTER ], [ CLAMP CONTROL REGISTER ], [ CLAMP TIMING 1 CONTROL REGISTER ] and [ CLAMP TIMING 2 CONTROL REGISTER ].

Select Sync-separation signal is done using the [ INPUT SIGNAL SELECT REGISTER ].

[Input Signal Select Register]

| bit 7         | bit 6    | bit 5   | bit 4   | bit 3  | bit 2  | bit 1  | bit 0  |

|---------------|----------|---------|---------|--------|--------|--------|--------|

| Reserved      | Reserved | SYNCIN1 | SYNCIN0 | INSEL3 | INSEL2 | INSEL1 | INSEL0 |

| Default Value |          |         |         |        |        |        |        |

| 0             | 0        | 0       | 1       | 0      | 0      | 0      | 1      |

[ SYNCIN 1 : SYNCIN 0 ]-bit selects one of the SYNC 1 / 2 / 3 input signals to generate the clamp pulse.

| [SYNCIN1:SYNCIN0]<br>(bit5:bit4) | Target video signal for Sync separation |

|----------------------------------|-----------------------------------------|

| 00                               | No Input                                |

| 01                               | Video signal input from SYNC1 pin       |

| 10                               | Video signal input from SYNC2 pin       |

| 11                               | Video signal input from SYNC3 pin       |

## ( 1-6-1 ) CLAMP TIMING PULSE SOURCE SET

Input clamp setting is done via the [ CLAMP CONTROL REGISTER ].

## [Clamp Control Register]

| bit 7         | bit 6    | bit 5  | bit 4    | bit 3     | bit 2     | bit 1   | bit 0   |

|---------------|----------|--------|----------|-----------|-----------|---------|---------|

| UNMASK        | Reserved | ACLAMP | INCLPTMG | FBCLPTMG1 | FBCLPTMG0 | CLPLVL1 | CLPLVL0 |

| Default Value |          |        |          |           |           |         |         |

| 0             | 0        | 0      | 0        | 0         | 0         | 0       | 0       |

[ INCLPTMG]-bit sets the clamp timing pulse of the input clamp.

| INCLPTMG-bit (bit-4) | Clamp timing pulse Generation                                  |

|----------------------|----------------------------------------------------------------|

| 0                    | Clamp timing pulse generated by Internal Clamp pulse generator |

| 1                    | Clamp timing pulse from EXTCLP pin                             |

[ FBCLPTMG1 : FBCLPTMG0]-bit sets the clamp position and the clamp source.

| [FBCLPTMG1:FBCLPTMG0]-bit<br>(bit-3:bit-2) | Clamp timing pulse                                                                  |  |  |

|--------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| 00                                         | Video signal is clamped at synctip level with internal Clamp timing pulse (Default) |  |  |

| 01                                         | Video signal is clamped at synctip level with External Clamp timing pulse           |  |  |

| 10                                         | Video signal is clamped at pedestal level with internal Clamp timing pulse          |  |  |

| 11                                         | Reserved                                                                            |  |  |

Combinations of INCLPTMG-bit, the [FBCLPTMG1 : FBCLPTMG0 ]-bit and input / output setting of the EXTCLP pin in various modes are shown in the following table. Some combinations are "Prohibited" as shown in the table, and therefore should not be selected ( otherwise internal timing has priority ).

Internal clamp timing monitoring is described below..

|              |                           | [FBCLPTMG1:FBCLPTMG0]-bit        |                                 |                                  |                                  |          |

|--------------|---------------------------|----------------------------------|---------------------------------|----------------------------------|----------------------------------|----------|

|              |                           | Synctip Clamp<br>FBCLPTMG1=0     |                                 | Pedestal Clamp<br>FBCLPTMG1 =1   |                                  |          |

|              |                           | Internal Timing<br>FBCLPTMG0=0   | External Timing<br>FBCLPTMG0=1  | Internal Timing<br>FBCLPTMG0=0   | External Timing<br>FBCLPTMG0=1   |          |

| INCLPTMG-bit | 0<br>(Internal Timing)    | EXTCLP = OUTPUT<br>Synctip Clamp | Prohibit                        | EXTCLP = OUTPUT<br>Pedestal      | EXTCLP = INPUT<br>Pedestal clamp |          |

|              | 1<br>(External<br>Timing) | Prohibit                         | EXTCLP = INPUT<br>Synctip Clamp | EXTCLP = INPUT<br>Pedestal Clamp |                                  | Prohibit |

## ( 1-6-2 ) INTERNAL CLAMP TIMING MONITORING FUNCTION VIA EXTCLP PIN

It is possible to monitor the clamp timing pulse on EXTCLP pin. This is enabled by the [ EXTMON1 : EXTMON0 ]-bit of the [ CLAMP TIMING1 CONTROL REGISTER ].

The timing pulse monitor function is disabled when the external clamp pulse input is selected.

## \* [ CLAMP TIMING 1 CONTROL REGISTER ]

| bit 7         | bit 6   | bit 5      | bit 4      | bit 3      | bit 2     | bit 1     | bit 0     |

|---------------|---------|------------|------------|------------|-----------|-----------|-----------|

| EXTMON1       | EXTMON0 | SCLPWIDTH2 | SCLPWIDTH1 | SCLPWIDTH0 | SCLPSTAT2 | SCLPSTAT1 | SCLPSTAT0 |

| Default Value |         |            |            |            |           |           |           |

| 0             | 0       | 0          | □          | □          | 0         | 0         | □         |

Monitoring of clamp timing is possible by setting [ INCLPTMG : FBCLPTMG 1 : FBCLPTMG 0 ]-bit.

| [INCLPTMG: FBCLPTMG1:FBCLPTMG0]-bit | Monitor with EXTCLP pin | Note           |

|-------------------------------------|-------------------------|----------------|

| [000]                               | possible                | Synctip Clamp  |

| [010]                               | possible                | Pedestal Clamp |

Monitor pulse is selected as follows.

| [EXTMON1:EXTMON0]-bit | Monitor source                           | Note    |

|-----------------------|------------------------------------------|---------|

| 00                    | High Impedance ( Unavailable monitoring) | Default |

| 01                    | Internal Synctip clamp timing pulse      |         |

| 10                    | Internal pedestal clamp timing pulse     |         |

| 11                    | SYNCDET pulse                            |         |

#### ( 1-6-3 ) SYNC-TIP CLAMP TIMING PULSE SET

When using the internal SYNC-TIP clamp timing pulse for clamp functions, set the start position and pulse width of the SYNC-TIP clamp timing pulse using the [ CLAMP TIMING1 CONTROL REGISTER ]. This setting is valid only when the [ INCLPTMG : FBCLPTMG1 : FBCLPTMG0 ]-bits are set to use the internal clamp pulse for SYNC-TIP clamping ( it is invalid if external clamp pulse is used ).

To monitor the clamp pulse timing generated by the internal clamp circuit, ensure that [ EXTMON1 : EXTMON0 ]-bit of the [ CLAMP TIMING1 CONTROL REGISTER ] is properly set.

The slice level is adjustable by setting [ SLCLV 1 : SLCLV 0 ]-bit of the [ CLAMP TIMING 2 CONTROL REGISTER ].

##### \* [ CLAMP TIMING1 CONTROL REGISTER ]

| bit 7         | bit 6   | bit 5      | bit 4      | bit 3      | bit 2     | bit 1     | bit 0     |

|---------------|---------|------------|------------|------------|-----------|-----------|-----------|

| EXTMON1       | EXTMON0 | SCLPWIDTH2 | SCLPWIDTH1 | SCLPWIDTH0 | SCLPSTAT2 | SCLPSTAT1 | SCLPSTAT0 |

| Default Value |         |            |            |            |           |           |           |

| 0             | 0       | 0          | □          | 0          | 0         | 0         | □         |

Start position of the Analog SYNC-TIP clamp timing pulse is set by [ SCLPSTA2 : SCLPSTAT0]-bit ,and the clamp pulse width is adjusted using the [ SCLPWIDTH3 : SCLPWIDTH0 ]-bit.

\* When [ SCLPSTA2 : SCLPSTAT0 ]-bit and [ SCLPWIDTH3 : SCLPWIDTH0 ]-bit are valid, settings are as follows.

| [INCLPTMG: FBCLPTMG1:FBCLPTMG0]-bit | monitor with EXTCLP | Note                                 |

|-------------------------------------|---------------------|--------------------------------------|

| [000]                               | Available           | Internal Synctip clamp pulse         |

| [010]                               | Available           | internal Pedestal clamp timing Pulse |

| [011]                               | Unavailable         | External Pedestal clamp timing pulse |

SYNC-TIP clamp pulse related settings are shown below.

\* SYNC-TIP clamp pulse start position set by [ SCLPSTAT2 : SCLPSTAT0 ]-bit

| [SCLPSTAT2:SCLPSTAT0]-bit | Start position from the falling edge of Synchronization pulse | Actual Clamp pulse timing position |

|---------------------------|---------------------------------------------------------------|------------------------------------|

| 000                       | Passed after 0-Clocks (0nsec)                                 | Passed after 2-Clocks (74nsec)     |

| 001                       | Passed after 2-Clocks (74nsec)                                | Passed after 4-Clocks (148nsec)    |

| 010                       | Passed after 4-Clocks (148nsec)                               | Passed after 6-Clocks (222nsec)    |

| 011                       | Passed after 6-Clocks (222nsec)                               | Passed after 8-Clocks (296nsec)    |

| 100                       | Passed after 8-Clocks (296nsec)                               | Passed after 10-Clocks (370nsec)   |

| 101                       | Passed after 10-Clocks (370nsec)                              | Passed after 12-Clocks (444nsec)   |

| 110                       | Passed after 12-Clocks (444nsec)                              | Passed after 14-Clocks (481nsec)   |

| 111                       | Passed after 14-Clocks (518nsec)                              | Passed after 16-Clocks (592nsec)   |

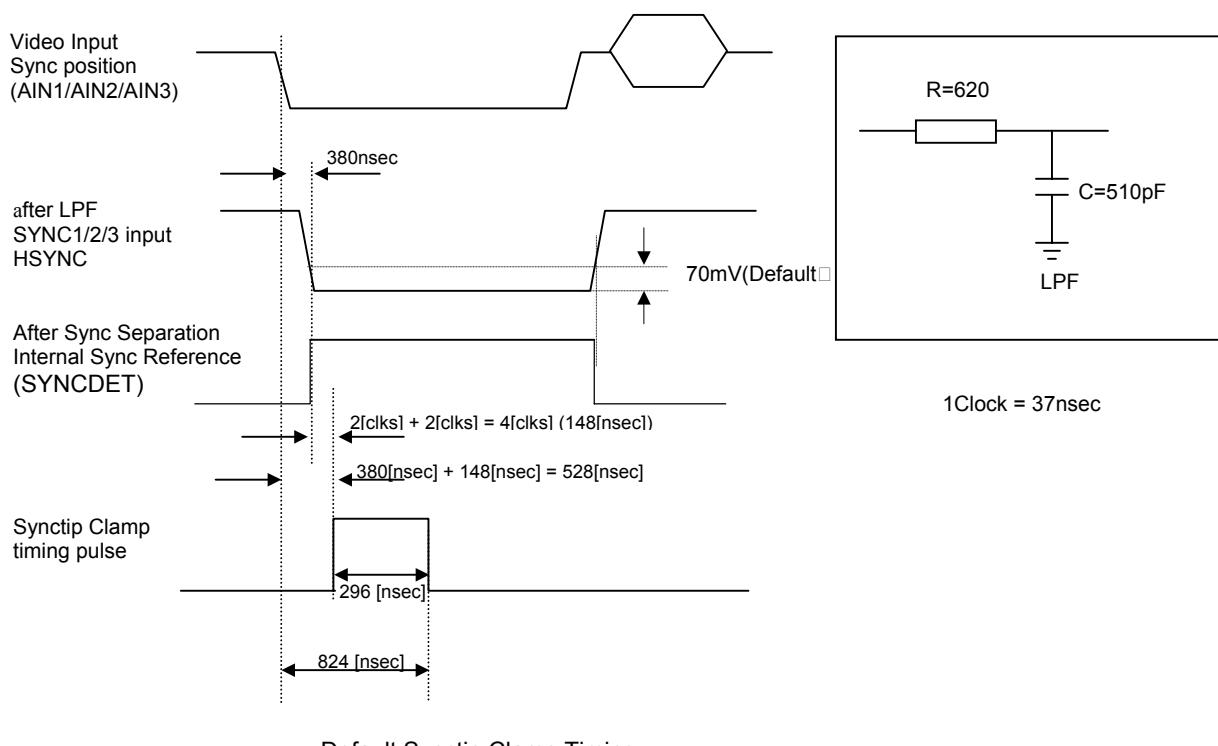

[ SCLPSTAT2 : SCLPSTAT0 ]-bit is used to fine-tune the start position whose default value is [001], or 2 clocks (74ns). The clamp start position is adjusted with the [ SCLPSTAT2 : SCLPSTAT0 ]-bit as follows. The actual clamping position occurs 2 clock cycles after sync pulse is generated..

\* SYNC-TIP clamp pulse width set by [ SCLPWIDTH2 : SCLPWIDTH0 ]-bit

| [SCLPWIDTH2: SCLPWIDTH0]-bit | Pulse width                  |

|------------------------------|------------------------------|

| 000                          | 2-Clocks (74nsec)            |

| 001                          | 4-Clocks (148nsec)           |

| 010                          | 8-Clocks (296nsec) (Default) |

| 011                          | 16-Clocks (592usec)          |

| 100                          | 24-Clocks (888nsec)          |

| 101                          | 32-Clocks (1.18usec)         |

| 110                          | 40-Clocks (1.48usec)         |

| 111                          | 48-Clocks (1.78usec)         |

SYNC-TIP clamp pulse width is set using the [ SCLPWIDTH2 : SCLPWIDTH0 ]-bit = [010], with ( 8 clocks = 296 ns) as the default value. Clamp pulse width can be adjusted using the [ PCLPWIDTH3 : PCLDWIDTH0 ]-bit as shown below.

\* [ CLAMP TIMING2 CONTROL REGISTER ]

| bit 7         | bit 6  | bit 5      | bit 4      | bit 3      | bit 2      | bit 1     | bit 0     |

|---------------|--------|------------|------------|------------|------------|-----------|-----------|

| SLCLV1        | SLCLV0 | PCLPWIDTH2 | PCLPWIDTH1 | PCLPWIDTH0 | PSCLPSTAT2 | PCLPSTAT1 | PCLPSTAT0 |

| Default Value |        |            |            |            |            |           |           |

| 0             | 0      | 0          | 1          | 1          | 1          | 0         | 0         |

Please use SLCLV1 : SLCLV0 to adjust the SYNC-TIP slice position.

| [SLCLV1: SLCLV0]-bit | Slice Level                                           |

|----------------------|-------------------------------------------------------|

| 00                   | Sliced at the position from about 70mV over synctip.  |

| 01                   | Sliced at the position from about 140mV over synctip. |

| 10                   | Invalid setting                                       |

| 11                   | Sliced at the position from about 105mV over synctip. |

The default SYNC-TIP clamp timing pulse generates a clamp pulse as shown in the following timing diagram.

## ( 1-6-4 ) SETTING OF PEDESTAL CLAMP TIMING PULSE

Both the start position and pulse width of the Pedestal clamp timing pulse are programmable. It is done using the [ CLAMP TIMING 2 CONTROL REGISTER ].

This is valid only when [ INCLPTMG : FBCLPTMG1 : FBCLPTMG0 ]-bit is set, causing the internal clamp pulse to be used for Pedestal clamping ( it is invalid if an external clamp pulse is used ).

To monitor the clamp timing pulse generated by an internal clamp timing circuit, proper setting of the [ EXTMON1 : EXTMON0 ]-bits of the [ CLAMP TIMING1 CONTROL REGISTER ] is required.

## \* [ CLAMP TIMING2 CONTROL REGISTER ]

| bit 7         | bit 6  | bit 5      | bit 4      | bit 3      | bit 2      | bit 1     | bit 0     |

|---------------|--------|------------|------------|------------|------------|-----------|-----------|

| SLCLV1        | SLCLV0 | PCLPWIDTH2 | PCLPWIDTH1 | PCLPWIDTH0 | PSCLPSTAT2 | PCLPSTAT1 | PCLPSTAT0 |

| Default Value |        |            |            |            |            |           |           |

| 0             | 0      | 0          | 1          | 1          | 1          | 0         | 0         |

The Start position of the Pedestal clamp timing pulse is set by [ PCLPSTA2 : PCLPSTAT0 ]-bit, and the clamp pulse width is adjusted by [ PCLPWIDTH3 : PCLPWIDTH0 ]-bit.

\* When [ PCLPSTA2 : PCLPSTAT0 ]-bit and [ PCLPWIDTH3 : PCLPWIDTH0 ]-bit are valid, the setting is as follows.

| [INCLPTMG: FBCLPTMG1:FBCLPTMG0]-bit | Monitoring with EXTCLP |                                      |

|-------------------------------------|------------------------|--------------------------------------|

| [010]                               | Available              | Internal pedestal clamp timing pulse |

| [110]                               | Unavailable            | External Pedestal clamp timing pulse |

Set the start position and the pulse width of the Pedestal clamp timing pulse.

\* Pedestal clamp timing pulse start position set by [ PCLPSTAT2 : PCLPSTAT0 ]-bit

| [PCLPSTAT2:PCLPSTAT0]-bit<br>(bit-2:bit-0) | Start position from the falling edge of<br>Synchronization pulse | Color subcarrier Cycles from the falling edge of<br>HSYNC         |

|--------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|

| 000                                        | Passed after 118-Clocks (4.37usec)                               | 17Cycles                                                          |

| 001                                        | Passed after 126-Clocks (4.65usec)                               | 18Cycles                                                          |

| 010                                        | Passed after 132-Clocks (4.88usec)                               | (Color burst start position of the standard NTSC<br>video signal) |

| 011                                        | Passed after 140-Clocks (5.18usec)                               | 20Cycles                                                          |

| 100                                        | Passed after 148-Clocks (5.49usec)                               | 21Cycles (Default)                                                |

| 101                                        | Passed after 156-Clocks (5.77usec)                               | 22Cycles                                                          |

| 110                                        | Passed after 164 Clocks (6.07usec)                               | 23Cycles                                                          |

| 111                                        | Passed after 172 Clocks (6.36usec)                               | 24Cycles                                                          |

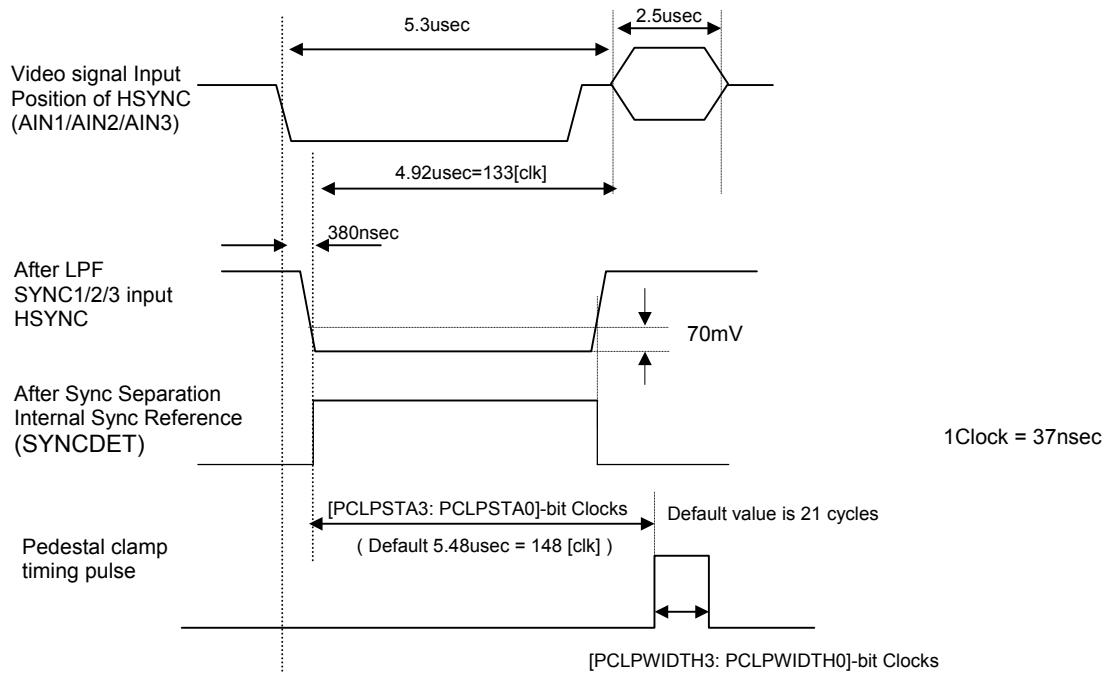

[ PCLPSTAT2 : PCLPSTAT0 ]-bit is used to fine-tune the start position which is set to be 2 clocks later [100] as default value.

Clamp pulse start position changes as follows by [ PCLPSTAT2 : PCLPSTAT0 ]-bit.

\* Pedestal Clamp pulse width set by [ PCLPWIDTH2 : PCLPWIDTH0]-bit

| [PCLPWIDTH2: PCLPWIDTH0]-bit<br>(bit-6:bit-4) | Pulse width          |

|-----------------------------------------------|----------------------|

| 000                                           | 16-Clocks (592nsec)  |

| 001                                           | 24-Clocks (888nsec)  |

| 010                                           | 28-Clocks (1.04usec) |

| 011                                           | 32-Clocks (1.18usec) |

| 100                                           | 40-Clocks (1.48usec) |

| 101                                           | 44-Clocks (1.63usec) |

| 110                                           | 48-Clocks (1.78usec) |

| 111                                           | 52-Clocks (1.92usec) |

Pedestal clamp pulse width is set to its default value of [011] via the [ PCLPWIDTH2 : PCLPWIDTH0 ]-bits =( 32 clocks = 1.18 micro sec ).

The clamp pulse width is adjusted using the [ PCLPWIDTH3 : PCLPWIDTH0 ]-bit as follows.

The Pedestal clamp timing pulse at the default state generates a clamp pulse as shown in the following timing diagram.

Default Pedestal clamp timing

#### ( 1-6-5 ) CLAMP TIMING PULSE MASK FUNCTION

The Clamp timing pulse generation is masked at the default state to avoid mis-clamping outside the SYNC signal timing. This masking function can be disabled.

\* [ CLAMP CONTROL REGISTER ] set is done by UNMASK-bit

| UNMASK-bit | Function  |         |

|------------|-----------|---------|

| 0          | Masked    | default |

| 1          | Un-Masked |         |

For typical use,please set UNMASK bit =0.

## ( 2 ) INPUT SIGNAL CLAMP FUNCTION

This function clamps the input signal to a proper level. The circuit clamps the SYNC-TIP level of input signal to approximately 0.7 V. The input signal is clamped at the position as shown below.

The clamp timing pulse is controlled by either the internal Sync-separation circuit or by an externally-fed clamp timing pulse via EXTCLP pin ( please refer to SYNC-TIP clamp timing pulse item ).

### ( 2-1 ) INPUT CLAMP CONTROL REGISTER:

\* INPUT SIGNAL CLAMP ON /OFF BIT : ACLAMP-bit ( bit-3 )

| ACLAMP | Function           |

|--------|--------------------|

| 0      | Clamp ON (default) |

| 1      | Clamp OFF          |

The Input signal clamp function can be turned –off, for example, when DC signals are input..

Set ACLAMP=0 ( ON ) for normal operation.

## ( 3 ) ANALOG CLAMP FUNCTION

This function clamps the input signal using analog signal processing for a higher degree of precision, enabling SYNC-TIP to be clamped to approximately 0.7 V by the input signal clamping.

Either of the SYNC-TIP clamp or the Pedestal clamp is selectable by the [ CLAMP CONTROL REGISTER ]. Clamp timing is controlled by a clamp pulse that is generated by an internal Sync-separation circuit. It is also possible to control it with an external signal connected to the EXTCLP pin. Either the SYNC-TIP clamp or the Pedestal clamp must be selected and its clamp level set by [ CLPLVL 1 : CLPLVL 0 ]-bit.

If an internal clamp pulse is used, the selected clamp pulse can be output on the EXTCLP pin. When the C signal and Pb / Pr component signals are input, the clamp levels of CLAMP2 / CLAMP3 are set to fixed values.

### ( 3-1 ) CLAMP CONTROL REGISTER DESCRIPTION

Clamp function is set by [ CLAMP CONTROL REGISTER ].

\* [ CLAMP CONTROL REGISTER ]

| bit 7         | bit 6    | bit 5  | bit 4    | bit 3     | bit 2     | bit 1   | bit 0   |

|---------------|----------|--------|----------|-----------|-----------|---------|---------|

| CLPMASK       | Reserved | ACLAMP | INCLPTMG | FBCLPTMG1 | FBCLPTMG0 | CLPLVL1 | CLPLVL0 |

| Default Value |          |        |          |           |           |         |         |

| 0             | 0        | 0      | 0        | 0         | 0         | 0       | 0       |

| [CLPLVL1: CLPLVL0]-bit<br>(bit1:bit0) | Clamp level | Note                                                                                                                                                                  |

|---------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [00]                                  | Synctip     | Clamped at synctip level.<br>□When internal clamp pulse is used, set to this mode□                                                                                    |

| [01]                                  | Pedestal    | Clamped at Pedestal Level<br>For 286mV Sync levels and Analog Pedestal Clamp settings, use this mode.<br>286mV Sync : NTSC Composite , Y/C signal , Betacam Component |

| [10]                                  | Pedestal    | Clamped at Pedestal Level<br>For 300mV Sync level and Analog Pedestal Clamp settings, use this mode.<br>300mV Sync : 625 Component, MIIComponent                      |

| [11]                                  | Clamp OFF   | Analog clamp function is off                                                                                                                                          |

The control clamp timing is done by setting the clamp pulse timing [ CLPTMG 1 : CLPTMG 0 ]-bit.

\* Clamp timing is set by [ FBCLPTMG 1 : FBCLPTMG 0 ]-bit ( bit-3 : bit-2 ).

| [FBCLPTMG1:FBCLPTMG0]-bit | Clamp Pulse                                        |

|---------------------------|----------------------------------------------------|

| 00                        | Internal Sync tip Clamp pulse                      |

| 01                        | Internal Pedestal Clamp pulse                      |

| 10                        | External clamp timing pulse input from EXTCLP pin. |

| 11                        | Reserved                                           |

\* Clamp timing and clamp level are summarized in the following table.

| Bit Set                   | Internal Clamp timing pulse |                |                   |                | External Clamp timing pulse |                |                   |                |

|---------------------------|-----------------------------|----------------|-------------------|----------------|-----------------------------|----------------|-------------------|----------------|

|                           | 286mV Sync signal           |                | 300mV Sync signal |                | 286mV Sync signal           |                | 300mV Sync signal |                |

|                           | Sync tip Clamp              | Pedestal Clamp | Sync tip Clamp    | Pedestal Clamp | Sync tip Clamp              | Pedestal Clamp | Sync tip Clamp    | Pedestal Clamp |

| [FBCLPTMG1:FBCLPTMG0]-bit | 00                          | 01             | 00                | 01             | 10                          | 10             | 10                | 10             |

| [CLPLVL1:CLPLVL0]-bit     | 00                          | 01             | 00                | 10             | 00                          | 01             | 00                | 10             |

#### ( 4 ) DIGITAL PEDESTAL CLAMP FUNCTION

This function clamps at the Pedestal position the Analog-clamped input signal by using digital signal processing. For details, please refer to digital portion details.

## 7-2-3 PGA ( PROGRAMMABLE GAIN AMP )

A Programmable Gain Amp ( PGA ) to adjust input signals to their proper levels.

The gain range of the PGA is from 0 dB to 12 dB with the gain step of 0.1 dB / step ( 127 steps ). When the AGC function is enabled, PGA1 / PGA 2 / PGA 3 are properly gain set by digital control. AGC function is disabled by default and the gain of each PGA is independently set via registers.

PGA Control Register description:

To manually control the PGA, the AGC function is turned off by the [ CONTROL 1 REGISTER ]. The AGC function is disabled by default.

## \* [ CONTROL 1 REGISTER ]

| bit 7         | bit 6    | bit 5     | bit 4     | bit 3 | bit 2 | bit 1 | bit 0 |

|---------------|----------|-----------|-----------|-------|-------|-------|-------|

| FRCSYNC       | Reserved | INTPOL[1] | INTPOL[0] | AGCC1 | AGCC0 | AGCT1 | AGCT0 |

| Default Value |          |           |           |       |       |       |       |

| 1             | 0        | 0         | 0         | 0     | 0     | 0     | 0     |

to the AGC must be disabled in order to set PGA manually. The setting is done as follows : i.e., set [ AGCT 1 : AGCT 0 ] = [ 0,0 ].

| [AGCT1:AGCT0](bit-1:bit-0) | AGC Function      |

|----------------------------|-------------------|

| [0,0]                      | Disable (Default) |

| [0,1]                      | T=1Field          |

| [1,0]                      | T=7Field          |

| [1,1]                      | T=29Field         |

For further details of AGC function, please refer to the AGC description section.

## \* [ PGA 1 / 2 / 3 GAIN CONTROL REGISTER ]

| bit 7         | bit 6       | bit 5       | bit 4       | bit 3       | bit 2       | bit 1       | bit 0       |

|---------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Reserved      | PGA1/2/3[6] | PGA1/2/3[5] | PGA1/2/3[4] | PGA1/2/3[3] | PGA1/2/3[2] | PGA1/2/3[1] | PGA1/2/3[0] |

| Default Value |             |             |             |             |             |             |             |

| 0             | 1           | 0           | 0           | 0           | 0           | 0           | 0           |

Registers for setting the PGA gain values are [ PGA 1 / 2 / 3 GAIN CONTROL REGISTER ]. Each PGA has a corresponding register. [ PGA 1 GAIN CONTROL REGISTER ] example is shown here.

| bit 7         | bit 6   | bit 5   | bit 4   | bit 3   | bit 2   | bit 1   | bit 0   |

|---------------|---------|---------|---------|---------|---------|---------|---------|

| Reserved      | PGA1[6] | PGA1[5] | PGA1[4] | PGA1[3] | PGA1[2] | PGA1[1] | PGA1[0] |

| Default Value |         |         |         |         |         |         |         |

| 0             | 1       | 0       | 0       | 0       | 0       | 0       | 0       |

Each value set by PGA 1 / 2 / 3 [ 6 : 0 ]-bit uses 0.1 dB / step increments. The default gain is set to approximately 6 dB ( PGA 1 / 2 / 3 [ 6 : 0 ] = 0x40 ).

### 7-2-4 CLOCK MODES

The AK8850 operates under the following 3 clock modes.

#### (1) LINE-LOCKED CLOCK MODE

A high quality input signal from a Signal generator or DVD can be used and the corresponding Horizontal Sync Signal ( HSYNC ) can be extracted. A clock generated in this way is called Line-Locked Clock. Even if the Line-Locked Clock mode is selected, it is possible for the chip to be forced into Fixed-Clock mode, depending upon the input signal quality (poor or no-input signal conditions).

#### (2) FRAME-LOCKED CLOCK MODE

The Vertical Sync Signal in the input signal is used to generate a clock when skew exists in the input signal, as in the case of a VCR. A clock generated in this way is called Frame-Locked Clock. Even if the Frame-Locked Clock mode is selected, there is a case to be forced to the Fixed-Clock mode which is depending on the input signal quality ( poor or no- input signal conditions ).

#### (3) FIXED-CLOCK MODE

A clock not affected by PLL control.

#### (4) CLOCK AUTO TRANSITION MODE ( default mode )

Depending on the characteristics of the input signal, the clock mode is automatically selected. When the auto select mode is enabled, the AK8850 automatically shifts its clock mode from / to Line-Clocked mode to / from Frame-Locked mode then to Fixed-Clock mode until it selects the optimum mode.

Since an input- signal-synchronized clock can be generated in both the Line-Locked Clock and Frame-Locked Clock modes, ITU-R BT.656 compatible output is available if the input signal quality is good enough.

In Fixed Clock mode operation, the AK8850's PLL is disabled. This clock mode is usually selected when the input signal quality is poor and the Auto Clock mode is set by Clock Mode Register. In this mode, the input clock must be synchronized with the input signal so that output data remains compatible with ITU-R BT.656 specifications.

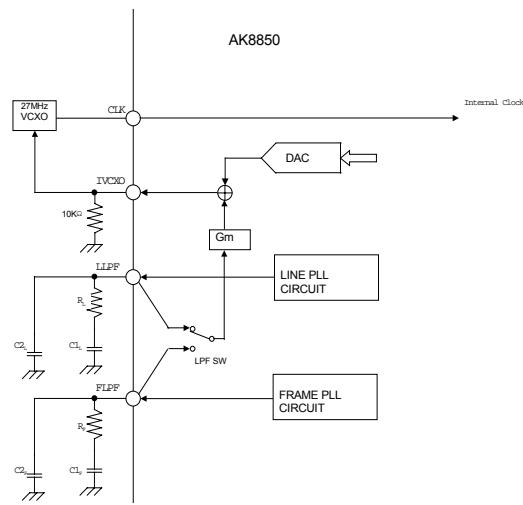

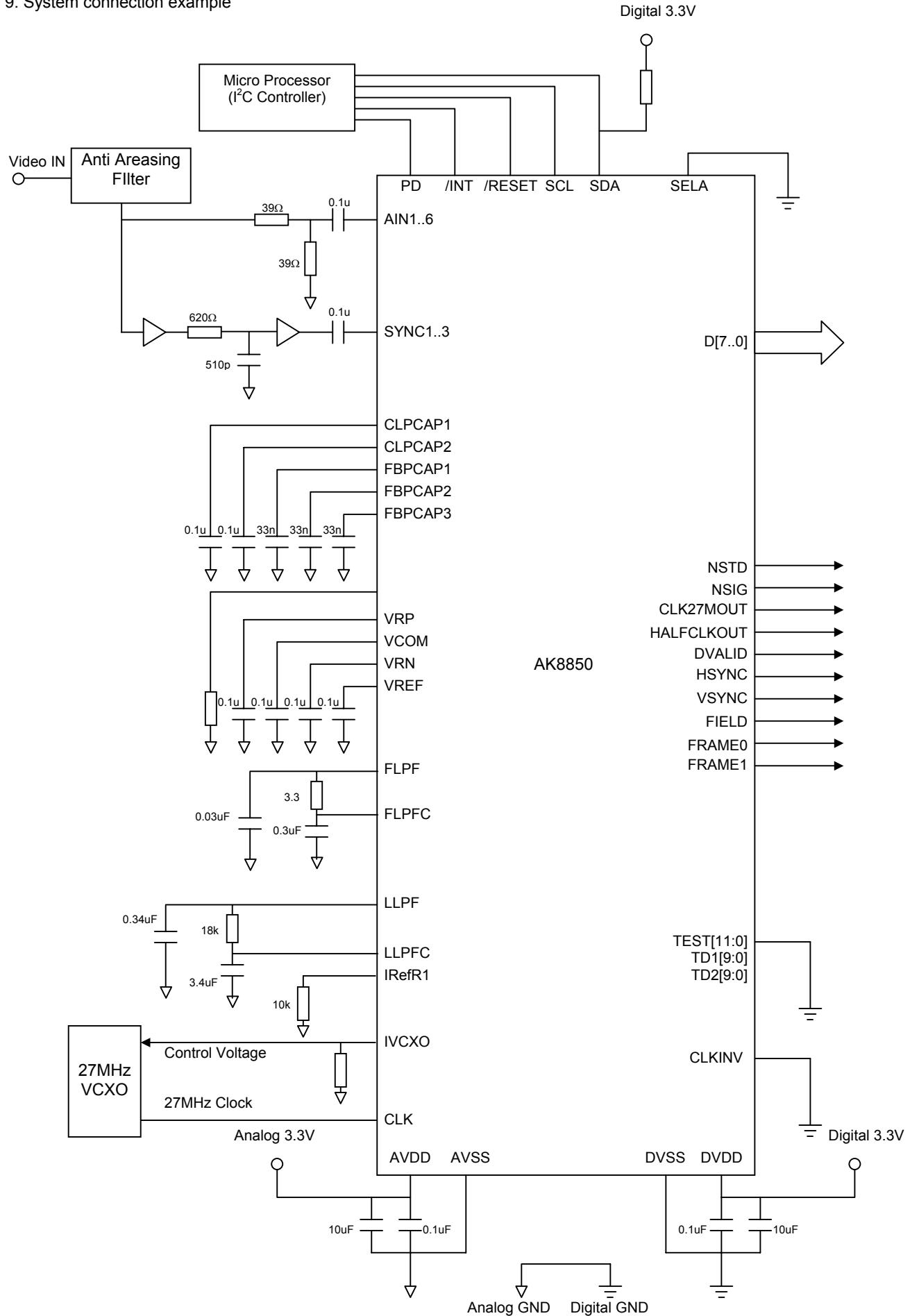

An external VCXO clock circuit connection is shown below.

The AK8850 internally switches the Line and the Frame-Locked Loop Filter outputs, and adds the V-I converted current and the internal current DAC output together, then it outputs this value on the IVCXO pin. By connecting an external resistor to this pin, a control voltage to the external VCXO is provided. A voltage to control the oscillating center frequency of the VCXO is adjustable by setting the above-mentioned current DAC input code, using the PLL-DAC Code Set Register ( address : 0x47 ). In this case, adjusting the external VCXO oscillating center frequency is accomplished by selecting the Fixed Clock mode [ CONTROL 2 REGISTER ].

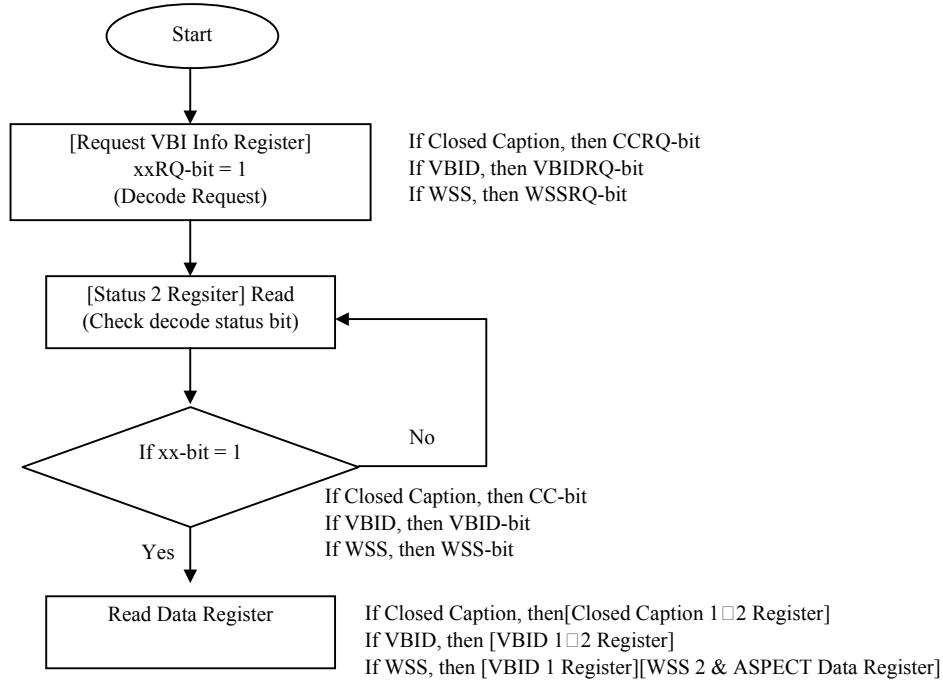

Clock Control Register Description :