## Single-Chip USB-to-USB Networking Solution

### **FEATURES**

- Smallest completely integrated solution in the market

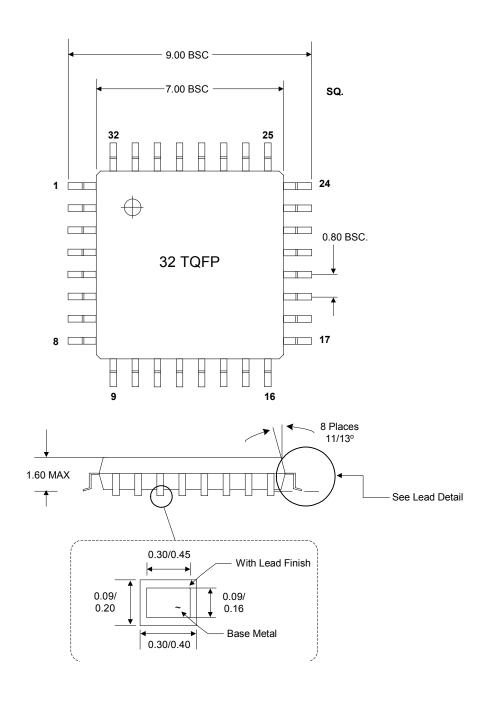

- 32 pin TQFP

- Only requires a single crystal and small 16 byte serial EEPROM for full implementation

- Meets difficult suspend current of 500 uA for both hosts

- 2K data buffer for maximum speed transfer

- Greater than 5 Mbps data transfer rate

- Low power Less than 100 mW power

#### **OVERVIEW**

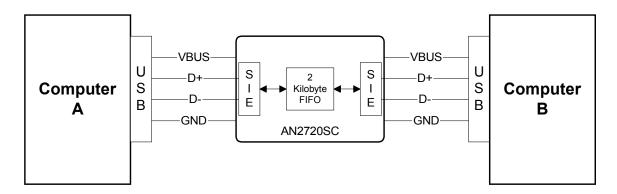

The Cypress AN2720SC provides a single-chip solution for networking two or more computers via their USB ports. In a USB system, the PC acts as a host, which initiates all USB traffic. USB devices act as slaves, which respond to host requests. It is inherently incompatible to connect two PCs together via a simple USB cable, since a master (host) cannot talk to another master (host). A master can talk only to one or more slave devices.

The AN2720SC overcomes this "peer-to-peer" incompatibility by providing two USB devices, one for each PC. Two independent Serial Interface Engines (SIE) exchange data through a 2 kilobyte FIFO. Thus, USB data transmitted by one computer is made available to the other computer through the AN2720SC. The connection is full duplex—data can be transferred in both directions simultaneously.

### **APPLICATIONS AND MARKETS**

The use of the AN2720SC and special network driver software provided by Cypress allows very simple and efficient networking between PCs. The "plug-and-play" nature of USB makes connecting two computers (even when powered) very simple. With the AN2720SC, simple networking can be provided in numerous form factors including:

- USB standalone hubs

- Computer monitors with USB hubs

- Standalone USB cables

- Port Replicators

- WinCE Machines

- Set-Top Boxes

- Docking Stations

- PC motherboards (particularly for laptops)

Depending on the driver set used, the AN2720SC can perform the following functions:

- USB networking

- File transfer (including MAC to PC file sharing)

- Windows CE synchronization

- Printer sharing

- Share internet connections (requires proxy or bridging software)

- Multi-player gaming

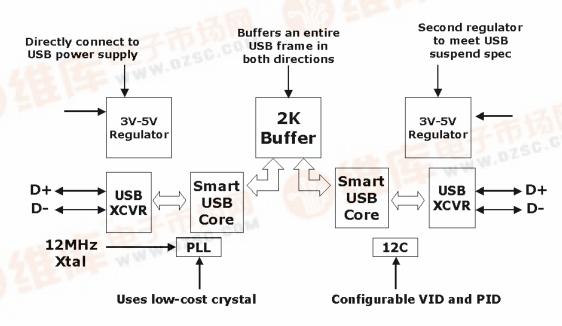

#### SYSTEM DIAGRAM

### CHIP DETAILS

The AN2720 contains two slave interfaces that transfer data between through a 2-kilobyte FIFO. It also contains two 5V to 3.3V regulators to supply power to the chip and to the USB pullup resistor. Figure 2 of this document shows a functional block diagram of the AN2720. The AN2720 contains:

- Two 5V to 3.3V regulators, which deliver clean, regulated power to the chip and to the pullup resistor connected to the USB D+ line. These regulators are powered by the USB 5V line.

- Two USB transceivers, one for each computer.

- Two USB cores, each consisting of a Serial Interface Engine (SIE) and an intelligent machine that can respond to standard USB requests. These are the same enhanced SIE's used in Cypress' line of EZ-USB products.

- A 2-Kilobyte FIFO which is used to buffer multiple packets between computers to optimize data throughput.

- Control logic to manage transfer of USB data between the two SIEs.

- A single-crystal oscillator and PLL, shared by both SIE's.

### SOFTWARE SUPPORT

Software is provided in two different configurations: Ethernet drivers or Ethernet plus bridging software.

The Ethernet drivers run on Windows 95/98/2000 and are miniport device driver software which emulates a network interface connector. It manages the USB protocol and the PC-to-PC data flow. The EZ-Link Ethernet device driver is written to the NDIS (Network Driver Interface Specification) standard and provides a standard Windows interface to the resources of the hardware. To the end user, EZ-Link appears and behaves like an Ethernet card even though no physical network interface card is present. Thus, users can use standard Windows interface such as Windows Explorer, Network Neighborhood and standard file sharing security features. With this driver, users can use multiple EZ-Links to generate their own private mobile network, with access to other peripheral devices such as printers appearing as network peripherals.

The Ethernet plus bridging drivers run on Windows 95/98/2000. In addition to the Ethernet connection capability between multiple EZ-Links, users can connect to corporate LANs using the PC that has both EZ-Link and a corporate Ethernet connection as a bridge device. With this capability, users have complete access to corporate LAN resources.

## **ADDITIONAL SOFTWARE UTILITIES**

Unlike other Host-to-Host devices in the market, Cypress provides an entire suite of software utilities which enhance the end user experiences. Such utilities include:

- Specialized Install procedure. The custom install procedure pioneered by Cypress allows immediate network operation without the need for the end user to access the Network Icon in the Control Panel. This makes it easy for "Instant Operation" without the need for the user to understand any networking jargon. Numerous article reviews rave over this feature.

- Make Disk Utility. In case an end user does not have the install CD-ROM in possession, the

end user can still install the necessary drivers to a floppy disk using this Make Disk Utility.

This allows the end user to continue to network to other computers without the need of the

install CD-ROM.

- Electronic On-line Users Manual. This slick HTML electronic manual includes everything with regards to Networking operation in an easy-to-read format. Such Information includes Getting Started information, installation, various configurations, advanced operations and a background in Networking.

- EZ-Link Network Manager. While the user can use Windows Explorer and Network Neighborhood to navigate for data transfer and accessing other computers, it may take up to 5 minutes for the system to recognize all computers connected to EZ-Link. With the EZ-Link Network Manager, the user can access all computers connected to the EZ-Link private LAN immediately. The interface is intuitive and requires no manual for operation.

#### **AN2720 ENDPOINTS**

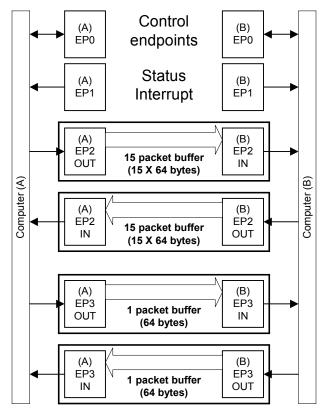

Figure below illustrates the AN2720 endpoints and how they are connected between two computers A and B.

AN2720 endpoints and FIFOS

Endpoint zero is the default CONTROL endpoints required by every USB device.

Endpoint 1 is an INTERRUPT endpoint, useful for communicating with the PC driver. Endpoints 2 and 3 are used to transfer USB BULK data. Endpoint 2 has extensive buffering (15 packets of 64 bytes each) and is designed to transfer high-bandwidth data. Endpoint 3, with a single packet of buffering, can be used as a higher priority channel for driver communication.

Endpoints 2 and 3 operate similarly to each other, differing only by the amount of buffering between the computers. Considering endpoint 2, when Computer (A) sends a packet over its endpoint 2 OUT, the packet is stored in the 15-packet FIFO. If Computer (B) does not send any IN tokens to its endpoint 2 (to retrieve a packet) by the time fifteen packets have been stored, the AN2720 NAKS the next OUT packet from Computer (A). This handshake is maintained by both endpoints 2 and 3, in both directions. When one side is unplugged, all packets are flushed from the FIFOS, and the AN2720 NAKS all IN and OUT tokens from the attached side.

### **USB CONFIGURATION**

The AN2720 supports a single configuration, with one interface consisting of the five alternate settings shown in Table 1.

Table 1. AN2720 endpoints and interface alternate settings

| Endpoints         | Setting 0 | Setting 1 | Setting 2    | Setting 3 | Setting 4 |

|-------------------|-----------|-----------|--------------|-----------|-----------|

| ep0 (8 Bytes)     | Control   | Test      | Control      | Test      | Test      |

| eplin (8 Bytes)   | X         | Mode      | intrpt (1mS) | Mode      | Mode      |

| ep2in (64 Bytes)  | Bulk      |           | Bulk         |           |           |

| ep2out (64 Bytes) | Bulk      |           | Bulk         |           |           |

| ep3in (64 Bytes)  | X         |           | Bulk         |           |           |

| ep3out (64 Bytes) | X         |           | Bulk         |           |           |

Alternate setting 0 is intended to consume no fixed USB bandwidth, ensuring that the AN2720 will always be enumerated on the USB bus. Alternate setting 2 uses the USB bandwidth more efficiently, employing an interrupt endpoint for status notification.

Alternate settings 1, 3 and 4 are diagnostic modes reserved by Cypress. Do not use these modes.

### VID/PID/DID CONFIGURATION

Windows plug and play (PnP) uses the USB VID, PID and DID to select the driver for each device in the system. It is possible to have two 2720 chips attached to a host, but have different drivers loaded for them (for example, to create a CE-Link serial link emulator and an EZ-Link NDIS product as separate devices).

The Manufacturing ID information is supplied from an EEPROM through the I2C port (SDADID1, SCLDID0). The I2C boot loader will check to make sure that an EEPROM exists and that the first byte in the EEPROM is 0xB0. If the boot loader finds that there is no EEPROM or that there is an EEPROM but the first byte is not 0xB0 then the VID/PID/DID will default to 0x0547, 0x2720, and 0x0000, respectively. If, however, there is an EEPROM and the first byte is 0xB0, then the boot loader will read the next six bytes to determine the custom VID/PID/DID:

| Byte Number | Value   |

|-------------|---------|

| 0           | 0xB0    |

| 1           | VID LSB |

| 2           | VID MSB |

| 3           | PID LSB |

| 4           | PID MSB |

| 5           | DID LSB |

| 6           | DID MSB |

These bytes are reported in bytes 8-13 of the device's response to a standard GET\_DESCRIPTOR device request.

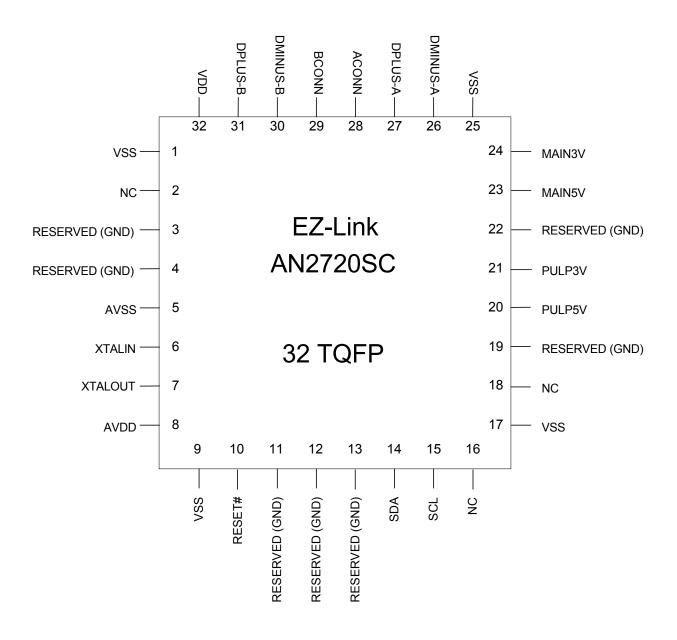

## **PINOUT**

Figure 1. AN2720SC pinout

## PIN DESCRIPTIONS

| Signal name | Pin<br># | Туре            | Driver                 | Description                                                                                                                                                            |  |

|-------------|----------|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VSS         | 1        | GROUND          |                        | Ground                                                                                                                                                                 |  |

| NC          | 2        |                 |                        | Reserved for future use. Must                                                                                                                                          |  |

|             |          |                 |                        | remain unconnected                                                                                                                                                     |  |

| Reserved    | 3        | INPUT           |                        | Connect to Ground                                                                                                                                                      |  |

| Reserved    | 4        | INPUT           |                        | Connect to Ground                                                                                                                                                      |  |

| AVSS        | 5        | GROUND          |                        | Ground                                                                                                                                                                 |  |

| XTALIN      | 6        | INPUT           | SPECIAL                | Connect this signal to a 12Mhz series resonant, fundamental mode crystal and 22-33 pF capacitor to GND. Data-rate tolerance is ±0.25% (2,500ppm) under all conditions. |  |

| XTALOUT     | 7        | OUTPUT          | SPECIAL                | Connect this signal to a 12Mhz series resonant, fundamental mode crystal and 22-33 pF capacitor to GND. Data-rate tolerance is ±0.25% (2,500ppm) under all conditions. |  |

| AVDD        | 8        | Analog<br>POWER |                        | Connect to MAIN3V and decoupling caps.                                                                                                                                 |  |

| VSS         | 9        | GROUND          |                        | Ground                                                                                                                                                                 |  |

| RESET#      | 10       | INPUT           | CMOS input             | Active low reset input                                                                                                                                                 |  |

| Reserved    | 11       | INPUT           |                        | Connect to Ground                                                                                                                                                      |  |

| Reserved    | 12       | INPUT           |                        | Connect to Ground                                                                                                                                                      |  |

| Reserved    | 13       | INPUT           |                        | Connect to Ground                                                                                                                                                      |  |

| SDA         | 14       | Ю               | 2mA CMOS bi-<br>dir    | Data line for I <sup>2</sup> C bus. Requires external 2.2K pullup.                                                                                                     |  |

| SCL         | 15       | Ю               | 2mA CMOS bi-<br>dir    | Clock line for I <sup>2</sup> C bus. Requires external 2.2K pullup.                                                                                                    |  |

| NC          | 16       | Reserved        | Reserved               | Reserved – No connect                                                                                                                                                  |  |

| VSS         | 17       | GROUND          |                        | Ground                                                                                                                                                                 |  |

| NC          | 18       | Reserved        | Reserved               | No connect                                                                                                                                                             |  |

| Reserved    | 19       | INPUT           | Reserved               | Connect to Ground                                                                                                                                                      |  |

| PULP5V      | 20       | INPUT           | Regulator power input  | Connect to B-side VBUS.                                                                                                                                                |  |

| PULP3V      | 21       | OUTPUT          | Regulator power output | Provides 3V for B-side D+ pullup resistor. See the example circuit for details on the use of this pin.                                                                 |  |

| Signal name | Pin<br># | Туре   | Driver                | Description                                                                                                         |

|-------------|----------|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| Reserved    | 22       | INPUT  | SPECIAL               | Connect to ground.                                                                                                  |

| MAIN5V      | 23       | INPUT  | Regulator power input | 5V input to integrated regulator. Connect to A side VBUS.                                                           |

| MAIN3V      | 24       | OUTPUT | Regulator<br>output   | 3V output from integrated regulator. Can be used as a 3.3V power supply and as 3.3v source for the 1.5K USB pullup. |

| VSS         | 25       | GROUND |                       | Ground                                                                                                              |

| DMINUSA     | 26       | IO     | SPECIAL               | D- pin for A side USB connection                                                                                    |

| DPLUSA      | 27       | IO     | SPECIAL               | D+ pin for A side USB connection                                                                                    |

| ACONN       | 28       | Input  | CMOS input            | Indicates to the chip that the 5V is present on the A side USB connector. Connect directly to A side VBUS.          |

| BCONN       | 29       | Input  | CMOS input            | Indicates to the chip that the 5V is present on the B-side USB connector. Connect directly to B-side VBUS.          |

| DMINUSB     | 30       | IO     | SPECIAL               | D- pin for B side USB connection                                                                                    |

| DPLUSB      | 31       | IO     | SPECIAL               | D+ pin for B side USB connection                                                                                    |

| VDD         | 32       | POWER  |                       | Input power for the digital portion of the chip. Connect to the 3.3V net w/ decoupling.                             |

## AC/DC PARAMETERS

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                      | 65 °C to +150 °C        |

|------------------------------------------|-------------------------|

| Ambient Temperature Under Bias           | 40 °C to +85 °C         |

| 3.3 V Supply Voltage to Ground Potential | $\dots$ -0.5V to +4.0 V |

| 5 V Supply Voltage to Ground Potential   | 0.5V to +5.8 V          |

| DC Input Voltage to Any Pin              | 0.5V to +5.8 V          |

## **OPERATING CONDITIONS**

| Ta (Ambient Temperature Under Bias)                | 0 °C to +70 °C   |

|----------------------------------------------------|------------------|

| 5V Supply Voltage (VBUS)                           | +4.4V to +5.25 V |

| Supply Voltage                                     | +3.0V to +3.6 V  |

| Ground Voltage                                     | 0 V              |

| F <sub>OSC</sub> (Oscillator or Crystal Frequency) |                  |

## **DC CHARACTERISTICS**

| Symbol                    | Parameter                | Condition                           | Min  | Max         | Unit | Notes                                                            |

|---------------------------|--------------------------|-------------------------------------|------|-------------|------|------------------------------------------------------------------|

| $V_{CC}$                  | Supply Voltage           |                                     | 3.0  | 3.6         | V    |                                                                  |

| $V_{\mathrm{IH}}$         | Input High Voltage       |                                     | 2    | 5.25        | V    |                                                                  |

| $V_{\rm IL}$              | Input Low Voltage        |                                     | 5    | .8          | V    |                                                                  |

| $I_{I}$                   | Input Leakage<br>Current | $0 < V_{IN} < V_{CC}$               |      | <u>+</u> 10 | μΑ   |                                                                  |

| V <sub>OH</sub>           | Output Voltage High      | $I_{OUT} = 1.6 \text{ ma}$          | 2.4  |             | V    |                                                                  |

| $V_{OL}$                  | Output Low Voltage       | $I_{OUT} = -1.6 \text{ ma}$         |      | .8          | V    |                                                                  |

| $C_{IN}$                  | Input Pin<br>Capacitance |                                     |      | 10          | pF   |                                                                  |

| $I_{SUSP}$                | Suspend Current          | Using internal regulator            |      | 250         | μΑ   | Add 220<br>µA for<br>1.5K<br>pullup<br>resistor.                 |

| $I_{CC}$                  | Supply Current           | Transferring data, connected to USB |      | 30          | mA   |                                                                  |

| $I_{OUT}$                 | Regulator output current |                                     | .200 | 50          | mA   |                                                                  |

| MAIN3<br>V <sub>OUT</sub> | Regulator output voltage |                                     | 3.3  | 5           | V    | Regulator will supply 5V for less than 200ms at initial startup. |

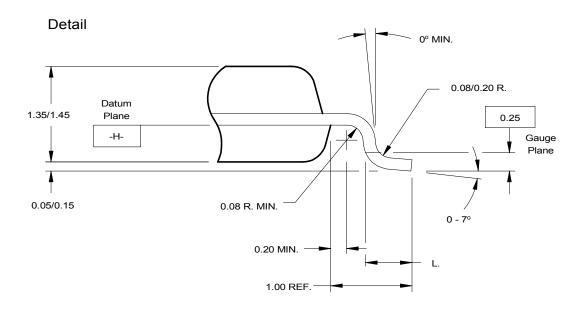

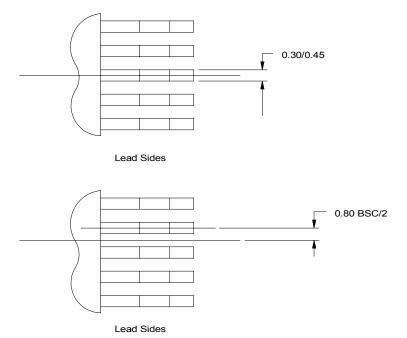

## **PACKAGE DRAWING**

Figure 2. Package information

Figure 3. Package detail

All Dimensions in MM.

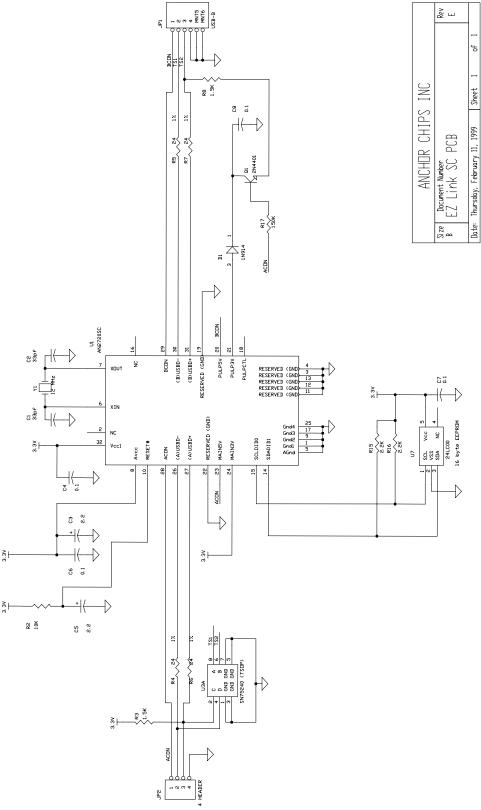

## **BOARD SCHEMATIC**

### SCHEMATIC NOTES

The AN2720SC includes two onboard regulators. The USB suspend current specification only permits a device to draw 500 uA in the suspend mode. The pullup resistor on D+draws 200 uA by itself, without any assistance from the AN2720SC. The second regulator allows each side to have its own 500 uA suspend budget.

The transistor and diode configuration on the BDPLUS pullup is used for power management. While only one side is connected, it is important not draw power from the host side even though it is physically connected. To simplify power management, we have assumed power is expected to always come from the A side of the chip. So when the A side is not connected and thus not receiving power, the B side must be disconnected from the host power source since the peripheral is not in use. The pullup on the B side is switched by the AVBUS line via the transistor, electrically disconnecting the B side when AVBUS is removed.

The "MNT" of the "MNT5" and "MNT6" in the JP1s USB-B represent mounting tabs on the USB B connector. They are on the schematic because they must be attached to the ground plane.

The schematic proposed will work for any number configurations, including the use of 2 B connectors or a complete cable with 2 A side connectors on each side of the chip.

The 24LC00 device is used for the VID and PID of the EZ-Link device. While we have included the most space efficient one in the schematic, any version will suffice.

The SN75240 is a USB surge suppressor from Texas Instruments. This surge suppressor is optional, but it does provide up to 8 KV of ESD protection. Since the USB interface has wires exposed to the outside world, some level of ESD immunity higher than the 2KV level inherent to the AN2720SC is recommended.

Should there be difficulties in passing the difficult EMI standards, a white paper at the Intel website should help guide the developer in resolving EMI problems. The white paper explores the variety of different methods of EMI reduction. For reference, the URL is <a href="http://developer.intel.com/design/USB/papers/EMI">http://developer.intel.com/design/USB/papers/EMI</a> APPS.HTM.

## **ORDERING PART NUMBERS**

| Cypress Part Number | Description                                  |

|---------------------|----------------------------------------------|

| AN2720SC-01         | AN2720SC plus Ethernet software              |

| AN2720SC-02         | AN2720SC plus Ethernet and bridging software |

## **DOCUMENTATION REVISION HISTORY**

| Revision | Date     | Changes                                                      |

|----------|----------|--------------------------------------------------------------|

| Initial  | 9/20/98  | Initial release. No revision information saved               |

| 0.9      | 9/29/98  | Updated based on Engineering feedback                        |

| 0.91     | 10/06/98 | Updated package drawing                                      |

| 0.92     | 10/8/98  | Slight corrections based on more Engineering feedback        |

| 0.95     | 11/10/98 | Updated block diagram, included part numbers and s/w section |

| 0.97     | 2/12/99  | Updated schematic. Included schematic notes.                 |

| 1.0      | 5/15/99  | Added more detailed description of the crystal requirements  |

| 1.1      | 6/07/00  | Changed from Anchor Chips to Cypress and other minor changes |