# 13-BIT LINEAR FEATURE CODEC WITH ANALOGUE FRONTEND

Austria Mikro Systeme International AG

#### **Key Features**

- □ 13-Bit Linear Sigma Delta Codec with Filters Exceeding ETSI prETS30085 and G712.

- □ Single Rail 3.0 V ~5.5 V Power Supply.

- Typical Power Dissipation of 30 mW at 3 V.

- Two Low Noise Microphone Inputs with Internal Gain Adjust (+16 / +46 dB).

- In 150Ω Push/Pull Earpiece Driver with Internal Gain Adjust (-12 / +6 dB).

- 50Ω Loudspeaker Amplifier with up to 50 mW Output Power.

- Push/ Pull Output Driver for Tone Ringer.

- On Chip Electret Microphone Voltage Source.

- Digital Transmit Gain Setting (-38 / +10 dB).

- Digital Receive Gain Setting (-42 / +6 dB).

- Digital Sidetone Control Function (0 / -48 dB).

- Programmable Call Progress Tone/ DTMF / Ring Tone Generator.

- Analogue and Digital Loopback Modes.

- 16-Bit Linear / 8-Bit A-Law Switchable Serial PCM Interface with Non Delayed and Delayed Timing Modes.

- **4**-Wire Serial Control Interface.

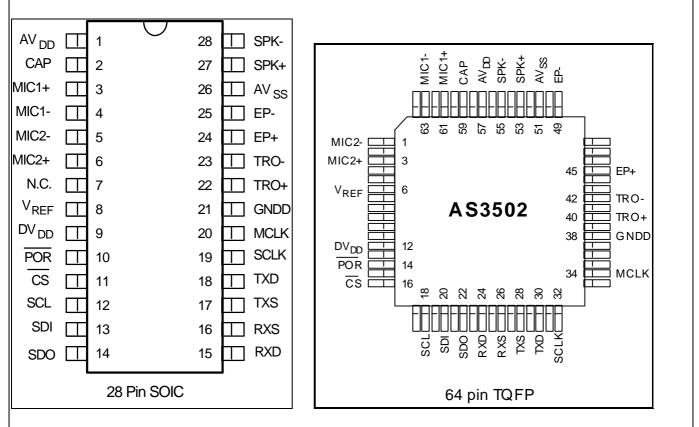

- Packaged in SOIC-28, TQFP-64.

#### **General Description**

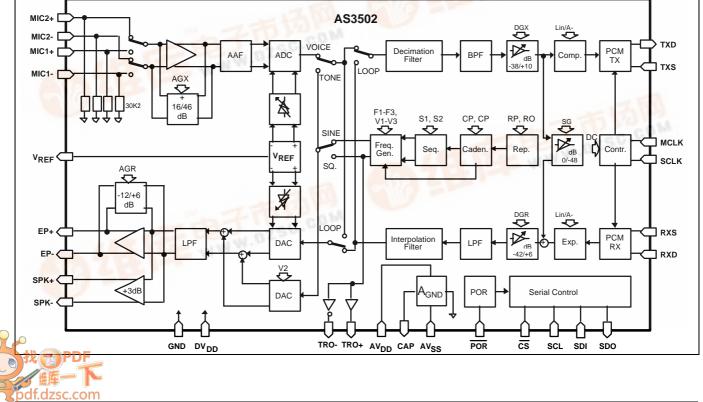

AS3502 is a high performance 13-bit linear feature Codec/Filter with 8 kHz sampling rate specifically tailored to implement all analogue frontend functions of battery powered digital terminals. It includes a programmable analogue interfaces for handset and handsfree operation with a minimum amount of external components.

The Codec function of AS3502 uses Sigma-Delta ( $\Sigma\Delta$ ) modulation conversion techniques with 2nd order modulators and an over sampling rate of 128 for excellent signal to noise performance. The AS3502 exceeds all CCITT G712 recommendations and the European ETSI prETS 300085 recommendations.

Digital gain setting stages for transmit and receive allow to compensate for transducer tolerances and to set up a handsfree function under software control. A programmable tone generator allows to generate DTMF/Call-Progress Tones and alert sounds required in digital terminals. All programmable functions of AS3502 are controlled by a 4-wire serial control port that easily interfaces to any popular micro controller.

The interface to the digital world is accomplished by a serial PCM interface that supports 16-bit linear format or 8-bit A-Law format for both non-delayed and delayed frame synchronzation modes.

September 1998

Page 1

# Block Diagramme

REV M

## **Pinout Diagramme**

## **Pin Description**

| Pin # | Name  | Туре | Function                                                                                                                                                                                                                   |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | AVDD  | SI   | Analogue Positive Supply Voltage Input                                                                                                                                                                                     |

| 2     | CAP   | AO   | <b>Filter Capacitor Output</b><br>This pin requires to be connected to an external blocking capacitor of app. 47µF<br>and is internally connected to the potential divider of the analogue ground genera-<br>tion circuit. |

| 3     | MIC1- | AI   | Differential Microphone 1 Inputs                                                                                                                                                                                           |

| 4     | MIC1+ | AI   | These two pins are differential inputs to the analogue input multiplexer of the gain programmable microphone amplifier with an input impedance of approx. 60 k $\Omega$ .                                                  |

| 5     | MIC2- | AI   | Differential Microphone 2 Inputs                                                                                                                                                                                           |

| 6     | MIC2+ | AI   | These two pins are differential inputs to the analogue input multiplexer of the gain programmable microphone amplifier with an input impedance of approx. 60 k $\Omega$ .                                                  |

| 7     | N.C.  |      |                                                                                                                                                                                                                            |

| 8     | VREF  | AO   | <b>Microphone Reference Voltage Output</b><br>This pin provides a stabilized reference voltage for an electret microphone of approx. 2V.                                                                                   |

| 9     | DVDD  | SI   | Digital Positive Supply Voltage Input                                                                                                                                                                                      |

| Pin Description (continue |

|---------------------------|

|---------------------------|

| Pin # | Name | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10    | POR  | DI   | <b>Power On Reset Input</b><br>An active Low signal on this pin starts the system initialization. All internal registers<br>are set to their default values and the serial interface will be reinitialized and the<br>chip will enter power down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11    | ĊS   | DI   | Serial Control Chip Select Input<br>An active Low signal on this pin enables serial data transfers via SDI and SDO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12    | SCL  | DI   | <b>Serial Control Clock Input</b><br>This pin acts as shift clock signal input for serial control data transfer via SDI and<br>SDO when CS is active Low and may be asynchronous to all other clock signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13    | SDI  | DI   | <b>Serial Control Data Input</b><br>This input samples control data bits on the rising edges of the serial clock SCL when $\overline{CS}$ is active Low. Depending on the type of transfer 8 or 16 bits are shifted in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14    | SDO  | DO   | Serial Control Data Output<br>This output shifts out control/status data with the falling edge of SCL when $\overline{CS}$ is active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15    | RXD  | DI   | <b>Receive PCM Data Input</b><br>This input samples PCM data bits on the falling edges of the serial clock SCLK following a rising edge on the receive strobe signal. After the time when all data bits have been shifted into the receive shift register all bits are latched into the receive latch for digital to analogue conversion.                                                                                                                                                                                                                                                                                                                                                             |

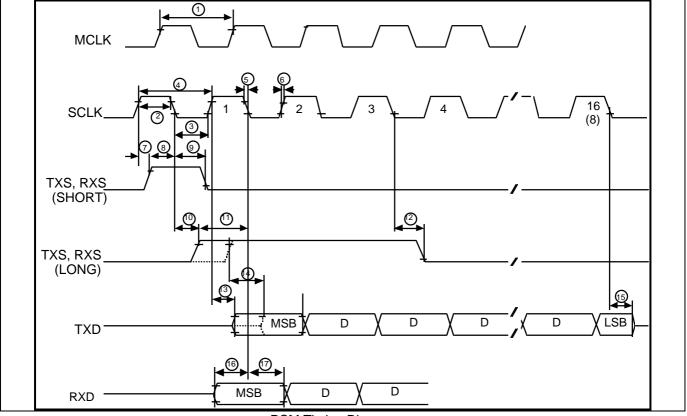

| 16    | RXS  | DI   | <b>Receive PCM Strobe Input</b><br>The signal on this input initiates shifting of serial data into the receive shift register.<br>It must be synchronized with SCLK. The clock rate is typically 8 kHz. The signal<br>width determines whether short strobe or long strobe mode is used: A pulse width<br>of one to two shift clock periods selects short strobe mode. (For further information<br>see PCM Timing Diagramme ). The strobe signal does not need to be active<br>throughout the transmission period since an internal bit counter generates the<br>necessary timing for 8 or16 bit periods depending on the selected output format for<br>serial PCM reception.                         |

| 17    | TXS  | DI   | <b>Transmit PCM Strobe Input</b><br>This signal on this input initiates shifting of serial data out of the transmit shift<br>register. It must be synchronized with SCLK. The clock rate is typically 8 kHz. The<br>signal width determines whether short strobe or long strobe mode is used: A pulse<br>width of one to two shift clock periods selects short strobe mode. Pulse widths<br>from 3 clock periods on wards select long strobe mode. The strobe signal does not<br>need to be active throughout the transmission period since an internal bit counter<br>generates the necessary timing for 8 or 16 bit periods depending on the selected<br>output format for serial PCM transmission. |

| 18    | TXD  | DO   | <b>Transmit PCM Data Output</b><br>This Tristate output shifts out PCM data from the Codec's A/D converter and is<br>activated during the transmission of serial data for 8 or 16 transmit clock periods<br>following a rising edge on the transmit strobe signal. It is updated by the rising<br>edges of the SCLK clock signal. The output goes back to high impedance after<br>transmission of 8 or 16 data bits.                                                                                                                                                                                                                                                                                  |

## Pin Description (continued)

| D: "     |                                            | ,<br>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|--------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #    | Name                                       | Туре     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19       | SCLK                                       | DI       | Serial PCM Shift Clock Input<br>This pin acts as shift clock input signal for the externally provided signal for serial<br>PCM data transfer. The frequency may vary from 128 kHz to 4.096 MHz in 8 kHz<br>increments and should be synchronized to MCLK. In the receive direction the<br>bitstream is latched with the falling edge of this clock. In the transmit direction the<br>bitstream is shifted out with the rising edges of this clock. |

| 20       | MCLK                                       | DI       | Master Clock Input<br>This signal is the timing reference for all internal operations. The clock frequency<br>must be a integer multiple of 2.048 MHz with a maximum of 18.432MHz and must<br>be synchronized to SCLK. The required master clock dividing ratio is selected by<br>setting the DIV3 -DIV0 bits in the Digital Control Register.                                                                                                     |

| 21       | GND                                        | SI       | Digital Negative Supply Voltage Input                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22<br>23 | TR+<br>TR-                                 | DO<br>DO | <b>Differential Toneringer Outputs</b><br>These digital outputs provide square or sine wave signal for driving transducers directly. TRO+ and TRO- are operating in push/pull mode providing peak to peak voltage swing of 2 x VDD. The output volume is programmable and is accomplished either through pulse density modulation or through pulse width modulation.                                                                               |

| 24<br>25 | EP-<br>EP+                                 | AO<br>AO | <b>Differential Earpiece Outputs</b><br>These two pins are the outputs of the differential earpiece amplifier driving either dynamic earpieces with $150\Omega$ impedance or ceramic transducers with up to $50nF$ directly. The signal reference on both pins is DC referenced to the internally generated Analogue Ground which is appr. 1/2 VDD.                                                                                                |

| 26       | AVSS                                       | SI       | Analogue Negative Supply Voltage Input                                                                                                                                                                                                                                                                                                                                                                                                             |

| 27<br>28 | SP+<br>SP-                                 | AO<br>AO | <b>Differential Loudspeaker Outputs</b><br>These two pins are the outputs of the differential loudspeaker amplifier that is ca-<br>pable driving dynamic speakers with $50\Omega$ impedance directly. The maximum<br>output power is 50mW. The signal reference on both pins is DC referenced to the<br>internally generated Analogue Ground which is appr. 1/2 VDD.                                                                               |

| DI: Di   | nalogue Inp<br>gital Input<br>gital Input/ |          | AO: Analogue Output<br>DO: Digital Output<br>SI: Supply Input                                                                                                                                                                                                                                                                                                                                                                                      |

## **Functional Description**

#### Power-On Reset

When power is applied first a power on reset signal is generated on chip which initializes AS3502:

The on chip programmable AFE registers are set to their default values (those values are defined in the register allocation section), the tone control register is set to the default status and the serial interface is initialized. AS3502 remains in power down state until a software start-up command. An active Low signal with a duration of min. 25  $\mu$ s on the power on reset pin can be used to externally reset the device AS3502. For normal operation this pin must be pulled High.

#### Power Up Mode

AS3502 is powered up through a one byte start-up command. The byte written into the Digital Control Register DC allows to individually enable the transmit and the receive section. If the transmit channel is enabled first, the receive channel may be enabled any time without any restrictions. On enabling the receive channel and subsequent enabling of the transmit channel the PCM strobe signals TXS and RXS have to be tied together. The configuration information written into the AC and AG define which analogue transducer interfaces will be enabled on power up. The PCM output TXD remains in Tristate until the second frame synchronization signal after start-up. Any of the programmable registers may be modified while AS3502 is in active mode.

#### **Power Down Mode**

In power down mode all chip functions except the serial interface are kept inactive. All analogue functions are powered down and all digital outputs are put into Tristate mode. In this operating state the internal registers are normally configured to the desired values prior to the start-up command. The chip can be brought into power down mode any time through a power down command written into the DC Register. In this case all programmable registers retain their programmed values.

#### Analogue Input interface

The AS3502 input interface provides two identical differential inputs e.g. for a handset microphone and for a handsfree microphone. The input sources are selected through the AG register. Clipping of signals with arbitrary DC offset must be avoided by capacitive coupling. The input impedance of 2 x 30 k $\Omega$  is compatible with both and electret dvnamic microphones. Each input is connected through an analogue input multiplexer to a low noise high gain preamplifier. The gain is software programmable through register AG from +16 to +46 dB in 6 dB steps with a tolerance of ±0.2 dB. This wide range guarantees optimum usage of the A/D converter dynamic range with various transducers.

#### Analogue Output Interface

The AS3502 output interface provides differential outputs for an earpiece, for a loudspeaker and for a toneringer. The output stages are selected through the AC register. The earpiece output driver is a fully differential amplifier that is capable of driving 3.2Vpp into a 150 $\Omega$  transducer directly and is gain programmable in three steps from -12 dB to +6 dB through the AG register. The +6 dB step allows to drive ceramic earpiece transducers or to boost the receive amplitude. The loudspeaker driver is a fully differential power amplifier with a peak output power of 50 mW into a 50 $\Omega$  loudspeaker. This output allows loudhearing and handsfree operation under software control.

The tone ringer outputs are digital push/pull outputs with rail to rail voltage swing that capable of driving various toneringers. For volume control the output signal may be either pulse density modulated or pulse width modulated under software control.

#### **Transmit Section**

The scaled analogue input signal enters a 1st order RC antialiasing filter with a corner frequency of approx. 40 kHz. This filter eliminates the need for any off chip filtering as it provides sufficient attenuation at 1.024 MHz to avoid aliasing. From there the bandlimited signal is fed to a 2nd order Sigma Delta modulator with a sampling frequency of 1.024 MHz. A factory trimmed voltage reference guarantees accurate absolute transmit gain (0 dBm0 reference level). The modulator is followed by a digital decimation filter that transforms the resolution in time to resolution in amplitude. The decimation filter is followed by a minimum phase 5th order IIR filter implementing the CCITT lowpass portion of the encoder bandpass frequency characteristics. Finally a 3rd order IIR high pass filter implements the highpass portion of the encoder bandpass frequency characteristics according to CCITT specifications.

The digitally filtered signal is further fed to a digital gain setting stage which allows to program the gain from -38 to +10 dB with a tolerance of better than  $\pm 0.05$  dB from 0 to +6 dB to compensate for transducer sensitivity variations. The same stage may additionally be used for digital volume control for transmit volume attenuation. This feature may be used for software based handsfree voice switching algorithms.

In case of 16 bit linear mode the voice band signals are converted to a PCM two's complement 12 data bit plus sign bit format with a sample rate of 8 kHz and shifted out of the encoder under control of an externally applied shift clock signal SCLK.

In case of 8-bit companded mode the voice band signals are converted to a PCM two's complement 7 data bit plus sign bit A-Law format with a sample rate of 8 kHz and shifted out of the encoder under control of an externally applied shift clock signal SCLK.

#### **Receive Section**

In case of 16 bit linear mode PCM data is shifted into the input shift register at a clock rate determined by the shift clock SCLK every 128  $\mu$ s. 13 bits of PCM data are transferred to the receive latch that holds the data throughout the conversion process.

In case of 8-bit companded mode PCM data is shifted into the input shift register at a clock rate determined by the shift clock SCLK every 128µs and converted from A-Law format to 13-bit linear format. Optionally a programmable digital sidetone stage adds a certain amount of the transmit signal to the receive path for natural acoustic performance. The sidetone range can be adjusted from -48 dB to 0 dB with a default value of -18 dB. Both signals are combined and fed to a digital gain setting stage which allows to program the gain from -42 to +6 dB with a tolerance of ±0.05 dB from 0 to -6dB to compensate for transducer sensitivity variations. The same stage may additionally be used for digital volume control for receive volume attenuation. This feature may be used for software based handsfree voice switching algorithms. The gainsetting stage is followed by a digital filter that bandlimits the signal according to CCITT recommendations and that converts the resolution in amplitude to resolution in time through interpolation. The output signal is fed to a digital 2nd order sigma delta modulator with a sampling rate of 1.024 MHz. The bit stream is further fed to a combined 1 bit DAC / 2nd order SC Lowpass filter with an corner frequency of 8 kHz and further to a 1st order RC active smoothing filter that provides additional filtering of out of band signals.

The loudspeaker volume may be controlled digitally through the Receive Digital Gain Register DGR.

#### **Tone Generator**

AS3502 contains a powerful tone generator that is capable of generating all European country specific ring/ call progress tones and DTMF tones for audible feedback in the receive path or inband signalling tones in the transmit path under software control.

The tone generator operation modes are programmable through 13 8-bit registers that are accessed through the serial control interface. (See register description for further details). Since all melody functions are handled by the AS3502 tone generator hardware only a minimum amount of

software overhead for the controlling microprocessor is necessary.

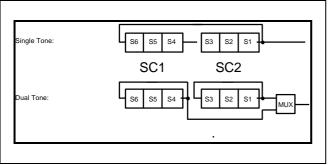

The tone generator consists of a single /dual tone synthesizer, a six tone sequencer, a cadence counter and a repetition counter.

#### **Frequency Generator**

For in band signalling a square wave or sine signal with precise DTMF capability is generated. The tones may be added to the receive section or injected into the transmit section. For tone ringing a square wave push/pull signal is generated on the TRO+ and TRO-. digital outputs.

#### Transmit Tone Volume Control

For sine wave forms the transmit PCM level is controlled by a 0 /-2.5 dB attenuation block and additionally by the digital transmit gain stage (DGX). For square wave forms the transmit PCM level is controlled by the V1 register and the DGX register.

#### Receive Tone Volume Control

The receive amplitude of sine wave signals may be controlled via the V2 register.

The receive amplitude of square wave signals may be controlled by both the V1 and the V2 register.

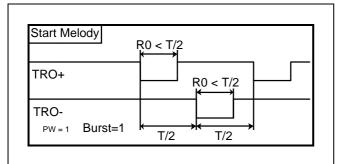

#### Tone Ringer Volume Control

The output volume is programmable through the V1 register and is accomplished either through pulse density modulation or through pulse width modulation. For pulse density volume control the amplitude is controlled through the V1 register.

Pulse Density Volume Control

For pulse width volume control the R0 counter is used where it generates the duty cycle. In this case the repetition has to be controlled by the microprocessor through software.

Pulse Width Volume Control

#### Sequencer

The sequencer controlling the synthesizer is a six step rotating shift register that is controlled by a cadence counter. Each location in the two sequence control registers (SC1, SC2) contains the value of one out of three different frequencies or the value of a tone pause that are played in consecutive order. In DTMF mode the 6-bit shift register is split up into two 3-byte shift registers. In this mode the cadence steps are interleaved as S1/S4, S2/S5, S3/S6 where the SC1 register defines the high group tones with an attenuation of 2.5 dB and where the SC2 register defines the low group tones.

Tone Sequencer

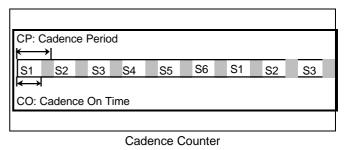

#### Cadence Generation

The cadence counter determines the sequencer rotation speed and the on/ off timing characteristics of the tones and controls both the sequencer shift clock and the tone synthesizer on/ off time. The tone off time allows to insert pauses on switching from one frequency to the other.

Cadence Period (CP) and Cadence On Time (CO) are programmed with an 8-bit value. The CS bit defines two time spans with different resolution:

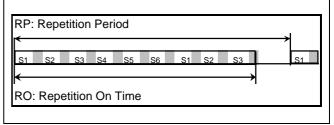

#### **Repetition Counter**

The repetition counter controls either the duration (RO) and repetition (RP) of the melody sequence or the volume for pulse width volume control of the tone ringer output.

In repetition mode the repetition counter may be operated in continuous mode where the ringing signal is turned on and off with the RP and R0 period or in single shot mode where the ringing signal is active for the R0 period. only.

Each tone signalling sequence must be started with this counter:

Repetition Period (RP) and Repetition On Time (RO) are programmed with an 8-bit value .

Repetition Counter

#### **PCM Serial Interface**

The AS3502 5-wire PCM port interfaces directly to many serial port standards. The PCM data word is either formated in 16-bit linear format with 13 bit 2's complement data justified left where the last three LSB bits are reserved or formatted according to 8-bit A-Law format with alternate mark inversion (AMI) meaning that the even bits are inverted per CCITT G711 specification.

| PCM Level          |        | 8-Bit A-Law Format |        |        |        |        |        | 16-Bit Linear Format |             |             |             |             |             |             |        |        |        |        |        |        |        |        |        |        |

|--------------------|--------|--------------------|--------|--------|--------|--------|--------|----------------------|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|                    | D<br>7 | D<br>6             | D<br>5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0               | D<br>1<br>5 | D<br>1<br>4 | D<br>1<br>3 | D<br>1<br>2 | D<br>1<br>1 | D<br>1<br>0 | D<br>9 | D<br>8 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0 |

| VIN = + Full Scale | 1      | 0                  | 1      | 0      | 1      | 0      | 1      | 0                    | 0           | 1           | 1           | 1           | 1           | 1           | 1      | 1      | 1      | 1      | 1      | 1      | 1      | Х      | х      | х      |

| VIN = +0-Code      | 1      | 1                  | 0      | 1      | 0      | 1      | 0      | 1                    | 0           | 0           | 0           | 0           | 0           | 0           | 0      | 0      | 0      | 0      | 0      | 0      | 1      | х      | х      | х      |

| VIN = -0-Code      | 0      | 1                  | 0      | 1      | 0      | 1      | 0      | 1                    | 1           | 1           | 1           | 1           | 1           | 1           | 1      | 1      | 1      | 1      | 1      | 1      | 1      | х      | х      | х      |

| VIN = - Full Scale | 0      | 0                  | 1      | 0      | 1      | 0      | 1      | 0                    | 1           | 0           | 0           | 0           | 0           | 0           | 0      | 0      | 0      | 0      | 0      | 0      | 0      | х      | х      | х      |

x: not used

The interface supports short and long strobe synchronisation modes and full duplex synchronous operations of both receive and transmit section. PCM data is written into the transmit register and shifted out in 8 or 16 clock cycles by the transmit shift register. In the receive direction serial input 8 or 16 samples are converted into parallel format by the receive shift register and hereafter buffered in the receive latch. This double buffered hardware I/O scheme guarantees minimum port latency and increased channel service time. Both shift registers have separate strobe signals for asynchronous time slot operation of transmit and receive channel and are clocked by a common shift clock signal that may vary from 64 kHz up to 4.096 MHz and that must be locked to the master clock. The strobe signals have to be synchronised to the shift clock and should have a repetition rate of 8 kHz. ±50 ppm.

#### Short Strobe Mode

This is the default mode on powering up the device. The transmit and receive strobe inputs must be one bit shift clock long and have to be High during a falling edge of the respective bit shift clocks (see PCM Timing Diagramme) In the transmit section the next rising edges of SCLK enable the TXD output buffer and shift out PCM data bits. The falling edge of the last bit shift clock SCLK disables the TXD output buffer. In the receive section the next falling edge of SCLK shifts in PCM data bits at RXD.

#### Long Strobe Mode

The serial port enters the long strobe mode if both strobe pulses (TXS, RXS) are more than three bit clock periods long (See PCM Timing Diagramme). In the transmit section the next rising edge of SCLK or TXS, whichever comes later, clocks out the first bit. The effect of the transmit strobe occurring after the shift clock is to shorten the first bit at the TXD output. The following rising edges of the SCLK shift out the remaining data bits. The TXD output is disabled by the last falling SCLK edge or by the TXS signal going Low, whichever comes later. In the receive section a rising edge on the receive strobe input RXS will initiate the PCM data on RXD pin to be shifted into the receive shift register with the falling edges of SCLK.

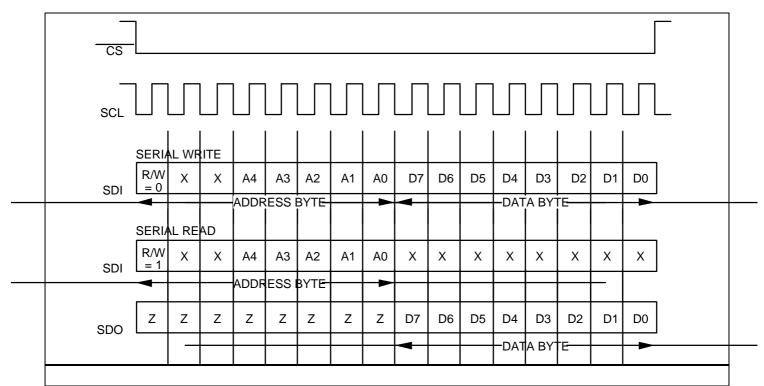

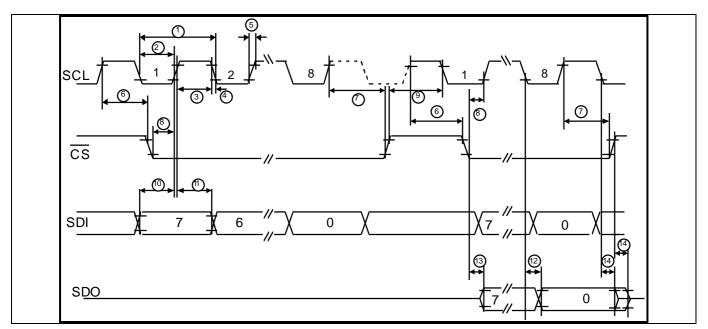

#### **Serial Control Interface**

The internal operation of AS3502 is controlled by a 4wire serial port that is designed to write and read back control and status information from any serial microprocessor port. It consists of a 16 bit shift register with 8 address bits and 8 data bits. The first byte is the Address Byte that is clocked in serially by asserting the  $\overline{CS}$  line for 8 clock cycles. The MSB address bit in the address field defines whether the data transfer is a write or a read operation. The second byte is the Command Data Byte that is clocked in by keeping  $\overline{CS}$  Low for another 8 clock cycles. The address decoder latches the address bits received into a register after 8 clock cycles. It operates fully autonomously and constantly cycles through 3 states:

- Load address decoder

- Calculate address and type of data transfer

- Data transfer

After decoding the data byte is latched into the decoded register during a write operation or retrieved from the selected register during a read operation.

Data is retrieved by asserting the  $\overline{CS}$  line and by shifting 8 address bits into the input shift register through SDI. The next 8 clock cycles shift out the data byte through SDO. The full shift register is shifted out where the 8 MSB bits are shifted out as Hi-Z.

Data states on the SDO line can only change with the falling edge of SCL. Data on the SDI line is shifted in with the rising edge of SCL.

All commands are preceded by the start condition, which is a High to Low transition of the  $\overline{CS}$  line. The AS3502 continuously monitors this line for the start condition and does not respond to any command until this condition has been met.  $\overline{CS}$  may either be kept Low for 16 clock cycles or may go High after 8 clock cycles and go Low again for the next 8 clock cycles when programming different register locations.

All communications are terminated by a stop condition, which is a Low to High transition of  $\overline{CS}$  after 16 shift clock cycles. The stop condition is also used to place the AS3502 serial control interface in the standby power mode.

Serial Control Interface

## **Programmable Functions**

19 8-bit internal registers are provided for control and operation status monitoring. The addresses are divided into two register banks with 16 locations each. Address bit A4 selects between the upper and the lower register bank. Address bit A7 defines whether the operation will be a write or read operation.

| Register Bit Sur    | nmary | <u>y</u>        |         |       |       |          |                 |                 |                 |       |

|---------------------|-------|-----------------|---------|-------|-------|----------|-----------------|-----------------|-----------------|-------|

| REGISTER            |       | ADDR            |         |       | Γ     | DATA BIT | NUMBER          | २               |                 |       |

|                     |       | A4- A0          | D7      | D6    | D5    | D4       | D3              | D2              | D1              | D0    |

| Digital Control     | DC    | 00 <sub>h</sub> | A / LIN | ENRX  | ENTX  | DIV3     | DIV2            | DIV1            | DIV0            | 0     |

| Analogue Control    | AC    | 01 <sub>h</sub> | 0       | 0     | LOOP  | CLRX     | CLTX            | ENEP            | ENSPK           | NOV   |

| Analogue Gain       | AG    | 02 <sub>h</sub> | 0       | ENM2  | ENM1  | AGX2     | AGX1            | AGX0            | AGR1            | AGR0  |

| TX Digital Gain     | DGX   | 03 <sub>h</sub> | DGX7    | DGX6  | DGX5  | DGX4     | DGX3            | DGX2            | DGX1            | DGX0  |

| Sidetone Gain       | SG    | 05 <sub>h</sub> | SG7     | SG6   | SG5   | SG4      | SG3             | SG2             | SG1             | SG0   |

| RX Digital Gain     | DGR   | 07 <sub>h</sub> | DGR7    | DGR6  | DGR5  | DGR4     | DGR3            | DGR2            | DGR1            | DGR0  |

| Tone Control        | тс    | 10 <sub>h</sub> | TRINJ   | RXINJ | TXINJ | CS       | BURST<br>MODE   | SHAPE           | TONE<br>MODE    | START |

| Sequence Control 1  | SC1   | 11 <sub>h</sub> | 0       | 0     | S31   | S30      | S21             | S20             | S1 <sub>1</sub> | S10   |

| Sequence Control 2  | SC2   | 12 <sub>h</sub> | 0       | 0     | S61   | S60      | S51             | S50             | S4 <sub>1</sub> | S40   |

| Frequency Control 1 | F1    | 13 <sub>h</sub> | F17     | F16   | F15   | F14      | F13             | F12             | F1 <sub>1</sub> | F10   |

| Volume Control 1    | V1    | 14 <sub>h</sub> | 0       | V14   | V13   | V12      | V1 <sub>1</sub> | V10             | F19             | F18   |

| Frequency Control 2 | F2    | 15 <sub>h</sub> | F27     | F26   | F25   | F24      | F23             | F22             | F21             | F20   |

| Volume Control 2    | V2    | 16 <sub>h</sub> | 0       | 0     | V23   | V22      | V2 <sub>1</sub> | V20             | F29             | F28   |

| Frequency Control 3 | F3    | 17 <sub>h</sub> | F37     | F36   | F35   | F34      | F33             | F3 <sub>2</sub> | F3 <sub>1</sub> | F30   |

| Volume Control 3    | V3    | 18 <sub>h</sub> | 0       | 0     | 0     | 0        | PS              | PW              | F39             | F38   |

| Repetition Period   | RP    | 19 <sub>h</sub> | RP7     | RP6   | RP5   | RP4      | RP3             | RP2             | RP1             | RP0   |

| Repetition On Time  | RO    | 1A <sub>h</sub> | RO7     | RO6   | RO5   | RO4      | RO3             | RO2             | RO1             | RO0   |

| Cadence Period      | СР    | 1B <sub>h</sub> | CP7     | CP6   | CP5   | CP4      | CP3             | CP2             | CP1             | CP0   |

| Cadence On Time     | со    | 1C <sub>h</sub> | C07     | CO6   | CO5   | CO4      | CO3             | CO2             | CO1             | CO0   |

## Register Bit Summary

## 1) DIGITAL CONTROL REGISTER

This register controls the master clock divider, the enabling of the transmit channel, the enabling of thereceive channel and the PCM format.

| DC      | D7    | D6   | D5   | D4   | D3   | D2   | D1   | D0 |

|---------|-------|------|------|------|------|------|------|----|

| Name    | A/LIN | ENRX | ENTX | DIV3 | DIV2 | DIV1 | DIV0 | Х  |

| Default | 0     | 0    | 0    | 0    | 0    | 0    | 0    | Х  |

| Bit No | Symbol    | Name ar               | nd Des                                                                                                                                                                                                                           | criptio            | on                  |                  |                                                                                                                                               |  |  |  |  |  |  |

|--------|-----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| D7     | A/LIN     |                       | Law / Linear Select. In default mode or when set to Low 16-bit linear PCM format is lected. When set to High 8-bit A-Law PCM format is selected.                                                                                 |                    |                     |                  |                                                                                                                                               |  |  |  |  |  |  |

| D6     | ENRX      | output dr             | table Receive Channel. When set to High the Receive Channel including the selected tput driver, the master clock divider and the Receive PCM interface are enabled.<br>then set to Low the Receive Channel will be powered down. |                    |                     |                  |                                                                                                                                               |  |  |  |  |  |  |

| D5     | ENTX      | Enable T<br>lected mi | ransm<br>icropho                                                                                                                                                                                                                 | it Char<br>one inp | nnel. V<br>out, the | /hen se<br>maste | et to High the Transmit Channel including the se-<br>r clock divider and the Transmit PCM interface are<br>smit Channel will be powered down. |  |  |  |  |  |  |

| D4- D1 | DIV3-DIV0 |                       |                                                                                                                                                                                                                                  |                    |                     |                  |                                                                                                                                               |  |  |  |  |  |  |

|        |           | DIV3                  | DIV2                                                                                                                                                                                                                             | DIV1               | DIV0                | <u>State</u>     | Master Clock Frequency                                                                                                                        |  |  |  |  |  |  |

|        |           | 0                     | 0                                                                                                                                                                                                                                | 0                  | 0                   | ÷1               | 2.048 MHz                                                                                                                                     |  |  |  |  |  |  |

|        |           | 0                     | 0                                                                                                                                                                                                                                | 0                  | 1                   | ÷2               | 4.096 MHz                                                                                                                                     |  |  |  |  |  |  |

|        |           | 0                     | 0                                                                                                                                                                                                                                | 1                  | 0                   | ÷3               | 6.144 MHz                                                                                                                                     |  |  |  |  |  |  |

|        |           | 0                     | 0                                                                                                                                                                                                                                | 1                  | 1                   | ÷4               | 8.192 MHz                                                                                                                                     |  |  |  |  |  |  |

|        |           | 0                     | 1                                                                                                                                                                                                                                | 0                  | 0                   | ÷5               | 10.240 MHz                                                                                                                                    |  |  |  |  |  |  |

|        |           | 0                     | 1                                                                                                                                                                                                                                | 0                  | 1                   | ÷6               | 12.288 MHz                                                                                                                                    |  |  |  |  |  |  |

|        |           | 0                     | 1                                                                                                                                                                                                                                | 1                  | 0                   | ÷7               | 14.336 MHz                                                                                                                                    |  |  |  |  |  |  |

|        |           | 0                     | 1                                                                                                                                                                                                                                | 1                  | 1                   | ÷8               | 16.386 MHz                                                                                                                                    |  |  |  |  |  |  |

|        |           | 1                     | 0                                                                                                                                                                                                                                | 0                  | 0                   | ÷9               | 18.432 MHz                                                                                                                                    |  |  |  |  |  |  |

## 2) ANALOGUE CONTROL REGISTER

The Analogue Control Register enables the output drivers and the muting of the receive voice channel. Further it allows to monitor clipping in both the transmit and the receive channel for software based automatic gain control.

| AC      | D7 | D6 | D5   | D4     | D3     | D2   | D1    | D0  |

|---------|----|----|------|--------|--------|------|-------|-----|

| Name    | 0  | 0  | LOOP | CLIPRX | CLIPTX | ENEP | ENSPK | NOV |

| Default | 0  | 0  | 0    | 0      | 0      | 0    | 0     | 0   |

| Bit No | Symbol | Name and Description                                                                                                                                                                                                                                           |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D6  | -      | These bits are Low during a read operation.                                                                                                                                                                                                                    |

| D5     | LOOP   | Loop Back Mode Enable. When set to High a loop back mode is enabled where the output of the sigma delta converter is directly fed to the input of the 1-bit DAC and where the output of the interpolation filter is fed to the input of the decimation filter. |

| D4     | CLIPRX | Receive Channel Clipping. On reading this bit a High indicates an overload condition in the receive channel.                                                                                                                                                   |

| D3     | CLIPTX | Transmit Channel Clipping. On reading this bit a High indicates an overload condition in the transmit channel.                                                                                                                                                 |

| D2     | ENEP   | Enable Earpiece. When set to High the earpiece driver is enabled. When set to Low the earpiece driver is powered down.                                                                                                                                         |

| D1     | ENSPK  | Enable Speaker. When set to High the loudspeaker driver is enabled. When set to Low the loudspeaker driver is powered down. Both drivers may be activated if necessary e.g. for call progress monitoring.                                                      |

| D0     | NOV    | No Voice. When set to High the voice signal in the receive channel is muted.                                                                                                                                                                                   |

## 3) ANALOGUE GAIN REGISTER

This register contains control bits for enabling on of the two microphone inputs and data for setting the analogue microphone amplifier and earpiece amplifier gains.

| AG      | D7 | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|---------|----|------|------|------|------|------|------|------|

| Name    | 0  | ENM2 | ENM1 | AGX2 | AGX1 | AGX0 | AGR1 | AGR2 |

| Default | 0  | 0    | 0    | 0    | 1    | 0    | 0    | 0    |

| Bit No | Symbol | Name and    | Descript                                                                                                            | ion          |                        |  |  |  |  |  |  |  |

|--------|--------|-------------|---------------------------------------------------------------------------------------------------------------------|--------------|------------------------|--|--|--|--|--|--|--|

| D6     | ENM2   |             | nable Microphone 2 Input. When set to High the microphone amplifier is connected to<br>ne MIC2 + and MIC2 - inputs. |              |                        |  |  |  |  |  |  |  |

| D5     | ENM1   |             | nable Microphone 1 Input. When set to High the microphone amplifier is connected to<br>the MIC1+ and MIC1- inputs.  |              |                        |  |  |  |  |  |  |  |

| D4-D2  | AGX2   | Analogue 7  | nalogue Transmit Gain Setting (AGX).                                                                                |              |                        |  |  |  |  |  |  |  |

|        | -      | <u>AGX2</u> | <u>AGX1</u>                                                                                                         | <u>AGX0</u>  | Microphone Gain        |  |  |  |  |  |  |  |

|        | AGX0   | 0           | 0                                                                                                                   | 0            | +15.5 dB               |  |  |  |  |  |  |  |

|        |        | 0           | 0                                                                                                                   | 1            | +21.5 dB               |  |  |  |  |  |  |  |

|        |        | 0           | 1                                                                                                                   | 0            | +27.5 dB Default Value |  |  |  |  |  |  |  |

|        |        | 0           | 1                                                                                                                   | 1            | +33.5 dB               |  |  |  |  |  |  |  |

|        |        | 1           | 0                                                                                                                   | 0            | +39.5 dB               |  |  |  |  |  |  |  |

|        |        | 1           | 0                                                                                                                   | 1            | +45.5 dB               |  |  |  |  |  |  |  |

| D1- D0 | AGR1   | Analogue F  | Receive G                                                                                                           | ain Setting  | . (AGR).               |  |  |  |  |  |  |  |

|        | -      | AGR1        | <u>AGR0</u>                                                                                                         | <u>Earpi</u> | <u>ece Gain</u>        |  |  |  |  |  |  |  |

|        | AGR0   | 0           | 0                                                                                                                   | -12 dE       | B Default Value        |  |  |  |  |  |  |  |

|        |        | 0           | 1                                                                                                                   | -6 dE        | 3                      |  |  |  |  |  |  |  |

|        |        | 1           | 0                                                                                                                   | 0 dE         | 3                      |  |  |  |  |  |  |  |

|        |        | 1           | 1                                                                                                                   | +6 dE        | 3                      |  |  |  |  |  |  |  |

## 4) TRANSMIT DIGITAL GAIN REGISTER

This register contains the 8 bit coefficient for digital transmit gain setting.

| DGX     | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|---------|------|------|------|------|------|------|------|------|

| Name    | DGX7 | DGX6 | DGX5 | DGX4 | DGX3 | DGX2 | DGX1 | DGX0 |

| Default | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    |

| Bit No | Symbol        | Name and Des                                                                 | Name and Description                                                                                                   |                                                                     |                                                                                                               |  |  |  |  |

|--------|---------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D7-D0  | DGX7-<br>DGX0 | •                                                                            | SX,                                                                                                                    |                                                                     | 5                                                                                                             |  |  |  |  |

|        |               | <u>Coefficient</u><br>154<br>137<br>123<br>109<br>97<br>87<br>77<br>55<br>39 | <u>Transmit Gain</u><br>+6 dB<br>+5 dB<br>+4 dB<br>+3 dB (Default Value)<br>+2 dB<br>+1 dB<br>0 dB<br>- 3 dB<br>- 6 dB | <u>Coefficient</u><br>27<br>19<br>13<br>10<br>7<br>5<br>3<br>2<br>1 | <u>Transmit Gain</u><br>-9 dB<br>-12 dB<br>-15 dB<br>-18 dB<br>-21 dB<br>-24 dB<br>-28 dB<br>-32 dB<br>-38 dB |  |  |  |  |

## **5) SIDETONE GAIN REGISTER**

This register contains an 8 bit coeficient for a digital sidetone. The sidetone may be disabled by writing 00<sub>h</sub> into this register.

| SG      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name    | SG7 | SG6 | SG5 | SG4 | SG3 | SG2 | SG1 | SG0 |

| Default | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   |

| Bit No | Symbol  | Name and Description                                                                                                                                                                                                                                                  |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D0  | SG7-SG0 | Digital Sidetone Attenuation Control. An 8-bit coefficient written into this register allows to control the sidetone attenuation in the receive channel. The sidetone attenuation range is 0 dB to -48dB. The coefficient in decimal format for a given attenuaton is |

|        |         | calculated as: $(\frac{SG}{20})$<br>The sidetone default coefficient is 32 which corresponds to an attenuation of -18 dB.                                                                                                                                             |

## 6) RECEIVE DIGITAL GAIN REGISTER

This register contains an 8-bit coefficient for digital receive gain setting.

| DGR     | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|---------|------|------|------|------|------|------|------|------|

| Name    | DGR7 | DGR6 | DGR5 | DGR4 | DGR3 | DGR2 | DGR1 | DGR0 |

| Default | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    |

| Bit No | Symbol        | Name and Desc                           | Name and Description                                                                                                                                                                                                |                    |              |  |  |  |

|--------|---------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--|--|--|

| D7-D0  | DGR7-<br>DGR0 | to fine trim the re                     | Receive Digital Gain Setting (DGR). An 8-bit coefficient written into this register allows o fine trim the receive path gain from -42 to +6 dB. The coefficient in decimal format or a given gain is calculated as: |                    |              |  |  |  |

|        |               | $X = 127.7 \times 10^{(\underline{L})}$ | DGR<br>20                                                                                                                                                                                                           |                    |              |  |  |  |

|        |               | <u>Coefficient</u>                      | Receive Gain                                                                                                                                                                                                        | <b>Coefficient</b> | Receive Gain |  |  |  |

|        |               | 128                                     | 0 dB                                                                                                                                                                                                                | 23                 | -15 dB       |  |  |  |

|        |               | 114                                     | -1 dB                                                                                                                                                                                                               | 16                 | -18 dB       |  |  |  |

|        |               | 101                                     | -2 dB                                                                                                                                                                                                               | 11                 | -21 dB       |  |  |  |

|        |               | 90                                      | -3 dB (Default \                                                                                                                                                                                                    | /alue) 8           | -24 dB       |  |  |  |

|        |               | 81                                      | -4 dB                                                                                                                                                                                                               | 5                  | -27 dB       |  |  |  |

|        |               | 72                                      | -5 dB                                                                                                                                                                                                               | 4                  | -30 dB       |  |  |  |

|        |               | 64                                      | -6 dB                                                                                                                                                                                                               | 3                  | -33 dB       |  |  |  |

|        |               | 46                                      | -9 dB                                                                                                                                                                                                               | 2                  | -36 dB       |  |  |  |

|        |               | 32                                      | -12 dB                                                                                                                                                                                                              | 1                  | -42 dB       |  |  |  |

|        |               |                                         |                                                                                                                                                                                                                     |                    |              |  |  |  |

## 7) TONE CONTROL REGISTER

This register controls the various tone generator operation modes and the tone desstinations.

| тс      | D7    | D6    | D5    | D4 | D3            | D2    | D1           | D0    |

|---------|-------|-------|-------|----|---------------|-------|--------------|-------|

| Name    | TRINJ | RXINJ | TXINJ | CS | BURST<br>MODE | SHAPE | TONE<br>MODE | START |

| Default | 0     | 0     | 0     | 0  | 0             | 0     | 0            | 0     |

| Bit No | Symbol        | Name and Description                                                                                                                                                         |

|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7     | TRINJ         | Tone Ringer Inject. When set to High the tone generator is connected to the toneringer output. When set to Low the TRO+ and TRO- outputs are forced to high impedance state. |

| D6     | RXINJ         | Receive Inject. When set to High the tone generator is connected to the AS3502 receive section.                                                                              |

| D5     | TXINJ         | Transmit Inject. When set to High the tone generator is connected to the AS3502 transmit section.                                                                            |

| D4     | CS            | Cadence Slow Bit. When set to High the cadence step size resolution is 4 ms. When set to Low the cadence step size resolution is 1 ms.                                       |

| D3     | BURST<br>MODE | When set to High tone burst mode operation is selected.                                                                                                                      |

| D2     | SHAPE         | When set to High square wave mode is selected. When set to Low sine wave mode is selected                                                                                    |

| D1     | TONE<br>MODE  | Tone Mode Bit. When set to High dual tone mode is selected. When set to Low single tone mode is selected.                                                                    |

| D0     | START         | Start Melody. When set to High the tone generation is enabled. This bit acts as single byte on/off sequence.                                                                 |

## 8) SEQUENCE CONTROL REGISTER 1

This register contains the frequency codes for the first three steps of the six tone cadence.

| SC1     | D7 | D6 | D5              | D4  | D3  | D2  | D1              | D0  |

|---------|----|----|-----------------|-----|-----|-----|-----------------|-----|

| Name    | 0  | 0  | S3 <sub>1</sub> | S30 | S21 | S20 | S1 <sub>1</sub> | S10 |

| Default | 0  | 0  | х               | х   | х   | х   | х               | х   |

| Bit No | Symbol                            | Name and Description                        |  |  |  |

|--------|-----------------------------------|---------------------------------------------|--|--|--|

| D7, D6 | -                                 | Not used; will be low during read           |  |  |  |

| D5, D4 | S31, S30                          | Cadence Step 3:                             |  |  |  |

| -      |                                   | 00: No Tone                                 |  |  |  |

|        |                                   | 01: Frequency/Volume Register 1 is selected |  |  |  |

|        |                                   | 10: Frequency/Volume Register 2 is selected |  |  |  |

|        |                                   | 11: Frequency/Volume Register 3 is selected |  |  |  |

|        | S2 <sub>1</sub> , S2 <sub>0</sub> | Cadence Step 2                              |  |  |  |

|        |                                   | 00: No Tone                                 |  |  |  |

|        |                                   | 01: Frequency/Volume Register 1 is selected |  |  |  |

|        |                                   | 10: Frequency/Volume Register 2 is selected |  |  |  |

|        |                                   | 11: Frequency/Volume Register 3 is selected |  |  |  |

| D1, D0 | S1 <sub>1</sub> , S1 <sub>0</sub> | Cadence Step1                               |  |  |  |

|        |                                   | 00: No Tone                                 |  |  |  |

|        |                                   | 01: Frequency/Volume Register 1 is selected |  |  |  |

|        |                                   | 10: Frequency/Volume Register 2 is selected |  |  |  |

|        |                                   | 11: Frequency/Volume Register 3 is selected |  |  |  |

## 9) SEQUENCE CONTROL REGISTER 2

This register contains the frequency codes for the second three steps of the six tone cadence.

| SC2     | D7 | D6 | D5              | D4              | D3              | D2              | D1              | D0              |

|---------|----|----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Name    | 0  | 0  | S6 <sub>1</sub> | S6 <sub>0</sub> | S5 <sub>1</sub> | S5 <sub>0</sub> | S4 <sub>1</sub> | S4 <sub>0</sub> |

| Default | 0  | 0  | Х               | Х               | Х               | Х               | Х               | Х               |

| Bit No | Symbol                            | Name and Description                        |  |  |  |

|--------|-----------------------------------|---------------------------------------------|--|--|--|

| D7, D6 | -                                 | Not used; will be low during read           |  |  |  |

| D5, D4 | S61,S60                           | Cadence Step 6:                             |  |  |  |

|        |                                   | 00: No Tone                                 |  |  |  |

|        |                                   | 01: Frequency/Volume Register 1 is selected |  |  |  |

|        |                                   | 10: Frequency/Volume Register 2 is selected |  |  |  |

|        |                                   | 11: Frequency/Volume Register 3 is selected |  |  |  |

| D3, D2 | S5 <sub>1</sub> , S5 <sub>0</sub> | Cadence Step 5                              |  |  |  |

|        | _                                 | 00: No Tone                                 |  |  |  |

|        |                                   | 01: Frequency/Volume Register 1 is selected |  |  |  |

|        |                                   | 10: Frequency/Volume Register 2 is selected |  |  |  |

|        |                                   | 11: Frequency/Volume Register 3 is selected |  |  |  |

| D1, D0 | S4 <sub>1</sub> , S4 <sub>0</sub> | Cadence Step 4                              |  |  |  |

|        | _                                 | 00: No Tone                                 |  |  |  |

|        |                                   | 01: Frequency/Volume Register 1 is selected |  |  |  |

|        |                                   | 10: Frequency/Volume Register 2 is selected |  |  |  |

|        |                                   | 11: Frequency/Volume Register 3 is selected |  |  |  |

## **10) FREQUENCY CONTROL REGISTER 1**

This register contains eight bits of the 10-bit coefficient of the first frequency.

| F1      | D7  | D6  | D5  | D4  | D3  | D2  | D1              | D0  |

|---------|-----|-----|-----|-----|-----|-----|-----------------|-----|

| Name    | F17 | F16 | F15 | F14 | F13 | F12 | F1 <sub>1</sub> | F10 |

| Default | Х   | Х   | Х   | Х   | Х   | Х   | Х               | Х   |

| Bit No | Symbol  | Name and Description                                                                                                                                                                                                                                         |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D0  | F17-F10 | A 10-bit coefficient (X) written into this register and into bits D0 and D1 of V1 allows to programme the first frequency from 3.9 Hz to 3996 Hz. The coefficient for a given frequency can be calculated as:<br>$X = \frac{f(Hz)^* 256}{1000}; X = (11023)$ |

## 11) VOLUME CONTROL REGISTER 1

This register contains the remaining two bits of the first frequency coefficient and volume control data for pulse density volume control of square waves.

| V1      | D7 | D6  | D5  | D4  | D3              | D2              | D1  | D0  |

|---------|----|-----|-----|-----|-----------------|-----------------|-----|-----|

| Name    | 0  | V14 | V13 | V12 | V1 <sub>1</sub> | V1 <sub>0</sub> | F19 | F18 |

| Default | Х  | Х   | Х   | Х   | Х               | Х               | Х   | Х   |

| Bit No | Symbol  | Name and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D6-D2  | V14-V10 | A 5 bit coefficient (X) written into this register allows to programme both the tone ringer attenuation in pulse density mode and the attenuation of the tone generator in square wave mode. The coefficient in decimal format for a given attenuation can be calculated as:<br>$X = 31*10^{\circ}(\frac{Volume(dB)}{20}); X = (131)$ $VOUT = 2*VDD*10^{\circ}(\frac{V1}{20}) (V)$ In tone generator square wave mode a 4-bit coefficient using bits V13 to V10 allows to programme the volume where coefficient in decimal format for a given volume can be calculated as:<br>$X = 16*10^{\circ}(\frac{Volume(dB)}{20}); X = (015)$ In receive direction the absolute output value on the speaker and earpiece outputs depends on AGR and V2.<br>VOUTEP = 6.14  dBm + V2C + V1 + AGR  (dBm) In transmit direction the output value depends on V1 and DGX. |

|        | F19-F18 | VOUT = 6.14 dBm0 + V1 + DGX (dBm0)<br>These bits are the two most significant bits of the 10-bit frequency coefficient.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 12) FREQUENCY CONTROL REGISTER 2

This register contains eight bits of the 10-bit coefficient of the second frequency.

| F2      | D7  | D6  | D5  | D4  | D3  | D2              | D1  | D0  |

|---------|-----|-----|-----|-----|-----|-----------------|-----|-----|

| Name    | F27 | F26 | F25 | F24 | F23 | F2 <sub>2</sub> | F21 | F20 |

| Default | Х   | х   | Х   | х   | Х   | х               | Х   | Х   |