#### **Features**

- All-in-one Design

- MIDI Control Processor

- Synthesis

- Compatible Effects: Reverb and Chorus

- Microphone Echo Processing (Two Channels)

- Programmable Spatial Effect or Four-channel Surround

- 4-band Stereo Equalizer

- · High-quality Synthesis

- Maximum 48-voice Polyphony and Reverb/Chorus (34 if all Features on)

- 24 dB Resonant Filter per Voice

- 16-bit Samples

- Alternate Loop

- Internal Computations on 28 Bits

- Crisp MIDI Response: Built-in 16-bit Processor Runs at 38.4 MHz

- High-quality Sound Post-processing

- 13 Delay Lines for Stereo Reverb

- Programmable Stereo Echo for Microphone

- Spatial Effect/Surround Allows Wide Stereo Image for Strong Sound Presence

- Top Technology

- Synthesizer Chip Set: ATSAM9703 + 32-Mbit ROM + 32K x 8 RAM + DAC or Codec

- Single 9.6 MHz Crystal with Built-in PLL

- 100-lead TQFP Space Saver Package

- Standard Firmware includes Top-quality CleanWave<sup>™</sup> Sound Set and Other Sample Sets under Special Conditions

- Typical Applications: Karaokes, Musical instruments, Battery-operated Instruments

- Pin- and Function-compatible with ATSAM9503, with Additional Features:

- Lower Consumption

- 3.3V Core Supply, 3V to 5.5V Periphery Supply

- Up to 8 Channels Audio-in

Note: Pin-to-pin replacement for ATSAM9503 requires 3.3V core supply V<sub>C3</sub>.

## **Description**

The highly-integrated architecture of the ATSAM9703 device combines a specialized high-performance RISC digital signal processor and a general-purpose 16-bit CISC control processor on a single chip. An on-chip memory management unit allows the digital signal processor and the control processor to share external ROM and RAM devices. The ROM bus width should be 16 bits, while the SRAM can be selected to be 8 or 16 bits wide. When using an 8-bit SRAM, fast type (static cache) should be selected as two SRAM cycles will be done in one ROM cycle duration.

Running at 300 million operations per second (MOPS), the digital signal processor supports high-quality PCM synthesis as well as most important functions like reverb, chorus, surround effect and equalizer. By adding an additional stereo DAC, four-channel audio surround can be obtained as well.

Computer Karaoke manufacturers will enjoy the built-in high-quality dual-microphone echo processing.

Dream<sup>®</sup> licenses a 32-Mbit jumper-configurable firmware ROM, CleanWave32<sup>™</sup>, which includes high-quality General MIDI-compliant synthesis with many additional sounds and drumsets. Please refer to the corresponding CleanWave32 datasheet. Other sample sets are available under special conditions.

More information, including licensing, can be obtained from any Atmel sales office.

Smaller capacity firmware is also available for more cost-sensitive or portable applications.

# Sound Synthesis

# ATSAM9703 Professional Integrated Synthesizer

Bev 1710C-DBMSD-12/02

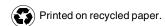

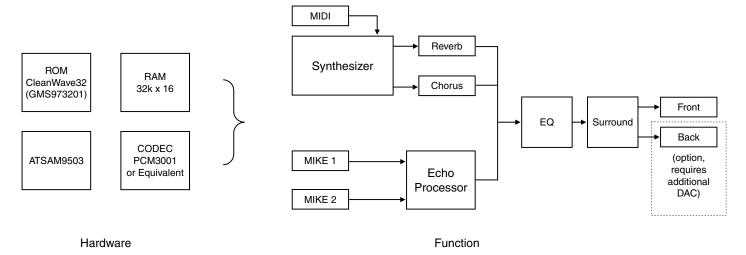

#### ATSAM9703 Configuration

The firmware can also be modified to fit customer specifications. An ATSAM9703-based development/prototyping board is available and includes the ATSAM9703, 32 Mbits of EPROM memory, 32K words of SRAM, a codec and one DAC, providing four channels of audio Out and a stereo line input (ref. 9703DVB).

The ATSAM9703 internal sound definition format is compatible with the ATSAM9407 sound studio IC. Therefore it is possible to develop specific sounds for the ATSAM9703 by using the development tools of the ATSAM9407.

The ATSAM9703 operates from a "low" frequency 9.6 MHz typical crystal. A built-in PLL raises this frequency to a 38.4 MHz internal clock which controls the two processors. Care has been taken that Output pin signals change only when necessary. This minimizes RFI (radio frequency interferences) and power consumption. Minimizing RFI is mostly important in order to comply with standards such as FCC, CSA and CE.

The core power supply for the ATSAM9703 should be  $3.3V \pm 10\%$ , while the periphery supports supply from 3V to 5.5V (5V  $\pm$  10% for TTL-compatible applications). Therefore, by selecting 3.3V ROM, SRAM and DAC, it is possible to develop low-power/low-voltage portable applications.

Figure 1. Typical Hardware Configuration

# **Pin Description**

## **Pins by Function**

Table 1. Power Supply Group

| Pin Name | Pin Number                                                          | Туре | Function                                                                                                                                                                   |

|----------|---------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | 2, 6, 8, 16, 20, 22, 26, 28, 38, 46, 49, 53, 59, 71, 75, 82, 83, 94 | PWR  | Digital Ground All pins should be connected to a ground plane.                                                                                                             |

| vcc      | 1, 7, 15, 21, 27, 37,<br>48, 52, 58, 70, 74, 81,<br>95              | PWR  | Power Supply, 3V to 5.5V All pins should be connected to a VCC plane.                                                                                                      |

| VC3      | 9, 19, 24, 77                                                       | PWR  | Core Power Supply, $3.3V \pm 10\%$ . All pins should be connected to $+3.3V$ . If $3.3V$ is not available, then it can be derived from 5V by two 1N41418 diodes in series. |

#### Table 2. Serial MIDI

| Pin Name | Pin Number | Туре | Function                                                   |

|----------|------------|------|------------------------------------------------------------|

| MIDI IN  | 17         | IN   | Serial TTL MIDI IN. All controls are received by this pin. |

#### Table 3. External ROM/RAM Group

| Pin Name | Pin Number                                                      | Туре | Function                                                                                                                                                           |

|----------|-----------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WA[24:0] | 47, 50, 51, 54 - 57,<br>60 - 69, 72, 73, 76,<br>78 - 80, 84, 85 | OUT  | External ROM/RAM address for up to 32M words (64 MB) of memory. ROM memory holds firmware and PCM data. RAM memory holds working variables and effect delay lines. |

| WD[15:0] | 86 - 93, 96 -100, 3 - 5                                         | I/O  | External ROM/RAM data. Holds read data from ROM or RAM when $\overline{\text{WOE}}$ is low, write data to RAM when $\overline{\text{WWE}}$ is low.                 |

| WCS0     | 34                                                              | OUT  | External ROM chip select, active low.                                                                                                                              |

| WCS1     | 35                                                              | OUT  | External RAM chip select, active low.                                                                                                                              |

| WOE      | 36                                                              | OUT  | External ROM/RAM Output enable, active low.                                                                                                                        |

| WWE      | 33                                                              | OUT  | External RAM write, active low                                                                                                                                     |

| RBS      | 25                                                              | OUT  | RAM byte select. Used as lower address from RAM when 8-bit wide RAM is connected.                                                                                  |

#### Table 4. Digital Audio Group

| Pin Name | Pin Number | Туре | Function                                                                                                                            |  |  |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLBD     | 23         | OUT  | Digital audio bit clock                                                                                                             |  |  |

| WSBD     | 32         | OUT  | Digital audio left/right select                                                                                                     |  |  |

| DABD0    | 30         | OUT  | Digital audio main stereo Output                                                                                                    |  |  |

| DABD1    | 31         | OUT  | Auxiliary digital stereo Output. Reserved for surround effects.                                                                     |  |  |

| DAAD     | 29         | IN   | Digital audio two channels input. Up to eight channels of audio can be input to the chip by using pins P1 to P3 alternate function. |  |  |

Table 5. Miscellaneous Group

| Pin Name  | Pin Number     | Туре | Function                                                                                                                                                                                         |  |  |  |

|-----------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| X1<br>X2  | 12, 11         | _    | 9.6 MHz crystal connection. An external 9.6 MHz clock can also be used on X1 (3.3V input). X2 cannot be used to drive external circuits.                                                         |  |  |  |

| LFT       | 10             | _    | PLL external RC network.                                                                                                                                                                         |  |  |  |

| RESET     | 13             | IN   | Reset input, active low. This is a Schmidt trigger input, allowing direct connection of an RC network.                                                                                           |  |  |  |

| PDWN      | 14             | IN   | Power down, active low. When power down is active, then all Output pins will be floated. The crystal oscillator will be stopped. To exit from power down, PDWN should be high and RESET applied. |  |  |  |

| TEST[2:0] | 43, 44, 45     | IN   | Test pins. Should be grounded.                                                                                                                                                                   |  |  |  |

| P[3:0]    | 39, 40, 41, 42 | I/O  | General-purpose I/O pins. As inputs, can be used to configure the software. P1 to P3 can also be used as three additional stereo serial inputs (six audio channels).                             |  |  |  |

| RUN       | 18             | OUT  | When high, indicates that the synthesizer is up and running. May be used as a RESET input for an external DAC.                                                                                   |  |  |  |

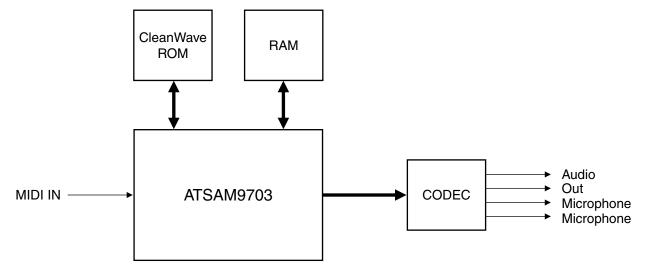

#### **Pinout**

Figure 2. ATSAM9703 Pinout in 100-lead TQFP Package

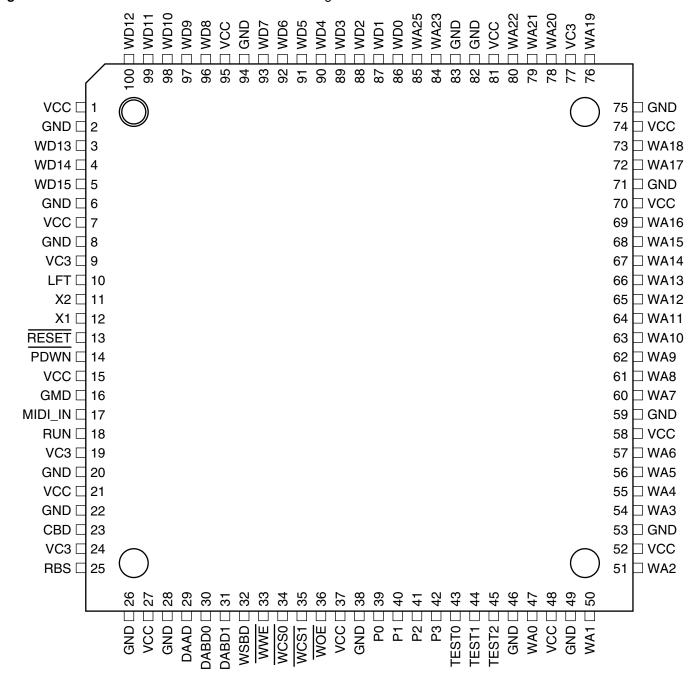

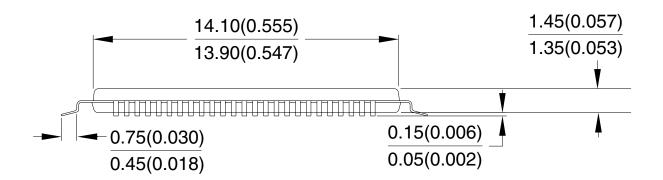

# Mechanical Dimensions

Figure 3. 100-lead Thin Plastic Quad Flat Pack

# **Absolute Maximum Ratings**

Table 6. Absolute Maximum Ratings

| Ambient Temperature (Power Applied)40°C to + 85°C            | *NOTICE: Stresses beyond those listed under "Absolute<br>Maximum Ratings" may cause permanent dam-     |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to + 160°C                           | age to the device. This is a stress rating only and functional operation of the device at these or any |

| Voltage on any pin (except X1)0.5V to V <sub>CC</sub> + 0.5V | other conditions beyond those indicated in the operational sections of this specification is not       |

| Supply Voltage0.5V to + 6.5V                                 | implied. Exposure to absolute maximum rating                                                           |

| V <sub>C3</sub> Supply Voltage0.5V t0 +4.5V                  | condtions for extended periods may affect device reliability.                                          |

| Maximum IOL per I/O pin10mA                                  |                                                                                                        |

Note: All voltages with respect to 0V, GND = 0V)

# Recommended Operating Conditions

Table 7. Recommended Operating Conditions

| Symbol          | Parameter/Condition           | Min | Тур     | Max | Unit |

|-----------------|-------------------------------|-----|---------|-----|------|

| V <sub>CC</sub> | Supply Voltage <sup>(1)</sup> | 3   | 3.3/5.0 | 5.5 | V    |

| V <sub>C3</sub> | Supply Voltage                | 3   | 3.3     | 3.6 | V    |

| T <sub>A</sub>  | Operating Ambient Temperature | 0   |         | 70  | °C   |

Note: 1. When using 3.3V supply in a 5V environment, care must be taken that pin voltage does not exceed  $V_{CC} + 0.5V$ .

#### **DC Characteristics**

**Table 8.** DC Characteristics ( $T_A = 25^{\circ}C$ ,  $V_{C3} = 3.3V \pm 10\%$ )

| Symbol          | Parameter/Condition                                  | vcc        | Min          | Тур      | Max                    | Unit     |

|-----------------|------------------------------------------------------|------------|--------------|----------|------------------------|----------|

| V <sub>IL</sub> | Low Level Input Voltage                              | 3.3<br>5.0 | -0.5<br>-0.5 |          | 1.0<br>1.7             | V<br>V   |

| V <sub>IH</sub> | High Level Input Voltage                             | 3.3<br>5.0 | 2.3<br>3.3   |          | VCC + 0.5<br>VCC + 0.5 | V<br>V   |

| V <sub>OL</sub> | Low Level Output Voltage (I <sub>OL</sub> = -3.2 mA) | 3.3<br>5.0 |              |          | 0.45<br>0.45           | V<br>V   |

| V <sub>OH</sub> | High Level Output Voltage (I <sub>OH</sub> = 0.8 mA) | 3.3<br>5.0 | 2.8<br>4.5   |          |                        | V<br>V   |

| I <sub>cc</sub> | Power Supply Current (Crystal Freq. = 9.6 MHz)       | 3.3<br>5.0 |              | 70<br>25 | 90<br>35               | mA<br>mA |

|                 | Power Down Supply Current                            |            |              | 70       | 100                    | μA       |

# **Timings**

All timing conditions:  $T_A$  = 25°C,  $V_{CC}$  = 5V,  $V_C$  = 3.3V, all Outputs exept X2 and LFT load capacitance = 30 pF, crystal frequency or external clock at X1 = 9.6 MHz.

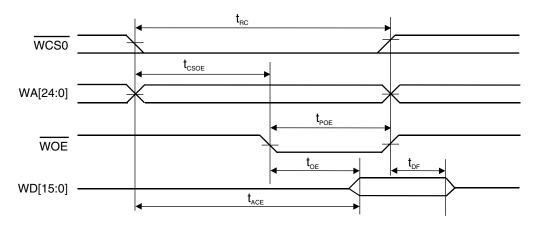

## **External ROM Timing**

Figure 4. ROM Read Cycle

Table 9. Timing Parameters

| Symbol            | Parameter                                    | Min | Тур | Max | Unit |

|-------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>RC</sub>   | Read Cycle Time                              | 130 |     |     | ns   |

| t <sub>CSOE</sub> | Chip Select Low/Address Valid to WOE low     | 45  |     | 80  | ns   |

| t <sub>POE</sub>  | Output Enable Pulse Width                    |     | 78  |     | ns   |

| t <sub>ACE</sub>  | Chip Select/Address Access Time              | 125 |     |     | ns   |

| t <sub>OE</sub>   | Output Enable Access Time                    | 70  |     |     | ns   |

| t <sub>DF</sub>   | Chip select or WOE High to Input Data High-Z | 0   |     | 50  | ns   |

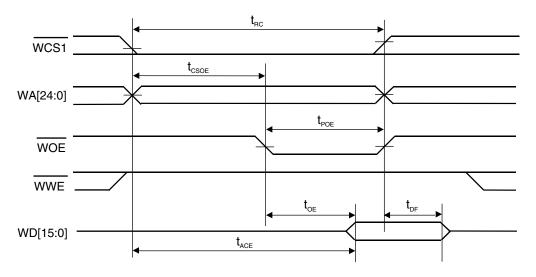

## **External RAM Timing**

Figure 5. 16-bit SRAM Read Cycle

WCS1

WA[24:0]

WOE

WWE

WD[15:0]

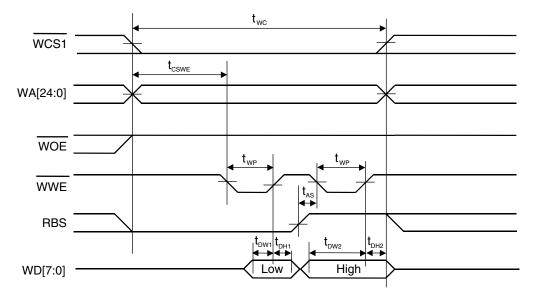

Figure 6. 16-bit SRAM Write Cycle

Table 10.

Timing Parameters

| Symbol            | Parameter                                                                          | Min | Тур | Max | Unit |

|-------------------|------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>RC</sub>   | Read Cycle Time                                                                    | 130 |     |     | ns   |

| t <sub>CSOE</sub> | Chip Select Low/Address Valid to WOE Low                                           | 45  |     | 80  | ns   |

| t <sub>POE</sub>  | Output Enable Pulse Width                                                          |     | 78  |     | ns   |

| t <sub>ACE</sub>  | Chip Select/Address Access Time                                                    | 125 |     |     | ns   |

| t <sub>OE</sub>   | Output Enable Access Time                                                          | 70  |     |     | ns   |

| t <sub>DF</sub>   | Chip Select or WOE High to Input Data High-Z                                       | 0   |     | 50  | ns   |

| t <sub>wc</sub>   | Write Cycle Time                                                                   | 130 |     |     | ns   |

| t <sub>CSWE</sub> | Write enable Low from $\overline{\text{CS}}$ or Address or $\overline{\text{WOE}}$ | 40  |     |     | ns   |

| t <sub>WP</sub>   | Write Pulse Width                                                                  |     | 104 |     | ns   |

| t <sub>DW</sub>   | Data Out Setup Time                                                                | 95  |     |     | ns   |

| t <sub>DH</sub>   | Data Out Hold Time                                                                 | 10  |     |     | ns   |

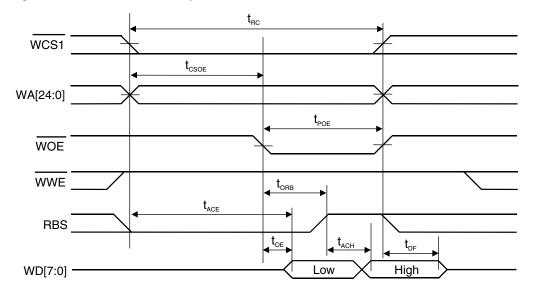

Figure 7. 8-bit SRAM Read Cycle

Figure 8. 8-bit SRAM Write Cycle

Table 11. Timing Parameters

| Symbol            | Parameter                                | Min | Тур | Max | Unit |

|-------------------|------------------------------------------|-----|-----|-----|------|

| t <sub>RC</sub>   | Word Read Cycle Time                     | 130 |     |     | ns   |

| t <sub>CSOE</sub> | Chip Select Low/Address Valid to WOE Low | 45  |     | 80  | ns   |

| t <sub>POE</sub>  | Output Enable Pulse Width                |     | 78  |     | ns   |

| t <sub>ACE</sub>  | Chip Select/Address Low Byte Access Time | 70  |     |     | ns   |

| t <sub>OE</sub>   | Output Enable Low Byte Access Time       | 20  |     |     | ns   |

Table 11. Timing Parameters (Continued)

| Symbol            | Parameter                               | Min | Тур | Max | Unit |

|-------------------|-----------------------------------------|-----|-----|-----|------|

| t <sub>ORB</sub>  | Output Enable Low Byte Select High      |     | 26  |     | ns   |

| t <sub>ACH</sub>  | Byte Select High Byte access Time       | 45  |     |     | ns   |

| t <sub>DF</sub>   | Chip select or WOE High to Input High-Z | 0   |     | 50  | ns   |

| t <sub>WC</sub>   | Word Write Cycle Time                   | 130 |     |     | ns   |

| t <sub>CSWE</sub> | 1st WWE Low from CS or Address or WOE   | 40  |     |     | ns   |

| $t_{WP}$          | Write (Low and High Byte) Pulse Width   | 20  |     |     | ns   |

| t <sub>DW1</sub>  | Data Out Low Byte Setup Time            | 25  |     |     | ns   |

| t <sub>DH1</sub>  | Data Out Low Byte Hold Time             | 20  |     |     | ns   |

| t <sub>AS</sub>   | RBS High to Second Write Pulse          | 8   |     |     | ns   |

| t <sub>DW</sub>   | Data Out High Byte Setup Time           | 40  |     |     | ns   |

| t <sub>DH2</sub>  | Data Out High Byte Hold Time            | 10  |     |     | ns   |

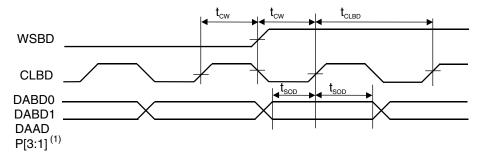

## **Digital Audio**

Figure 9. Digital Audio Timing

Note: 1. When used as alternate audio in.

Table 12. Timing Parameters

| Symbol            | Parameter                          | Min | Тур    | Max | Unit |

|-------------------|------------------------------------|-----|--------|-----|------|

| t <sub>CW</sub>   | CLBD Rising to WSBD Change         | 200 |        |     | ns   |

| t <sub>SOD</sub>  | DABD Valid Prior/After CLBD Rising | 200 |        |     | ns   |

| t <sub>CLBD</sub> | CLBD Cycle Time                    |     | 416.67 |     | ns   |

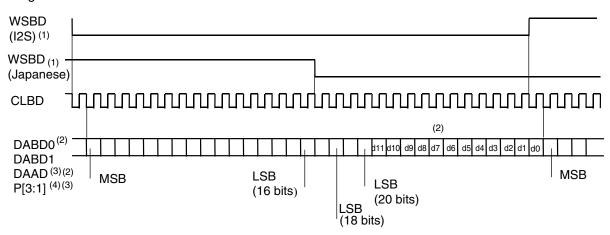

## **Digital Audio Frame**

Figure 10. Digital Audio Frame Format

Notes: 1. Selection between I2S and Japanese format is a firmware option.

- 2. When connected to codecs such as CS4216 or CS4218, D[11:0] can be used to hold independent auxiliary information on left and right words. Refer to the corresponding codec data sheets for details. Auxiliary information is available on DABD0 and DAAD.

- 3. DAAD, P[3:1] are 16 bits only.

- 4. When used as an alternate audio in.

#### Reset and Power-down

During power-up, the RESET input should be held low until the crystal oscillator and PLL are stabilized, which can take abOut 20 ms. A typical RC/diode power-up network can be used.

After the low-to-high transition of RESET, the following occurs:

- The synthesis enters an idle state.

- The RUN Output is set to zero.

- Firmware execution starts from address 0100H in ROM space (WCSO low).

If PDWN is asserted low, then all I/Os and Outputs will be floated and the crystal oscillator and PLL will be stopped. The chip enters a deep power-down sleep mode. To exit power-down, PDWN has to be asserted high, then RESET applied.

# Recommended Board Layout

As for all HCMOS high-integration ICs, some rules of board layout should be followed for reliable operation:

GND, V<sub>CC</sub>, V<sub>C3</sub> distribution, decouplings

All GND,  $V_{CC}$ ,  $V_{C3}$  pins should be connected. GND +  $V_{CC}$  planes are strongly recommended below the ATSAM9703. The board GND +  $V_{CC}$  distribution should be in grid form. For 5V  $V_{CC}$  operation, if 3.3V is not available, then  $V_{C3}$  can be connected to  $V_{CC}$  by two 1N4148 diodes in serial. This guarantees a minimum voltage drop of 1.2V.

Recommended  $V_{CC}$  decoupling is 0.1  $\mu F$  at each corner of the IC with an additional 10  $\mu F$  decoupling close to the crystal.  $V_{C3}$  requires a single 0.1  $\mu F$  decoupling close to the IC.

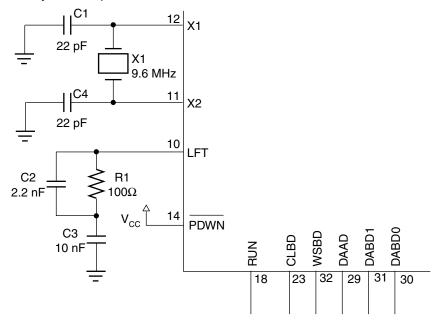

Crystal, LFT

The paths between the crystal, the crystal compensation capacitors, the LFT filter R-C-R and the ATSAM9703 should be short and shielded. The ground return from the compensation capacitors and LFT filter should be the GND plane from ATSAM9703.

Analog Section

A specific AGND ground plane should be provided, which connects by a single trace to the GND ground. No digital signals should cross the AGND plane. Refer to the codec vendor recommended layOut for correct implementation of the analog section.

Unused Inputs

Unused inputs should always be connected. A floating input can cause internal oscillation inside the IC, which can destroy the device by dramatically increasing the power consumption. If the power-down feature is to be used, care should be taken that no pin is left floating during power down. Usually, a 1  $M\Omega$  ground return is sufficient.

# Recommended Crystal Compensation and LFT Filter

Figure 11. Crystal Compensation and LFT Filter

Note: The X2 Output cannot be used to drive another circuit.

# CleanWave32<sup>™</sup> ROM Firmware (Ref. GMS973201)

- ROM includes Firmware and PCM Data

- Full GM implementation with Top-quality Additional Sounds

- 128 General MIDI Sounds

- 189 Variation Sounds including Sound Effects

- 9 Drum Sets + 1 SFX Set

- Powerful MIDI implementation

- Built-in Compatible Reverb and Chorus

- Built-in Four-band Parametric Equalizer, Fully Controllable by MIDI

- Built-in Spatial Effect with MIDI Control

- Microphone Echo Processing

Figure 12. CleanWave 32 ROM Firmware Description

For detailed information about sound list and MIDI implementation, please request the CleanWave32 user's manual.

# Reference Design ATSAM9703DVB

ATSAM9703 + 2 x 16-Mbit EPROMs + 2 x 32k x 8 SRAMs + Codec + DAC

ATSAM9703DVB can be used for CleanWave32 evaluation or other specific applications requiring not more than 4 Mb of PCM data.

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and Dream® are the registered trademarks of Atmel; CleanWave32™ is the trademark of Atmel.

Other terms and product names may be the trademarks of others.