DATA SHEET

# MB87001A CMOS PLL FREQUENCY SYNTHESIZER

#### CMOS SERIAL INPUT PHASE-LOCKED-LOOP (PLL) FREQUENCY SYNTHESIZER

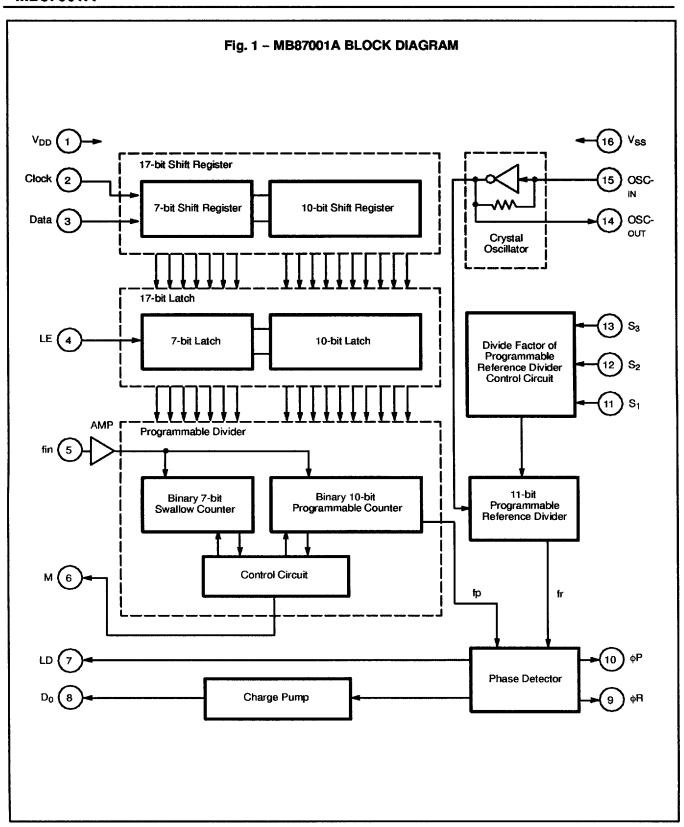

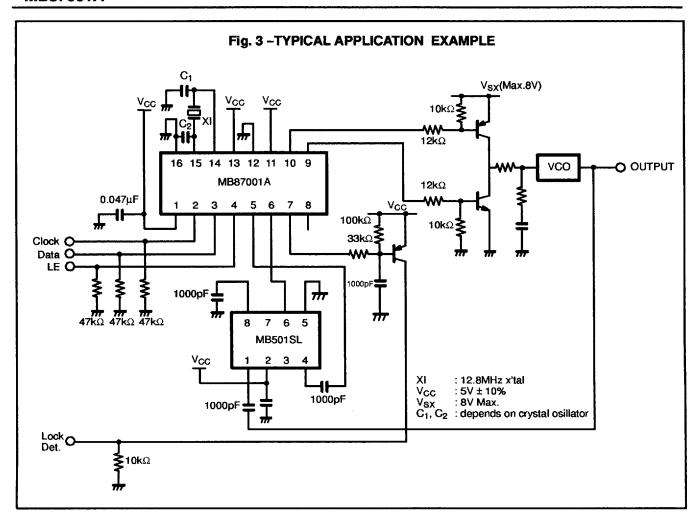

The Fujitsu MB87001A, fabricated in CMOS technology, is a serial input PLL frequency synthesizer.

The MB87001A contains an inverter for connection to an external oscillator, a programmable reference divider, a divide factor of programmable reference divider control circuit, a phase detector, a charge pump, a 17-bit shift register, a 17-bit latch, a programmable divider (a binary 7-bit swallow counter, a binary 10-bit programmable counter), and a control generator for an external dual modulus prescaler.

When supplemented with a loop filter and VCO, the MB87001A contains the necessary circuitry to make up a Phase Locked Loop (PLL). Typically, a dual modulus prescaler such as the MB501L can be added, allowing input frequency operation up to 1.1 GHz.

- Single power supply voltage:

V<sub>DD</sub> = 2.7V to 5.5V

- Wide temperature range:

T<sub>A</sub> = -40 to 85°C

- 13MHz typical input capability

@5V (fin input)

- On-chip inverter for oscillator

- 8 divide factors for programmable reference divider is selected by S<sub>1</sub>,

S<sub>2</sub> and S<sub>3</sub> input (1/8, 1/16, 1/64, 1/128, 1/256, 1/512, 1/1024, 1/2048)

- Programmable 17-bit divider with input amplifier consisting of: Binary 7-bit swallow counter Binary 10-bit programmable counter

- 2 type of phase detector output On-chip charge pump output Output for external charge pump

- Easy interface to Fujitsu dual modulus prescaler

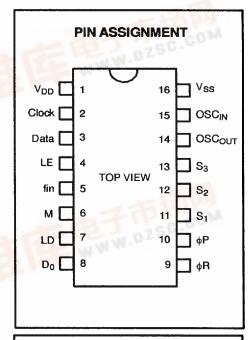

# PLASTIC PACKAGE DIP-16P-M04 PLASTIC PACKAGE FPT-16P-M06

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### ABSOLUTE MAXIMUM RATINGS (see NOTE)

$(V_{SS} = 0V)$

| Rating                | Symbol           | Value                                        | Unit |

|-----------------------|------------------|----------------------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | V <sub>SS</sub> -0.5 to V <sub>SS</sub> +7.0 | ٧    |

| Input Voltage .       | V <sub>IN</sub>  | V <sub>SS</sub> -0.5 to V <sub>DD</sub> +0.5 | ٧    |

| Output Voltage        | V <sub>ОИТ</sub> | V <sub>SS</sub> -0.5 to V <sub>DD</sub> +0.5 | ٧    |

| Output Current        | lout             | ±10                                          | mA   |

| Open-drain Output     | V <sub>OOP</sub> | V <sub>SS</sub> -0.5 to V <sub>DD</sub> +3.0 | ٧    |

| Operating Temperature | TA               | -40 to +85                                   | °C   |

| Storage Temperature   | T <sub>STG</sub> | -65 to +150                                  | °C   |

| Power Dissipation     | PD               | 300                                          | mW   |

NOTE:

Permanent device damage may occur if the above **Absolute Maximum Ratings** are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

opyright ©1995 by FUJITSU LIMITED and FUJITSU MICROELECTRONICS, INC.

# **PIN DESCRIPTION**

| Pin No. | Symbol          | VO | Description                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub> | -  | Power supply voltage input.                                                                                                                                                                                                                                                                                                                               |

| 2       | Clock           | 1  | Clock signal input for 17-bit shift register.<br>Each rising edge of the clock shifts one bit of the data into the shifter register.                                                                                                                                                                                                                      |

| 3       | Data            | l  | Serial data input for 17-bit shift register. The data is used for setting the divide factor of programmable divider.                                                                                                                                                                                                                                      |

| 4       | LË              | -  | Load enable input.<br>When this pin is high level (high active), the data stored in the 17-bit shift register is transferred to 17-bit<br>latch.                                                                                                                                                                                                          |

| 5       | fin             | 1  | Input for programmable divider from VCO or prescaler output. This input involves bias circuit and amplifier. The connection with external dual modulus prescaler should be an AC connection.                                                                                                                                                              |

| 6       | М               | 0  | Control output for external dual modulus prescaler.  The connection to the prescaler should be DC connection. This output level is synchronized with falling edge of fin input signal (pin #5).  Pulse Swallow Function:  MB501L                                                                                                                          |

| 7       | LD              | o  | Output of phase detector.<br>It is high level when fr and fp are equal, and then the loop is locked. Otherwise it outputs negative pulse<br>signal.                                                                                                                                                                                                       |

| 8       | Do              | 0  | Three-state charge pump output of the phase detector. The mode of $D_O$ is changed by the combination of programmable reference divider output frequency fr and programmable divider output frequency fp as listed below: fr > fp: Drive mode ( $D_O$ = High level) fr = fp: High-impedance mode fr < fp: Sink mode ( $D_O$ = Low level)                  |

| 9<br>10 | φR<br>φР        | 0  | Phase detector outputs for an external charge pump.  The mode of φR and φP are changed by the combination of programmable reference divider output frequency fr and programmable divider output frequency fp as listed below:  φR φP  fr > fp: Low Low  fr ≈ fp: Low High-Impedance  fr < fp: High High-Impedance  * φP is a N-channel open drain output. |

# PIN DESCRIPTION (Continued)

| Pin No.        | Symbol                                             | VO |                                                                                                                                                      | Description                                                                                                                                                                                                                                                                       |                |          |                 |                 |                 |            |            |        |

|----------------|----------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-----------------|-----------------|-----------------|------------|------------|--------|

| 11<br>12<br>13 | S <sub>1</sub><br>S <sub>2</sub><br>S <sub>3</sub> |    | Control input for programmable reference divider. The combination of these inputs provides 8 k divide factor for the programmable reference divider. |                                                                                                                                                                                                                                                                                   |                |          |                 |                 |                 |            | ides 8 kir | nds of |

|                |                                                    |    | Divide<br>Factor<br>Sn                                                                                                                               | 1 8                                                                                                                                                                                                                                                                               | <u>1</u><br>16 | 1<br>64  | <u>1</u><br>128 | <u>1</u><br>256 | <u>1</u><br>512 | 1<br>1024  | 1<br>2048  |        |

|                |                                                    |    | S <sub>1</sub>                                                                                                                                       | 0                                                                                                                                                                                                                                                                                 | 1              | 0        | 1               | 0               | 1               | 0          | 1          |        |

|                |                                                    |    | S <sub>2</sub>                                                                                                                                       | 0                                                                                                                                                                                                                                                                                 | 0              | 1        | 1               | 0               | 0               | 1          | 1          |        |

|                |                                                    |    | S <sub>3</sub>                                                                                                                                       | 0                                                                                                                                                                                                                                                                                 | 0              | 0        | 0               | 1               | 1               | 1          | 1          |        |

| 14             | OSC <sub>OUT</sub>                                 | 0  | Output pin for crystal<br>Output of the inverting                                                                                                    |                                                                                                                                                                                                                                                                                   |                | n should | be open v       | when an         | external (      | oscillator | is used.   |        |

| 15             | OSCIN                                              | I  | Input to the inverting a<br>AC coupled when an                                                                                                       | Input pin for crystal oscillator. Input to the inverting amplifier that forms part of the oscillator. This pin receives the oscillator signal as AC coupled when an external oscillator is used. For large amplitude signals (standard CMOS levels) DC coupling may also be used. |                |          |                 |                 |                 |            |            |        |

| 16             | V <sub>SS</sub>                                    |    | Ground                                                                                                                                               |                                                                                                                                                                                                                                                                                   |                |          |                 |                 |                 |            |            |        |

### **FUNCTIONAL DESCRIPTION**

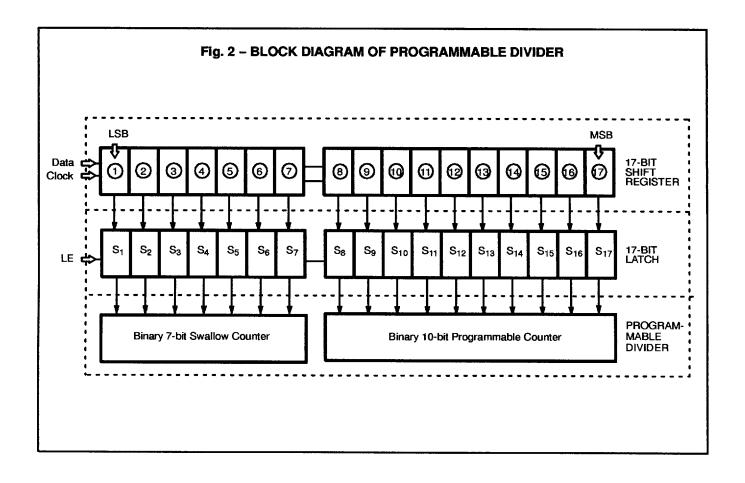

#### **DIVIDE FACTOR OF PROGRAMMABLE DIVIDER**

Serial data of binary code is input to Data pin. These data are loaded into the 17-bit shift register from MSB. When load enable signal LE is high, the data stored in the 17-bit shift register is transferred to the 17-bit latch.

The data 1) to 7) set a divide factor of the binary 7-bit swallow counter and data 8) to 7) set a divide factor of binary 10-bit programmable counter. In other words, serial data is equivalent to the divide factor of programmable divider.

#### MB87001A

#### Binary 7-bit Swallow Counter Data Input

| 0 | <b>©</b> | (5) | 4 | 3 | 2 | 0 | Divide<br>Factor A |

|---|----------|-----|---|---|---|---|--------------------|

| 0 | 0        | 0   | 0 | 0 | 0 | 0 | 0                  |

| 0 | 0        | 0   | 0 | 0 | 0 | 1 | 1                  |

| 0 | 0        | 0   | 0 | 0 | 1 | 0 | 2                  |

| 0 | 0        | 0   | 0 | 0 | 1 | 1 | 3                  |

| 0 | 0        | 0   | 0 | 1 | 0 | 0 | 4                  |

|   | •        |     |   |   |   |   |                    |

| 1 | 1        | 1   | 1 | 1 | 1 | 1 | 127                |

Note: Divide factor A: 0 to 127

Depending upon the divide factor set input (SW) of external prescaler, the input data should be as follows. Example MB501L

SW = H (64/65): Bit 7 of shift register (7) should be zero.

#### Binary 10-bit Programmable Counter Data Input

| 0 | <b>©</b> | <b>(5)</b> | 4 | <b>®</b> | 129 | <b>①</b> | 9 | 9 | 8 | Divide<br>Factor N |

|---|----------|------------|---|----------|-----|----------|---|---|---|--------------------|

| 0 | 0        | 0          | 0 | 0        | 0   | 0        | 1 | 0 | 1 | 5                  |

| 0 | 0        | 0          | 0 | 0        | 0   | 0        | 1 | 1 | 0 | 6                  |

| 0 | 0        | 0          | 0 | 0        | 0   | o        | 1 | 1 | 1 | 7                  |

| • |          |            | • | •        |     |          |   |   |   |                    |

| 1 | 1        | 1          | 1 | 1        | 1   | 1        | 1 | 1 | 1 | 1023               |

Note: Divide factor less than 5 is prohibited.

Divide factor N: 5 to 1023

#### **PULSE SWALLOW FUNCTION**

$f_{VCO} = [(N \times M) + A] \times fr$

f<sub>VCO</sub>: Output frequency of external voltage controlled oscillator (VCO)

N : Preset divide factor of binary 10-bit programmable counter (5 to 1023)

: Preset modulus factor of external dual modulus prescaler (e.g. 64 in 64/65 mode, 128 in 128/129 mode of an MB501L prescaler)

: Preset divide factor of binary 7-bit swallow counter (0 to 127)

: Output frequency of the programmable reference divider

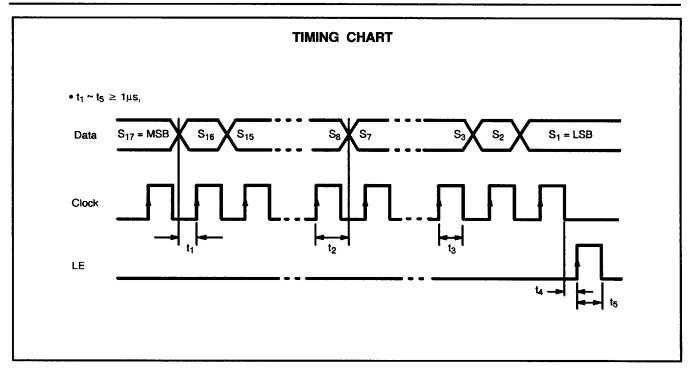

Clock: Clock signal input for the 17-bit shift register.

Each rising edge of the clock shifts one bit of data into the shift register.

Data: Serial data input for the 17-bit shift register.

LE : Load enable input.

When LE is high (high active), the data stored in the 17-bit shift register is transferred to the 17-bit latch.

The 17-bit data is used for setting a divide factor of the programmable divider.

# **RECOMMENDED OPERATING CONDITIONS**

$(V_{SS} = 0V)$

|                       |                 |                 | 11-74 |                 |      |

|-----------------------|-----------------|-----------------|-------|-----------------|------|

| Parameter             | Symbol          | Min             | Тур   | Max             | Unit |

| Power Supply Voltage  | V <sub>DD</sub> | 2.7             |       | 5.5             | ٧    |

| Input Voltage         | V <sub>IN</sub> | V <sub>SS</sub> |       | V <sub>DD</sub> | ٧    |

| Operating Temperature | T <sub>A</sub>  | -40             |       | +85             | °C   |

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 3.0V, V_{SS} = 0V, T_A = -40 \text{ to } 85^{\circ}\text{C})$

|                                                               | Value                  |                  |                                   |      |      |      | i Imla           |

|---------------------------------------------------------------|------------------------|------------------|-----------------------------------|------|------|------|------------------|

| Parameter                                                     |                        | Symbol           | Condition                         | Min  | Тур  | Max  | Unit             |

| High-level Input Voltage                                      | Except fin             | V <sub>IH</sub>  |                                   | 2.1  |      |      | ٧                |

| Low-level Input Voltage                                       | and OSC <sub>IN</sub>  | V <sub>IL</sub>  |                                   |      |      | 0.9  |                  |

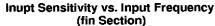

| Input Sensitivity                                             | fin                    | Vfin             | Amplitude in AC                   | 0.8  |      |      | V <sub>P-P</sub> |

|                                                               | OSCIN                  | Vosc             | coupling, sine wave               | 1.0  |      |      |                  |

| High-level Input Current                                      | Except fin             | ήн               | $V_{IN} = V_{DD}$                 |      | 1.0  |      | μΑ               |

| Low-level Input Current                                       | and OSC <sub>IN</sub>  | I <sub>IL</sub>  | V <sub>IN</sub> = V <sub>SS</sub> |      | -1.0 |      |                  |

|                                                               | fin                    | lfin             | $V_{IN} = V_{SS}$ to $V_{DD}$     |      | ±30  |      | μА               |

| Input Current                                                 | OSCIN                  | losc             | VIN = VSS to VDD                  |      | ±30  |      |                  |

| High-level Output Voltage                                     | Except   P             | V <sub>OH</sub>  | l <sub>OH</sub> = 0μA             | 2.95 |      |      | \ \ \            |

| Low-level Output Voltage                                      | and OSC <sub>OUT</sub> | V <sub>OL</sub>  | I <sub>OL</sub> = 0μA             |      |      | 0.05 |                  |

| Low-level Output Voltage                                      | φР                     | V <sub>OLP</sub> | I <sub>OL</sub> = 0.8mA           |      |      | 0.8  | 4                |

| High-level Output Voltage                                     | 000                    | V <sub>ОНХ</sub> | I <sub>OH</sub> = <b>0</b> μA     | 2.50 |      |      | \ \ \            |

| Low-level Output Voltage                                      | - OSC <sub>OUT</sub>   | V <sub>OLX</sub> | I <sub>OL</sub> = 0μA             |      |      | 0.50 | ļ                |

| High-level Output Current                                     | Except    P            | Юн               | V <sub>OH</sub> = 2.0V            | -0.5 |      |      | mA               |

| Low-level Output Current                                      | and OSC <sub>OUT</sub> | l <sub>OL</sub>  | V <sub>OL</sub> = 0.8V            | 0.5  |      |      |                  |

| N-channel Open Drain<br>Cut Off Current                       | φР                     | loff             | $V_O = V_{DD} + 3.0$              |      | 1.0  |      | μА               |

| Power Supply Current*1                                        |                        | IDD              |                                   |      | 2.0  |      | mA               |

| Max. Operating Frequency of<br>Programmable Reference Divider |                        | fmaxd            |                                   | 13   | 20   |      | МН               |

| Max. Operating Frequency of<br>Programmable Divider           |                        | fmaxp            |                                   | 10   | 20   |      | мн               |

Note: \*1: fin = 5.0MHz, 12.8MHz Crystal is connected between OSC<sub>IN</sub> and OSC<sub>OUT</sub>. Inputs are connected to ground except for fin and OSC<sub>IN</sub>. Outputs are open.

# ELECTRICAL CHARACTERISTICS (continued) (V<sub>DD</sub> = 5.0V, V<sub>SS</sub> = 0V, T<sub>A</sub> = -40 to 85°C)

|                                                               | O due                  |                  |                                                      | Value |      |      |                  |

|---------------------------------------------------------------|------------------------|------------------|------------------------------------------------------|-------|------|------|------------------|

| Parameter                                                     |                        | Symbol Condition |                                                      | Min   | Тур  | Max  | Unit             |

| High-level Input Voltage                                      | Except fin             | V <sub>IH</sub>  |                                                      | 3.5   |      |      |                  |

| Low-level Input Voltage                                       | and OSC <sub>IN</sub>  | V <sub>IL</sub>  |                                                      |       |      | 1.5  | V                |

|                                                               | fin                    | Vfin             | Amplitude in AC                                      | 1.0   |      |      |                  |

| Input Sensitivity                                             | OSCIN                  | Vosc             | coupling, sine wave                                  | 1.5   |      |      | V <sub>P-P</sub> |

| High-level Input Current                                      | Except fin             | ин               | V <sub>IN</sub> = V <sub>DD</sub>                    |       | 1.0  |      | μА               |

| Low-level Input Current                                       | and OSC <sub>IN</sub>  | կլ               | VIN = VSS                                            |       | -1.0 |      |                  |

|                                                               | fin                    | lfin             | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>DD</sub> |       | ±50  |      | μА               |

| Input Current                                                 | OSCIN                  | losc             | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>DD</sub> |       | ±50  |      | ,                |

| High-level Output Voltage                                     | Except   P             | V <sub>OH</sub>  | I <sub>OH</sub> = 0μΑ                                | 4.95  |      |      | V                |

| Low-level Output Voltage                                      | and OSC <sub>OUT</sub> | VOL              | l <sub>OL</sub> = 0μA                                |       |      | 0.05 | · ·              |

| Low-level Output Voltage                                      | φР                     | V <sub>OLP</sub> | I <sub>OL</sub> = 2mA                                |       |      | 1.0  |                  |

| High-level Output Voltage                                     |                        | V <sub>OHX</sub> | I <sub>OH</sub> = 0μA                                | 4.50  |      |      | V                |

| Low-level Output Voltage                                      | OSC <sub>OUT</sub>     | loLX             | l <sub>OL</sub> = 0μA                                |       |      | 0.50 |                  |

| High-level Output Current                                     | Except    P            | ЮН               | V <sub>OH</sub> = 4.0V                               | -1.0  |      |      | mA               |

| Low-level Output Current                                      | and OSC <sub>OUT</sub> | loL              | V <sub>OL</sub> = 0.8V                               | 1.0   |      |      | 11114            |

| N-channel Open Drain<br>Cut Off Current                       | φР                     | loff             | V <sub>O</sub> = V <sub>DD</sub> +3.0                |       | 1.0  |      | μА               |

| Power Supply Current*1                                        |                        | I <sub>DD</sub>  |                                                      |       | 3.0  |      | mA               |

| Max. Operating Frequency of<br>Programmable Reference Divider |                        | fmaxd            |                                                      | 15    | 25   |      | МН               |

| Max. Operating Frequency of<br>Programmable Divider           |                        | fmaxp            |                                                      | 13    | 25   |      | МН               |

Note: \*1: fin = 5.0MHz, 12.8MHz Crystal is connected between OSC<sub>IN</sub> and OSC<sub>OUT</sub>. Inputs are connected to ground except for fin and OSCIN. Outputs are open.

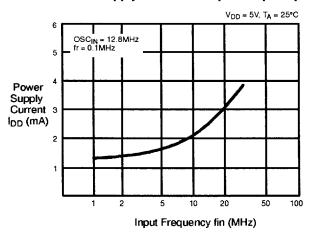

## **TYPICAL CHARACTERISTICS CURVES**

#### **Power Supply Current vs. Input Frequency**

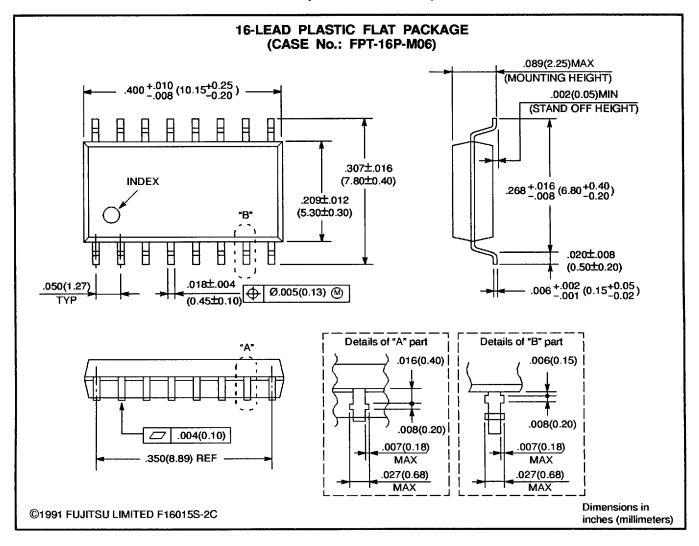

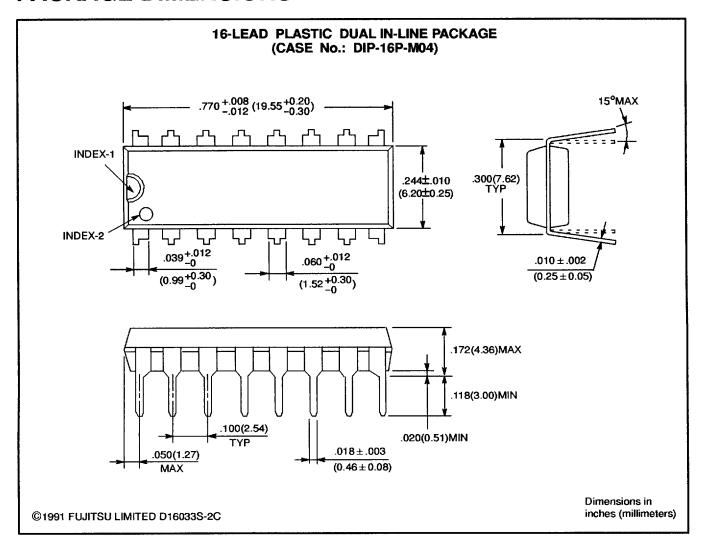

# **PACKAGE DIMENSIONS**

# **PACKAGE DIMENSIONS (Continued)**