DS04-13211-3E

# General Purpose Linear IC's General Purpose Converters

# D/A Converter for Digital Tuning

(With Built-in OP Amp and I/O Expander)

# **MB88141**

#### DESCRIPTION

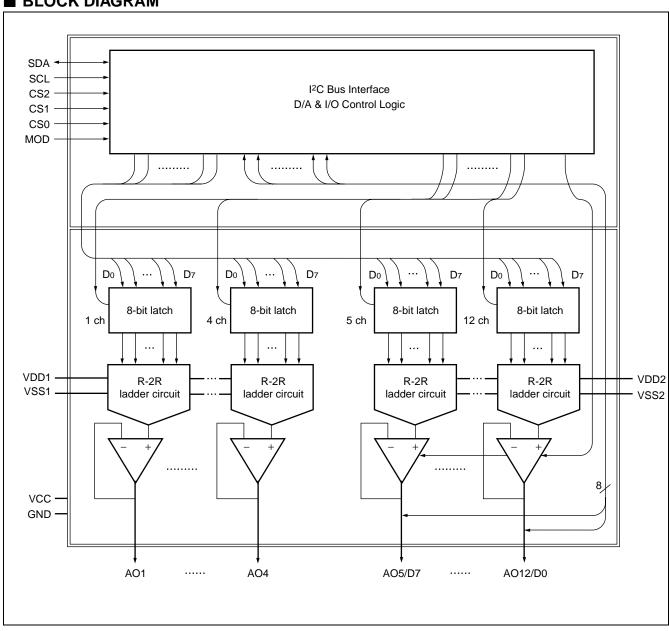

The FUJITSU MB88141 is a D/A converter with 12 built-in channels.

The 12 analog output channels have built-in OP Amps, providing large current drive capability.

Data input is compatible with I<sup>2</sup>C specifications, and is controlled by two control lines.

The built-in I/O expander function allows the MB88141 to be controlled by devices incompatible with I<sup>2</sup>C bus specifications (provides conversion between I<sup>2</sup>C serial and 8- or 4-bit parallel I/O).

Can be adapted for tuning by electronically variable or pre-fixed resistance, etc.

#### ■ FEATURES

- Ultra-low power consumption (0.9 mW/channel Typ.)

- Ultra-compact package

- Built-in 12-channel R-2R type 8-bit D/A converter

- Built-in analog output amplifier (maximum sink current 1.0 mA, maximum source current 1.0 mA)

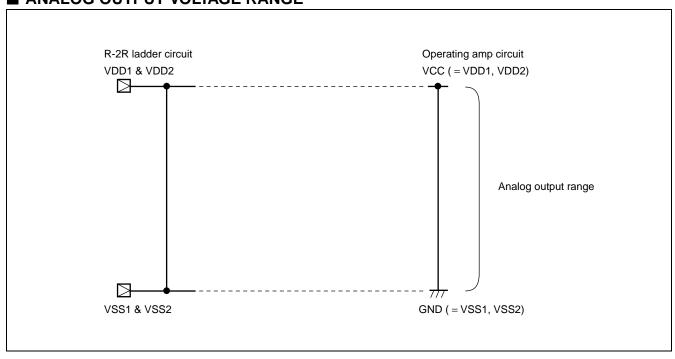

- Analog output range 0 V to Vcc

(Continued)

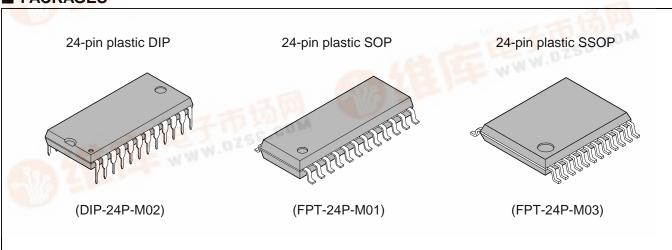

### ■ PACKAGES

Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips."

# (Continued)

- 5 V single power supply

- Power supply/GND for MCU interface and OP Amp is separate from power supply/GND for D/A converter

- Power supply for D/A converter is divided into two systems for V<sub>DD1</sub>/V<sub>SS1</sub> (AO<sub>1</sub> to AO<sub>4</sub>) and V<sub>DD2</sub>/V<sub>SS2</sub> (AO<sub>5</sub> to AO<sub>12</sub>), allowing separate level settings for each system

- Compatible with serial data input, I2C specifications

- Built-in I/O expander function (converts between I<sup>2</sup>C serial and 8- or 4-bit parallel)

- CMOS process

- Packages: DIP 24-pin, SOP 24-pin, SSOP 24-pin

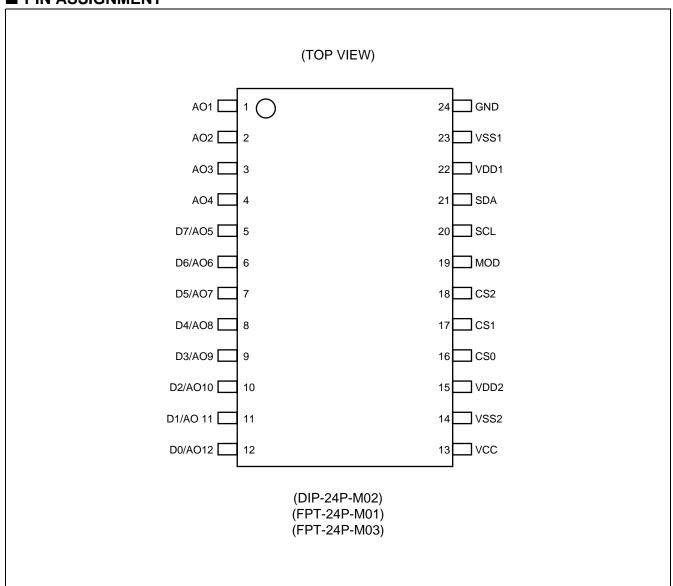

# **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTIONS**

| Pin no.                           | Symbol                                                                          | I/O | Description                                                                                                                                          |

|-----------------------------------|---------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21                                | SDA                                                                             | BUS | I <sup>2</sup> C bus data input/output pin (hysteresis input). * <sup>2</sup> Outputs the acknowledge signal.                                        |

| 20                                | SCL                                                                             | I   | I <sup>2</sup> C bus shift clock input pin (hysteresis input). * <sup>2</sup>                                                                        |

| 19                                | MOD                                                                             | I   | D/A converter and I/O expander mode switching pin. *1, *3 Input "L" to operate as a D/A converter, "H" to operate as I/O expander and D/A converter. |

| 16<br>17<br>18                    | CS0<br>CS1<br>CS2                                                               | I   | Lower 3 bits of the slave address setting pins. *1 This allows up to eight MB88141 chips to be used on the same bus line.                            |

| 1<br>2<br>3<br>4                  | AO1<br>AO2<br>AO3<br>AO4                                                        | 0   | 8-bit D/A output with OP Amp. *3                                                                                                                     |

| 5<br>6<br>7<br>8<br>9<br>10<br>11 | D7/AO5<br>D6/AO6<br>D5/AO7<br>D4/AO8<br>D3/AO9<br>D2/AO10<br>D1/AO11<br>D0/AO12 | I/O | 8-bit D/A output with OP Amp. *3 In I/O expander operation, these pins function as parallel data input/output pins.                                  |

| 13                                | VCC                                                                             | _   | Power supply pin for digital circuits and OP Amp.                                                                                                    |

| 24                                | GND                                                                             | _   | GND pin for digital circuits and OP Amp.                                                                                                             |

| 22                                | VDD1                                                                            | _   | Reference power supply pin for D/A converter (H). AO1 to AO4.                                                                                        |

| 23                                | VSS1                                                                            | _   | Reference power supply pin for D/A converter (L). AO1 to AO4.                                                                                        |

| 15                                | VDD2                                                                            | _   | Reference power supply pin for D/A converter (H). AO5 to AO12.                                                                                       |

| 14                                | VSS2                                                                            | _   | Reference power supply pin for D/A converter (L). AO5 to AO12.                                                                                       |

<sup>\*1:</sup> The MOD and CS0-CS2 pins should be used with fixed level input.

<sup>\*2:</sup> Use particular caution in handling the SDA and SCL pins. These pins have no transistor protection against Vcc voltage and therefore have weaker anti-static characteristics than other pins.

<sup>\*3:</sup> When using the I/O expander function together with the D/A converter function, take care that D/A converter output precision is within a range that will not affect overall system operation.

# **■ BLOCK DIAGRAM**

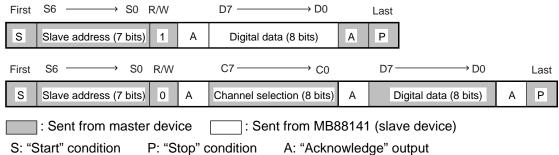

## **■ DATA CONFIGURATION**

The MB88141 data configuration differs in each of the two operating modes (D/A converter (12-channel) and I/O expander plus D/A converter), selected by the MOD pin signal.

# 1. For D/A Converter (12-channel) Operation (MOD = "L")

# (1) I2C Bus Format

| First S6 ───── S0      | R/W    |        | C7 ———        | —— C0         |      | D7                |   | Last |

|------------------------|--------|--------|---------------|---------------|------|-------------------|---|------|

| S Slave address (7 bit | s) 0   | А      | Channel selec | tion (8 bits) | Α    | D/A data (8 bits) | Α | Р    |

| : Sent from mas        | er dev | ice    | : Sent        | from MB8      | 8141 | (slave device)    |   |      |

| S: "Start" condition   | P: "S  | top" ( | condition     | A: "Ackno     | wled | ge" output        |   |      |

### (2) Slave Address Comparison (7 bits)

|    | Slave address input (7 bits) |    |    |    |    |    |  |  |  |  |  |  |  |  |  |

|----|------------------------------|----|----|----|----|----|--|--|--|--|--|--|--|--|--|

| S6 | S5                           | S4 | S3 | S2 | S1 | S0 |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 0  | 0  | 0  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 0  | 0  | 1  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 0  | 1  | 0  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 0  | 1  | 1  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 1  | 0  | 0  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 1  | 0  | 1  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 1  | 1  | 0  |  |  |  |  |  |  |  |  |  |

| 1  | 0                            | 0  | 1  | 1  | 1  | 1  |  |  |  |  |  |  |  |  |  |

| Ir  | nterna | lly fixe | ed  | Exte | ernally | set |

|-----|--------|----------|-----|------|---------|-----|

| CS6 | CS5    | CS4      | CS3 | CS2  | CS1     | CS0 |

| 1   | 0      | 0        | 1   | 0    | 0       | 0   |

| 1   | 0      | 0        | 1   | 0    | 0       | 1   |

| 1   | 0      | 0        | 1   | 0    | 1       | 0   |

| 1   | 0      | 0        | 1   | 0    | 1       | 1   |

| 1   | 0      | 0        | 1   | 1    | 0       | 0   |

| 1   | 0      | 0        | 1   | 1    | 0       | 1   |

| 1   | 0      | 0        | 1   | 1    | 1       | 0   |

| 1   | 0      | 0        | 1   | 1    | 1       | 1   |

Address comparison: Operates only for devices whose own slave address (internally fixed CS6 to CS3 and externally set CS2 to CS0) matches the slave address input value.

=

## (3) R/W Selection (1 bit)

Fixed at "0" (the D/A converter performs write operations only).

(4) Channel Selection (8 bit)

| <b>C7</b> | C6 | C5 | C4 | C3 | C2 | C1 | C0 | Channel select           |

|-----------|----|----|----|----|----|----|----|--------------------------|

| ×         | ×  | ×  | ×  | 0  | 0  | 0  | 0  | All channels selected *1 |

| ×         | ×  | ×  | ×  | 0  | 0  | 0  | 1  | AO1 selected             |

| 5         | 5  | 5  | 5  | 5  | 5  | 5  | 5  | (                        |

| ×         | ×  | ×  | ×  | 1  | 1  | 0  | 0  | AO12 selected            |

| ×         | ×  | ×  | ×  | 1  | 1  | 0  | 1  | Don't care               |

| ×         | ×  | ×  | ×  | 1  | 1  | 1  | 0  | Don't care               |

| ×         | ×  | ×  | ×  | 1  | 1  | 1  | 1  | All channels selected *2 |

×: Don't care

\*1: The 1 byte of data following the channel selection is set on all channels (all channels set to the same data value).

| S | Slave address (7 bits) | 0 | Α | XXXX0000 | Α | D/A data (8 bits) | Α | Р |

|---|------------------------|---|---|----------|---|-------------------|---|---|

\*2: The 12 bytes of data following the channel selection are set on all channels (all channels set to separate data values).

| S Slave address 0 | A XXXX1111 | Α | AO1 data | Α | ••• | AO12 data | Α | Р |

|-------------------|------------|---|----------|---|-----|-----------|---|---|

: Sent from master device : Sent from MB88141 (slave device)

S: "Start" condition P: "Stop" condition A: "Acknowledge" output

Note: Setting will repeat, continuing in order from ch1, until the start and stop conditions are acknowledged.

# (5) D/A Data (8 bits)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Channel select                                   |  |  |  |  |  |

|----|----|----|----|----|----|----|----|--------------------------------------------------|--|--|--|--|--|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | ≅ Vss                                            |  |  |  |  |  |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | ≅ (V <sub>REF</sub> / 256) × 1 + V <sub>SS</sub> |  |  |  |  |  |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | ≅ (V <sub>REF</sub> / 256) × 2 + Vss             |  |  |  |  |  |

| 5  | 5  | 5  | 5  | 5  | 5  | 5  | 5  | <b>\</b>                                         |  |  |  |  |  |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | ≅ (VREF / 256) × 254 + Vss                       |  |  |  |  |  |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | ≅ (VREF / 256) × 255 + Vss                       |  |  |  |  |  |

Note:  $V_{REF} = V_{DD} - V_{SS}$

# 2. For D/A Converter + I/O Expander Operation (MOD = "H")

### (1) I2C Bus Format

# (2) Slave Address Comparison (7 bits)

Slave address comparison is the same as for D/A converter (12-channel) operation (see "1. (2) "Slave Address Comparison"), with the exception that the CS2 setting determines the number of D/A converter channels and the number of I/O expander bits.

| CS2 | D/A converter           | I/O expander      |

|-----|-------------------------|-------------------|

| 0   | 4 channels (AO1 to AO4) | 8 bits (D7 to D0) |

| 1   | 8 channels (AO1 to AO8) | 4 bits (D3 to D0) |

When CS2 = "1" is selected, the upper 4 bits ( $D_7$  to  $D_4$ ) of write operations ( $I^2C$  bus to parallel interface) are ignored, and the upper 4 bits or read operations (parallel interface to  $I^2C$  bus) are output at "0" (low).

#### (3) R/W Selection (1 bit)

| R/W | I/O expander operation                                        | D/A converter operation             |  |  |

|-----|---------------------------------------------------------------|-------------------------------------|--|--|

| 0   | I <sup>2</sup> C bus input → parallel data output             | $I^2C$ bus input $	o$ analog output |  |  |

| 1   | Parallel data input $\rightarrow$ I <sup>2</sup> C bus output | _                                   |  |  |

### (4) Channel Selection (8 bits)

| <b>C7</b> | C6 | C5 | C4 | C3 | C2 | C1 | C0 | Channel select                    |

|-----------|----|----|----|----|----|----|----|-----------------------------------|

| ×         | ×  | ×  | ×  | 0  | 0  | 0  | 0  | I/O expander operation            |

| ×         | ×  | ×  | ×  | 0  | 0  | 0  | 1  | AO1 selected                      |

| 5         | 5  | 5  | 5  | 5  | 5  | 5  | 5  | \$                                |

| ×         | ×  | ×  | ×  | 0  | 1  | 0  | 0  | AO4 selected                      |

| ×         | ×  | ×  | ×  | 0  | 1  | 0  | 1  | Don't care (AO5 selected)         |

| 5         | 5  | 5  | 5  | 5  | 5  | 5  | 5  | \$                                |

| ×         | ×  | ×  | ×  | 1  | 0  | 0  | 0  | Don't care (AO8 selected)         |

| ×         | ×  | ×  | ×  | 1  | 0  | 0  | 1  | Don't care                        |

| 5         | 5  | 5  | 5  | 5  | 5  | 5  | 5  | <b>S</b>                          |

| ×         | ×  | ×  | ×  | 1  | 1  | 1  | 0  | Don't care                        |

| ×         | ×  | ×  | ×  | 1  | 1  | 1  | 1  | I/O expander continuous operation |

<sup>():</sup> When using D/A converter 8 channel, I/O expander 4 bit operation.

# (5) D/A Data (8 bits)

Same as "1. (5) D/A Data (8 bits)."

# (6) I/O Expander Continuous Operation

$I^2C$  bus input  $\rightarrow$  parallel data output

| S | Slave address | 0 | Α | XXXX1111 | Α | Digital data | Α | • • • | Digital data | A | Р |

|---|---------------|---|---|----------|---|--------------|---|-------|--------------|---|---|

Note: In continuous operation, operation continues until start and stop conditions are acknowledged.

Parallel data input  $\rightarrow$  I  $^2$ C bus output

| S                                                            | Slave address                                                 | 1 | Α | Digital data | Α | Digital data | Α |    | Digital data | А | Р |

|--------------------------------------------------------------|---------------------------------------------------------------|---|---|--------------|---|--------------|---|----|--------------|---|---|

| : Sent from master device : Sent from MB88141 (slave device) |                                                               |   |   |              |   |              |   |    |              |   |   |

| S: "                                                         | "Start" condition P: "Stop" condition A: "Acknowledge" outpot |   |   |              |   |              |   | ıt |              |   |   |

<sup>×:</sup> Don't care

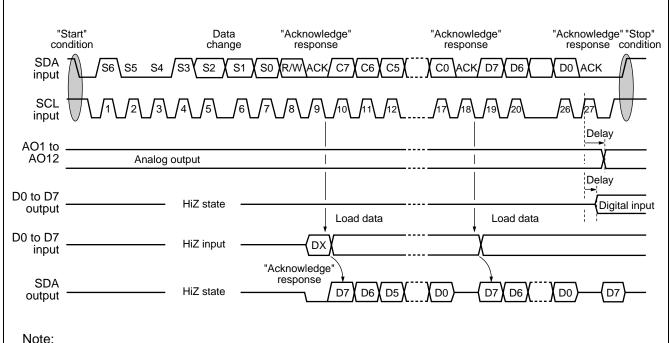

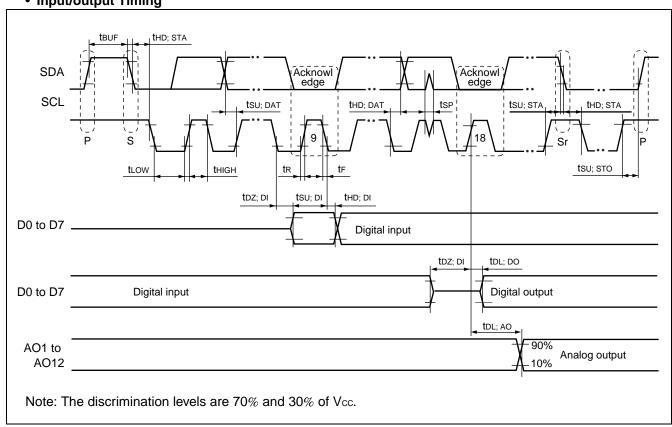

# ■ TIMING CHART (I<sup>2</sup>C BUS SPECIFICATIONS)

- The SDA input acknowledge response (ACK) is an output signal from the MB88141.

- The D0-D7 input and output timing represent the timing of switching to write and read operations respectively. Also, D0-D7 input remains in HiZ state between the end of a read operation and the acknowledgment of the next I/O write signal.

## ■ ANALOG OUTPUT VOLTAGE RANGE

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol          | Conditions                               | Rat  | Unit      |       |

|-----------------------|-----------------|------------------------------------------|------|-----------|-------|

| rarameter             | Symbol          |                                          | Min. | Max.      | Offic |

|                       | Vcc             |                                          | -0.3 | +7.0*     | V     |

| Supply voltage        | V <sub>DD</sub> |                                          | -0.3 | +7.0*     | V     |

|                       | Vss             | With reference to GND,<br>at Ta = +25 °C | -0.3 | +7.0*     | V     |

| Input voltage         | Vin             | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1  | -0.3 | Vcc + 0.3 | V     |

| Output voltage        | Vоит            |                                          | -0.3 | Vcc + 0.3 | V     |

| Power consumption     | Po              | _                                        | _    | 250       | mW    |

| Operating temperature | Та              | _                                        | -20  | +85       | °C    |

| Storage temperature   | Tstg            | _                                        | -55  | +120      | °C    |

<sup>\*:</sup>  $V_{CC} \ge V_{DD1} \ge V_{SS1}$ ,  $V_{CC} \ge V_{DD2} \ge V_{SS2}$

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                           | Symbol           | Conditions                                      |      | Unit |      |      |

|-------------------------------------|------------------|-------------------------------------------------|------|------|------|------|

| Farameter                           | Symbol           | Conditions                                      | Min. | Тур. | Max. | Onit |

| Supply voltage 1                    | Vcc              | _                                               | 4.5  | 5.0  | 5.5  | V    |

| Supply voltage 1                    | GND              | _                                               | _    | 0    | _    | V    |

| Supply voltage 2                    | V <sub>DD1</sub> | Vcc ≥ V <sub>DD1</sub> > Vss1                   | 2.0  | _    | Vcc  | V    |

| Supply voltage 2                    | Vss1             | $V_{SS1}$ $V_{DD1} - V_{SS1} \ge 2.0 \text{ V}$ |      | _    | 3.5  | V    |

| Supply voltage 3                    | V <sub>DD2</sub> | Vcc ≥ V <sub>DD2</sub> > Vss <sub>2</sub>       | 2.0  | _    | Vcc  | V    |

| Supply voltage 3                    | Vss2             | V <sub>DD2</sub> - V <sub>SS2</sub> ≥ 2.0 V     | 0    | _    | 3.5  | V    |

| Analog output ourrent               | Ial              | Source current                                  | 0    | _    | 1.0  | mA   |

| Analog output current               | <b>I</b> ан      | Sink current                                    | 0    | _    | 1.0  | mA   |

| Oscillator limit output capacitance | CoL              | _                                               | _    | _    | 1.0  | μF   |

| Digital data setting range          | _                | _                                               | #00  | _    | #FF  | _    |

| Operating temperature               | Та               | _                                               | -20  |      | +85  | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

# **■ ELECTRICAL CHARACTERISTICS**

# 1. DC Characteristics

# (1) Digital Circuits

$(VCC = 5 V \pm 10\%, GND = 0 V, Ta = -20 °C to +85 °C)$

| Parameter                | Symbol Pin name  |                        | Conditions                             |           | Unit |         |       |

|--------------------------|------------------|------------------------|----------------------------------------|-----------|------|---------|-------|

| Parameter                |                  |                        | Conditions                             | Min.      | Тур. | Max.    | Offic |

| Supply voltage           | Vcc              |                        | _                                      | 4.5       | 5.0  | 5.5     | V     |

| Supply current           | Icc              | VCC                    | SCL = 400 kHz,<br>no load              | _         | 1.0  | 3.7     | mA    |

| Input leak current       | lilk             | SDA, SCL,              | V <sub>IN</sub> = 0 to V <sub>CC</sub> | -10       | _    | +10     | μΑ    |

| "L" level input voltage  | VIL              | CS0, CS1,<br>CS2, MOD, | _                                      | 0         | _    | 0.3 Vcc | V     |

| "H" level input voltage  | ViH              | D0 to D7               | _                                      | 0.7 Vcc   |      | Vcc     | V     |

| Input hysteresis width   | VHYS             | SDA, SCL               | _                                      | 0.05 Vcc  | _    | _       | V     |

| "H" level output voltage | Vон              | D0 to D7               | Іон = -400 μА                          | Vcc - 0.4 | _    | _       | V     |

|                          | V <sub>OL1</sub> | ז'ט טו טט              | IoL = 2.5 mA                           | _         | _    | 0.4     | V     |

| "L" level output voltage | V <sub>OL2</sub> | SDA                    | IoL = 3.0 mA                           | _         | _    | 0.4     | V     |

|                          | Vol3             | SDK                    | IoL = 6.0 mA                           |           |      | 0.6     | V     |

# (2) Analog Circuits 1

(VCC = 5 V  $\pm$  10%, GND = 0 V, Ta = -20 °C to +85 °C)

| Parameter                    | Symbol Pin name |                                                                                                                                                                                     | Conditions                                                         |      | Unit |      |       |

|------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|-------|

| rarameter                    |                 |                                                                                                                                                                                     | Conditions                                                         | Min. | Тур. | Max. | Ollit |

| Current consumption          | loo             | VDD1,<br>VDD2                                                                                                                                                                       | No load<br>IDD = IDD1 + IDD2                                       | _    | 1.2  | 2.5  | mA    |

|                              | V <sub>DD</sub> | VDD2                                                                                                                                                                                | V <sub>DD1</sub> – V <sub>SS1</sub> ≥ 2.0 V                        | 2.0  | _    | Vcc  | V     |

| Analog voltage               | Vss             | $\begin{array}{c} \text{VSS1,} \\ \text{VSS2} \end{array}  \begin{array}{c} \text{VDD1} - \text{VSS1} \ge 2.0 \text{ V} \\ \text{VDD2} - \text{VSS2} \ge 2.0 \text{ V} \end{array}$ |                                                                    | GND  | _    | 3.5  | V     |

| Resolution                   | Res             |                                                                                                                                                                                     |                                                                    | _    | 8    |      | bit   |

| Monotonic increase           | Rem             | AO1 to                                                                                                                                                                              | $1 \text{ Vpp}_4 \text{ Vpp}_2 \leq \text{ Vcc} = (1.1 \text{ V})$ |      | 8    |      | bit   |

| Non-linearity error          | LE              | AO12                                                                                                                                                                                |                                                                    | -1.5 | _    | +1.5 | LSB   |

| Differential linearity error | DLE             |                                                                                                                                                                                     |                                                                    | -1.0 |      | +1.0 | LSB   |

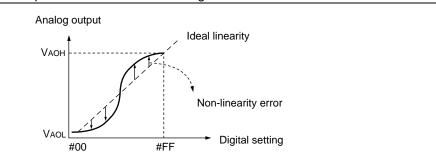

### Non-linearity error:

Error in the input/output curve with respect to a straight line connecting output voltage at "00" and output voltage at "FF" levels.

## Differential linearity error:

Deviation from ideal voltage with respect to a 1-bit increase in digital value.

Note:  $V_{AOH}$  and  $V_{DD}$ , as well as  $V_{AOL}$  and  $V_{SS}$  are not necessarily the same values.

## (3) Analog Circuits 2

$$(VCC = VDD1 = VDD2 = 5.0 \text{ V}, GND = VSS1 = VSS2 = 0.0 \text{ V}, Ta = -20 ^{\circ}C \text{ to } +85 ^{\circ}C)$$

| Parameter                | Symbol            | Pin name | Conditions               |                      |                       | Unit            |                       |       |

|--------------------------|-------------------|----------|--------------------------|----------------------|-----------------------|-----------------|-----------------------|-------|

| raiailletei              | Symbol            | Fin name | Conu                     | 1110115              | Min.                  | Тур.            | Max.                  | Ollic |

| Output minimum voltage 1 | V <sub>AOL1</sub> |          | $I_{AL} = 0 \mu A$       |                      | Vss                   | _               | Vss + 0.1             | V     |

| Output minimum voltage 2 | V <sub>AOL2</sub> |          | $I_{AL} = 500 \ \mu A$   | Digital data<br>"00" | Vss - 0.2             | Vss             | Vss + 0.2             | V     |

| Output minimum voltage 3 | V <sub>AOL3</sub> |          | I <sub>AH</sub> = 500 μA |                      | Vss                   | _               | Vss + 0.2             | V     |

| Output minimum voltage 4 | V <sub>AOL4</sub> |          | I <sub>AL</sub> = 1.0 mA |                      | Vss - 0.3             | Vss             | Vss + 0.3             | V     |

| Output minimum voltage 5 | V <sub>AOL5</sub> | AO1 to   | I <sub>AH</sub> = 1.0 mA |                      | Vss                   | _               | Vss + 0.3             | V     |

| Output maximum voltage 1 | V <sub>AOH1</sub> | AO12     | $I_{AL} = 0 \mu A$       |                      | V <sub>DD</sub> – 0.1 | _               | V <sub>DD</sub>       | V     |

| Output maximum voltage 2 | V <sub>AOH2</sub> |          | $I_{AL} = 500 \ \mu A$   |                      | V <sub>DD</sub> – 0.2 |                 | V <sub>DD</sub>       | V     |

| Output maximum voltage 3 | V <sub>AOH3</sub> |          | I <sub>AH</sub> = 500 μA | Digital data "FF"    | V <sub>DD</sub> – 0.2 | V <sub>DD</sub> | V <sub>DD</sub> + 0.2 | V     |

| Output maximum voltage 4 | V <sub>AOH4</sub> |          | I <sub>AL</sub> = 1.0 mA |                      | V <sub>DD</sub> - 0.3 | _               | V <sub>DD</sub>       | V     |

| Output maximum voltage 5 | V <sub>AOH5</sub> |          | I <sub>AH</sub> = 1.0 mA |                      | V <sub>DD</sub> – 0.3 | $V_{DD}$        | V <sub>DD</sub> + 0.3 | V     |

# 2. AC Characteristics

|                                                   |                                   |                                    |                      | _              |           | V           | alue        |        |      |

|---------------------------------------------------|-----------------------------------|------------------------------------|----------------------|----------------|-----------|-------------|-------------|--------|------|

|                                                   | Parame                            | eter                               | Symbol               | Con-<br>dition | Standa    | rd mode     | High spee   | d mode | Unit |

|                                                   |                                   |                                    | Min.                 | Max.           | Min. Max. |             |             |        |      |

| SCL clock                                         | frequency                         |                                    | fscL                 | _              | 0         | 100         | 0           | 400    | kHz  |

| Bus free ti<br>and "start"                        |                                   | "stop" condition                   | <b>t</b> BUF         | _              | 4.7       | _           | 1.3         |        | μs   |

|                                                   | ock pulse is                      | art" condition.<br>generated after | <b>t</b> HD;STA      | _              | 4.0       | _           | 0.6         | _      | μs   |

| SCL clock                                         | low hold tim                      | ne                                 | <b>t</b> LOW         | _              | 4.7       | _           | 1.3         | _      | μs   |

| SCL clock                                         | high hold tii                     | me                                 | <b>t</b> HIGH        | _              | 4.0       | _           | 0.6         | _      | μs   |

| Resend "s                                         | send "start" condition setup time |                                    | tsu;sta              | _              | 4.7       | _           | 0.6         | _      | μs   |

| Data hold                                         | time                              | ne                                 |                      | _              | 0         | _           | 0           | 0.9    | μs   |

| Data setup time                                   |                                   |                                    | tsu; dat             | _              | 250       | _           | 100         | _      | ns   |

| SDA and SCL signal fall time                      |                                   |                                    | <b>t</b> R           | _              | _         | 1000        | 20 + 0.1 Cb | 300    | ns   |

| SDA and SCL signal rise time                      |                                   | tr                                 | _                    | _              | 300       | 20 + 0.1 Cb | 300         | ns     |      |

| "Stop" con                                        | dition setup                      | time                               | tsu;sto              | _              | 4.0       | _           | 0.6         | _      | μs   |

| Pulse widt filter                                 | h of spike su                     | ippressed by input                 | <b>t</b> sp          | _              | _         | _           | 0           | 50     | ns   |

|                                                   | time when                         | Sink current 3 mA                  |                      | _              | _         | 250         | 20 + 0.1 Cb | 250    | ns   |

| bus capacitance is<br>between 10 pF and<br>400 pF |                                   | Sink current 6 mA                  | <b>t</b> of          |                | _         | _           | 20 + 0.1 Cb | 250    | ns   |

| I <sup>2</sup> C bus line capacitance load        |                                   | Cb                                 | _                    | _              | 400       |             | 400         | pF     |      |

| D/A                                               | Analog output settling time       |                                    | <b>t</b> DL; AO      | *1             | _         | 100         |             | 100    | μs   |

|                                                   | Digital outp                      | out delay time                     | tdl;do               | *2             | _         | 300         | _           | 300    | ns   |

| I/O                                               | Input open                        | time                               | t <sub>DZ</sub> ; DI | *3             | 200       | _           | 200         |        | ns   |

| expander                                          | Digital inpu                      | ıt setup time                      | tsu; DI              | _              | 250       | _           | 100         | _      | ns   |

|                                                   | Digital inpu                      | ıt hold time                       | <b>t</b> HD ; DI     | _              | 0.9       | _           | 0.9         | _      | μs   |

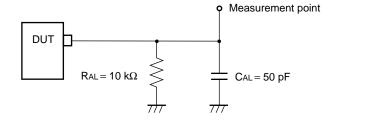

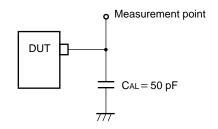

<sup>\*1:</sup> Load condition 1

\*2: Load condition 2

<sup>\*3:</sup> The I/O expander input open time value applies to read operation following an I/O write operation, or to an I/O write operation following a read operation.

# • Input/output Timing

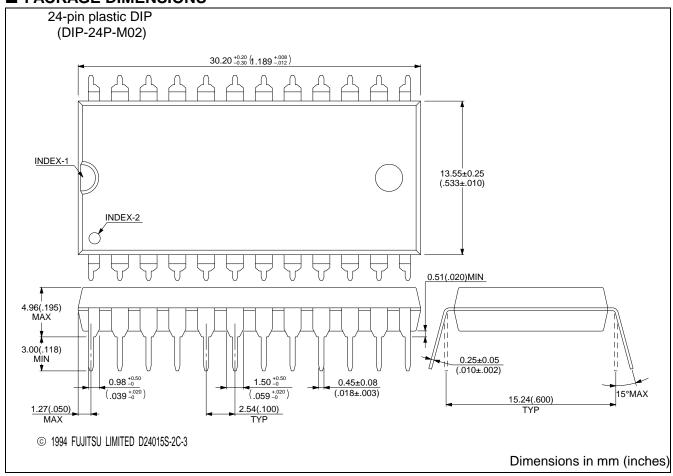

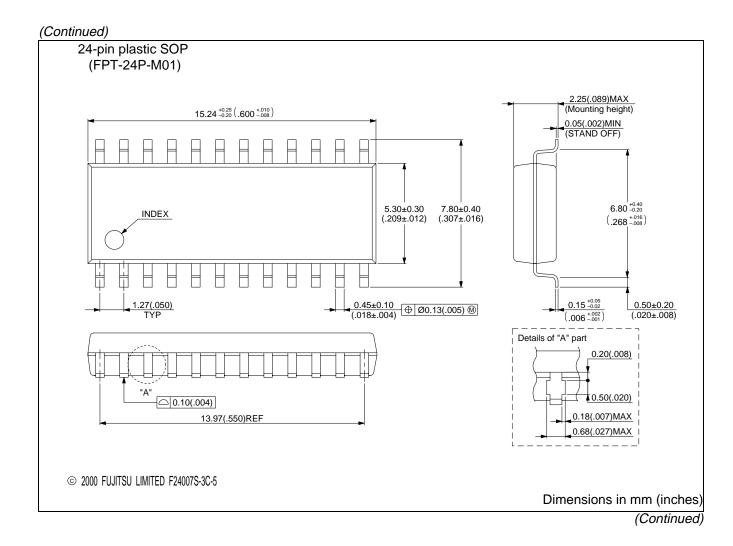

# **■** ORDERING INFORMATION

| Part number | Package                              | Remarks |

|-------------|--------------------------------------|---------|

| MB88141P    | 24-pin plastic DIP<br>(DIP-24P-M02)  |         |

| MB88141PF   | 24-pin plastic SOP<br>(FPT-24P-M01)  |         |

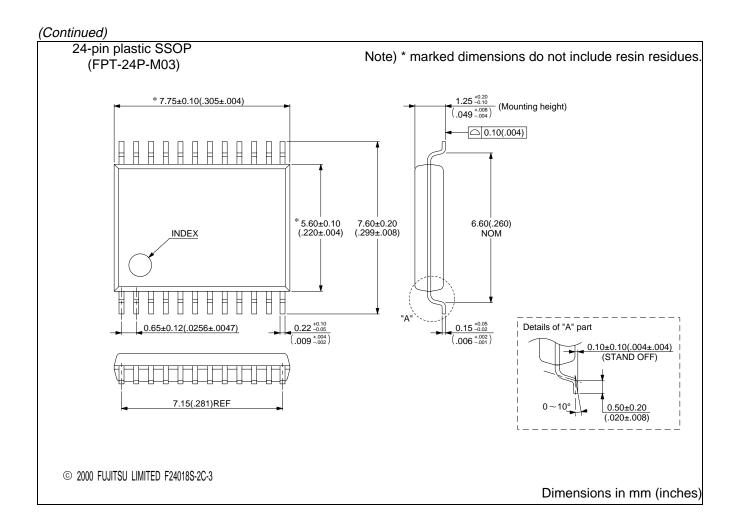

| MB88141PFV  | 24-pin plastic SSOP<br>(FPT-24P-M03) |         |

# **■ PACKAGE DIMENSIONS**

(Continued)

# **FUJITSU LIMITED**

For further information please contact:

### **Japan**

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices

Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku,

Tokyo 163-0721, Japan Tel: +81-3-5322-3347 Fax: +81-3-5322-3386

http://edevice.fujitsu.com/

#### **North and South America**

FUJITSU MICROELECTRONICS, INC. 3545 North First Street, San Jose, CA 95134-1804, U.S.A.

Tel: +1-408-922-9000 Fax: +1-408-922-9179

Customer Response Center Mon. - Fri.: 7 am - 5 pm (PST)

Tel: +1-800-866-8608 Fax: +1-408-922-9179 http://www.fujitsumicro.com/

## **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH

Am Siebenstein 6-10, D-63303 Dreieich-Buchschlag,

Germany

Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://www.fujitsu-fme.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. #05-08, 151 Lorong Chuan,

New Tech Park, Singapore 556741 Tel: +65-281-0770 Fax: +65-281-0220

http://www.fmap.com.sg/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 1702 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu, Seoul 135-280

Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

F0101 © FUJITSU LIMITED Printed in Japan All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.).

#### CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.